Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2525-i-so |

#### 4.0 RESET

The PIC18F2525/2620/4525/4620 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 5.1.2.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 23.2 "Watchdog Timer (WDT)".

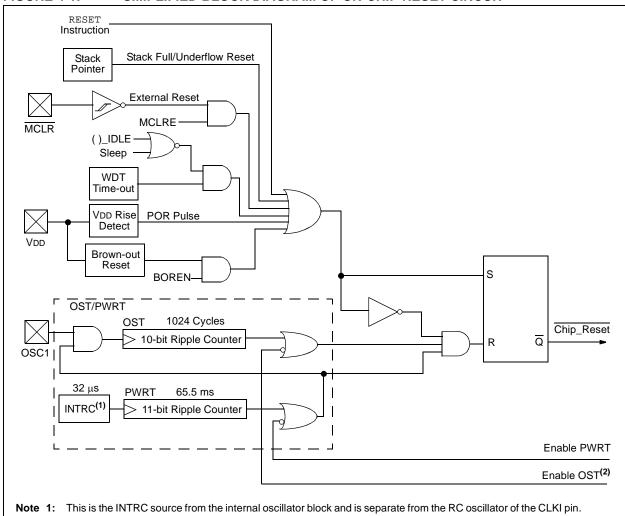

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 4-1.

#### 4.1 RCON Register

Device Reset events are tracked through the RCON register (Register 4-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 4.6** "Reset State of Registers".

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 10.0 "Interrupts". BOR is covered in Section 4.4 "Brown-out Reset (BOR)".

FIGURE 4-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

2: See Table 4-2 for time-out situations.

#### 4.4 Brown-out Reset (BOR)

PIC18F2525/2620/4525/4620 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV1:BORV0 and BOREN1:BOREN0 Configuration bits. There are a total of four BOR configurations which are summarized in Table 4-1.

The BOR threshold is set by the BORV1:BORV0 bits. If BOR is enabled (any values of BOREN1:BOREN0, except '00'), any drop of VDD below VBOR (parameter D005) for greater than TBOR (parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-on Timer (PWRT) are independently configured. Enabling BOR Reset does not automatically enable the PWRT.

#### 4.4.1 SOFTWARE ENABLED BOR

When BOREN1:BOREN0 = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'.

Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note: Even when BOR is under software control, the BOR Reset voltage level is still set by the BORV1:BORV0 Configuration bits. It cannot be changed in software.

#### 4.4.2 DETECTING BOR

When BOR is enabled, the BOR bit always resets to '0' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any POR event. If BOR is '0' while POR is '1', it can be reliably assumed that a BOR event has occurred.

#### 4.4.3 DISABLING BOR IN SLEEP MODE

When BOREN1:BOREN0 = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

TABLE 4-1: BOR CONFIGURATIONS

| BOR Con | BOR Configuration |                     | DOD Constitution                                                                   |  |  |

|---------|-------------------|---------------------|------------------------------------------------------------------------------------|--|--|

| BOREN1  | BOREN0            | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |  |  |

| 0       | 0                 | Unavailable         | BOR disabled; must be enabled by reprogramming the Configuration bits.             |  |  |

| 0       | 1                 | Available           | BOR enabled in software; operation controlled by SBOREN.                           |  |  |

| 1       | 0                 | Unavailable         | BOR enabled in hardware in Run and Idle modes, disabled during Sleep mode.         |  |  |

| 1       | 1                 | Unavailable         | BOR enabled in hardware; must be disabled by reprogramming the Configuration bits. |  |  |

#### 4.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different Reset situations, as indicated in Table 4-3. These bits are used in software to determine the nature of the Reset.

Table 4-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

TABLE 4-3: STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR RCON REGISTER

| Condition                                                | Program               | RCON Register |    |    |    |     | STKPTR Register |        |        |

|----------------------------------------------------------|-----------------------|---------------|----|----|----|-----|-----------------|--------|--------|

| Condition                                                | Counter               | SBOREN        | RI | то | PD | POR | BOR             | STKFUL | STKUNF |

| Power-on Reset                                           | 0000h                 | 1             | 1  | 1  | 1  | 0   | 0               | 0      | 0      |

| RESET Instruction                                        | 0000h                 | u <b>(2)</b>  | 0  | u  | u  | u   | u               | u      | u      |

| Brown-out Reset                                          | 0000h                 | u <b>(2)</b>  | 1  | 1  | 1  | u   | 0               | u      | u      |

| MCLR during power-managed Run Modes                      | 0000h                 | <b>u</b> (2)  | u  | 1  | u  | u   | u               | u      | u      |

| MCLR during power-managed Idle modes and Sleep mode      | 0000h                 | <b>u</b> (2)  | u  | 1  | 0  | u   | u               | u      | u      |

| WDT time-out during full power or power-managed Run mode | 0000h                 | ս <b>(2)</b>  | u  | 0  | u  | u   | u               | u      | u      |

| MCLR during full-power execution                         | 0000h                 | ս <b>(2)</b>  | u  | u  | u  | u   | u               | u      | u      |

| Stack Full Reset (STVREN = 1)                            | 0000h                 | u <b>(2)</b>  | u  | u  | u  | u   | u               | 1      | u      |

| Stack Underflow Reset (STVREN = 1)                       | 0000h                 | ս <b>(2)</b>  | u  | u  | u  | u   | u               | u      | 1      |

| Stack Underflow Error (not an actual Reset, STVREN = 0)  | 0000h                 | ս <b>(2)</b>  | u  | u  | u  | u   | u               | u      | 1      |

| WDT time-out during power-managed Idle or Sleep modes    | PC + 2                | u <b>(2)</b>  | u  | 0  | 0  | u   | u               | u      | u      |

| Interrupt exit from power-managed modes                  | PC + 2 <sup>(1)</sup> | <b>u</b> (2)  | u  | u  | 0  | u   | u               | u      | u      |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for POR and unchanged for all other Resets when software BOR is enabled (BOREN1:BOREN0 Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is '0'.

#### 5.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 5.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

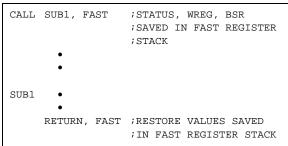

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

### 5.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF<br>CALL | OFFSET, | W |

|-------|--------------|---------|---|

| ORG   | nn00h        |         |   |

| TABLE | ADDWF        | PCL     |   |

|       | RETLW        | nnh     |   |

|       | RETLW        | nnh     |   |

|       | RETLW        | nnh     |   |

|       | •            |         |   |

|       | •            |         |   |

|       |              |         |   |

#### 5.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 7.1 "Table Reads and Table Writes".

TABLE 9-5: PORTC I/O SUMMARY

| Pin            | Function            | TRIS<br>Setting | I/O | I/O<br>Type          | Description                                                                                                                               |

|----------------|---------------------|-----------------|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/     | RC0                 | 0               | 0   | DIG                  | LATC<0> data output.                                                                                                                      |

| T13CKI         |                     | 1               | ı   | ST                   | PORTC<0> data input.                                                                                                                      |

|                | T1OSO               | х               | 0   | ANA                  | Timer1 oscillator output; enabled when Timer1 oscillator enabled. Disables digital I/O.                                                   |

|                | T13CKI              | 1               | I   | ST                   | Timer1/Timer3 counter input.                                                                                                              |

| RC1/T1OSI/CCP2 | RC1                 | 0               | 0   | DIG                  | LATC<1> data output.                                                                                                                      |

|                |                     | 1               | ı   | ST                   | PORTC<1> data input.                                                                                                                      |

|                | T1OSI               | х               | I   | ANA                  | Timer1 oscillator input; enabled when Timer1 oscillator enabled. Disables digital I/O.                                                    |

|                | CCP2 <sup>(1)</sup> | 0               | 0   | DIG                  | CCP2 compare and PWM output; takes priority over port data.                                                                               |

|                |                     | 1               | - 1 | ST                   | CCP2 capture input.                                                                                                                       |

| RC2/CCP1/P1A   | RC2                 | 0               | 0   | DIG                  | LATC<2> data output.                                                                                                                      |

|                |                     | 1               | ı   | ST                   | PORTC<2> data input.                                                                                                                      |

|                | CCP1                | 0               | 0   | DIG                  | ECCP1 compare or PWM output; takes priority over port data.                                                                               |

|                |                     | 1               | ı   | ST                   | ECCP1 capture input.                                                                                                                      |

|                | P1A <sup>(2)</sup>  | 0               | 0   | DIG                  | ECCP1 Enhanced PWM output, channel A. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RC3/SCK/SCL    | RC3                 | 0               | 0   | DIG                  | LATC<3> data output.                                                                                                                      |

|                |                     | 1               | ı   | ST                   | PORTC<3> data input.                                                                                                                      |

|                | SCK                 | 0               | 0   | DIG                  | SPI clock output (MSSP module); takes priority over port data.                                                                            |

|                |                     | 1               | ı   | ST                   | SPI clock input (MSSP module).                                                                                                            |

|                | SCL                 | 0               | 0   | DIG                  | I <sup>2</sup> C™ clock output (MSSP module); takes priority over port data.                                                              |

|                |                     | 1               | I   | I <sup>2</sup> C/SMB | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting.                                                         |

| RC4/SDI/SDA    | RC4                 | 0               | 0   | DIG                  | LATC<4> data output.                                                                                                                      |

|                |                     | 1               | I   | ST                   | PORTC<4> data input.                                                                                                                      |

|                | SDI                 | 1               | ı   | ST                   | SPI data input (MSSP module).                                                                                                             |

|                | SDA                 | 0               | 0   | DIG                  | I <sup>2</sup> C data output (MSSP module); takes priority over port data.                                                                |

|                |                     | 1               | I   | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.                                                          |

| RC5/SDO        | RC5                 | 0               | 0   | DIG                  | LATC<5> data output.                                                                                                                      |

|                |                     | 1               | I   | ST                   | PORTC<5> data input.                                                                                                                      |

|                | SDO                 | 0               | 0   | DIG                  | SPI data output (MSSP module); takes priority over port data.                                                                             |

| RC6/TX/CK      | RC6                 | 0               | 0   | DIG                  | LATC<6> data output.                                                                                                                      |

|                |                     | 1               | I   | ST                   | PORTC<6> data input.                                                                                                                      |

|                | TX                  | 0               | 0   | DIG                  | Asynchronous serial transmit data output (EUSART module); takes priority over port data. User must configure as output.                   |

|                | CK                  | 0               | 0   | DIG                  | Synchronous serial clock output (EUSART module); takes priority over port data.                                                           |

|                |                     | 1               | ı   | ST                   | Synchronous serial clock input (EUSART module).                                                                                           |

| RC7/RX/DT      | RC7                 | 0               | 0   | DIG                  | LATC<7> data output.                                                                                                                      |

|                |                     | 1               | I   | ST                   | PORTC<7> data input.                                                                                                                      |

|                | RX                  | 1               | I   | ST                   | Asynchronous serial receive data input (EUSART module).                                                                                   |

|                | DT                  | 0               | 0   | DIG                  | Synchronous serial data output (EUSART module); takes priority over port data.                                                            |

|                |                     | 1               | I   | ST                   | Synchronous serial data input (EUSART module). User must configure as an input.                                                           |

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;  $I^2C/SMB = I^2C/SMBus$  input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set. Alternate assignment is RB3.

2: Enhanced PWM output is available only on PIC18F4525/4620 devices.

NOTES:

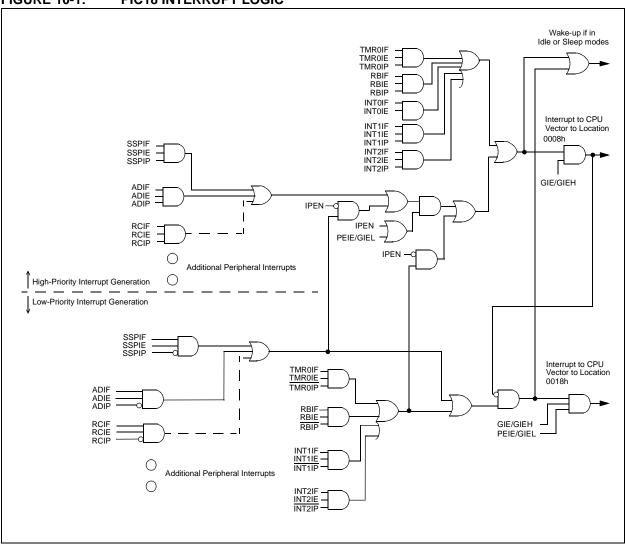

FIGURE 10-1: PIC18 INTERRUPT LOGIC

NOTES:

# 15.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F2525/2620/4525/4620 devices all have two CCP (Capture/Compare/PWM) modules. Each module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register.

In 28-pin devices, the two standard CCP modules (CCP1 and CCP2) operate as described in this chapter. In 40/44-pin devices, CCP1 is implemented as an Enhanced CCP module with standard Capture and Compare modes and Enhanced PWM modes. The ECCP implementation is discussed in Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

The Capture and Compare operations described in this chapter apply to all standard and Enhanced CCP modules.

Note: Throughout this section and Section 16.0

"Enhanced Capture/Compare/PWM (ECCP)

Module", references to the register and bit names for CCP modules are referred to generically by the use of 'x' or 'y' in place of the specific module number. Thus, "CCPxCON" might refer to the control register for CCP1, CCP2 or ECCP1. "CCPxCON" is used throughout these sections to refer to the module control register, regardless of whether the CCP module is a standard or enhanced implementation.

#### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER (28-PIN DEVICES)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| _     | _   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 **DCxB1:DCxB0**: PWM Duty Cycle bit 1 and bit 0 for CCPx Module

Capture mode:

Unused.

Compare mode:

Unused.

PWM mode:

These bits are the two LSbs (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight MSbs (DCx9:DCx2) of the duty cycle are found in CCPRxL.

#### bit 3-0 CCPxM3:CCPxM0: CCPx Module Mode Select bits

0000 = Capture/Compare/PWM disabled (resets CCPx module)

0001 = Reserved

0010 = Compare mode, toggle output on match (CCPxIF bit is set)

0011 = Reserved

0100 = Capture mode, every falling edge

0101 = Capture mode, every rising edge

0110 = Capture mode, every 4th rising edge

0111 = Capture mode, every 16th rising edge

1000 = Compare mode, initialize CCPx pin low; on compare match, force CCPx pin high (CCPxIF bit is set)

1001 = Compare mode, initialize CCPx pin high; on compare match, force CCPx pin low (CCPxIF bit is set)

1010 = Compare mode, generate software interrupt on compare match (CCPxIF bit is set, CCPx pin reflects I/O state)

1011 = Compare mode, trigger special event; reset timer; CCPx match starts A/D conversion (CCPxIF bit is set)

11xx = PWM mode

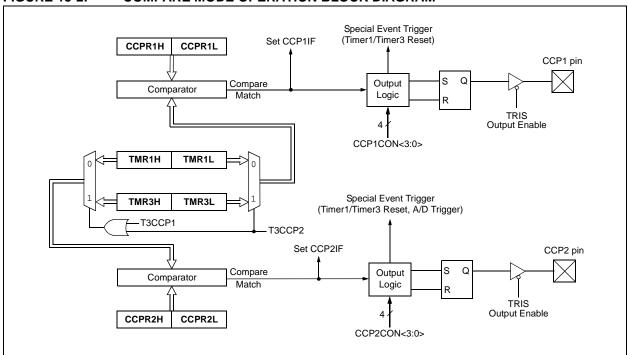

#### 15.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCPx pin can be:

- · driven high

- · driven low

- toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM3:CCPxM0). At the same time, the interrupt flag bit, CCPxIF, is set.

#### 15.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

Note:

Clearing the CCP2CON register will force the RB3 or RC1 compare output latch (depending on device configuration) to the default low level. This is not the PORTB or PORTC I/O data latch.

#### 15.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 15.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM3:CCPxM0 = 1010), the corresponding CCPx pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCPxIE bit is set.

#### 15.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCPxM3:CCPxM0 = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

The Special Event Trigger for CCP2 can also start an A/D conversion. In order to do this, the A/D converter must already be enabled.

FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 16.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP module for PWM operation:

- Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- 3. If auto-shutdown is required, do the following:

- Disable auto-shutdown (ECCP1AS = 0)

- Configure source (FLT0, Comparator 1 or Comparator 2)

- Wait for non-shutdown condition

- Configure the ECCP module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M1:P1M0 bits.

- Select the polarities of the PWM output signals with the CCP1M3:CCP1M0 bits.

- Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 6. For Half-Bridge Output mode, set the deadband delay by loading PWM1CON<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS2:ECCPAS0 bits.

- Select the shutdown states of the PWM output pins using the PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 8. If auto-restart operation is required, set the PRSEN bit (PWM1CON<7>).

- 9. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the CCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

### 16.4.10 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCP pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

### 16.4.10.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit (PIR2<7>) will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

#### 16.4.11 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

#### 18.1 Baud Rate Generator (BRG)

The BRG is a dedicated 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCON<3>) selects 16-bit mode.

The SPBRGH:SPBRG register pair controls the period of a free-running timer. In Asynchronous mode, bits, BRGH (TXSTA<2>) and BRG16 (BAUDCON<3>), also control the baud rate. In Synchronous mode, BRGH is ignored. Table 18-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGH:SPBRG registers can be calculated using the formulas in Table 18-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 18-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 18-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing any value (even the same value) to the SPBRGH:SPBRG registers immediately reloads the BRG timer. This may corrupt a transmission or reception already in progress. This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

### 18.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG register pair.

#### 18.1.2 SAMPLING

The data on the RX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin when SYNC is clear or when BRG16 and BRGH are both not set. The data on the RX pin is sampled once when SYNC is set or when BRGH16 and BRGH are both set.

TABLE 18-1: BAUD RATE FORMULAS

| Configuration Bits |       | DDC/FUCADT Mada | Bourd Boto Formula  |                   |

|--------------------|-------|-----------------|---------------------|-------------------|

| SYNC               | BRG16 | BRGH            | BRG/EUSART Mode     | Baud Rate Formula |

| 0                  | 0     | 0               | 8-bit/Asynchronous  | Fosc/[64 (n + 1)] |

| 0                  | 0     | 1               | 8-bit/Asynchronous  | F000/[16 (n + 1)] |

| 0                  | 1     | 0               | 16-bit/Asynchronous | Fosc/[16 (n + 1)] |

| 0                  | 1     | 1               | 16-bit/Asynchronous |                   |

| 1                  | 0     | х               | 8-bit/Synchronous   | Fosc/[4 (n + 1)]  |

| 1                  | 1     | х               | 16-bit/Synchronous  |                   |

**Legend:** x = Don't care, n = value of SPBRGH:SPBRG register pair

| SLEEP | Enter | Sleep | mode |

|-------|-------|-------|------|

|       |       |       |      |

SLEEP Syntax: Operands: None  $00h \rightarrow WDT$ , Operation:  $0 \rightarrow WDT$  postscaler,  $1 \rightarrow \overline{TO}$  $0 \to \overline{PD}$ TO, PD Status Affected: Encoding: 0000 0000 0000 0011

Description: The Power-Down status bit  $(\overline{PD})$  is cleared. The Time-out status bit (TO)

> is set. Watchdog Timer and its postscaler are cleared.

The processor is put into Sleep mode

with the oscillator stopped.

Words: Cycles:

Q Cycle Activity:

| Q1     | Q2        | Q3      | Q4    |  |

|--------|-----------|---------|-------|--|

| Decode | No        | Process | Go to |  |

|        | operation | Data    | Sleep |  |

Example: SLEEP

> Before Instruction TO =

PD = ?

After Instruction

TO = 1+ PD =

† If WDT causes wake-up, this bit is cleared.

| SUBFWB Subtra | act f from W with Borr | ow |

|---------------|------------------------|----|

|---------------|------------------------|----|

SUBFWB Syntax: f {,d {,a}} Operands:  $0 \leq f \leq 255$  $d \in \left[0,1\right]$  $a \in [0,1]$

Operation:  $(W) - (f) - (\overline{C}) \rightarrow dest$ Status Affected: N, OV, C, DC, Z Encoding: 01da ffff ffff 0101

Subtract register 'f' and Carry flag Description: (borrow) from W (2's complement method). If 'd' is '0', the result is stored

in W. If 'd' is '1', the result is stored in

register 'f' (default).

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used

to select the GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See **Section 24.2.3** "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset

Mode" for details.

Words: 1 Cycles:

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example 1: SUBFWB REG, 1, 0

Before Instruction REG After Instruction

REG FF W 2 0 C Ν ; result is negative

Example 2: SUBFWB REG, 0, 0

Before Instruction

REG W 5 After Instruction 2 REG W

3 C 0 Ν 0

; result is positive Example 3: SUBFWB REG, 1, 0

Before Instruction

REG W 2 С ō After Instruction

REG 0 W C Z = 2 =

; result is zero =

Data

**FSR**

#### 24.2.2 EXTENDED INSTRUCTION SET

| ADD               | FSR         | Add Lite       | Add Literal to FSR                                                          |     |         |   |  |  |

|-------------------|-------------|----------------|-----------------------------------------------------------------------------|-----|---------|---|--|--|

| Synta             | ax:         | ADDFSR         | ADDFSR f, k                                                                 |     |         |   |  |  |

| Operands:         |             |                | $0 \le k \le 63$                                                            |     |         |   |  |  |

|                   |             | $f \in [0, 1,$ | 2]                                                                          |     |         |   |  |  |

| Oper              | ation:      | FSR(f) + l     | $k \rightarrow FSR($                                                        | f)  |         |   |  |  |

| Statu             | s Affected: | None           | None                                                                        |     |         |   |  |  |

| Enco              | ding:       | 1110           | 1000                                                                        | ffk | k kkk   | k |  |  |

| Description:      |             | 11.0000.11     | The 6-bit literal 'k' is added to the contents of the FSR specified by 'f'. |     |         |   |  |  |

| Words:            |             | 1              | 1                                                                           |     |         |   |  |  |

| Cycles:           |             | 1              | 1                                                                           |     |         |   |  |  |

| Q Cycle Activity: |             |                |                                                                             |     |         |   |  |  |

|                   | Q1          | Q2             | Q3                                                                          |     | Q4      |   |  |  |

|                   | Decode      | Read           | Proce                                                                       | SS  | Write t | 0 |  |  |

Example: ADDFSR 2, 23h

literal 'k'

Before Instruction

FSR2 = 03FFh

After Instruction

FSR2 = 0422h

| ADDULNK          | Add Lite                                                                                                                                                                                                                                                                                                                              | eral to FS           | SR2 and | Return |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|--------|

| Syntax:          | ADDULNK k                                                                                                                                                                                                                                                                                                                             |                      |         |        |

| Operands:        | $0 \le k \le 63$                                                                                                                                                                                                                                                                                                                      | 3                    |         |        |

| Operation:       | FSR2 + k                                                                                                                                                                                                                                                                                                                              | $A \rightarrow FSR2$ | ,       |        |

|                  | $(TOS) \to$                                                                                                                                                                                                                                                                                                                           | PC                   |         |        |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |                      |         |        |

| Encoding:        | 1110 1000 11kk kk                                                                                                                                                                                                                                                                                                                     |                      |         |        |

| Description:     | The 6-bit literal 'k' is added to the contents of FSR2. A RETURN is then executed by loading the PC with the TOS.  The instruction takes two cycles to execute; a NOP is performed during the second cycle.  This may be thought of as a special case of the ADDFSR instruction, where f = 3 (binary '11'); it operates only on FSR2. |                      |         |        |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                     |                      |         |        |

Q Cycle Activity:

Cycles:

| Q1 Q2       |                     | Q3   | Q4        |

|-------------|---------------------|------|-----------|

| Decode      | Decode Read         |      | Write to  |

| literal 'k' |                     | Data | FSR       |

| No No       |                     | No   | No        |

| Operation   | Operation Operation |      | Operation |

Example: ADDULNK 23h

Before Instruction

FSR2 = 03FFhPC = 0100h

After Instruction

FSR2 = 0422hPC = (TOS)

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction syntax then becomes: {label} instruction argument(s).

SUBFSR Subtract Literal from FSR

Syntax: SUBFSR f, k Operands:  $0 \le k \le 63$

$f \in [0, 1, 2]$

Status Affected: None

Encoding: 1110 1001 ffkk kkkk

Description: The 6-bit literal 'k' is subtracted from

The 6-bit literal 'k' is subtracted from the contents of the FSR specified

by 'f'.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1          | Q2   | Q3      | Q4          |  |

|-------------|------|---------|-------------|--|

| Decode      | Read | Process | Write to    |  |

| register 'f |      | Data    | destination |  |

Example: SUBFSR 2, 23h

Before Instruction

FSR2 = 03FFh

After Instruction

FSR2 = 03DCh

SUBULNK Subtract Literal from FSR2 and Return

Syntax: SUBULNK k

Operands:  $0 \le k \le 63$

Operation:  $FSR2 - k \rightarrow FSR2$ ,

$(TOS) \rightarrow PC$

Status Affected: None

Description:

**Encoding**: 1110 1001 11kk kkkk

contents of the FSR2. A RETURN is then executed by loading the PC with the TOS. The instruction takes two cycles to execute; a NOP is performed during the

The 6-bit literal 'k' is subtracted from the

second cycle.

This may be thought of as a special case of the SUBFSR instruction, where f=3 (binary

'11'); it operates only on FSR2.

Words: 1

Cycles: 2

Q Cycle Activity:

|   | Q1                  | Q1 Q2        |           | Q4          |  |

|---|---------------------|--------------|-----------|-------------|--|

|   | Decode Read         |              | Process   | Write to    |  |

|   |                     | register 'f' | Data      | destination |  |

| ſ | No No               |              | No        | No          |  |

|   | Operation Operation |              | Operation | Operation   |  |

Example: SUBULNK 23h

Before Instruction

FSR2 = 03FFhPC = 0100h

After Instruction

FSR2 = 03DChPC = (TOS)

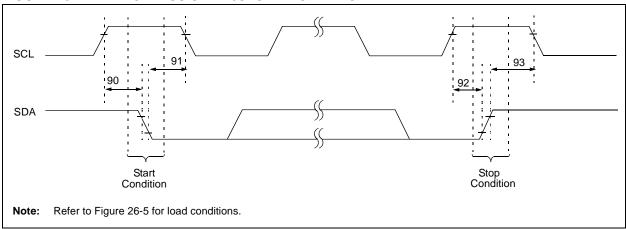

FIGURE 26-17: I<sup>2</sup>C™ BUS START/STOP BITS TIMING

TABLE 26-18: I<sup>2</sup>C™ BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characte        | ristic       | Min  | Max | Units | Conditions                                            |

|---------------|---------|-----------------|--------------|------|-----|-------|-------------------------------------------------------|

| 90            | Tsu:sta | Start Condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated Start condition            |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                                                       |

| 91            | THD:STA | Start Condition | 100 kHz mode | 4000 | _   | ns    | After this period, the first clock pulse is generated |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       |                                                       |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                                                       |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                                                       |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                                                       |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       |                                                       |

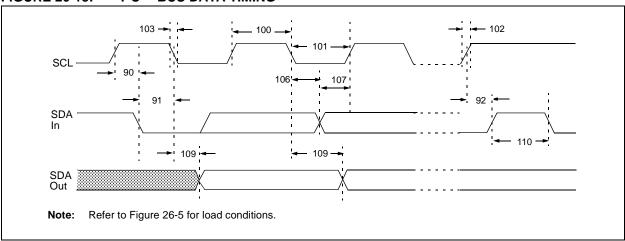

FIGURE 26-18: I<sup>2</sup>C™ BUS DATA TIMING

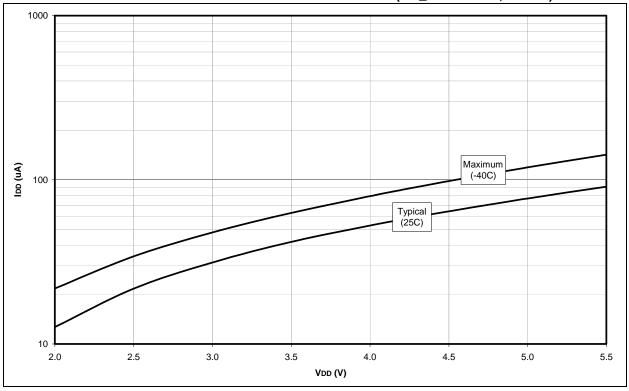

FIGURE 27-13: TYPICAL AND MAXIMUM IDD ACROSS VDD (RC\_RUN MODE, 31 kHz)

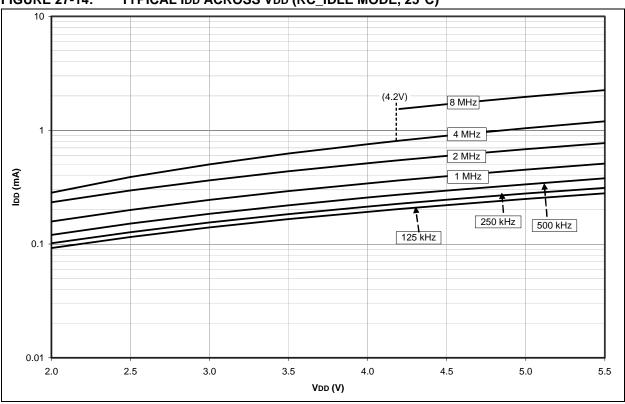

FIGURE 27-14: TYPICAL IDD ACROSS VDD (RC\_IDLE MODE, 25°C)

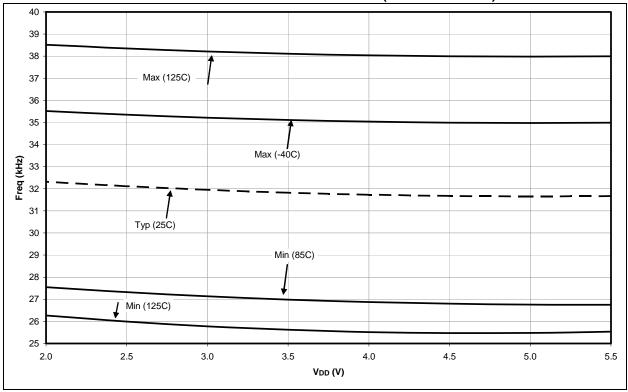

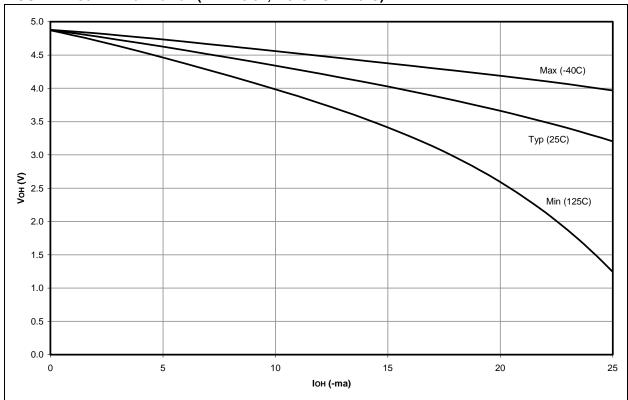

FIGURE 27-37: INTOSC FREQUENCY vs. VDD, TEMPERATURE (-40°C, +25°C, +85°C, +125°C)

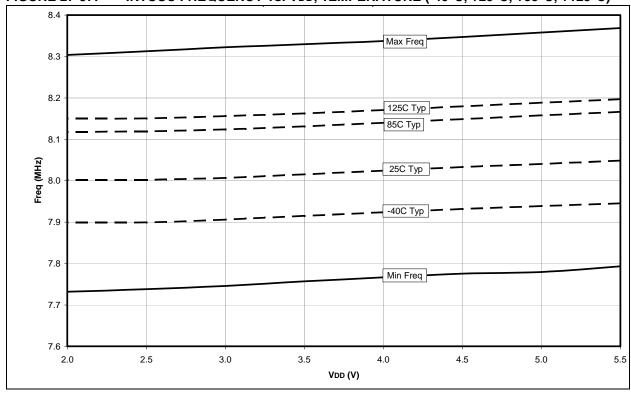

FIGURE 27-38: INTRC vs. VDD ACROSS TEMPERATURE (-40°C TO +125°C)