#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2525-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

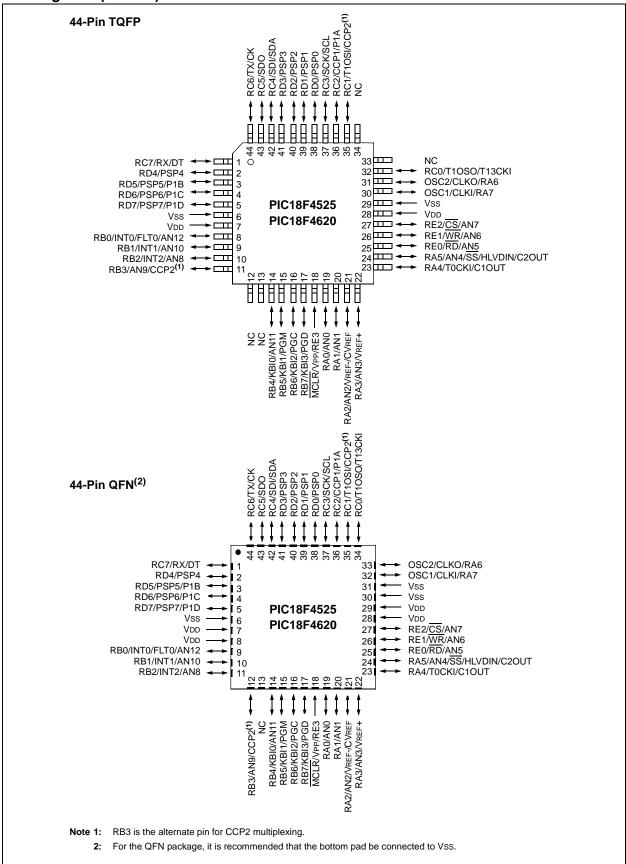

#### Pin Diagrams (Cont.'d)

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F2525 PIC18LF2525

- PIC18F2620 PIC18LF2620

- PIC18F4525 PIC18LF4525

- PIC18F4620 PIC18LF4620

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Enhanced Flash program memory. On top of these features, the PIC18F2525/2620/4525/4620 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

### 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2525/2620/4525/4620 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4%, of normal operation requirements.

- **On-the-Fly Mode Switching:** The powermanaged modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 26.0 "Electrical Characteristics" for values.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2525/2620/4525/4620 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O)

- Two External RC Oscillator modes with the same pin options as the External Clock modes

- An internal oscillator block which provides an 8 MHz clock and an INTRC source (approximately 31 kHz), as well as a range of 6 user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of 8 clock frequencies. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and Internal Oscillator modes, which allows clock speeds of up to 40 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz – all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

| TABLE 1-3: PIC18F4525/4620 PINOUT I/O DESCRIPTIONS (CONTINUED) |           |        |      |                 |                |                                                                                                                                                                                       |

|----------------------------------------------------------------|-----------|--------|------|-----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                       | Pi        | n Numb | ber  | Pin Buffer      |                | Description                                                                                                                                                                           |

|                                                                | PDIP      | QFN    | TQFP | Туре            | Туре           |                                                                                                                                                                                       |

|                                                                |           |        |      |                 |                | PORTD is a bidirectional I/O port or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when the PSP<br>module is enabled. |

| RD0/PSP0<br>RD0<br>PSP0                                        | 19        | 38     | 38   | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD1/PSP1<br>RD1<br>PSP1                                        | 20        | 39     | 39   | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD2/PSP2<br>RD2<br>PSP2                                        | 21        | 40     | 40   | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD3/PSP3<br>RD3<br>PSP3                                        | 22        | 41     | 41   | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD4/PSP4<br>RD4<br>PSP4                                        | 27        | 2      | 2    | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                             |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                             | 28        | 3      | 3    | I/O<br>I/O<br>O | ST<br>TTL<br>— | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                             | 29        | 4      | 4    | I/O<br>I/O<br>O | ST<br>TTL<br>— | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D                             | 30        | 5      | 5    | I/O<br>I/O<br>O | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                    |

| Legend: TTL = TTL c<br>ST = Schm<br>O = Outpu                  | itt Trigg |        |      | /IOS lev        |                |                                                                                                                                                                                       |

## TABLE 1-3: PIC18F4525/4620 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

3: For the QFN package, it is recommended that the bottom pad be connected to Vss.

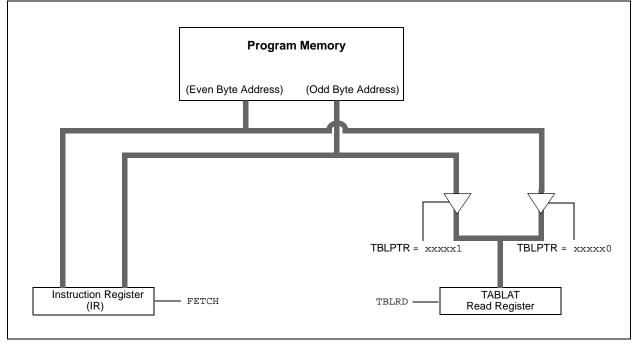

#### 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; Load TBLPTR with the base      |

|-----------|---------|-----------------|----------------------------------|

|           | MOVWF   | TBLPTRU         | ; address of the word            |

|           | MOVLW   | CODE_ADDR_HIGH  |                                  |

|           | MOVWF   | TBLPTRH         |                                  |

|           | MOVLW   | CODE_ADDR_LOW   |                                  |

|           | MOVWF   | TBLPTRL         |                                  |

| READ_WORD |         |                 |                                  |

|           | TBLRD*+ |                 | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; get data                       |

|           | MOVWF   | WORD_EVEN       |                                  |

|           | TBLRD*+ |                 | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; get data                       |

|           | MOVWF   | WORD_ODD        |                                  |

|           |         |                 |                                  |

NOTES:

| R-0        | R-0                             | R/W-0                            | R/W-0            | U-0               | R/W-1            | R/W-1            | R/W-1    |

|------------|---------------------------------|----------------------------------|------------------|-------------------|------------------|------------------|----------|

| IBF        | OBF                             | IBOV                             | PSPMODE          | —                 | TRISE2           | TRISE1           | TRISE0   |

| bit 7      |                                 |                                  |                  |                   |                  |                  | bit C    |

| Legend:    |                                 |                                  |                  |                   |                  |                  |          |

| R = Reada  | ble bit                         | W = Writable                     | bit              | U = Unimplen      | nented bit, read | d as '0'         |          |

| -n = Value | at POR                          | '1' = Bit is se                  |                  | '0' = Bit is clea |                  | x = Bit is unkr  | nown     |

|            |                                 |                                  |                  |                   |                  |                  |          |

| bit 7      | IBF: Input Bu                   | uffer Full Status                | bit              |                   |                  |                  |          |

|            |                                 | as been receiv<br>has been recei | •                | to be read by th  | ne CPU           |                  |          |

| bit 6      | <b>OBF:</b> Output              | Buffer Full Sta                  | tus bit          |                   |                  |                  |          |

|            |                                 |                                  | olds a previousl | y written word    |                  |                  |          |

|            | -                               | ut buffer has be                 |                  |                   |                  |                  |          |

| bit 5      | •                               |                                  |                  | Vicroprocessor    |                  |                  |          |

|            | 1 = A write or<br>0 = No overfl |                                  | previously input | t word has not b  | een read (must   | be cleared in so | oftware) |

| bit 4      | PSPMODE:                        | Parallel Slave I                 | Port Mode Sele   | ct bit            |                  |                  |          |

|            |                                 | Slave Port mod<br>purpose I/O mo | -                |                   |                  |                  |          |

| bit 3      | Unimplemer                      | nted: Read as                    | ·0'              |                   |                  |                  |          |

| bit 2      | TRISE2: RE                      | 2 Direction Cor                  | trol bit         |                   |                  |                  |          |

|            | 1 = Input                       |                                  |                  |                   |                  |                  |          |

| bit 1      | 0 = Output                      | 1 Direction Cor                  | stral hit        |                   |                  |                  |          |

| DILT       | 1 = Input                       | I Direction Cor                  |                  |                   |                  |                  |          |

|            | 0 = Output                      |                                  |                  |                   |                  |                  |          |

| bit 0      | TRISE0: RE                      | Direction Cor                    | trol bit         |                   |                  |                  |          |

|            | 1 = Input                       |                                  |                  |                   |                  |                  |          |

|            | 0 = Output                      |                                  |                  |                   |                  |                  |          |

#### REGISTER 9-1: TRISE REGISTER (40/44-PIN DEVICES ONLY)

## REGISTER 10-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0         | R/W-0                                                      | U-0                                 | R/W-0                               | R/W-0            | R/W-0           | R/W-0            | R/W-0    |

|---------------|------------------------------------------------------------|-------------------------------------|-------------------------------------|------------------|-----------------|------------------|----------|

| OSCFIF        | CMIF                                                       |                                     | EEIF                                | BCLIF            | HLVDIF          | TMR3IF           | CCP2IF   |

| bit 7         | ÷                                                          |                                     |                                     |                  | ÷               | •                | bit (    |

| Legend:       |                                                            |                                     |                                     |                  |                 |                  |          |

| R = Readable  | e bit                                                      | W = Writable                        | bit                                 | U = Unimplen     | nented bit, rea | d as '0'         |          |

| -n = Value at | POR                                                        | '1' = Bit is set                    |                                     | '0' = Bit is cle | ared            | x = Bit is unkr  | nown     |

| bit 7         | OSCFIF: Osc                                                | illator Fail Inte                   | rrupt Flag bit                      |                  |                 |                  |          |

|               | 1 = Device os<br>0 = Device cl                             |                                     | clock input has                     | changed to IN    | TOSC (must b    | be cleared in so | ftware)  |

| bit 6         | CMIF: Compa                                                | arator Interrupt                    | Flag bit                            |                  |                 |                  |          |

|               | •                                                          | tor input has c<br>tor input has n  | hanged (must l<br>ot changed        | be cleared in so | oftware)        |                  |          |

| bit 5         | Unimplemen                                                 | ted: Read as '                      | 0'                                  |                  |                 |                  |          |

| bit 4         | EEIF: Data EEPROM/Flash Write Operation Interrupt Flag bit |                                     |                                     |                  |                 |                  |          |

|               |                                                            |                                     | omplete (must<br>ot complete or     |                  |                 |                  |          |

| bit 3         | BCLIF: Bus C                                               | Collision Interru                   | pt Flag bit                         |                  |                 |                  |          |

|               |                                                            | llision occurred                    | l (must be clea<br>ed               | red in software  | )               |                  |          |

| bit 2         | HLVDIF: High                                               | /Low-Voltage                        | Detect Interrup                     | t Flag bit       |                 |                  |          |

|               |                                                            |                                     | lition occurred<br>lition has not o |                  | mined by VDII   | RMAG bit, HLVI   | DCON<7>) |

| bit 1         | TMR3IF: TMF                                                | R3 Overflow In                      | terrupt Flag bit                    |                  |                 |                  |          |

|               |                                                            | gister overflow<br>gister did not o | ed (must be cle<br>verflow          | eared in softwa  | re)             |                  |          |

| bit 0         | CCP2IF: CCF                                                | 2 Interrupt Fla                     | g bit                               |                  |                 |                  |          |

|               |                                                            |                                     | e occurred (mu<br>ire occurred      | st be cleared in | n software)     |                  |          |

|               |                                                            | register compa                      | are match occu                      |                  | leared in softw | vare)            |          |

|               | <u>PWM mode:</u><br>Unused in this                         | s mode.                             |                                     |                  |                 |                  |          |

#### 10.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1 and IPR2). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 10-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                | R/W-1                         | R/W-1              | R/W-1            | R/W-1             | R/W-1           | R/W-1           | R/W-1  |

|----------------------|-------------------------------|--------------------|------------------|-------------------|-----------------|-----------------|--------|

| PSPIP <sup>(1)</sup> | ADIP                          | RCIP               | TXIP             | SSPIP             | CCP1IP          | TMR2IP          | TMR1IP |

| bit 7                |                               | ·                  | •                |                   | •               |                 | bit (  |

| Legend:              |                               |                    |                  |                   |                 |                 |        |

| R = Readable         | e bit                         | W = Writable       | bit              | U = Unimpler      | nented bit, rea | d as '0'        |        |

| -n = Value at        |                               | '1' = Bit is set   |                  | '0' = Bit is cle  |                 | x = Bit is unkr | nown   |

| L:1. <b>7</b>        |                               |                    |                  |                   | :.(1)           |                 |        |

| bit 7                |                               | allel Slave Port F | kead/write into  | errupt Priority b | It'''           |                 |        |

|                      | 1 = High pri<br>0 = Low prior | •                  |                  |                   |                 |                 |        |

| bit 6                | -                             | Converter Interru  | ot Priority bit  |                   |                 |                 |        |

|                      | 1 = High pri                  |                    | pri              |                   |                 |                 |        |

|                      | 0 = Low price                 | •                  |                  |                   |                 |                 |        |

| bit 5                | RCIP: EUSA                    | ART Receive Int    | errupt Priority  | bit               |                 |                 |        |

|                      | 1 = High pri                  |                    |                  |                   |                 |                 |        |

|                      | 0 = Low price                 | •                  |                  |                   |                 |                 |        |

| bit 4                | TXIP: EUSA                    | RT Transmit Int    | errupt Priority  | bit               |                 |                 |        |

|                      | 1 = High pri                  |                    |                  |                   |                 |                 |        |

|                      | 0 = Low price                 | •                  |                  |                   |                 |                 |        |

| bit 3                |                               | ter Synchronous    | s Serial Port Ir | iterrupt Priority | bit             |                 |        |

|                      | 1 = High pri<br>0 = Low prior |                    |                  |                   |                 |                 |        |

| bit 2                | •                             | CP1 Interrupt Pri  | ority bit        |                   |                 |                 |        |

|                      | 1 = High pri                  | •                  | only bit         |                   |                 |                 |        |

|                      | 0 = Low price                 | •                  |                  |                   |                 |                 |        |

| bit 1                | TMR2IP: TM                    | IR2 to PR2 Mate    | ch Interrupt Pr  | iority bit        |                 |                 |        |

|                      | 1 = High pri                  | ority              |                  | -                 |                 |                 |        |

|                      | 0 = Low price                 | ority              |                  |                   |                 |                 |        |

| bit 0                | TMR1IP: TM                    | IR1 Overflow In    | terrupt Priority | bit               |                 |                 |        |

|                      | 1 = High pri                  |                    |                  |                   |                 |                 |        |

|                      | 0 = Low price                 | ority              |                  |                   |                 |                 |        |

Note 1: This bit is unimplemented on 28-pin devices and will read as '0'.

| R/W-1          | R/W-1                                | U-0                        | R/W-1             | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|----------------|--------------------------------------|----------------------------|-------------------|-------------------|------------------|-----------------|--------|

| OSCFIP         | CMIP                                 | —                          | EEIP              | BCLIP             | HLVDIP           | TMR3IP          | CCP2IP |

| oit 7          |                                      |                            |                   |                   |                  |                 | bit C  |

|                |                                      |                            |                   |                   |                  |                 |        |

| Legend:        |                                      |                            |                   |                   |                  |                 |        |

| R = Readable   | bit                                  | W = Writable               | bit               | -                 | nented bit, read | d as '0'        |        |

| n = Value at I | POR                                  | '1' = Bit is set           |                   | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |

| oit 7          | <b>OSCFIP:</b> Osc<br>1 = High prior | illator Fail Inter<br>ritv | rrupt Priority bi | it                |                  |                 |        |

|                | 0 = Low prior                        | ,                          |                   |                   |                  |                 |        |

| bit 6          | CMIP: Compa                          | arator Interrupt           | Priority bit      |                   |                  |                 |        |

|                | 1 = High prior $0 = Low prior$       |                            |                   |                   |                  |                 |        |

| bit 5          | Unimplement                          | ted: Read as '             | 0'                |                   |                  |                 |        |

| bit 4          | EEIP: Data El                        | EPROM/Flash                | Write Operation   | on Interrupt Prio | rity bit         |                 |        |

|                | 1 = High prior $0 = Low prior$       |                            |                   |                   |                  |                 |        |

| bit 3          | BCLIP: Bus C                         | Collision Interru          | pt Priority bit   |                   |                  |                 |        |

|                | 1 = High prior $0 = Low prior$       | •                          |                   |                   |                  |                 |        |

| bit 2          | HLVDIP: High                         | /Low-Voltage I             | Detect Interrup   | ot Priority bit   |                  |                 |        |

|                | 1 = High prior $0 = Low prior$       | •                          |                   |                   |                  |                 |        |

| bit 1          | TMR3IP: TMF                          | R3 Overflow Int            | errupt Priority   | bit               |                  |                 |        |

|                | 1 = High prior $0 = Low prior$       | •                          |                   |                   |                  |                 |        |

| bit 0          | <b>CCP2IP:</b> CCF<br>1 = High prior | 2 Interrupt Prie           | ority bit         |                   |                  |                 |        |

#### REGISTER 10-9: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

#### 10.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxIE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high-priority interrupt source.

#### 10.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 11.0 "Timer0 Module" for further details on the Timer0 module.

#### 10.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

## 10.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (see **Section 5.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 10-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| MOVWF  | W_TEMP              | ; W_TEMP is in virtual bank    |

|--------|---------------------|--------------------------------|

| MOVFF  | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF  | BSR, BSR_TEMP       | ; BSR_TMEP located anywhere    |

| ;      |                     |                                |

| ; USER | ISR CODE            |                                |

| ;      |                     |                                |

| MOVFF  | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF   | W_TEMP, W           | ; Restore WREG                 |

| MOVFF  | STATUS_TEMP, STATUS | ; Restore STATUS               |

|        |                     |                                |

EXAMPLE 10-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

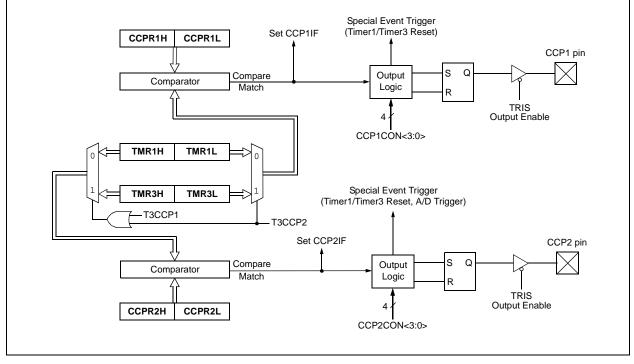

## 15.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 15.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

## TABLE 15-1:CCP MODE – TIMER<br/>RESOURCES

| CCP/ECCP Mode | Timer Resource   |

|---------------|------------------|

| Capture       | Timer1 or Timer3 |

| Compare       | Timer1 or Timer3 |

| PWM           | Timer2           |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 14-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 15-1 and Figure 15-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

#### 15.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (capture input, compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                                                                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                     |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare            | Capture            | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                              |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                          |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | PWM                | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

#### TABLE 15-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

Note 1: Includes standard and Enhanced PWM operation.

## 15.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCPx pin can be:

- driven high

- · driven low

- toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM3:CCPxM0). At the same time, the interrupt flag bit, CCPxIF, is set.

#### 15.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP2CON register will force    |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | the RB3 or RC1 compare output latch         |  |  |  |  |

|       | (depending on device configuration) to the  |  |  |  |  |

|       | default low level. This is not the PORTB or |  |  |  |  |

|       | PORTC I/O data latch.                       |  |  |  |  |

#### 15.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 15.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM3:CCPxM0 = 1010), the corresponding CCPx pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCPxIE bit is set.

#### 15.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCPxM3:CCPxM0 = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

The Special Event Trigger for CCP2 can also start an A/D conversion. In order to do this, the A/D converter must already be enabled.

## FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 17.4.14 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 17.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

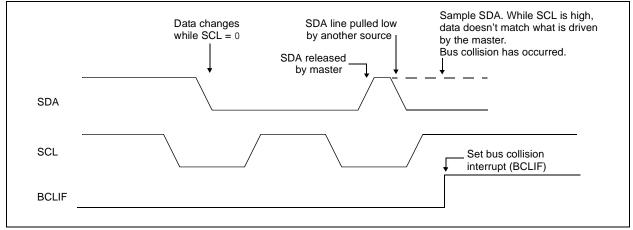

#### 17.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 17.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the  $I^2C$  port to its Idle state (Figure 17-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 17-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

## 19.2 Selecting and Configuring Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set. It also gives users the option to use an automatically determined acquisition time.

Acquisition time may be set with the ACQT2:ACQT0 bits (ADCON2<5:3>), which provides a range of 2 to 20 TAD. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

Manual acquisition is selected when ACQT2:ACQT0 = 000. When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This option is also the default Reset state of the ACQT2:ACQT0 bits and is compatible with devices that do not offer programmable acquisition times.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

## 19.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD (see parameter 130 for more information).

Table 19-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

| AD Clock S        | ource (TAD)           | Maximum Device Frequency |                                 |  |

|-------------------|-----------------------|--------------------------|---------------------------------|--|

| Operation         | Operation ADCS2:ADCS0 |                          | PIC18LF2X20/4X20 <sup>(4)</sup> |  |

| 2 Tosc            | 000                   | 2.86 MHz                 | 1.43 kHz                        |  |

| 4 Tosc            | 100                   | 5.71 MHz                 | 2.86 MHz                        |  |

| 8 Tosc            | 001                   | 11.43 MHz                | 5.72 MHz                        |  |

| 16 Tosc           | 101                   | 22.86 MHz                | 11.43 MHz                       |  |

| 32 Tosc           | 010                   | 40.0 MHz                 | 22.86 MHz                       |  |

| 64 Tosc           | 110                   | 40.0 MHz                 | 22.86 MHz                       |  |

| RC <sup>(3)</sup> | x11                   | 1.00 MHz <sup>(1)</sup>  | 1.00 MHz <sup>(2)</sup>         |  |

#### TABLE 19-1: TAD vs. DEVICE OPERATING FREQUENCIES

**Note 1:** The RC source has a typical TAD time of  $1.2 \ \mu s$ .

**2:** The RC source has a typical TAD time of 2.5  $\mu$ s.

- **3:** For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or the A/D accuracy may be out of specification.

- 4: Low-power (PIC18LFXXXX) devices only.

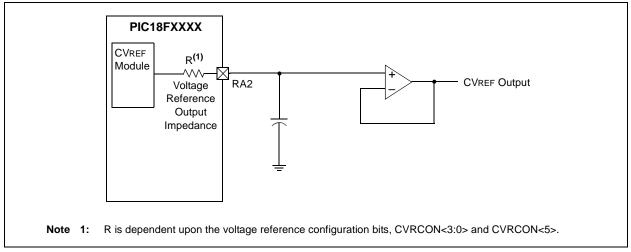

#### FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 21-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7                 | Bit 6                 | Bit 5   | Bit 4                                | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|---------|--------------------------------------|-------|-------|-------|-------|----------------------------|

| CVRCON | CVREN                 | CVROE                 | CVRR    | CVRSS                                | CVR3  | CVR2  | CVR1  | CVR0  | 51                         |

| CMCON  | C2OUT                 | C1OUT                 | C2INV   | C1INV                                | CIS   | CM2   | CM1   | CM0   | 51                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA D | ORTA Data Direction Control Register |       |       |       |       | 52                         |

Legend: Shaded cells are not used with the comparator voltage reference.

**Note 1:** PORTA pins are enabled based on oscillator configuration.

| Byte-oriented file register operations                                                                                                                                                                                                                                              | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                                                       |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                                               | ADDWF MYREG, W, B    |

| $      d = 0 \ \text{for result destination to be WREG register} \\      d = 1 \ \text{for result destination to be file register (f)} \\      a = 0 \ \text{to force Access Bank} \\      a = 1 \ \text{for BSR to select bank} \\      f = 8-bit \ \text{file register address} $ |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                                               |                      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                                                   |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                                                            | MOVFF MYREG1, MYREG2 |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                                                   |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                                                         |                      |

| f = 12-bit file register address                                                                                                                                                                                                                                                    |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                                               |                      |

| 15 1211 987 0                                                                                                                                                                                                                                                                       |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                                                       | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                                               |                      |

| Literal operations                                                                                                                                                                                                                                                                  |                      |

| 15 8 7 0                                                                                                                                                                                                                                                                            |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                                                  | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                                                           |                      |

| Control operations                                                                                                                                                                                                                                                                  |                      |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                                                    |                      |

| 15 8 7 0                                                                                                                                                                                                                                                                            |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                                                             | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                                                          |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                                              |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                                                          |                      |

| 15 8 7 0                                                                                                                                                                                                                                                                            |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                                                           | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                                                          |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                                              |                      |

| S = Fast bit                                                                                                                                                                                                                                                                        |                      |

| 15 11 10 0                                                                                                                                                                                                                                                                          |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                                                            | BRA MYFUNC           |

|                                                                                                                                                                                                                                                                                     |                      |

|                                                                                                                                                                                                                                                                                     |                      |

| 15 8 7 0<br>OPCODE n<7:0> (literal)                                                                                                                                                                                                                                                 | BC MYFUNC            |

| BTFSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit Test Fil                                          | le, Skip if Cl                     | ear             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------|-----------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BTFSC f, b                                            | {,a}                               |                 |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$ |                                    |                 |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | skip if (f <b>) = 0</b>                               |                                    |                 |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | None                                                  |                                    |                 |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1011 bbba ffff ffff                                   |                                    |                 |  |  |  |

| Description:<br>If bit 'b' in register 'f' is '0', then the nex<br>instruction is skipped. If bit 'b' is '0', the<br>the next instruction fetched during the<br>current instruction execution is discard<br>and a NOP is executed instead, making<br>this a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected<br>'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh).<br>See Section 24.2.3 "Byte-Oriented an<br>Bit-Oriented Instructions in Indexed |                                                       |                                    |                 |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                     | et Mode" for d                     | etalis.         |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1(2)                                                  |                                    |                 |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | by a                                                  | cles if skip and<br>2-word instruc |                 |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q2                                                    | Q3                                 | Q4              |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Read<br>register 'f'                                  | Process<br>Data                    | No<br>operation |  |  |  |

| lf skip:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                       | Data                               | operation       |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q2                                                    | Q3                                 | Q4              |  |  |  |

| No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                                    | No                                 | No              |  |  |  |

| operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation                                             | operation                          | operation       |  |  |  |

| If skip and followed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |                                    | -               |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q2                                                    | Q3                                 | Q4              |  |  |  |

| No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                                    | No                                 | No              |  |  |  |

| operation<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | operation<br>No                                       | operation<br>No                    | operation<br>No |  |  |  |