Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

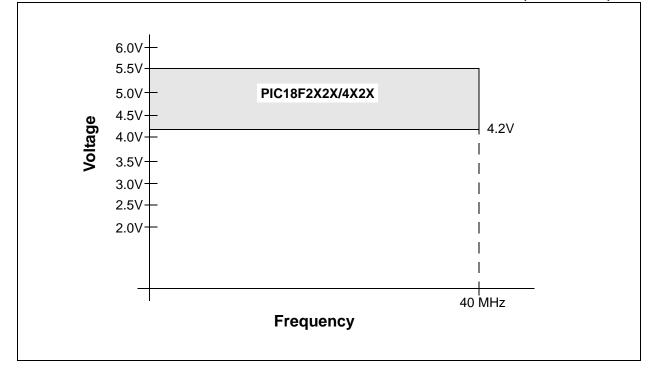

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2620-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

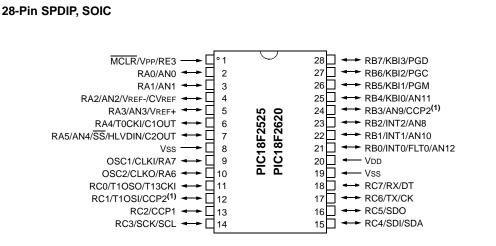

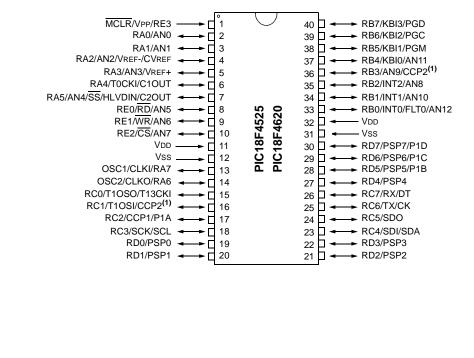

### **Pin Diagrams**

40-Pin PDIP

Note 1: RB3 is the alternate pin for CCP2 multiplexing.

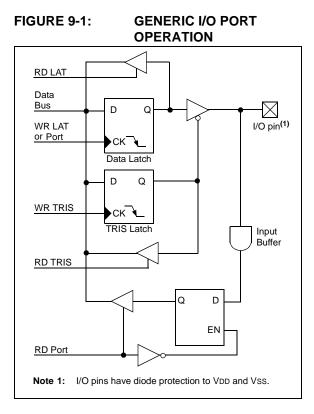

## 9.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 9-1.

## 9.1 PORTA, TRISA and LATA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 23.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA3:RA0 and RA5 as A/D converter inputs is selected by clearing or setting the control bits in the ADCON1 register (A/D Control Register 1).

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register. To use RA3:RA0 as digital inputs, it is also necessary to turn off the comparators.

| Note: | On a Power-on Reset, RA5 and RA3:RA0          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels. All PORTA pins have full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| EXAMPL  | E 9-1: |   | INITIALIZING PORTA        |

|---------|--------|---|---------------------------|

| CLRF 1  | PORTA  | ; | Initialize PORTA by       |

|         |        | ; | clearing output           |

|         |        | ; | data latches              |

| CLRF 1  | LATA   | ; | Alternate method          |

|         |        | ; | to clear output           |

|         |        | ; | data latches              |

| MOVLW   | 07h    | ; | Configure A/D             |

| MOVWF 2 | ADCON1 | ; | for digital inputs        |

| MOVWF   | 07h    | ; | Configure comparators     |

| MOVWF   | CMCON  | ; | for digital input         |

| MOVLW   | 0CFh   | ; | Value used to             |

|         |        | ; | initialize data           |

|         |        | ; | direction                 |

| MOVWF   | TRISA  | ; | Set RA<7:6,3:0> as inputs |

|         |        | ; | RA<5:4> as outputs        |

## 9.4 PORTD, TRISD and LATD Registers

| Note: | PORTD    | is | only | available | on | 40/44-pin |

|-------|----------|----|------|-----------|----|-----------|

|       | devices. |    |      |           |    |           |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

Three of the PORTD pins are multiplexed with outputs P1B, P1C and P1D of the Enhanced CCP module. The operation of these additional PWM output pins is covered in greater detail in Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

Note: On a Power-on Reset, these pins are configured as digital inputs.

PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See **Section 9.6** "**Parallel Slave Port**" for additional information on the Parallel Slave Port (PSP).

| Note: | When the Enhanced PWM mode is used        |

|-------|-------------------------------------------|

|       | with either dual or quad outputs, the PSP |

|       | functions of PORTD are automatically      |

|       | disabled.                                 |

#### EXAMPLE 9-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by<br>; clearing output |

|-------|-------|--------------------------------------------|

| CLRF  | LATD  | ; data latches<br>; Alternate method       |

| CLRF  | LAID  |                                            |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 0CFh  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISD | ; Set RD<3:0> as inputs                    |

|       |       | ; RD<5:4> as outputs                       |

|       |       | ; RD<7:6> as inputs                        |

|       |       |                                            |

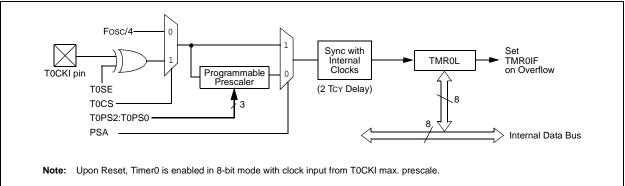

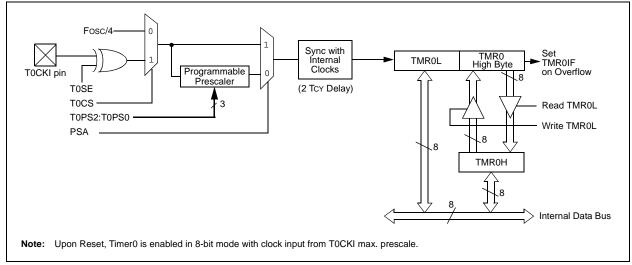

## 11.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected with the TOCS bit (TOCON<5>). In Timer mode (TOCS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 11.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI/C1OUT. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

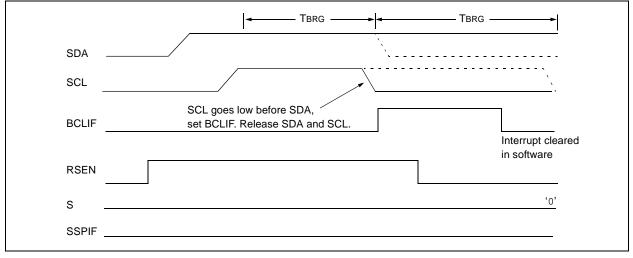

### 11.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 11-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

### FIGURE 11-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

### FIGURE 11-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

### REGISTER 16-3: ECCP1AS: ECCP AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0        | R/W-0                     | R/W-0              | R/W-0            | R/W-0             | R/W-0               | R/W-0                 | R/W-0                 |

|--------------|---------------------------|--------------------|------------------|-------------------|---------------------|-----------------------|-----------------------|

| ECCPASE      | ECCPAS2                   | ECCPAS1            | ECCPAS0          | PSSAC1            | PSSAC0              | PSSBD1 <sup>(1)</sup> | PSSBD0 <sup>(1)</sup> |

| oit 7        |                           |                    |                  |                   |                     | 4                     | bit 0                 |

|              |                           |                    |                  |                   |                     |                       |                       |

| Legend:      |                           |                    |                  |                   |                     |                       |                       |

| R = Readab   | le bit                    | W = Writable       | bit              | U = Unimplem      | nented bit, read    | d as '0'              |                       |

| -n = Value a | t POR                     | '1' = Bit is set   |                  | '0' = Bit is clea | ared                | x = Bit is unkr       | nown                  |

|              |                           |                    |                  |                   |                     |                       |                       |

| bit 7        | ECCPASE: E                | CCP Auto-Shu       | tdown Event S    | tatus bit         |                     |                       |                       |

|              |                           |                    |                  | outputs are in    | shutdown stat       | e                     |                       |

|              |                           | tputs are opera    | •                |                   |                     |                       |                       |

| oit 6-4      |                           |                    |                  | wn Source Sele    | ect dits            |                       |                       |

|              |                           | r Comparator       |                  | or 2              |                     |                       |                       |

|              |                           | r Comparator 2     |                  |                   |                     |                       |                       |

|              | 101 = FLT00<br>100 = FLT0 | or Comparator      |                  |                   |                     |                       |                       |

|              |                           | Comparator 1 of    | or 2             |                   |                     |                       |                       |

|              |                           | arator 2 output    | <i></i>          |                   |                     |                       |                       |

|              |                           | arator 1 output    |                  |                   |                     |                       |                       |

|              |                           | hutdown is disa    | abled            |                   |                     |                       |                       |

| bit 3-2      | PSSAC1:PS                 | SAC0: Pins A a     | nd C Shutdow     | n State Control   | bits                |                       |                       |

|              | 1x = Pins A a             | and C are tri-st   | ate (40/44-pin ( | devices);         |                     |                       |                       |

|              |                           | utput is tri-state |                  |                   |                     |                       |                       |

|              | 01 = Drive Pi             | ins A and C to     | '1'              |                   |                     |                       |                       |

|              | 00 = Drive Pi             | ins A and C to     | '0'              |                   |                     |                       |                       |

| bit 1-0      | PSSBD1:PSS                | SBD0: Pins B a     | nd D Shutdow     | n State Control   | bits <sup>(1)</sup> |                       |                       |

|              | 1x = Pins Ba              | and D tri-state    |                  |                   |                     |                       |                       |

|              | 01 = Drive Pi             | ins B and D to     | '1'              |                   |                     |                       |                       |

|              | 00 = Drive P              |                    | (a)              |                   |                     |                       |                       |

Note 1: Unimplemented on 28-pin devices; bits read as '0'.

## 17.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>) and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL

(SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP status register (SSPSTAT) indicates the various status conditions.

| Note: | The SSPBUF regis          | ster cannot be | used | vith |  |  |  |

|-------|---------------------------|----------------|------|------|--|--|--|

|       | read-modify-write         | instructions   | such | as   |  |  |  |

|       | BCF, BTFSC and COMF, etc. |                |      |      |  |  |  |

Note: To avoid lost data in Master mode, a read of the SSPBUF must be performed to clear the Buffer Full (BF) detect bit (SSPSTAT<0>) between each transmission.

### EXAMPLE 17-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been received (transmit complete)? |

|------|-------|-------------|----------------------------------------------|

|      | BRA   | LOOP        | ;No                                          |

|      | MOVF  | SSPBUF, W   | ;WREG reg = contents of SSPBUF               |

|      | MOVWF | RXDATA      | ;Save in user RAM, if data is meaningful     |

|      | MOVF  | TXDATA, W   | ;W reg = contents of TXDATA                  |

|      | MOVWF | SSPBUF      | ;New data to xmit                            |

| R/W-0         | R/W-0                                                                                                 | R/W-0                                                                       | R/W-0                                                                              | R/W-0                                                  | R/W-0                                     | R/W-0            | R/W-0          |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|------------------|----------------|--|--|--|

| WCOL          | SSPOV                                                                                                 | SSPEN <sup>(1)</sup>                                                        | CKP                                                                                | SSPM3                                                  | SSPM2                                     | SSPM1            | SSPM0          |  |  |  |

| bit 7         |                                                                                                       |                                                                             |                                                                                    |                                                        |                                           |                  | bit            |  |  |  |

| Lonondi       |                                                                                                       |                                                                             |                                                                                    |                                                        |                                           |                  |                |  |  |  |

| Legend:       |                                                                                                       |                                                                             | .,                                                                                 |                                                        |                                           |                  |                |  |  |  |

| R = Readabl   |                                                                                                       | W = Writable k                                                              | Dit                                                                                | -                                                      | nented bit, read                          |                  |                |  |  |  |

| -n = Value at | t POR                                                                                                 | '1' = Bit is set                                                            |                                                                                    | '0' = Bit is clea                                      | ared                                      | x = Bit is unkr  | nown           |  |  |  |

| bit 7         | WCOL: Write                                                                                           | e Collision Detec                                                           | t bit                                                                              |                                                        |                                           |                  |                |  |  |  |

|               | In Master Tra                                                                                         |                                                                             |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               |                                                                                                       | to the SSPBUF                                                               |                                                                                    |                                                        |                                           | nditions were i  | not valid for  |  |  |  |

|               |                                                                                                       | sion to be starte                                                           | d (must be cl                                                                      | eared in softwa                                        | re)                                       |                  |                |  |  |  |

|               | 0 = No  collis                                                                                        |                                                                             |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | In Slave Tran                                                                                         | PBUF register is                                                            | written while                                                                      | it is still transm                                     | itting the previo                         | ous word (mus    | t he cleared i |  |  |  |

|               | software                                                                                              |                                                                             |                                                                                    |                                                        | intering the provide                      |                  |                |  |  |  |

|               | 0 = No collis                                                                                         | ion                                                                         |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               |                                                                                                       | ode (Master or S                                                            | <u>Slave modes)</u>                                                                | <u>:</u>                                               |                                           |                  |                |  |  |  |

|               | This is a "dor                                                                                        | n't care" bit.                                                              |                                                                                    |                                                        |                                           |                  |                |  |  |  |

| bit 6         | SSPOV: Receive Overflow Indicator bit                                                                 |                                                                             |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | In Receive m                                                                                          |                                                                             |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | 1 = A byte is software                                                                                | s received while                                                            | the SSPBUF                                                                         | register is still h                                    | olding the prev                           | ious byte (mus   | t be cleared i |  |  |  |

|               | 0 = No overf                                                                                          | /                                                                           |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | In Transmit n                                                                                         | node:                                                                       |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               |                                                                                                       | n't care" bit in Tra                                                        | ansmit mode.                                                                       |                                                        |                                           |                  |                |  |  |  |

| bit 5         | SSPEN: Mas                                                                                            | ster Synchronous                                                            | s Serial Port E                                                                    | Enable bit <sup>(1)</sup>                              |                                           |                  |                |  |  |  |

|               |                                                                                                       | the serial port ar                                                          |                                                                                    |                                                        | CL pins as the                            | serial port pins | i              |  |  |  |

|               | 0 = Disables                                                                                          | serial port and c                                                           | onfigures the                                                                      | se pins as I/O p                                       | oort pins                                 |                  |                |  |  |  |

| bit 4         | CKP: SCK R                                                                                            | elease Control b                                                            | oit                                                                                |                                                        |                                           |                  |                |  |  |  |

|               | In Slave mod                                                                                          |                                                                             |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | 1 = Releases                                                                                          |                                                                             |                                                                                    |                                                        | ture time e                               |                  |                |  |  |  |

|               | In Master mo                                                                                          | ock low (clock str                                                          | etch), used to                                                                     | o ensure data se                                       | etup time                                 |                  |                |  |  |  |

|               | Unused in th                                                                                          |                                                                             |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               |                                                                                                       |                                                                             |                                                                                    |                                                        | (0)                                       |                  |                |  |  |  |

| bit 3-0       | SSPM3:SSP                                                                                             | M0: Master Svn                                                              | chronous Ser                                                                       | ial Port Mode S                                        | elect bits <sup>(2)</sup>                 |                  |                |  |  |  |

| bit 3-0       |                                                                                                       | <b>M0:</b> Master Syn<br>Slave mode, 10-b                                   |                                                                                    |                                                        |                                           | enabled          |                |  |  |  |

| bit 3-0       | $1111 = I^2 C S$<br>$1110 = I^2 C S$                                                                  | Slave mode, 10-b<br>Slave mode, 7-bi                                        | oit address wi<br>t address with                                                   | th Start and Ston<br>Start and Stop                    | p bit interrupts<br>bit interrupts e      |                  |                |  |  |  |

| bit 3-0       | $1111 = I^2CS$<br>$1110 = I^2CS$<br>$1011 = I^2CF$                                                    | Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Contro                     | oit address wi<br>t address with<br>lled Master m                                  | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |  |  |  |

| bit 3-0       | $1111 = I^{2}C S$<br>$1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C N$                      | Blave mode, 10-b<br>Blave mode, 7-bi<br>Firmware Contro<br>Master mode, clo | bit address wi<br>t address with<br>lled Master m<br>lock = FOSC/(4                | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |  |  |  |

| bit 3-0       | $1111 = I^{2}C S$<br>$1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C N$<br>$0111 = I^{2}C S$ | Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Contro                     | bit address wi<br>t address with<br>lled Master m<br>lock = Fosc/(4<br>bit address | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |  |  |  |

## REGISTER 17-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

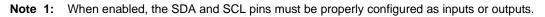

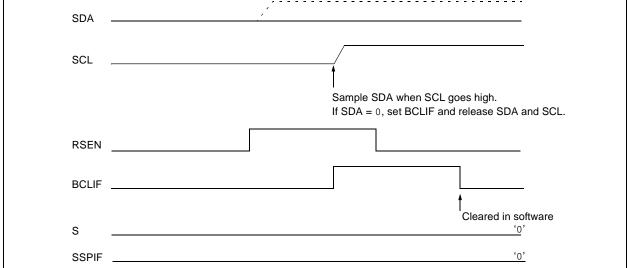

#### 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

FIGURE 17-29:

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 17-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 17-30: **BUS COLLISION DURING REPEATED START CONDITION (CASE 2)**

### REGISTER 23-6: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

|            |                    |                              |               |                    | -                |            |       |

|------------|--------------------|------------------------------|---------------|--------------------|------------------|------------|-------|

| U-0        | U-0                | U-0                          | U-0           | R/C-1              | R/C-1            | R/C-1      | R/C-1 |

| _          | —                  | —                            | —             | CP3 <sup>(1)</sup> | CP2              | CP1        | CP0   |

| bit 7      |                    |                              |               |                    |                  |            | bit 0 |

|            |                    |                              |               |                    |                  |            |       |

| Legend:    |                    |                              |               |                    |                  |            |       |

| R = Readal | ble bit            | C = Clearable                | bit           | U = Unimpler       | mented bit, read | as '0'     |       |

| -n = Value | when device is unp | programmed                   |               | u = Unchang        | ed from program  | nmed state |       |

|            |                    |                              |               |                    |                  |            |       |

| bit 7-4    |                    | ted: Read as '               | )'            |                    |                  |            |       |

| bit 3      | CP3: Code Pr       | rotection bit <sup>(1)</sup> |               |                    |                  |            |       |

|            |                    | 06000-007FFF                 | <i>,</i> .    |                    |                  |            |       |

|            | 0 = Block 3 (0)    | 06000-007FFF                 | h) code-prote | ected              |                  |            |       |

| bit 2      | CP2: Code Pr       | rotection bit                |               |                    |                  |            |       |

|            |                    | 04000-005FFF                 | <i>,</i> .    |                    |                  |            |       |

|            |                    | 04000-005FFF                 | h) code-prote | ected              |                  |            |       |

| bit 1      | CP1: Code Pr       |                              |               |                    |                  |            |       |

|            | •                  | 02000-003FFF                 | <i>'</i> .    |                    |                  |            |       |

|            |                    | 02000-003FFF                 | h) code-prote | ected              |                  |            |       |

| bit 0      | CP0: Code Pr       |                              | <b>.</b>      |                    |                  |            |       |

|            |                    | 00800-001FFF                 | <i>,</i> .    |                    |                  |            |       |

|            | 0 = Block 0 (0)    | 00800-001FFF                 | m code-prote  | ected              |                  |            |       |

Note 1: Unimplemented in PIC18FX525 devices; maintain this bit set.

### REGISTER 23-7: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1 | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| CPD   | СРВ   | —   | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:                |                   |                                     |  |

|------------------------|-------------------|-------------------------------------|--|

| R = Readable bit       | C = Clearable bit | U = Unimplemented bit, read as '0'  |  |

| -n = Value when device | is unprogrammed   | u = Unchanged from programmed state |  |

| bit 7                  | CPD: Data EEPROM Code Protection bit                                                                                        |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                        | 1 = Data EEPROM not code-protected                                                                                          |

|                        | 0 = Data EEPROM code-protected                                                                                              |

| bit 6                  | CPB: Boot Block Code Protection bit                                                                                         |

|                        | <ul><li>1 = Boot block (000000-0007FFh) not code-protected</li><li>0 = Boot block (000000-0007FFh) code-protected</li></ul> |

| <b>h</b> :+ <b>C</b> O | Unimplemented, Dood op (0)                                                                                                  |

bit 5-0 Unimplemented: Read as '0'

## 24.0 INSTRUCTION SET SUMMARY

PIC18F2525/2620/4525/4620 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions, for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

## 24.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- **Bit-oriented** operations

- Literal operations

- Control operations

The PIC18 instruction set summary in Table 24-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 24-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 24-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The instruction set summary, shown in Table 24-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

Section 24.1.1 "Standard Instruction Set" provides a description of each instruction.

## 24.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB<sup>®</sup> IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18F2525/2620/4525/4620 family of devices. This includes the MPLAB C18 C compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- A command line option

- · A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

26.2

## DC Characteristics: Power-Down and Supply Current PIC18F2525/2620/4525/4620 (Industrial) PIC18LF2525/2620/4525/4620 (Industrial) (Continued)

| PIC18LF2     | 5 <b>25/2620/4525/4620</b><br>rial)          |     | -   | rating (<br>perature |                       | ss otherwise sta<br>≤ +85°C for indu                                                     | -                |

|--------------|----------------------------------------------|-----|-----|----------------------|-----------------------|------------------------------------------------------------------------------------------|------------------|

|              | 2 <b>5/2620/4525/4620</b><br>rial, Extended) |     | -   | rating (<br>perature | $-40^{\circ}C \le TA$ | ss otherwise sta<br>$\leq +85^{\circ}$ C for indus<br>$\leq +125^{\circ}$ C for extended | strial           |

| Param<br>No. | Device                                       | Тур | Max | Units                | Conditions            |                                                                                          | ns               |

| D025L        | Timer1 Oscillator                            | 4.5 | 9.0 | μΑ                   | -40°C <b>(3)</b>      |                                                                                          |                  |

| (∆IOSCB)     |                                              | 0.9 | 1.6 | μΑ                   | -10°C                 | VDD = 2.0V                                                                               | 32 kHz on Timer1 |

|              |                                              | 0.9 | 1.6 | μA                   | +25°C                 | VDD = 2.0V                                                                               | 32 KHZ UN NINEN  |

|              |                                              | 0.9 | 1.8 | μA                   | +85°C                 |                                                                                          |                  |

|              |                                              | 4.8 | 10  | μA                   | -40°C <sup>(3)</sup>  |                                                                                          |                  |

|              |                                              | 1.0 | 2.0 | μA                   | -10°C                 | VDD = 3.0V                                                                               | 32 kHz on Timer1 |

|              |                                              | 1.0 | 2.0 | μA                   | +25°C                 | VDD = 3.0V                                                                               | SZ KHZ UN TIMEN  |

|              |                                              | 1.0 | 2.6 | μA                   | +85°C                 |                                                                                          |                  |

|              |                                              | 6.0 | 11  | μA                   | -40°C <sup>(3)</sup>  |                                                                                          |                  |

|              |                                              | 1.6 | 4.0 | μΑ                   | -10°C                 | VDD = 5.0V                                                                               | 32 kHz on Timer1 |

|              |                                              | 1.6 | 4.0 | μΑ                   | +25°C                 | VDD = 5.0V                                                                               |                  |

|              |                                              | 1.6 | 4.0 | μΑ                   | +85°C                 |                                                                                          |                  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD or Vss;

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

**3:** When operation below -10°C is expected, use T1OSC High-Power mode, where LPT1OSC (CONFIG3H<2>) = 0. When operation will always be above -10°C, then the low-power Timer1 oscillator may be selected.

4: BOR and HLVD enable internal band gap reference. With both modules enabled, current consumption will be less than the sum of both specifications.

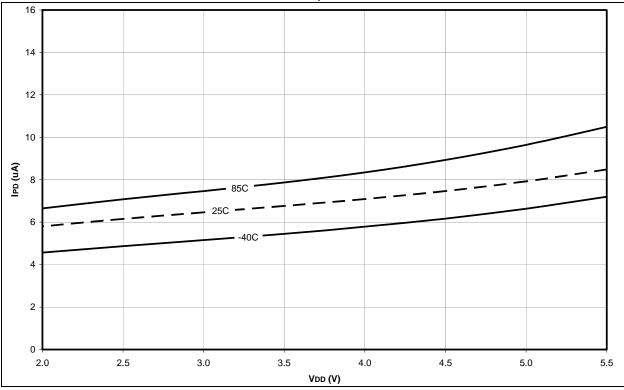

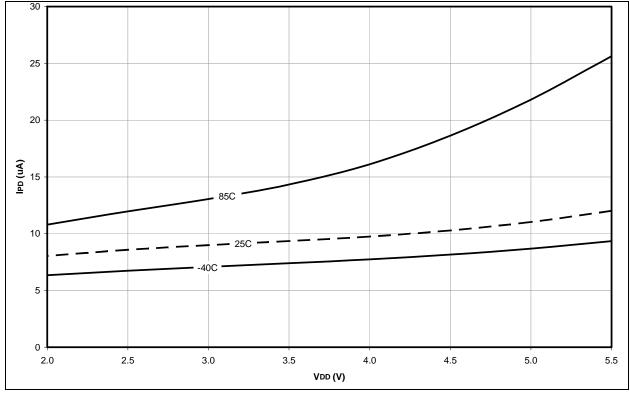

## FIGURE 27-6: TYPICAL T1OSC DELTA CURRENT vs. VDD ACROSS TEMP. (DEVICE IN SLEEP, T1OSC IN HIGH-POWER MODE)

## FIGURE 27-7: MAXIMUM T1OSC DELTA CURRENT vs. VDD ACROSS TEMP. (DEVICE IN SLEEP, T1OSC IN HIGH-POWER MODE)

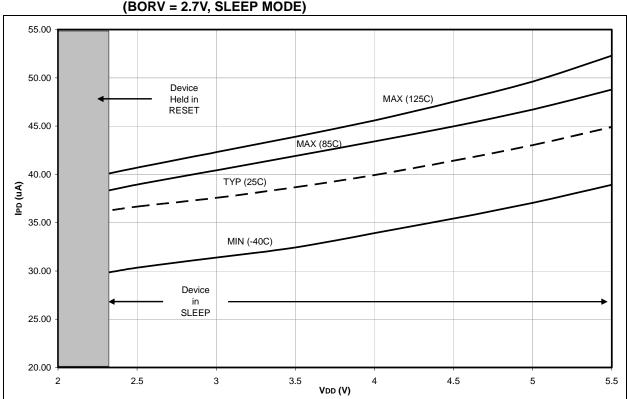

FIGURE 27-8: TYPICAL BOR DELTA CURRENT vs. VDD ACROSS TEMP. (BORV = 2.7V, SLEEP MODE)

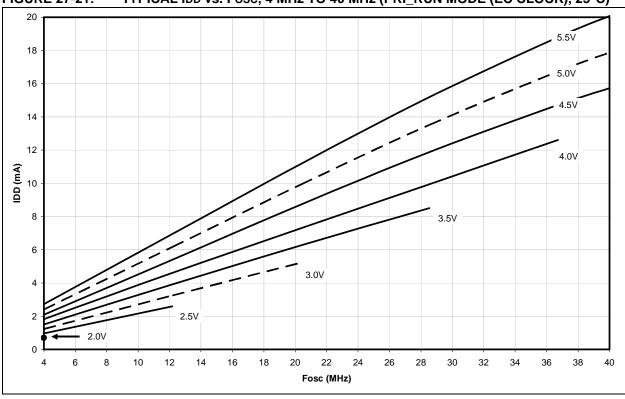

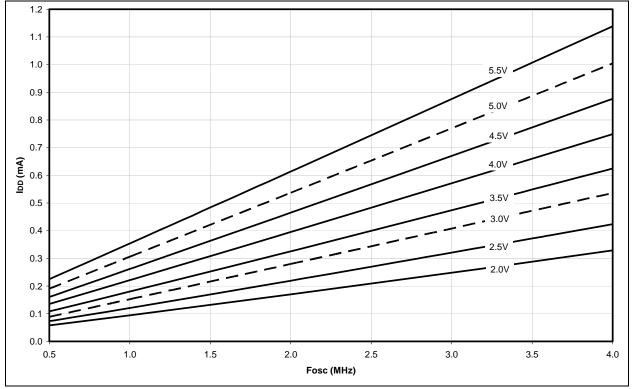

FIGURE 27-21: TYPICAL IDD vs. Fosc, 4 MHz TO 40 MHz (PRI\_RUN MODE (EC CLOCK), 25°C)

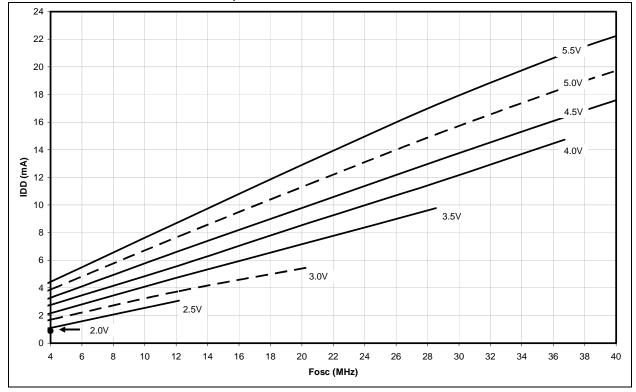

FIGURE 27-22: MAXIMUM IDD vs. Fosc, 4 MHz TO 40 MHz (PRI\_RUN MODE (EC CLOCK), -40°C TO +125°C)

#### Sleep

| OSC1 and OSC2 Pin States                          |

|---------------------------------------------------|

| Software Simulator (MPLAB SIM)                    |

| Special Event Trigger. See Compare (ECCP Mode).   |

| Special Event Trigger. See Compare (ECCP Module). |

| Special Features of the CPU                       |

| Special Function Registers                        |

| Map62                                             |

| SPI Mode (MSSP)                                   |

| Associated Registers169                           |

| Bus Mode Compatibility169                         |

| Effects of a Reset 169                            |

| Enabling SPI I/O165                               |

| Master Mode166                                    |

| Master/Slave Connection165                        |

| Operation164                                      |

| Operation in Power-Managed Modes                  |

| Serial Clock161                                   |

| Serial Data In161                                 |

| Serial Data Out161                                |

| Slave Mode167                                     |

| Slave Select161                                   |

| Slave Select Synchronization167                   |

| SPI Clock166                                      |

| Typical Connection165                             |

| SS161                                             |

| SSPOV191                                          |

| SSPOV Status Flag191                              |

| SSPSTAT Register                                  |

| R/W Bit174, 175                                   |

| Stack Full/Underflow Resets                       |

| Standard Instructions                             |

| STATUS Register                                   |

| SUBFSR                                            |

| SUBFWB                                            |

| SUBLW                                             |

| SUBULNK                                           |

| SUBWF                                             |

| SUBWFB                                            |

| SWAPF                                             |

| т                                                 |

|                                        | 50  |

|----------------------------------------|-----|

| Table Reads/Table Writes               |     |

| TBLRD                                  | 305 |

| TBLWT                                  | 306 |

| Time-out in Various Situations (table) | 45  |

| Timer0                                 | 123 |

| Associated Registers                   | 125 |

| Operation                              | 124 |

| Overflow Interrupt                     |     |

| Prescaler                              | 125 |

| Prescaler Assignment (PSA Bit)         |     |

| Prescaler Select (T0PS2:T0PS0 Bits)    |     |

| Prescaler. See Prescaler, Timer0.      |     |

| Reads and Writes in 16-Bit Mode        |     |

| Source Edge Select (T0SE Bit)          | 124 |

| Source Select (T0CS Bit)               |     |

| Switching Prescaler Assignment         |     |

| Timer1                                 |     |

| 16-Bit Read/Write Mode                 |     |

| Associated Registers                   |     |

| Interrupt                              |     |

| Operation                              |     |

| Oscillator                             |     |

|                                        | ,   |

| Layout Considerations                  |     |

| Low-Power Option                       | 129 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 127                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resetting, Using the CCP Special Event Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 130                                                                                                                                                    |

| Special Event Trigger (ECCP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 148                                                                                                                                                    |

| TMR1H Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

| TMR1L Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

| Use as a Real-Time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

| Timer2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                        |

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |

| Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |

| Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 134                                                                                                                                                    |

| PR2 Register1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44, 149                                                                                                                                                |

| TMR2 to PR2 Match Interrupt1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44, 149                                                                                                                                                |

| Timer3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                        |

| 16-Bit Read/Write Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                        |

| Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                        |

| Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| Overflow Interrupt1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        |