Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 64KB (32K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 1K x 8                                                                   |

| RAM Size                   | 3.8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 13x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4620-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                         | Pi   | n Numb | ber  | Pin      | Buffer | Description                                                                                                                                      |

|----------------------------------|------|--------|------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                         | PDIP | QFN    | TQFP | Туре     | Туре   | Description                                                                                                                                      |

| MCLR/VPP/RE3<br>MCLR             | 1    | 18     | 18   | I        | ST     | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.            |

| VPP                              |      |        |      | Р        |        | Programming voltage input.                                                                                                                       |

| RE3                              |      |        |      | Ι        | ST     | Digital input.                                                                                                                                   |

| OSC1/CLKI/RA7<br>OSC1            | 13   | 32     | 30   | I        | ST     | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode; |

| CLKI                             |      |        |      | I        | CMOS   | analog otherwise.<br>External clock source input. Always associated with<br>pin function OSC1. (See related OSC1/CLKI,<br>OSC2/CLKO pins.)       |

| RA7                              |      |        |      | I/O      | TTL    | General purpose I/O pin.                                                                                                                         |

| OSC2/CLKO/RA6<br>OSC2            | 14   | 33     | 31   | 0        | _      | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                |

| CLKO                             |      |        |      | 0        | _      | In RC mode, OSC2 pin outputs CLKO which has 1/4 the frequency of OSC1 and denotes                                                                |

| RA6                              |      |        |      | I/O      | TTL    | the instruction cycle rate.<br>General purpose I/O pin.                                                                                          |

| Legend: TTL = TTL o<br>ST = Schm | •    | •      |      | /IOS lev |        | CMOS = CMOS compatible input or output<br>= Input                                                                                                |

#### **TABLE 1-3:** PIC18F4525/4620 PINOUT I/O DESCRIPTIONS

Ρ = Power

O = Output Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

3: For the QFN package, it is recommended that the bottom pad be connected to Vss.

| Register | Ар   | plicabl | e Devi | ces  | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

|----------|------|---------|--------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|

| TOSU     | 2525 | 2620    | 4525   | 4620 | 0 0000                             | 0 0000                                                           | 0 uuuu <b>(3)</b>               |  |

| TOSH     | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |  |

| TOSL     | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu <b>(3)</b>            |  |

| STKPTR   | 2525 | 2620    | 4525   | 4620 | 00-0 0000                          | uu-0 0000                                                        | uu-u uuuu <b>(3)</b>            |  |

| PCLATU   | 2525 | 2620    | 4525   | 4620 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| PCLATH   | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| PCL      | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU  | 2525 | 2620    | 4525   | 4620 | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |

| TBLPTRH  | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| TBLPTRL  | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| TABLAT   | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |  |

| PRODH    | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| PRODL    | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| INTCON   | 2525 | 2620    | 4525   | 4620 | 0000 000x                          | 0000 000u                                                        | uuuu uuuu <b>(1)</b>            |  |

| INTCON2  | 2525 | 2620    | 4525   | 4620 | 1111 -1-1                          | 1111 -1-1                                                        | uuuu -u-u <b>(1)</b>            |  |

| INTCON3  | 2525 | 2620    | 4525   | 4620 | 11-0 0-00                          | 11-0 0-00                                                        | uu-u u-uu <b>(1)</b>            |  |

| INDF0    | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| POSTINC0 | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| POSTDEC0 | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| PREINC0  | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| PLUSW0   | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| FSR0H    | 2525 | 2620    | 4525   | 4620 | 0000                               | 0000                                                             | uuuu                            |  |

| FSR0L    | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| WREG     | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |  |

| INDF1    | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| POSTINC1 | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| POSTDEC1 | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| PREINC1  | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

| PLUSW1   | 2525 | 2620    | 4525   | 4620 | N/A                                | N/A                                                              | N/A                             |  |

### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 4-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

| Register | Ар   | plicabl | e Devi | ces  | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |

|----------|------|---------|--------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|

| ADRESH   | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |

| ADRESL   | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |

| ADCON0   | 2525 | 2620    | 4525   | 4620 | 00 0000                            | 00 0000                                                          | uu uuuu                         |

| ADCON1   | 2525 | 2620    | 4525   | 4620 | 00 0qqq                            | 00 0qqq                                                          | uu uuuu                         |

| ADCON2   | 2525 | 2620    | 4525   | 4620 | 0-00 0000                          | 0-00 0000                                                        | u-uu uuuu                       |

| CCPR1H   | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |

| CCPR1L   | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |

| CCP1CON  | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

|          | 2525 | 2620    | 4525   | 4620 | 00 0000                            | 00 0000                                                          | uu uuuu                         |

| CCPR2H   | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | սսսս սսսս                                                        | uuuu uuuu                       |

| CCPR2L   | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |

| CCP2CON  | 2525 | 2620    | 4525   | 4620 | 00 0000                            | 00 0000                                                          | uu uuuu                         |

| BAUDCON  | 2525 | 2620    | 4525   | 4620 | 0100 0-00                          | 0100 0-00                                                        | uuuu u-uu                       |

| PWM1CON  | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| ECCP1AS  | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

|          | 2525 | 2620    | 4525   | 4620 | 0000 00                            | 0000 00                                                          | uuuu uu                         |

| CVRCON   | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| CMCON    | 2525 | 2620    | 4525   | 4620 | 0000 0111                          | 0000 0111                                                        | uuuu uuuu                       |

| TMR3H    | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |

| TMR3L    | 2525 | 2620    | 4525   | 4620 | XXXX XXXX                          | uuuu uuuu                                                        | uuuu uuuu                       |

| T3CON    | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | uuuu uuuu                                                        | uuuu uuuu                       |

| SPBRGH   | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| SPBRG    | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| RCREG    | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| TXREG    | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| TXSTA    | 2525 | 2620    | 4525   | 4620 | 0000 0010                          | 0000 0010                                                        | uuuu uuuu                       |

| RCSTA    | 2525 | 2620    | 4525   | 4620 | 0000 000x                          | 0000 000x                                                        | uuuu uuuu                       |

| EEADRH   | 2585 | 2680    | 4585   | 4680 | 00                                 | 00                                                               | uu                              |

| EEADR    | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| EEDATA   | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | uuuu uuuu                       |

| EECON2   | 2525 | 2620    | 4525   | 4620 | 0000 0000                          | 0000 0000                                                        | 0000 0000                       |

| EECON1   | 2525 | 2620    | 4525   | 4620 | xx-0 x000                          | uu-0 u000                                                        | uu-0 u000                       |

### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

### 5.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

### 5.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL | SUB1, FAST        | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|------|-------------------|---------------------------------------------------------|

| SUB1 | •                 |                                                         |

|      | •<br>RETURN, FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

# 5.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

### 5.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF<br>CALL | OFFSET,<br>TABLE | W |

|-------|--------------|------------------|---|

| ORG   | nn00h        |                  |   |

| TABLE | ADDWF        | PCL              |   |

|       | RETLW        | nnh              |   |

|       | RETLW        | nnh              |   |

|       | RETLW        | nnh              |   |

|       | •            |                  |   |

|       | •            |                  |   |

|       | •            |                  |   |

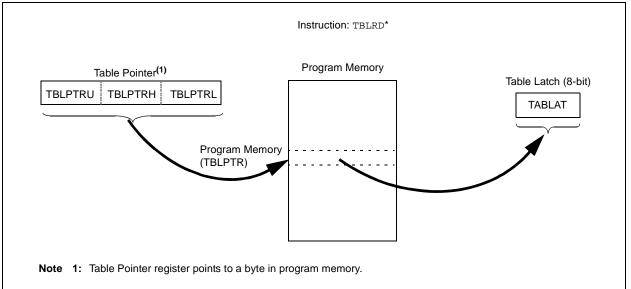

### 5.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 7.1 "Table Reads and Table Writes".

# 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 64 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

### 7.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 7.5** "**Writing to Flash Program Memory**". Figure 7-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1: TABLE READ OPERATION

| Pin            | Function            | TRIS<br>Setting | I/O | l/O<br>Type          | Description                                                                                                                               |

|----------------|---------------------|-----------------|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/     | RC0                 | 0               | 0   | DIG                  | LATC<0> data output.                                                                                                                      |

| T13CKI         |                     | 1               | Ι   | ST                   | PORTC<0> data input.                                                                                                                      |

|                | T1OSO               | х               | 0   | ANA                  | Timer1 oscillator output; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                |

|                | T13CKI              | 1               | Ι   | ST                   | Timer1/Timer3 counter input.                                                                                                              |

| RC1/T1OSI/CCP2 | RC1                 | 0               | 0   | DIG                  | LATC<1> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<1> data input.                                                                                                                      |

|                | T1OSI               | x               | Ι   | ANA                  | Timer1 oscillator input; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                 |

|                | CCP2 <sup>(1)</sup> | 0               | 0   | DIG                  | CCP2 compare and PWM output; takes priority over port data.                                                                               |

|                |                     | 1               | Ι   | ST                   | CCP2 capture input.                                                                                                                       |

| RC2/CCP1/P1A   | RC2                 | 0               | 0   | DIG                  | LATC<2> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<2> data input.                                                                                                                      |

|                | CCP1                | 0               | 0   | DIG                  | ECCP1 compare or PWM output; takes priority over port data.                                                                               |

|                |                     | 1               | Ι   | ST                   | ECCP1 capture input.                                                                                                                      |

|                | P1A <sup>(2)</sup>  | 0               | 0   | DIG                  | ECCP1 Enhanced PWM output, channel A. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RC3/SCK/SCL    | RC3                 | 0               | 0   | DIG                  | LATC<3> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<3> data input.                                                                                                                      |

|                | SCK                 | 0               | 0   | DIG                  | SPI clock output (MSSP module); takes priority over port data.                                                                            |

|                |                     | 1               |     | ST                   | SPI clock input (MSSP module).                                                                                                            |

|                | SCL                 | 0               | 0   | DIG                  | I <sup>2</sup> C <sup>™</sup> clock output (MSSP module); takes priority over port data.                                                  |

|                |                     | 1               | Ι   | I <sup>2</sup> C/SMB | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting                                                          |

| RC4/SDI/SDA    | RC4                 | 0               | 0   | DIG                  | LATC<4> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<4> data input.                                                                                                                      |

|                | SDI                 | 1               | Ι   | ST                   | SPI data input (MSSP module).                                                                                                             |

|                | SDA                 | 0               | 0   | DIG                  | I <sup>2</sup> C data output (MSSP module); takes priority over port data.                                                                |

|                |                     | 1               | Ι   | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.                                                          |

| RC5/SDO        | RC5                 | 0               | 0   | DIG                  | LATC<5> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<5> data input.                                                                                                                      |

|                | SDO                 | 0               | 0   | DIG                  | SPI data output (MSSP module); takes priority over port data.                                                                             |

| RC6/TX/CK      | RC6                 | 0               | 0   | DIG                  | LATC<6> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<6> data input.                                                                                                                      |

|                | ТΧ                  | 0               | 0   | DIG                  | Asynchronous serial transmit data output (EUSART module);<br>takes priority over port data. User must configure as output.                |

|                | СК                  | 0               | 0   | DIG                  | Synchronous serial clock output (EUSART module); takes priority over port data.                                                           |

|                |                     | 1               | Ι   | ST                   | Synchronous serial clock input (EUSART module).                                                                                           |

| RC7/RX/DT      | RC7                 | 0               | 0   | DIG                  | LATC<7> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<7> data input.                                                                                                                      |

|                | RX                  | 1               | Ι   | ST                   | Asynchronous serial receive data input (EUSART module).                                                                                   |

|                | DT                  | 0               | 0   | DIG                  | Synchronous serial data output (EUSART module); takes priority over port data.                                                            |

|                |                     | 1               | Ι   | ST                   | Synchronous serial data input (EUSART module). User must configure as an input.                                                           |

### TABLE 9-5: PORTC I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set. Alternate assignment is RB3.

2: Enhanced PWM output is available only on PIC18F4525/4620 devices.

# 12.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 12-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:       |                                           |                                                                                                              |                                                              |                    |

|---------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|

| R = Readabl   | le bit                                    | W = Writable bit                                                                                             | U = Unimplemented bit                                        | , read as '0'      |

| -n = Value at | t POR                                     | '1' = Bit is set                                                                                             | '0' = Bit is cleared                                         | x = Bit is unknown |

| bit 7         | <b>RD16:</b> 16-                          | Bit Read/Write Mode Enab                                                                                     | le bit                                                       |                    |

|               |                                           | -                                                                                                            | ner1 in one 16-bit operation<br>ner1 in two 8-bit operations |                    |

| bit 6         | T1RUN: Ti                                 | mer1 System Clock Status                                                                                     | bit                                                          |                    |

|               |                                           | e clock is derived from Time<br>e clock is derived from ano                                                  |                                                              |                    |

| bit 5-4       | 11 = 1:8 P<br>10 = 1:4 P<br>01 = 1:2 P    | T1CKPS0: Timer1 Input C<br>rescale value<br>rescale value<br>rescale value<br>rescale value<br>rescale value | lock Prescale Select bits                                    |                    |

| bit 3         | 1 = Timer1<br>0 = Timer1                  | : Timer1 Oscillator Enable<br>oscillator is enabled<br>oscillator is shut off<br>tor inverter and feedback r | bit<br>esistor are turned off to elimina                     | ate power drain.   |

| bit 2         | T1SYNC:<br>When TMF                       | •                                                                                                            | t Synchronization Select bit                                 |                    |

|               | 1 = Do not                                | synchronize external clock                                                                                   | < input                                                      |                    |

|               | <u>When TMF</u><br>This bit is i          |                                                                                                              | iternal clock when TMR1CS =                                  | 0.                 |

| bit 1         | 1 = Extern                                | Timer1 Clock Source Sele<br>al clock from pin RC0/T1C<br>al clock (Fosc/4)                                   | ct bit<br>DSO/T13CKI (on the rising edg                      | e)                 |

| bit 0         | <b>TMR1ON:</b><br>1 = Enable<br>0 = Stops |                                                                                                              |                                                              |                    |

|               |                                           |                                                                                                              |                                                              |                    |

# REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | СКР   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:    |                                                                 |                                                                            |                                                                            |                                                                                                            |  |  |  |  |

|------------|-----------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| R = Read   | able bit W                                                      | / = Writable bit                                                           | U = Unimplemented bit                                                      | , read as '0'                                                                                              |  |  |  |  |

| -n = Value | at POR '1                                                       | ' = Bit is set                                                             | '0' = Bit is cleared                                                       | x = Bit is unknown                                                                                         |  |  |  |  |

| bit 7      | WCOL: Write Co                                                  | ollision Detect bit                                                        |                                                                            |                                                                                                            |  |  |  |  |

|            | software)                                                       |                                                                            | while it is still transmitting the                                         | previous word (must be cleared ir                                                                          |  |  |  |  |

|            | 0 = No collision                                                |                                                                            |                                                                            |                                                                                                            |  |  |  |  |

| bit 6      | SSPOV: Receive<br>SPI Slave mode                                | e Overflow Indicator I                                                     | pit <sup>(1)</sup>                                                         |                                                                                                            |  |  |  |  |

|            | 1 = A new byte<br>flow, the da                                  | is received while the S<br>ta in SSPSR is lost.<br>ven if only transmittin | Overflow can only occur in Sla                                             | the previous data. In case of over<br>ave mode. The user must read the<br>w (must be cleared in software). |  |  |  |  |

| bit 5      | SSPEN: Master Synchronous Serial Port Enable bit <sup>(2)</sup> |                                                                            |                                                                            |                                                                                                            |  |  |  |  |

|            |                                                                 |                                                                            | s SCK, SDO, SDI and $\overline{SS}$ as s<br>as these pins as I/O port pins | erial port pins                                                                                            |  |  |  |  |

| bit 4      | CKP: Clock Pola                                                 | arity Select bit                                                           |                                                                            |                                                                                                            |  |  |  |  |

|            |                                                                 | clock is a high level<br>clock is a low level                              |                                                                            |                                                                                                            |  |  |  |  |

| bit 3-0    | SSPM3:SSPM0                                                     | : Master Synchronou                                                        | s Serial Port Mode Select bits                                             | 3)                                                                                                         |  |  |  |  |

|            | 0100 = SPI Slav<br>0011 = SPI Mas                               |                                                                            | •                                                                          | SS can be used as I/O pin                                                                                  |  |  |  |  |

|            | 0001 = SPI Mas                                                  | ster mode, clock = Fo<br>ster mode, clock = Fo<br>ster mode, clock = Fo    | sc/16                                                                      |                                                                                                            |  |  |  |  |

| Note 1:    | In Master mode, the writing to the SSPBI                        |                                                                            | et since each new reception (ar                                            | nd transmission) is initiated by                                                                           |  |  |  |  |

- 2: When enabled, these pins must be properly configured as input or output.

- 3: Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C<sup>™</sup> mode only.

| R/W-0         | R/W-0                                                                                                                                                                     | R/W-0                                                                             | R/W-0                                                                              | R/W-0                                                  | R/W-0                                     | R/W-0            | R/W-0          |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|------------------|----------------|--|--|--|

| WCOL          | SSPOV                                                                                                                                                                     | SSPEN <sup>(1)</sup>                                                              | CKP                                                                                | SSPM3                                                  | SSPM2                                     | SSPM1            | SSPM0          |  |  |  |

| bit 7         |                                                                                                                                                                           |                                                                                   |                                                                                    |                                                        |                                           |                  | bit            |  |  |  |

| Lonondi       |                                                                                                                                                                           |                                                                                   |                                                                                    |                                                        |                                           |                  |                |  |  |  |

| Legend:       |                                                                                                                                                                           |                                                                                   | .,                                                                                 |                                                        |                                           |                  |                |  |  |  |

| R = Readabl   |                                                                                                                                                                           | W = Writable k                                                                    | Dit                                                                                | -                                                      | nented bit, read                          |                  |                |  |  |  |

| -n = Value at | t POR                                                                                                                                                                     | '1' = Bit is set                                                                  |                                                                                    | '0' = Bit is clea                                      | ared                                      | x = Bit is unkr  | nown           |  |  |  |

| bit 7         | WCOL: Write                                                                                                                                                               | e Collision Detec                                                                 | t bit                                                                              |                                                        |                                           |                  |                |  |  |  |

|               | In Master Tra                                                                                                                                                             |                                                                                   |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               |                                                                                                                                                                           | to the SSPBUF                                                                     |                                                                                    |                                                        |                                           | nditions were i  | not valid for  |  |  |  |

|               |                                                                                                                                                                           | sion to be starte                                                                 | d (must be cl                                                                      | eared in softwa                                        | re)                                       |                  |                |  |  |  |

|               | 0 = No  collis                                                                                                                                                            |                                                                                   |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | In Slave Tran                                                                                                                                                             | PBUF register is                                                                  | written while                                                                      | it is still transm                                     | itting the previo                         | ous word (mus    | t he cleared i |  |  |  |

|               | software                                                                                                                                                                  |                                                                                   |                                                                                    |                                                        | intering the provide                      |                  |                |  |  |  |

|               | 0 = No collis                                                                                                                                                             | ion                                                                               |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               |                                                                                                                                                                           | ode (Master or S                                                                  | <u>Slave modes)</u>                                                                | <u>:</u>                                               |                                           |                  |                |  |  |  |

|               | This is a "dor                                                                                                                                                            | n't care" bit.                                                                    |                                                                                    |                                                        |                                           |                  |                |  |  |  |

| bit 6         |                                                                                                                                                                           | eive Overflow Ir                                                                  | dicator bit                                                                        |                                                        |                                           |                  |                |  |  |  |

|               | In Receive mode:                                                                                                                                                          |                                                                                   |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | <ul> <li>1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared i<br/>software)</li> </ul>                                  |                                                                                   |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | 0 = No overf                                                                                                                                                              | /                                                                                 |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | In Transmit n                                                                                                                                                             | node:                                                                             |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               |                                                                                                                                                                           | n't care" bit in Tra                                                              | ansmit mode.                                                                       |                                                        |                                           |                  |                |  |  |  |

| bit 5         | SSPEN: Mas                                                                                                                                                                | ster Synchronous                                                                  | s Serial Port E                                                                    | Enable bit <sup>(1)</sup>                              |                                           |                  |                |  |  |  |

|               |                                                                                                                                                                           | the serial port ar                                                                |                                                                                    |                                                        | CL pins as the                            | serial port pins | i              |  |  |  |

|               | 0 = Disables                                                                                                                                                              | serial port and c                                                                 | onfigures the                                                                      | se pins as I/O p                                       | oort pins                                 |                  |                |  |  |  |

| bit 4         | CKP: SCK R                                                                                                                                                                | elease Control b                                                                  | oit                                                                                |                                                        |                                           |                  |                |  |  |  |

|               | In Slave mod                                                                                                                                                              |                                                                                   |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | 1 = Releases                                                                                                                                                              |                                                                                   |                                                                                    |                                                        | ture time e                               |                  |                |  |  |  |

|               |                                                                                                                                                                           | = Holds clock low (clock stretch), used to ensure data setup time<br>Master mode: |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               | Unused in th                                                                                                                                                              |                                                                                   |                                                                                    |                                                        |                                           |                  |                |  |  |  |

|               |                                                                                                                                                                           |                                                                                   |                                                                                    |                                                        | (0)                                       |                  |                |  |  |  |

| bit 3-0       | <b>SSPM3:SSPM0:</b> Master Synchronous Serial Port Mode Select bits <sup>(2)</sup><br>1111 = $I^2C$ Slave mode, 10-bit address with Start and Stop bit interrupts enabled |                                                                                   |                                                                                    |                                                        |                                           |                  |                |  |  |  |

| bit 3-0       |                                                                                                                                                                           |                                                                                   |                                                                                    |                                                        |                                           | enabled          |                |  |  |  |

| bit 3-0       | $1111 = I^2 C S$<br>$1110 = I^2 C S$                                                                                                                                      | Slave mode, 10-b<br>Slave mode, 7-bi                                              | oit address wi<br>t address with                                                   | th Start and Ston<br>Start and Stop                    | p bit interrupts<br>bit interrupts e      |                  |                |  |  |  |

| bit 3-0       | $1111 = I^2CS$<br>$1110 = I^2CS$<br>$1011 = I^2CF$                                                                                                                        | Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Contro                           | oit address wi<br>t address with<br>lled Master m                                  | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |  |  |  |

| bit 3-0       | $1111 = I^{2}C S$<br>$1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C N$                                                                                          | Blave mode, 10-b<br>Blave mode, 7-bi<br>Firmware Contro<br>Master mode, clo       | bit address wi<br>t address with<br>lled Master m<br>lock = FOSC/(4                | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |  |  |  |

| bit 3-0       | $1111 = I^{2}C S$<br>$1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C N$<br>$0111 = I^{2}C S$                                                                     | Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Contro                           | bit address wi<br>t address with<br>lled Master m<br>lock = Fosc/(4<br>bit address | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |  |  |  |

# REGISTER 17-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

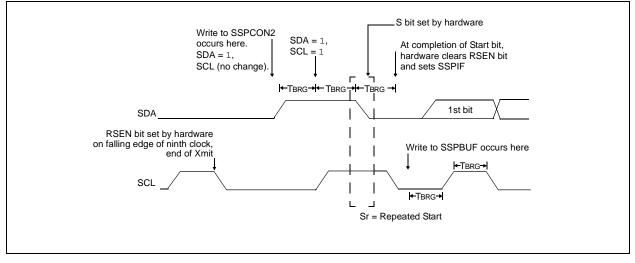

## 17.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 17.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

# FIGURE 17-20: REPEAT START CONDITION WAVEFORM

| R/W-0        | R/W-0                             | R/W-0                                                | R/W-0         | R/W-0             | R/W-0           | R-1             | R/W-0 |

|--------------|-----------------------------------|------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| CSRC         | TX9                               | TXEN <sup>(1)</sup>                                  | SYNC          | SENDB             | BRGH            | TRMT            | TX9D  |

| bit 7        |                                   | ·                                                    | ·             |                   |                 |                 | bit   |

| Legend:      |                                   |                                                      |               |                   |                 |                 |       |

| R = Readal   | ole bit                           | W = Writable                                         | bit           | U = Unimplem      | nented bit, rea | ıd as '0'       |       |

| -n = Value a | at POR                            | '1' = Bit is set                                     |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                                   |                                                      |               |                   |                 |                 |       |

| bit 7        |                                   | k Source Select                                      | bit           |                   |                 |                 |       |

|              | Asynchrono<br>Don't care.         | <u>us mode:</u>                                      |               |                   |                 |                 |       |

|              |                                   | <u>s mode:</u><br>node (clock gen<br>ode (clock from |               |                   |                 |                 |       |

| bit 6        | <b>TX9:</b> 9-Bit T               | ransmit Enable I                                     | oit           |                   |                 |                 |       |

|              | 1 = Selects                       | 9-bit transmissio                                    | n             |                   |                 |                 |       |

|              |                                   | 8-bit transmissio                                    |               |                   |                 |                 |       |

| oit 5        |                                   | smit Enable bit <sup>(1</sup>                        | )             |                   |                 |                 |       |

|              | 1 = Transm<br>0 = Transm          |                                                      |               |                   |                 |                 |       |

| oit 4        |                                   | ART Mode Sele                                        | et hit        |                   |                 |                 |       |

| 511 4        | 1 = Synchro                       |                                                      |               |                   |                 |                 |       |

|              | 0 = Asynchr                       |                                                      |               |                   |                 |                 |       |

| bit 3        | SENDB: Se                         | nd Break Chara                                       | cter bit      |                   |                 |                 |       |

|              | Asynchrono                        |                                                      |               |                   |                 |                 |       |

|              |                                   |                                                      |               | n (cleared by ha  | rdware upon o   | completion)     |       |

|              | 0 = Sync Bro<br>Synchronou        | eak transmissior                                     | i completed   |                   |                 |                 |       |

|              | Don't care.                       | s moue.                                              |               |                   |                 |                 |       |

| bit 2        | BRGH: High                        | Baud Rate Sel                                        | ect bit       |                   |                 |                 |       |

|              | Asynchrono                        | <u>us mode:</u>                                      |               |                   |                 |                 |       |

|              | 1 = High spectrum                 |                                                      |               |                   |                 |                 |       |

|              | 0 = Low spe                       |                                                      |               |                   |                 |                 |       |

|              | <u>Synchronou</u><br>Unused in th |                                                      |               |                   |                 |                 |       |

| oit 1        |                                   | smit Shift Regist                                    | er Status bit |                   |                 |                 |       |

|              | 1 = TSR em<br>0 = TSR full        | •                                                    |               |                   |                 |                 |       |

| bit 0        |                                   | it of Transmit Da                                    | ata           |                   |                 |                 |       |

|              |                                   |                                                      |               |                   |                 |                 |       |