innin receive

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4620-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.2 Other Special Features

- Memory Endurance: The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-Programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18F2525/ 2620/4525/4620 family introduces an optional extension to the PIC18 instruction set, which adds 8 new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced CCP Module: In PWM mode, this module provides 1, 2 or 4 modulated outputs for controlling half-bridge and full-bridge drivers. Other features include auto-shutdown, for disabling PWM outputs on interrupt or other select conditions and auto-restart, to reactivate outputs once the condition has cleared.

- Enhanced Addressable USART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 26.0 "Electrical Characteristics" for time-out periods.

### 1.3 Details on Individual Family Members

Devices in the PIC18F2525/2620/4525/4620 family are available in 28-pin and 40/44-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in five ways:

- Flash program memory (48 Kbytes for PIC18FX525 devices, 64 Kbytes for PIC18FX620 devices).

- A/D channels (10 for 28-pin devices, 13 for 40/44-pin devices).

- 3. I/O ports (3 bidirectional ports on 28-pin devices, 5 bidirectional ports on 40/44-pin devices).

- CCP and Enhanced CCP implementation (28-pin devices have 2 standard CCP modules, 40/44-pin devices have one standard CCP module and one ECCP module).

- 5. Parallel Slave Port (present only on 40/44-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in Table 1-2 and Table 1-3.

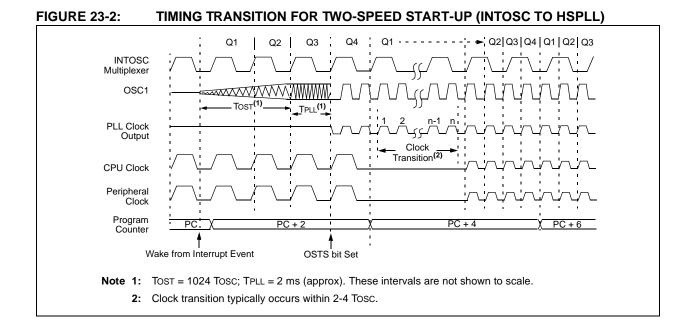

Like all Microchip PIC18 devices, members of the PIC18F2525/2620/4525/4620 family are available as both standard and low-voltage devices. Standard devices with Enhanced Flash memory, designated with an "F" in the part number (such as PIC18F2620), accommodate an operating VDD range of 4.2V to 5.5V. Low-voltage parts, designated by "LF" (such as PIC18LF2620), function over an extended VDD range of 2.0V to 5.5V.

# 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set, after the INTOSC output becomes stable, after an interval of TIOBST (parameter 39, Table 26-10). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

# 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/ GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see **Section 10.0 "Interrupts"**).

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 23.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

### 3.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 3-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see **Section 23.3 "Two-Speed Start-up"**) or Fail-Safe Clock Monitor (see **Section 23.4 "Fail-Safe Clock Monitor"**) is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

| TABLE 4-4:           | 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |      |                                                |      |                          |                                                                  |                                 |

|----------------------|--------------------------------------------------------------|------|------------------------------------------------|------|--------------------------|------------------------------------------------------------------|---------------------------------|

| Register             | ster Applicable Devices                                      |      | ble Devices Power-on Reset,<br>Brown-out Reset |      | ,                        | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |

| IPR2                 | 2525                                                         | 2620 | 4525                                           | 4620 | 11-1 1111                | 11-1 1111                                                        | uu-u uuuu                       |

| PIR2                 | 2525                                                         | 2620 | 4525                                           | 4620 | 00-0 0000                | 00-0 0000                                                        | uu-u uuuu <b>(1)</b>            |

| PIE2                 | 2525                                                         | 2620 | 4525                                           | 4620 | 00-0 0000                | 00-0 0000                                                        | uu-u uuuu                       |

| IPR1                 | 2525                                                         | 2620 | 4525                                           | 4620 | 1111 1111                | 1111 1111                                                        | uuuu uuuu                       |

|                      | 2525                                                         | 2620 | 4525                                           | 4620 | -111 1111                | -111 1111                                                        | -uuu uuuu                       |

| PIR1                 | 2525                                                         | 2620 | 4525                                           | 4620 | 0000 0000                | 0000 0000                                                        | uuuu uuuu <sup>(1)</sup>        |

|                      | 2525                                                         | 2620 | 4525                                           | 4620 | -000 0000                | -000 0000                                                        | -uuu uuuu <b>(1)</b>            |

| PIE1                 | 2525                                                         | 2620 | 4525                                           | 4620 | 0000 0000                | 0000 0000                                                        | uuuu uuuu                       |

|                      | 2525                                                         | 2620 | 4525                                           | 4620 | -000 0000                | -000 0000                                                        | -uuu uuuu                       |

| OSCTUNE              | 2525                                                         | 2620 | 4525                                           | 4620 | 00-0 0000                | 00-0 0000                                                        | uu-u uuuu                       |

| TRISE                | 2525                                                         | 2620 | 4525                                           | 4620 | 0000 -111                | 0000 -111                                                        | uuuu -uuu                       |

| TRISD                | 2525                                                         | 2620 | 4525                                           | 4620 | 1111 1111                | 1111 1111                                                        | uuuu uuuu                       |

| TRISC                | 2525                                                         | 2620 | 4525                                           | 4620 | 1111 1111                | 1111 1111                                                        | uuuu uuuu                       |

| TRISB                | 2525                                                         | 2620 | 4525                                           | 4620 | 1111 1111                | 1111 1111                                                        | uuuu uuuu                       |

| TRISA <sup>(5)</sup> | 2525                                                         | 2620 | 4525                                           | 4620 | 1111 1111 <b>(5)</b>     | 1111 1111 <b>(5)</b>                                             | uuuu uuuu <sup>(5)</sup>        |

| LATE                 | 2525                                                         | 2620 | 4525                                           | 4620 | xxx                      | uuu                                                              | uuu                             |

| LATD                 | 2525                                                         | 2620 | 4525                                           | 4620 | XXXX XXXX                | սսսս սսսս                                                        | uuuu uuuu                       |

| LATC                 | 2525                                                         | 2620 | 4525                                           | 4620 | xxxx xxxx                | uuuu uuuu                                                        | uuuu uuuu                       |

| LATB                 | 2525                                                         | 2620 | 4525                                           | 4620 | XXXX XXXX                | uuuu uuuu                                                        | uuuu uuuu                       |

| LATA <sup>(5)</sup>  | 2525                                                         | 2620 | 4525                                           | 4620 | xxxx xxxx <sup>(5)</sup> | uuuu uuuu <sup>(5)</sup>                                         | uuuu uuuu <b>(5)</b>            |

| PORTE                | 2525                                                         | 2620 | 4525                                           | 4620 | xxxx                     | uuuu                                                             | uuuu                            |

|                      | 2525                                                         | 2620 | 4525                                           | 4620 | x                        | u                                                                | u                               |

| PORTD                | 2525                                                         | 2620 | 4525                                           | 4620 | xxxx xxxx                | սսսս սսսս                                                        | սսսս սսսս                       |

| PORTC                | 2525                                                         | 2620 | 4525                                           | 4620 | xxxx xxxx                | սսսս սսսս                                                        | uuuu uuuu                       |

| PORTB                | 2525                                                         | 2620 | 4525                                           | 4620 | xxxx xxxx                | นนนน นนนน                                                        | uuuu uuuu                       |

| PORTA <sup>(5)</sup> | 2525                                                         | 2620 | 4525                                           | 4620 | xx0x 0000 <b>(5)</b>     | uu0u 0000 <b>(5)</b>                                             | uuuu uuuu <sup>(5)</sup>        |

# TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

# 6.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, that is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Five SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- EECON1

- EECON2

- EEDATA

- EEADR

- EEADRH

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADRH:EEADR register pair holds the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer; it will vary with voltage and temperature as well as from chip to chip. Please refer to parameter D122 (Table 26-1 in **Section 26.0 "Electrical Characteristics**") for exact limits.

# 6.1 EEADR and EEADRH Registers

The EEADRH:EEADR register pair is used to address the data EEPROM for read and write operations. EEADRH holds the two MSbits of the address; the upper 6 bits are ignored. The 10-bit range of the pair can address a memory range of 1024 bytes (00h to 3FFh).

# 6.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 6-1) is the control register for data and program memory access. Control bit EEPGD determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either Flash program or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is<br>read as '1'. This can indicate that a write<br>operation was prematurely terminated by |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

|       | a Reset, or a write operation was attempted improperly.                                                                         |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

| Note: | The EEIF interrupt flag bit (PIR2<4>) is set |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|

|       | when the write is complete. It must be       |  |  |  |  |

|       | cleared in software.                         |  |  |  |  |

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 7.1 "Table Reads** and **Table Writes"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

# 7.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. TBLPTR<5:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

|                      | MOVLW<br>MOVWF<br>MOVLW<br>MOVLW<br>MOVLW<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block                                                                                         |

|----------------------|----------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| ERASE_ROW            | MOVWF                                              | IBLPIRL                                                                             |                                                                                                                                                      |

|                      | BSF<br>BCF<br>BSF<br>BSF<br>BCF                    | EECON1, EEPGD<br>EECON1, CFGS<br>EECON1, WREN<br>EECON1, FREE<br>INTCON, GIE        | ; point to Flash program memory<br>; access Flash program memory<br>; enable write to memory<br>; enable Row Erase operation<br>; disable interrupts |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF            | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1, WR                                       | ; write 55h<br>; write 0AAh<br>; start erase (CPU stall)                                                                                             |

|                      | BSF                                                | INTCON, GIE                                                                         | ; re-enable interrupts                                                                                                                               |

### EXAMPLE 7-2: ERASING A FLASH PROGRAM MEMORY ROW

### 17.3.3 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

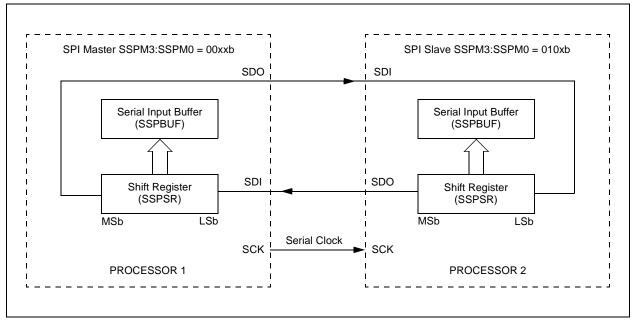

#### 17.3.4 TYPICAL CONNECTION

Figure 17-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 17-2: SPI MASTER/SLAVE CONNECTION

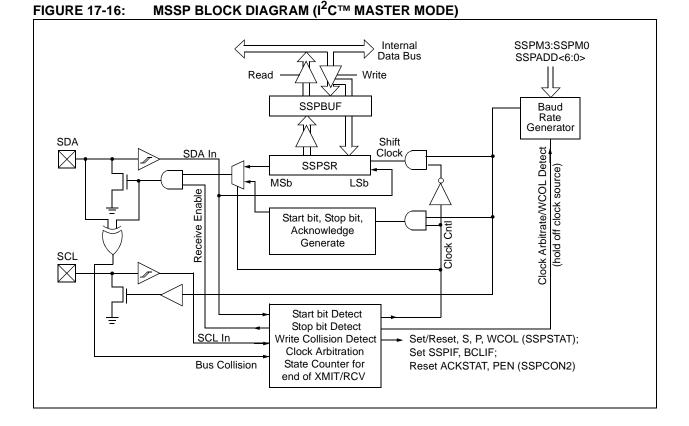

### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $l^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

- Start condition

- Stop condition

- Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated Start

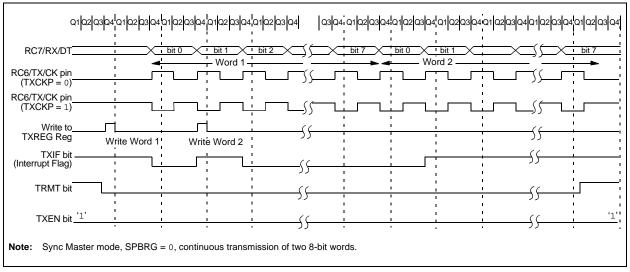

### 18.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the TXCKP bit (BAUDCON<4>); setting TXCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 18.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 18-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

FIGURE 18-11: SYNCHRONOUS TRANSMISSION

# 20.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins RA0 through RA5, as well as the on-chip voltage reference (see Section 21.0 "Comparator Voltage Reference Module"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register.

The CMCON register (Register 20-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 20-1.

#### **REGISTER 20-1: CMCON: COMPARATOR CONTROL REGISTER**

| R-0      | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 | R/W-1 | R/W-1 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| C2OUT    | C1OUT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   |

| bit 7    |       |       |       |       |       |       | bit 0 |

|          |       |       |       |       |       |       |       |

| l egend. |       |       |       |       |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | C2OUT: Comparator 2 Output bit                                             |

|---------|----------------------------------------------------------------------------|

|         | When $C2INV = 0$ :                                                         |

|         | 1 = C2 VIN + > C2 VIN -                                                    |

|         | 0 = C2 VIN + < C2 VIN -                                                    |

|         | <u>When C2INV = 1:</u>                                                     |

|         | 1 = C2  VIN+ < C2  VIN-                                                    |

|         | 0 = C2  VIN+ > C2  VIN-                                                    |

| bit 6   | C1OUT: Comparator 1 Output bit                                             |

|         | $\frac{\text{When C1INV} = 0}{1 - 24}$                                     |

|         | 1 = C1 VIN+ > C1 VIN-<br>0 = C1 VIN+ < C1 VIN-                             |

|         | When $C1INV = 1$ :                                                         |

|         | 1 = C1 VIN+ < C1 VIN-                                                      |

|         | 0 = C1  Vin + > C1  Vin                                                    |

| bit 5   | C2INV: Comparator 2 Output Inversion bit                                   |

|         | 1 = C2 output inverted                                                     |

|         | 0 = C2 output not inverted                                                 |

| bit 4   | C1INV: Comparator 1 Output Inversion bit                                   |

|         | 1 = C1 output inverted                                                     |

|         | 0 = C1 output not inverted                                                 |

| bit 3   | CIS: Comparator Input Switch bit                                           |

|         | $\frac{\text{When CM2:CM0} = 110:}{2}$                                     |

|         | 1 = C1  VIN- connects to RA3/AN3/VREF+                                     |

|         | C2 VIN- connects to RA2/AN2/VREF-/CVREF<br>0 = C1 VIN- connects to RA0/AN0 |

|         | C2 VIN- connects to RA1/AN1                                                |

| bit 2-0 | CM2:CM0: Comparator Mode bits                                              |

|         | Figure 20-1 shows the Comparator modes and the CM2:CM0 bit settings.       |

|         | о                                                                          |

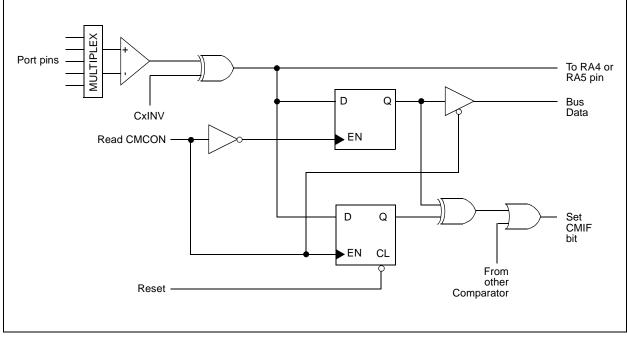

# 20.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR2<6>) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

Both the CMIE bit (PIE2<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

# 20.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode, when enabled. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM2:CM0 = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

### 20.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator modules to be turned off (CM2:CM0 = 111). However, the input pins (RA0 through RA3) are configured as analog inputs by default on device Reset. The I/O configuration for these pins is determined by the setting of the PCFG3:PCFG0 bits (ADCON1<3:0>). Therefore, device current is minimized when analog inputs are present at Reset time.

#### REGISTER 23-12: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F2525/2620/4525/4620

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:                                |                                                                     |                                                                                            |                                     |  |  |  |  |  |

|----------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|--|

| R = Readable bit                       |                                                                     | P = Programmable bit                                                                       | U = Unimplemented bit, read as '0'  |  |  |  |  |  |

| -n = Value when device is unprogrammed |                                                                     |                                                                                            | u = Unchanged from programmed state |  |  |  |  |  |

| bit 7-5                                | <b>DEV2:DEV</b><br>000 = PIC<br>010 = PIC<br>100 = PIC<br>110 = PIC | 18F4525<br>18F2620                                                                         |                                     |  |  |  |  |  |

| bit 4-0                                |                                                                     | <b>REV4:REV0:</b> Revision ID bits<br>These bits are used to indicate the device revision. |                                     |  |  |  |  |  |

#### REGISTER 23-13: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F2525/2620/4525/4620

| R                    | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV10 <sup>(1)</sup> | DEV9 <sup>(1)</sup> | DEV8 <sup>(1)</sup> | DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> |

| bit 7                |                     |                     |                     |                     |                     |                     | bit 0               |

| Legend:                      |                      |                                     |

|------------------------------|----------------------|-------------------------------------|

| R = Read-only bit            | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is ur | programmed           | u = Unchanged from programmed state |

bit 7-0 **DEV10:DEV3:** Device ID bits<sup>(1)</sup> These bits are used with the DEV2:DEV0 bits in Device ID Register 1 to identify the part number. 0000 1100 = PIC18F2525/2620/4525/4620 devices

**Note 1:** These values for DEV10:DEV3 may be shared with other devices. The specific device is always identified by using the entire DEV10:DEV0 bit sequence.

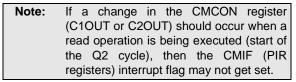

# 23.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTOSC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (Crystal-Based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF2:IRCF0, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF2:IRCF0 bits prior to entering Sleep mode. In all other power-managed modes, Two-Speed Startup is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

### 23.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTOSC oscillator in Two-Speed Startup, the device still obeys the normal command sequences for entering power-managed modes, including multiple SLEEP instructions (refer to **Section 3.1.4 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS1:SCS0 bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

| POP                                               | Рор Тор о                                                               | Pop Top of Return Stack                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Syntax:                                           | POP                                                                     |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Operands:                                         | None                                                                    | None                                                                                                                                                                                                                                                                                       |                 |  |  |  |  |

| Operation:                                        | (TOS) $\rightarrow$ bit bucket                                          |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Status Affected:                                  | None                                                                    |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Encoding:                                         | 0000                                                                    | 0000 00                                                                                                                                                                                                                                                                                    | 00 0110         |  |  |  |  |

| Description:                                      | stack and is<br>then becom<br>was pushed<br>This instruc<br>the user to | The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. |                 |  |  |  |  |

| Words:                                            | 1                                                                       |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Cycles:                                           | 1                                                                       |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Q Cycle Activity:                                 |                                                                         |                                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Q1                                                | Q2                                                                      | Q3                                                                                                                                                                                                                                                                                         | Q4              |  |  |  |  |

| Decode                                            | No<br>operation                                                         | POP TOS<br>value                                                                                                                                                                                                                                                                           | No<br>operation |  |  |  |  |

| Example:                                          | POP<br>GOTO                                                             | NEW                                                                                                                                                                                                                                                                                        |                 |  |  |  |  |

| Before Instruction<br>TOS<br>Stack (1 level down) |                                                                         | = 0031A<br>= 01433                                                                                                                                                                                                                                                                         |                 |  |  |  |  |

| After Instruction<br>TOS<br>PC                    |                                                                         | = 01433<br>= NEW                                                                                                                                                                                                                                                                           | 2h              |  |  |  |  |

| PUSH Push Top     |                                              |                                                                                                                                                                                                                                             | of Return Stack |                |   |                |

|-------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---|----------------|

| Synta             | ax:                                          | PUSH                                                                                                                                                                                                                                        |                 |                |   |                |

| Oper              | ands:                                        | None                                                                                                                                                                                                                                        |                 |                |   |                |

| Oper              | ation:                                       | $(PC + 2) \rightarrow$                                                                                                                                                                                                                      | тоѕ             |                |   |                |

| Statu             | s Affected:                                  | None                                                                                                                                                                                                                                        |                 |                |   |                |

| Enco              | ding:                                        | 0000                                                                                                                                                                                                                                        | 0000            | 000            | 0 | 0101           |

| Desc              | ription:                                     | The PC + 2 is pushed onto the top of<br>the return stack. The previous TOS<br>value is pushed down on the stack.<br>This instruction allows implementing a<br>software stack by modifying TOS and<br>then pushing it onto the return stack. |                 |                |   |                |

| Word              | ls:                                          | 1                                                                                                                                                                                                                                           |                 |                |   |                |

| Cycles:           |                                              | 1                                                                                                                                                                                                                                           |                 |                |   |                |

| Q Cycle Activity: |                                              |                                                                                                                                                                                                                                             |                 |                |   |                |

|                   | Q1                                           | Q2                                                                                                                                                                                                                                          |                 | Q3             |   | Q4             |

|                   | Decode                                       | PUSH<br>PC + 2 onto<br>return stack                                                                                                                                                                                                         | No<br>operation |                | o | No<br>peration |

|                   |                                              |                                                                                                                                                                                                                                             |                 |                |   |                |

| Exan              | nple:                                        | PUSH                                                                                                                                                                                                                                        |                 |                |   |                |

|                   | n <u>ple:</u><br>Before Instruc<br>TOS<br>PC |                                                                                                                                                                                                                                             | =               | 345Ah<br>0124h |   |                |

| SUBWFB                        | Su                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ubtract    | W from         | f witł   | n Borrow    |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|----------|-------------|

| Syntax:                       | SL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JBWFB      | f {,d {,a      | a}}      |             |

| Operands:                     | 0 ≤ f ≤ 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                |          |             |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | [0,1]      |                |          |             |

|                               | a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                |          |             |

| Operation:                    | $(f) - (W) - (\overline{C}) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                |          |             |

| Status Affected:              | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                |          |             |

| Encoding:                     | 0101 10da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                |          |             |

| Description:                  | Subtract W and the Carry flag (borrow)<br>from register 'f' (2's<br>complement method). If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '0', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |            |                |          |             |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | eral Offs  |                |          |             |

| Words:                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                |          |             |

| Cycles:                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                |          |             |

| Q Cycle Activity:             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                |          |             |

| Q Cycle Activity.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q2         | Q              | 3        | Q4          |

| Decode                        | l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read       | Proc           |          | Write to    |

|                               | reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | gister 'f' | Dat            | ta       | destination |

| Example 1:                    | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UBWFB      | REG, 1         | L, O     |             |

| Before Instruc                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 106        | (              | 1 100    | . 1 .       |

| REG<br>W                      | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19h<br>0Dh | (000)<br>(000) |          |             |

| C<br>After Instructio         | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1          |                |          |             |

| After Instructio<br>REG       | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0Ch        | (000           | 0 101    | .1)         |

| W<br>C                        | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0Dh<br>1   | (000           | 0 110    | 1)          |

| Z                             | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0          |                |          |             |

| N                             | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0          |                | It is po | sitive      |

| Example 2:<br>Before Instruct |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UBWFB      | REG, U         | , 0      |             |