Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4620-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>D</b> ' 1                                                                | Pin<br>Number  | Pin               | Buffer                    |                                                                                                               |

|-----------------------------------------------------------------------------|----------------|-------------------|---------------------------|---------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                    | SPDIP,<br>SOIC | Туре              | Туре                      | Description                                                                                                   |

|                                                                             |                |                   |                           | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0/FLT0/AN12<br>RB0<br>INT0<br>FLT0<br>AN12                           | 21             | I/O<br> <br> <br> | TTL<br>ST<br>ST<br>Analog | Digital I/O.<br>External interrupt 0.<br>PWM Fault input for CCP1.<br>Analog input 12.                        |

| RB1/INT1/AN10<br>RB1<br>INT1<br>AN10                                        | 22             | I/O<br>I<br>I     | TTL<br>ST<br>Analog       | Digital I/O.<br>External interrupt 1.<br>Analog input 10.                                                     |

| RB2/INT2/AN8<br>RB2<br>INT2<br>AN8                                          | 23             | I/O<br>I<br>I     | TTL<br>ST<br>Analog       | Digital I/O.<br>External interrupt 2.<br>Analog input 8.                                                      |

| RB3/AN9/CCP2<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup>                           | 24             | I/O<br>I<br>I/O   | TTL<br>Analog<br>ST       | Digital I/O.<br>Analog input 9.<br>Capture 2 input/Compare 2 output/PWM2 output.                              |

| RB4/KBI0/AN11<br>RB4<br>KBI0<br>AN11                                        | 25             | I/O<br>I<br>I     | TTL<br>TTL<br>Analog      | Digital I/O.<br>Interrupt-on-change pin.<br>Analog input 11.                                                  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                                          | 26             | I/O<br>I<br>I/O   | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                         |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                                          | 27             | I/O<br>I<br>I/O   | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.               |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                                          | 28             | I/O<br>I<br>I/O   | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                |

| Legend: TTL = TTL co<br>ST = Schmit<br>O = Output<br>Note 1: Default assign | t Trigger inpu | t with CN         |                           | CMOS = CMOS compatible input or output<br>els I = Input<br>P = Power<br>P2MX Configuration bit is set.        |

### TABLE 1-2: PIC18F2525/2620 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

| R/W-0      | R/W-1                                                                                                                                                                                                         | R/W-0                                                                                                                                        | R/W-0          | R <sup>(1)</sup>  | R-0             | R/W-0           | R/W-0 |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| IDLEN      | IRCF2                                                                                                                                                                                                         | IRCF1                                                                                                                                        | IRCF0          | OSTS              | IOFS            | SCS1            | SCS0  |  |  |  |  |  |  |

| bit 7      | ·                                                                                                                                                                                                             |                                                                                                                                              |                |                   |                 | •               | bit ( |  |  |  |  |  |  |

|            |                                                                                                                                                                                                               |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

| Legend:    |                                                                                                                                                                                                               |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

| R = Reada  |                                                                                                                                                                                                               | W = Writable                                                                                                                                 |                |                   | nented bit, rea |                 |       |  |  |  |  |  |  |

| -n = Value | at POR                                                                                                                                                                                                        | '1' = Bit is set                                                                                                                             |                | '0' = Bit is clea | ared            | x = Bit is unkn | nown  |  |  |  |  |  |  |

| bit 7      | IDI EN: Idle F                                                                                                                                                                                                | nahle hit                                                                                                                                    |                |                   |                 |                 |       |  |  |  |  |  |  |

|            | IDLEN: Idle Enable bit<br>1 = Device enters Idle mode on SLEEP instruction                                                                                                                                    |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            |                                                                                                                                                                                                               | 0 = Device enters Sleep mode on SLEEP instruction                                                                                            |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 6-4    | IRCF2:IRCF0                                                                                                                                                                                                   | : Internal Osci                                                                                                                              | llator Frequen | cy Select bits    |                 |                 |       |  |  |  |  |  |  |

|            |                                                                                                                                                                                                               | 111 = 8 MHz (INTOSC drives clock directly)                                                                                                   |                |                   |                 |                 |       |  |  |  |  |  |  |

|            | 110 = 4 MHz                                                                                                                                                                                                   |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            | 101 = 2  MHz<br>$100 = 1 \text{ MHz}^{(3)}$                                                                                                                                                                   |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            | 011 = 500  kH                                                                                                                                                                                                 |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            | 010 <b>= 250</b> kHz                                                                                                                                                                                          |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            | 001 = 125 kHz                                                                                                                                                                                                 |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            |                                                                                                                                                                                                               | 000 = 31 kHz (from either INTOSC/256 or INTRC directly) <sup>(2)</sup><br>OSTS: Oscillator Start-up Timer Time-out Status bit <sup>(1)</sup> |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 3      |                                                                                                                                                                                                               |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            | <ul> <li>1 = Oscillator Start-up Timer (OST) time-out has expired; primary oscillator is running</li> <li>0 = Oscillator Start-up Timer (OST) time-out is running; primary oscillator is not ready</li> </ul> |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 2      |                                                                                                                                                                                                               | C Frequency S                                                                                                                                |                | , p               | innary ocomate  | i le liet leady |       |  |  |  |  |  |  |

|            |                                                                                                                                                                                                               | frequency is st                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            | 0 = INTOSC frequency is not stable                                                                                                                                                                            |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 1-0    | SCS1:SCS0:                                                                                                                                                                                                    | System Clock                                                                                                                                 | Select bits    |                   |                 |                 |       |  |  |  |  |  |  |

|            | 1x = Internal oscillator block                                                                                                                                                                                |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

|            |                                                                                                                                                                                                               | ary (Timer1) os                                                                                                                              | cillator       |                   |                 |                 |       |  |  |  |  |  |  |

|            | 00 = Primary                                                                                                                                                                                                  | oscillator                                                                                                                                   |                |                   |                 |                 |       |  |  |  |  |  |  |

| Note 1:    | Reset state deper                                                                                                                                                                                             | nds on state of                                                                                                                              | the IESO Cor   | figuration bit.   |                 |                 |       |  |  |  |  |  |  |

|            | Source selected b                                                                                                                                                                                             | -                                                                                                                                            |                | -                 |                 |                 |       |  |  |  |  |  |  |

| 3:         | Default output fre                                                                                                                                                                                            | quency of INT                                                                                                                                | OSC on Reset   |                   |                 |                 |       |  |  |  |  |  |  |

|            |                                                                                                                                                                                                               |                                                                                                                                              |                |                   |                 |                 |       |  |  |  |  |  |  |

### REGISTER 2-2: OSCCON: OSCILLATOR CONTROL REGISTER

### 5.4 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 5.5 "Data Memory and the Extended Instruction Set" for more information.

The data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.5.1 "Indexed Addressing with Literal Offset**".

## 5.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 5.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 5.3.3 "General Purpose Register File") or a location in the Access Bank (Section 5.3.2 "Access Bank") as the data source for the instruction. The Access RAM bit, 'a', determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

### 5.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

#### EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|          | LFSR  | FSR0, 100h | ; |                |

|----------|-------|------------|---|----------------|

| NEXT     | CLRF  | POSTINC0   |   | Clear INDF     |

|          |       |            | ; | register then  |

|          |       |            | ; | inc pointer    |

|          | BTFSS | FSROH, 1   | ; | All done with  |

|          |       |            | ; | Bank1?         |

|          | BRA   | NEXT       | ; | NO, clear next |

| CONTINUE | Ξ     |            | ; | YES, continue  |

|          |       |            |   |                |

| R/W-1                                                                                                                           | R/W-1                                                                                   | R/W-1                             | R/W-1             | U-0               | R/W-1  | U-0            | R/W-1 |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------|-------------------|-------------------|--------|----------------|-------|--|--|--|

| RBPU                                                                                                                            | INTEDG0                                                                                 | INTEDG1                           | INTEDG2           | —                 | TMR0IP | _              | RBIP  |  |  |  |

| bit 7                                                                                                                           |                                                                                         |                                   |                   |                   |        |                | bit 0 |  |  |  |

|                                                                                                                                 |                                                                                         |                                   |                   |                   |        |                |       |  |  |  |

| Legend:                                                                                                                         |                                                                                         |                                   |                   |                   |        |                |       |  |  |  |

| R = Readable                                                                                                                    | e bit                                                                                   | nented bit, read                  | d as '0'          |                   |        |                |       |  |  |  |

| -n = Value at                                                                                                                   | POR                                                                                     | '1' = Bit is set                  |                   | '0' = Bit is clea | ared   | x = Bit is unk | nown  |  |  |  |

| bit 7 <b>RBPU:</b> PORTB Pull-up Enable bit                                                                                     |                                                                                         |                                   |                   |                   |        |                |       |  |  |  |

| <ul> <li>1 = All PORTB pull-ups are disabled</li> <li>0 = PORTB pull-ups are enabled by individual port latch values</li> </ul> |                                                                                         |                                   |                   |                   |        |                |       |  |  |  |

| bit 6 INTEDG0: External Interrupt 0 Edge Select bit                                                                             |                                                                                         |                                   |                   |                   |        |                |       |  |  |  |

|                                                                                                                                 | <ul> <li>1 = Interrupt on rising edge</li> <li>0 = Interrupt on falling edge</li> </ul> |                                   |                   |                   |        |                |       |  |  |  |

| bit 5                                                                                                                           | •                                                                                       | ternal Interrupt                  | 1 Edge Selec      | t bit             |        |                |       |  |  |  |

|                                                                                                                                 |                                                                                         | on rising edge<br>on falling edge | C C               |                   |        |                |       |  |  |  |

| bit 4                                                                                                                           | INTEDG2: Ex                                                                             | ternal Interrupt                  | 2 Edge Selec      | t bit             |        |                |       |  |  |  |

|                                                                                                                                 |                                                                                         | on rising edge<br>on falling edge |                   |                   |        |                |       |  |  |  |

| bit 3                                                                                                                           |                                                                                         | ted: Read as '                    | )'                |                   |        |                |       |  |  |  |

| bit 2                                                                                                                           | •                                                                                       | R0 Overflow Int                   |                   | bit               |        |                |       |  |  |  |

|                                                                                                                                 | 1 = High prio                                                                           |                                   |                   |                   |        |                |       |  |  |  |

|                                                                                                                                 | 0 = Low prior                                                                           | rity                              |                   |                   |        |                |       |  |  |  |

| bit 1                                                                                                                           | Unimplemen                                                                              | ted: Read as '                    | )'                |                   |        |                |       |  |  |  |

| bit 0                                                                                                                           | RBIP: RB Po                                                                             | rt Change Inter                   | rupt Priority bit | :                 |        |                |       |  |  |  |

|                                                                                                                                 | 1 = High prio                                                                           | rity                              |                   |                   |        |                |       |  |  |  |

|                                                                                                                                 | 0 = Low prior                                                                           | ritv                              |                   |                   |        |                |       |  |  |  |

### REGISTER 10-2: INTCON2: INTERRUPT CONTROL REGISTER 2

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

### 12.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 12-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | D R-0 R/W-0              |  | R/W-0   | R/W-0  | R/W-0  | R/W-0  |       |

|-------|--------------------------|--|---------|--------|--------|--------|-------|

| RD16  | 16 T1RUN T1CKPS1 T1CKPS0 |  | T1OSCEN | T1SYNC | TMR1CS | TMR10N |       |

| bit 7 |                          |  |         |        |        |        | bit 0 |

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:       |                                           |                                                                                                              |                                                              |                    |

|---------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|

| R = Readabl   | le bit                                    | W = Writable bit                                                                                             | U = Unimplemented bit                                        | , read as '0'      |

| -n = Value at | t POR                                     | '1' = Bit is set                                                                                             | '0' = Bit is cleared                                         | x = Bit is unknown |

| bit 7         | <b>RD16:</b> 16-                          | Bit Read/Write Mode Enab                                                                                     | le bit                                                       |                    |

|               |                                           | -                                                                                                            | ner1 in one 16-bit operation<br>ner1 in two 8-bit operations |                    |

| bit 6         | T1RUN: Ti                                 | mer1 System Clock Status                                                                                     | bit                                                          |                    |

|               |                                           | e clock is derived from Time<br>e clock is derived from ano                                                  |                                                              |                    |

| bit 5-4       | 11 = 1:8 P<br>10 = 1:4 P<br>01 = 1:2 P    | T1CKPS0: Timer1 Input C<br>rescale value<br>rescale value<br>rescale value<br>rescale value<br>rescale value | lock Prescale Select bits                                    |                    |

| bit 3         | 1 = Timer1<br>0 = Timer1                  | : Timer1 Oscillator Enable<br>oscillator is enabled<br>oscillator is shut off<br>tor inverter and feedback r | bit<br>esistor are turned off to elimina                     | ate power drain.   |

| bit 2         | T1SYNC:<br>When TMF                       | •                                                                                                            | t Synchronization Select bit                                 |                    |

|               | 1 = Do not                                | synchronize external clock                                                                                   | < input                                                      |                    |

|               | <u>When TMF</u><br>This bit is i          |                                                                                                              | iternal clock when TMR1CS =                                  | 0.                 |

| bit 1         | 1 = Extern                                | Timer1 Clock Source Sele<br>al clock from pin RC0/T1C<br>al clock (Fosc/4)                                   | ct bit<br>DSO/T13CKI (on the rising edg                      | e)                 |

| bit 0         | <b>TMR1ON:</b><br>1 = Enable<br>0 = Stops |                                                                                                              |                                                              |                    |

|               |                                           |                                                                                                              |                                                              |                    |

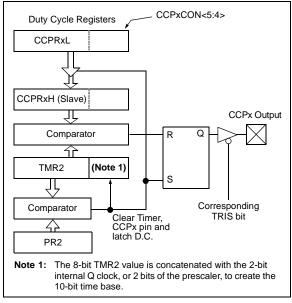

### 15.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP2 pin is multiplexed with a PORTB or PORTC data latch, the appropriate TRIS bit must be cleared to make the CCP2 pin an output.

| Note: | Clearing the CCP2CON register will force<br>the RB3 or RC1 output latch (depending on<br>device configuration) to the default low |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

|       | level. This is not the PORTB or PORTC I/O                                                                                         |

|       | data latch.                                                                                                                       |

Figure 15-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 15.4.4** "Setup for PWM Operation".

### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

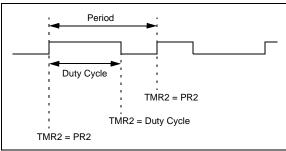

A PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 15-4: PWM OUTPUT

### 15.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

### **EQUATION 15-1:**

$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set (exception: if PWM duty cycle = 0%, the CCPx pin will not be set)

- The PWM duty cycle is latched from CCPRxL into CCPRxH

### 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPRxL register and to the CCPxCON<5:4> bits. Up to 10-bit resolution is available. The CCPRxL contains the eight MSbs and the CCPxCON<5:4> contains the two LSbs. This 10-bit value is represented by CCPRxL:CCPxCON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

### **EQUATION 15-2:**

```

PWM Duty Cycle = (CCPRxL:CCPxCON<5:4>) •

Tosc • (TMR2 Prescale Value)

```

CCPRxL and CCPxCON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR2H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPRxH is a read-only register.

| R/W-0         | R/W-0                                                                                                                                     | R/W-0                                                                       | R/W-0                                                                              | R/W-0                                                  | R/W-0                                     | R/W-0           | R/W-0          |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|-----------------|----------------|--|--|--|--|

| WCOL          | SSPOV                                                                                                                                     | SSPEN <sup>(1)</sup>                                                        | CKP                                                                                | SSPM3                                                  | SSPM2                                     | SSPM1           | SSPM0          |  |  |  |  |

| bit 7         |                                                                                                                                           |                                                                             |                                                                                    |                                                        |                                           |                 | bit            |  |  |  |  |

| Lonondi       |                                                                                                                                           |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

| Legend:       |                                                                                                                                           |                                                                             | .,                                                                                 |                                                        |                                           |                 |                |  |  |  |  |

| R = Readabl   |                                                                                                                                           | W = Writable k                                                              | Dit                                                                                | -                                                      | nented bit, read                          |                 |                |  |  |  |  |

| -n = Value at | t POR                                                                                                                                     | '1' = Bit is set                                                            |                                                                                    | '0' = Bit is clea                                      | ared                                      | x = Bit is unkr | nown           |  |  |  |  |

| bit 7         | WCOL: Write                                                                                                                               | e Collision Detec                                                           | t bit                                                                              |                                                        |                                           |                 |                |  |  |  |  |

|               | In Master Tra                                                                                                                             |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               |                                                                                                                                           | to the SSPBUF                                                               |                                                                                    |                                                        |                                           | nditions were i | not valid for  |  |  |  |  |

|               |                                                                                                                                           | sion to be starte                                                           | d (must be cl                                                                      | eared in softwa                                        | re)                                       |                 |                |  |  |  |  |

|               | 0 = No  collis                                                                                                                            |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               | In Slave Tran                                                                                                                             | PBUF register is                                                            | written while                                                                      | it is still transm                                     | itting the previo                         | ous word (mus   | t he cleared i |  |  |  |  |

|               | software                                                                                                                                  |                                                                             |                                                                                    |                                                        | intering the provide                      |                 |                |  |  |  |  |

|               | 0 = No collis                                                                                                                             | ion                                                                         |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               |                                                                                                                                           | ode (Master or S                                                            | <u>Slave modes)</u>                                                                | <u>:</u>                                               |                                           |                 |                |  |  |  |  |

|               | This is a "dor                                                                                                                            | n't care" bit.                                                              |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

| bit 6         |                                                                                                                                           | eive Overflow Ir                                                            | dicator bit                                                                        |                                                        |                                           |                 |                |  |  |  |  |

|               | In Receive m                                                                                                                              |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               | <ul> <li>1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in<br/>software)</li> </ul> |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               | 0 = No overf                                                                                                                              | /                                                                           |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               | In Transmit n                                                                                                                             | node:                                                                       |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               |                                                                                                                                           | n't care" bit in Tra                                                        | ansmit mode.                                                                       |                                                        |                                           |                 |                |  |  |  |  |

| bit 5         | SSPEN: Mas                                                                                                                                | ster Synchronous                                                            | s Serial Port E                                                                    | Enable bit <sup>(1)</sup>                              |                                           |                 |                |  |  |  |  |

|               | 1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins                                                   |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               | 0 = Disables                                                                                                                              | serial port and c                                                           | onfigures the                                                                      | se pins as I/O p                                       | oort pins                                 |                 |                |  |  |  |  |

| bit 4         | CKP: SCK R                                                                                                                                | elease Control b                                                            | oit                                                                                |                                                        |                                           |                 |                |  |  |  |  |

|               | In Slave mode:                                                                                                                            |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               | 1 = Releases clock                                                                                                                        |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               | 0 = Holds clock low (clock stretch), used to ensure data setup time                                                                       |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               | In Master mode:<br>Unused in this mode.                                                                                                   |                                                                             |                                                                                    |                                                        |                                           |                 |                |  |  |  |  |

|               |                                                                                                                                           |                                                                             |                                                                                    |                                                        | (0)                                       |                 |                |  |  |  |  |

| bit 3-0       | SSPM3:SSP                                                                                                                                 | M0: Master Svn                                                              | chronous Ser                                                                       | ial Port Mode S                                        | elect bits <sup>(2)</sup>                 |                 |                |  |  |  |  |

| bit 3-0       |                                                                                                                                           | <b>M0:</b> Master Syn<br>Slave mode, 10-b                                   |                                                                                    |                                                        |                                           | enabled         |                |  |  |  |  |

| bit 3-0       | $1111 = I^2 C S$<br>$1110 = I^2 C S$                                                                                                      | Slave mode, 10-b<br>Slave mode, 7-bi                                        | oit address wi<br>t address with                                                   | th Start and Ston<br>Start and Stop                    | p bit interrupts<br>bit interrupts e      |                 |                |  |  |  |  |

| bit 3-0       | $1111 = I^2CS$<br>$1110 = I^2CS$<br>$1011 = I^2CF$                                                                                        | Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Contro                     | oit address wi<br>t address with<br>lled Master m                                  | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                 |                |  |  |  |  |

| bit 3-0       | $1111 = I^{2}C S$<br>$1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C N$                                                          | Blave mode, 10-b<br>Blave mode, 7-bi<br>Firmware Contro<br>Master mode, clo | bit address wi<br>t address with<br>lled Master m<br>lock = FOSC/(4                | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                 |                |  |  |  |  |

| bit 3-0       | $1111 = I^{2}C S$<br>$1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C N$<br>$0111 = I^{2}C S$                                     | Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Contro                     | bit address wi<br>t address with<br>lled Master m<br>lock = Fosc/(4<br>bit address | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                 |                |  |  |  |  |

### REGISTER 17-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

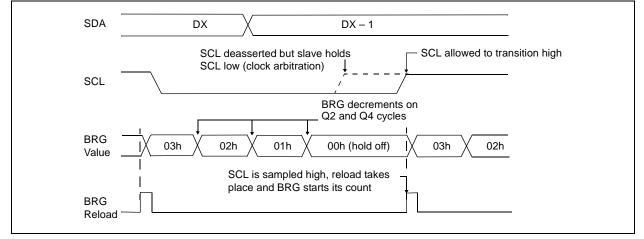

### 17.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 17-18).

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | l = 0, BRO            | <b>G16 =</b> 0 |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc                  | = 40.000   | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |                |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | —                     | _          | _                           |                       | _          | _                           | _                     |                | _                           | _                     | _          | _                           |

| 1.2         | —                     | —          | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16           | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4         | 2.441                 | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16           | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6         | 9.615                 | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73           | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2        | 19.531                | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73           | 7                           | _                     | _          | _                           |

| 57.6        | 56.818                | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58          | 2                           | —                     | _          | _                           |

| 115.2       | 125.000               | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18         | 1                           | _                     | —          | —                           |

#### TABLE 18-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|--|

| BAUD<br>RATE | Fos                   | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |  |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |  |

| 0.3          | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | —                           |  |  |  |  |  |

| 9.6          | 8.929                 | -6.99                         | 6                           | _                     | _          | —                           | _                     | _          | —                           |  |  |  |  |  |

| 19.2         | 20.833                | 8.51                          | 2                           | —                     | _          | _                           | —                     | —          | —                           |  |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 0                           | —                     | _          | _                           | —                     | —          | —                           |  |  |  |  |  |

| 115.2        | 62.500                | -45.75                        | 0                           | —                     | —          | —                           | —                     | —          | —                           |  |  |  |  |  |

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | l = 1, BRG            | <b>16 =</b> 0 |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|---------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc                  | = 40.000   | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |               |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     | _          | —                           | _                     | _          | _                           | _                     | _             | _                           |                       | _          | _                           |

| 1.2         | —                     | _          | —                           | —                     | —          | _                           | —                     |               | _                           | —                     | —          | —                           |

| 2.4         | —                     | _          | —                           | —                     | _          | _                           | 2.441                 | 1.73          | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6         | 9.766                 | 1.73       | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16          | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2        | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73          | 31                          | 19.230                | -0.16      | 25                          |

| 57.6        | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36         | 10                          | 55.555                | 3.55       | 8                           |

| 115.2       | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51          | 4                           | —                     | _          | _                           |

|       | <b>SYNC</b> = 0, <b>BRGH</b> = 1, <b>BRG16</b> = 0 |            |                             |                       |            |                             |                       |            |                             |

|-------|----------------------------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fosc = 4.000 MHz                                   |            |                             | Fosc = 2.000 MHz      |            |                             | Fosc = 1.000 MHz      |            |                             |

| (K)   | Actual<br>Rate<br>(K)                              | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | _                                                  |            | _                           | _                     | _          | _                           | 0.300                 | -0.16      | 207                         |

| 1.2   | 1.202                                              | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |

| 2.4   | 2.404                                              | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |

| 9.6   | 9.615                                              | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | —                     | —          | —                           |

| 19.2  | 19.231                                             | 0.16       | 12                          | _                     | _          | —                           | _                     | _          | —                           |

| 57.6  | 62.500                                             | 8.51       | 3                           | —                     | —          | —                           | —                     | —          | —                           |

| 115.2 | 125.000                                            | 8.51       | 1                           | _                     | —          | —                           | —                     | —          | —                           |

© 2008 Microchip Technology Inc.

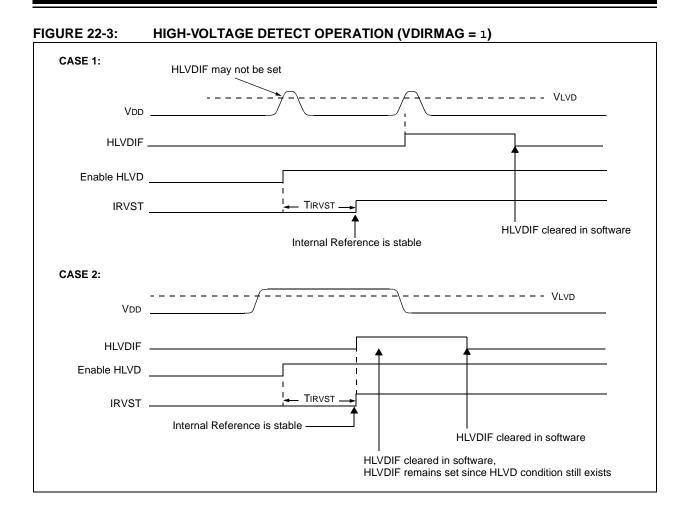

### 22.5 Applications

In many applications, the ability to detect a drop below or rise above a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect a Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

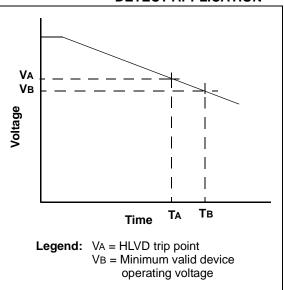

For general battery applications, Figure 22-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

#### TYPICAL LOW-VOLTAGE DETECT APPLICATION

### 22.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

### 22.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG  | _         | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 50                         |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR2    | OSCFIF   | CMIF      | —      | EEIF   | BCLIF  | HLVDIF | TMR3IF | CCP2IF | 52                         |

| PIE2    | OSCFIE   | CMIE      | —      | EEIE   | BCLIE  | HLVDIE | TMR3IE | CCP2IE | 52                         |

| IPR2    | OSCFIP   | CMIP      |        | EEIP   | BCLIP  | HLVDIP | TMR3IP | CCP2IP | 52                         |

#### TABLE 22-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

### 24.0 INSTRUCTION SET SUMMARY

PIC18F2525/2620/4525/4620 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions, for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

### 24.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- **Bit-oriented** operations

- Literal operations

- Control operations

The PIC18 instruction set summary in Table 24-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 24-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands: