Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2620-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0      | R/W-1                      | R/W-0            | R/W-0            | R <sup>(1)</sup>                      | R-0             | R/W-0           | R/W-0 |

|------------|----------------------------|------------------|------------------|---------------------------------------|-----------------|-----------------|-------|

| IDLEN      | IRCF2                      | IRCF1            | IRCF0            | OSTS                                  | IOFS            | SCS1            | SCS0  |

| bit 7      | ·                          |                  |                  |                                       |                 | •               | bit ( |

|            |                            |                  |                  |                                       |                 |                 |       |

| Legend:    |                            |                  |                  |                                       |                 |                 |       |

| R = Reada  |                            | W = Writable     |                  |                                       | nented bit, rea |                 |       |

| -n = Value | at POR                     | '1' = Bit is set |                  | '0' = Bit is clea                     | ared            | x = Bit is unkn | nown  |

| bit 7      | IDLEN: Idle E              | nahle hit        |                  |                                       |                 |                 |       |

|            |                            | nters Idle mod   | ON SLEEP in      | struction                             |                 |                 |       |

|            |                            | nters Sleep mo   |                  |                                       |                 |                 |       |

| bit 6-4    | IRCF2:IRCF0                | : Internal Osci  | llator Frequen   | cy Select bits                        |                 |                 |       |

|            |                            | (INTOSC drive    | es clock directl | y)                                    |                 |                 |       |

|            | 110 = 4 MHz                |                  |                  |                                       |                 |                 |       |

|            | 101 = 2 MHz<br>100 = 1 MHz | (3)              |                  |                                       |                 |                 |       |

|            | 011 = 500  kH              |                  |                  |                                       |                 |                 |       |

|            | 010 <b>= 250 k</b> H       |                  |                  |                                       |                 |                 |       |

|            | 001 = <b>125 k</b> H       |                  |                  |                                       | (2)             |                 |       |

|            |                            | -                |                  | INTRC directly                        | )(2)            |                 |       |

| bit 3      |                            | ator Start-up Ti |                  |                                       |                 |                 |       |

|            |                            | •                | · ·              | out has expired;<br>out is running; p | • •             | •               |       |

| bit 2      |                            | C Frequency S    |                  | , p                                   | innary ocomate  | i le liet leady |       |

|            |                            | frequency is st  |                  |                                       |                 |                 |       |

|            |                            | frequency is n   |                  |                                       |                 |                 |       |

| bit 1-0    | SCS1:SCS0:                 | System Clock     | Select bits      |                                       |                 |                 |       |

|            |                            | oscillator block | -                |                                       |                 |                 |       |

|            |                            | ary (Timer1) os  | cillator         |                                       |                 |                 |       |

|            | 00 = Primary               | oscillator       |                  |                                       |                 |                 |       |

| Note 1:    | Reset state deper          | nds on state of  | the IESO Cor     | figuration bit.                       |                 |                 |       |

|            | Source selected b          | -                |                  | -                                     |                 |                 |       |

| 3:         | Default output fre         | quency of INT    | OSC on Reset     |                                       |                 |                 |       |

|            |                            |                  |                  |                                       |                 |                 |       |

### REGISTER 2-2: OSCCON: OSCILLATOR CONTROL REGISTER

| File Name | Bit 7                                                                                                      | Bit 6                 | Bit 5          | Bit 4         | Bit 3           | Bit 2         | Bit 1            | Bit 0       | Value on POR, BOR | Details on<br>page: |

|-----------|------------------------------------------------------------------------------------------------------------|-----------------------|----------------|---------------|-----------------|---------------|------------------|-------------|-------------------|---------------------|

| TOSU      | _                                                                                                          | _                     | _              | Top-of-Stack  | Upper Byte (T   | OS<20:16>)    |                  |             | 0 0000            | 49, 54              |

| TOSH      | Top-of-Stack                                                                                               | High Byte (TO         | S<15:8>)       | •             |                 |               |                  |             | 0000 0000         | 49, 54              |

| TOSL      | Top-of-Stack                                                                                               | Low Byte (TO          | S<7:0>)        |               |                 |               |                  |             | 0000 0000         | 49, 54              |

| STKPTR    | STKFUL <sup>(6)</sup>                                                                                      | STKUNF <sup>(6)</sup> | —              | SP4           | SP3             | SP2           | SP1              | SP0         | 00-0 0000         | 49, 55              |

| PCLATU    | _                                                                                                          | _                     | -              | Holding Regi  | ister for PC<20 | :16>          |                  |             | 0 0000            | 49, 54              |

| PCLATH    | Holding Regis                                                                                              | ster for PC<15        | :8>            |               |                 |               |                  |             | 0000 0000         | 49, 54              |

| PCL       | PC Low Byte                                                                                                | (PC<7:0>)             |                |               |                 |               |                  |             | 0000 0000         | 49, 54              |

| TBLPTRU   | _                                                                                                          | _                     | bit 21         | Program Me    | mory Table Poi  | nter Upper By | te (TBLPTR<20    | ):16>)      | 00 0000           | 49, 82              |

| TBLPTRH   | Program Mer                                                                                                | nory Table Poi        | nter High Byte | e (TBLPTR<1   | 5:8>)           |               |                  |             | 0000 0000         | 49, 82              |

| TBLPTRL   | Program Mer                                                                                                | nory Table Poi        | nter Low Byte  | (TBLPTR<7:    | 0>)             |               |                  |             | 0000 0000         | 49, 82              |

| TABLAT    | Program Mer                                                                                                | nory Table Lat        | ch             |               |                 |               |                  |             | 0000 0000         | 49, 82              |

| PRODH     | Product Regi                                                                                               | ster High Byte        |                |               |                 |               |                  |             | xxxx xxxx         | 49, 89              |

| PRODL     | Product Regi                                                                                               | ster Low Byte         |                |               |                 |               |                  |             | xxxx xxxx         | 49, 89              |

| INTCON    | GIE/GIEH                                                                                                   | PEIE/GIEL             | TMR0IE         | INTOIE        | RBIE            | TMR0IF        | <b>INT0IF</b>    | RBIF        | 0000 000x         | 49, 111             |

| INTCON2   | RBPU                                                                                                       | INTEDG0               | INTEDG1        | INTEDG2       | _               | TMR0IP        | _                | RBIP        | 1111 -1-1         | 49, 112             |

| INTCON3   | INT2IP                                                                                                     | INT1IP                |                | INT2IE        | INT1IE          | -             | INT2IF           | INT1IF      | 11-0 0-00         | 49, 113             |

| INDF0     | Uses contents of FSR0 to address data memory – value of FSR0 not changed (not a physical register)         |                       |                |               |                 |               |                  | ter)        | N/A               | 49, 68              |

| POSTINC0  | U Uses contents of FSR0 to address data memory – value of FSR0 post-incremented (not a physical register)  |                       |                |               |                 |               |                  | register)   | N/A               | 49, 68              |

| POSTDEC0  | C0 Uses contents of FSR0 to address data memory – value of FSR0 post-decremented (not a physical register) |                       |                |               |                 |               | N/A              | 49, 68      |                   |                     |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)     |                       |                |               |                 |               | N/A              | 49, 68      |                   |                     |

| PLUSW0    | Uses content value of FSR                                                                                  |                       | ddress data n  | nemory – valu | e of FSR0 pre-  | incremented ( | not a physical r | egister) –  | N/A               | 49, 68              |

| FSR0H     |                                                                                                            |                       |                | —             | Indirect Data   | Memory Addr   | ess Pointer 0 H  | igh Byte    | 0000              | 49, 68              |

| FSR0L     | Indirect Data                                                                                              | Memory Addre          | ess Pointer 0  | Low Byte      |                 |               |                  |             | xxxx xxxx         | 49, 68              |

| WREG      | Working Regi                                                                                               | ster                  |                |               |                 |               |                  |             | xxxx xxxx         | 49                  |

| INDF1     | Uses content                                                                                               | s of FSR1 to a        | ddress data n  | nemory – valu | e of FSR1 not   | changed (not  | a physical regis | ter)        | N/A               | 49, 68              |

| POSTINC1  | Uses content                                                                                               | s of FSR1 to a        | ddress data n  | nemory – valu | e of FSR1 pos   | t-incremented | (not a physical  | register)   | N/A               | 49, 68              |

| POSTDEC1  | Uses content                                                                                               | s of FSR1 to a        | ddress data n  | nemory – valu | e of FSR1 pos   | t-decremented | l (not a physica | l register) | N/A               | 49, 68              |

| PREINC1   | Uses content                                                                                               | s of FSR1 to a        | ddress data n  | nemory – valu | e of FSR1 pre-  | incremented ( | not a physical r | egister)    | N/A               | 49, 68              |

| PLUSW1    | Uses content<br>value of FSR                                                                               |                       | ddress data n  | nemory – valu | e of FSR1 pre-  | incremented ( | not a physical r | egister) –  | N/A               | 49, 68              |

| FSR1H     | -                                                                                                          | —                     | -              | —             | Indirect Data   | Memory Addr   | ess Pointer 1 H  | igh Byte    | 0000              | 50, 68              |

| FSR1L     | Indirect Data                                                                                              | Memory Addre          | ess Pointer 1  | Low Byte      |                 |               |                  |             | xxxx xxxx         | 50, 68              |

| BSR       |                                                                                                            |                       |                | —             | Bank Select I   | Register      |                  |             | 0000              | 50, 59              |

| INDF2     | Uses content                                                                                               | s of FSR2 to a        | ddress data n  | nemory – valu | e of FSR2 not   | changed (not  | a physical regis | ter)        | N/A               | 50, 68              |

| POSTINC2  | Uses content                                                                                               | s of FSR2 to a        | ddress data n  | nemory – valu | e of FSR2 pos   | t-incremented | (not a physical  | register)   | N/A               | 50, 68              |

| POSTDEC2  | Uses content                                                                                               | s of FSR2 to a        | ddress data n  | nemory – valu | e of FSR2 pos   | t-decremented | l (not a physica | l register) | N/A               | 50, 68              |

| PREINC2   | Uses content                                                                                               | s of FSR2 to a        | ddress data n  | nemory – valu | e of FSR2 pre-  | incremented ( | not a physical r | egister)    | N/A               | 50, 68              |

| PLUSW2    | Uses content<br>value of FSR                                                                               |                       | ddress data n  | nemory – valu | e of FSR2 pre-  | incremented ( | not a physical r | egister) –  | N/A               | 50, 68              |

| FSR2H     | _                                                                                                          | _                     | _              | _             | Indirect Data   | Memory Addr   | ess Pointer 2 H  | igh Byte    | 0000              | 50, 68              |

| FSR2L     | Indirect Data                                                                                              | Memory Addre          | ess Pointer 2  | Low Byte      |                 |               |                  |             | XXXX XXXX         | 50, 68              |

|           |                                                                                                            |                       |                |               |                 |               |                  |             |                   |                     |

#### TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2525/2620/4525/4620)

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition**Note 1:**The SBOREN bit is only available when the BOREN1:BOREN0 Configuration bits =

1: The SBOREN bit is only available when the BOREN1:BOREN0 Configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

3: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

4: The RE3 bit is only available when Master Clear Reset is disabled (MCLRE Configuration bit = 0); otherwise, RE3 reads as '0'. This bit is read-only.

5: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

6: Bit 7 and bit 6 are cleared by user software or by a POR.

### 16.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

| Note: | The ECCP module is implemented only in |

|-------|----------------------------------------|

|       | 40/44-pin devices.                     |

In PIC18F4525/4620 devices, CCP1 is implemented as a standard CCP module with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown and restart. The Enhanced features are discussed in detail in **Section 16.4** "Enhanced PWM Mode". Capture, Compare and single-output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 16-1. It differs from the CCPxCON registers in PIC18F2525/2620 devices in that the two Most Significant bits are implemented to control PWM functionality.

### REGISTER 16-1: CCP1CON: ECCP CONTROL REGISTER (40/44-PIN DEVICES)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:    |                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                        |                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| R = Reada  | able bit                                                                                                                                                                        | W = Writable bit                                                                                                                                                                                                                                                                   | U = Unimplemented bit,                                                                                                                                                                                                                                                                 | read as '0'                                                |

| -n = Value | at POR                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                   | '0' = Bit is cleared                                                                                                                                                                                                                                                                   | x = Bit is unknown                                         |

| bit 7-6    | <u>If CCP1M</u><br>xx = P1A<br><u>If CCP1M</u><br>00 = Sing<br>01 = Full-<br>10 = Half                                                                                          | <u>3:CCP1M2 = 11:</u><br>le output, P1A modulated; P<br>bridge output forward, P1D n<br>-bridge output, P1A, P1B mo                                                                                                                                                                | re input/output; P1B, P1C, P1I<br>1B, P1C, P1D assigned as por<br>nodulated; P1A active; P1B, P                                                                                                                                                                                        | t pins<br>1C inactive<br>I; P1C, P1D assigned as port pins |

| bit 5-4    | <u>Capture r</u><br>Unused.<br><u>Compare</u><br>Unused.<br><u>PWM mo</u>                                                                                                       | mode:<br>de:                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                        | //Sbs of the duty cycle are found in                       |

| bit 3-0    | CCP1M3:<br>0000 = C<br>0001 = F<br>0010 = C<br>0011 = C<br>0100 = C<br>0110 = C<br>1000 = C<br>1001 = C<br>1010 = C<br>1010 = C<br>1011 = C<br>1001 = P<br>1101 = P<br>1110 = P | Compare mode, toggle output<br>Capture mode<br>Capture mode, every falling ed<br>Capture mode, every rising ed<br>Capture mode, every 4th rising<br>Capture mode, every 16th rising<br>Compare mode, initialize CCP<br>Compare mode, initialize CCP<br>Compare mode, generate soft | esets ECCP module)<br>on match<br>dge<br>lge<br>g edge<br>I pin low; set output on compare<br>I pin low; set output on comp<br>ware interrupt only; CCP1 pin r<br>al event (ECCP resets TMR1 o<br>high; P1B, P1D active-high<br>high; P1B, P1D active-low<br>low; P1B, P1D active-high | everts to I/O state                                        |

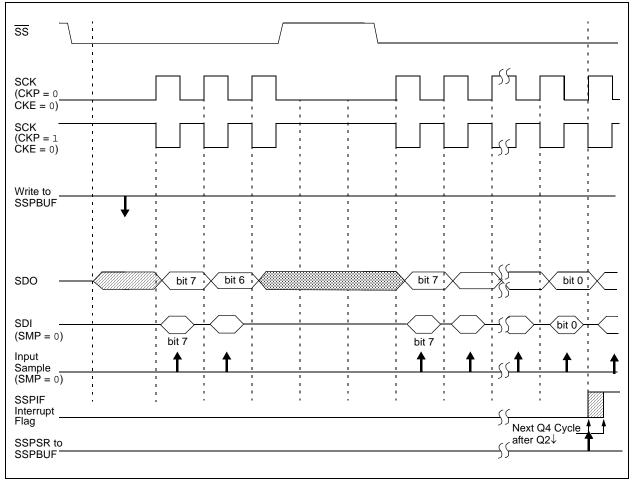

### 17.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit (SSPCON1<4>).

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

### 17.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI operation must be in Slave mode with the  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the

SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When     | the SP  | l interfa | ace is in Sla | ave mode |

|---------|----------|---------|-----------|---------------|----------|

|         | with     | SS      | pin       | control       | enabled  |

|         | (SSPC    | ON1<3   | 8:0> =    | 0100), the    | SPI mod- |

|         | ule will | reset i | f the S   | S pin is set  | to VDD.  |

2: If the SPI interface is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

### FIGURE 17-4: SLAVE SYNCHRONIZATION WAVEFORM

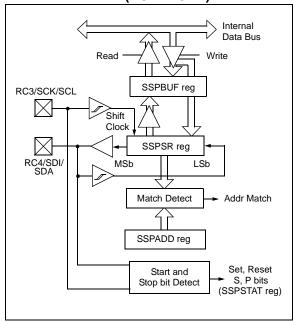

## 17.4 I<sup>2</sup>C Mode

The MSSP module in  $I^2C$  mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCL) RC3/SCK/SCL

- Serial data (SDA) RC4/SDI/SDA

The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

#### FIGURE 17-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

### 17.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON1, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON1 and SSPCON2 registers are readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPADD act as the Baud Rate Generator reload value.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

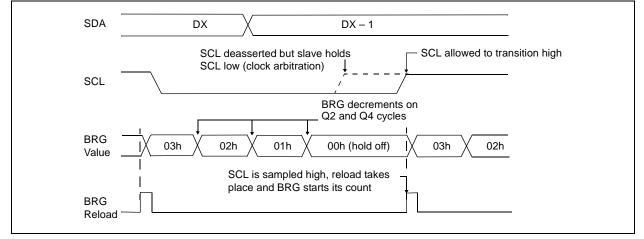

### 17.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 17-18).

### 18.0 ENHANCED UNIVERSAL SYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT as a USART:

- SPEN bit (RCSTA<7>) must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be set (= 1)

| Note: | The EUSART control will automatically                  |

|-------|--------------------------------------------------------|

|       | reconfigure the pin from input to output as<br>needed. |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 18-1, Register 18-2 and Register 18-3, respectively.

### 18.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 18.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG register.

- c) Flag bit, TXIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit, TXIF, will now be set.

- e) If enable bit, TXIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name                                                 | Bit 7                | Bit 6        | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|------------------------------------------------------|----------------------|--------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON                                               | GIE/GIEH             | PEIE/GIEL    | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR1                                                 | PSPIF <sup>(1)</sup> | ADIF         | RCIF        | TXIF         | SSPIF | CCP1IF | TMR2IF | TMR1IF | 52                         |

| PIE1                                                 | PSPIE <sup>(1)</sup> | ADIE         | RCIE        | TXIE         | SSPIE | CCP1IE | TMR2IE | TMR1IE | 52                         |

| IPR1                                                 | PSPIP <sup>(1)</sup> | ADIP         | RCIP        | TXIP         | SSPIP | CCP1IP | TMR2IP | TMR1IP | 52                         |

| RCSTA                                                | SPEN                 | RX9          | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 51                         |

| TXREG                                                | EUSART T             | ransmit Regi | ster        |              |       |        |        |        | 51                         |

| TXSTA                                                | CSRC                 | TX9          | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 51                         |

| BAUDCON                                              | ABDOVF               | RCIDL        | RXDTP       | TXCKP        | BRG16 | —      | WUE    | ABDEN  | 51                         |

| SPBRGH EUSART Baud Rate Generator Register High Byte |                      |              |             |              |       |        | 51     |        |                            |

| SPBRG                                                | EUSART B             | aud Rate Ge  | enerator Re | gister Low I | Byte  |        |        |        | 51                         |

### TABLE 18-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

NOTES:

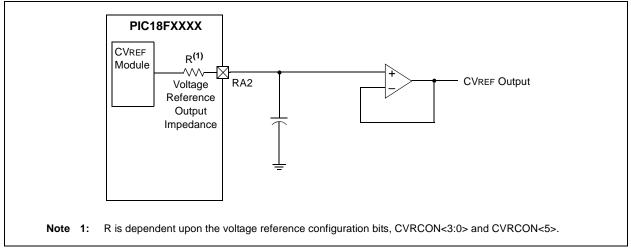

### FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 21-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7                 | Bit 6                 | Bit 5   | Bit 4        | Bit 3        | Bit 2   | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|--------|-----------------------|-----------------------|---------|--------------|--------------|---------|-------|-------|----------------------------|

| CVRCON | CVREN                 | CVROE                 | CVRR    | CVRSS        | CVR3         | CVR2    | CVR1  | CVR0  | 51                         |

| CMCON  | C2OUT                 | C10UT                 | C2INV   | C1INV        | CIS          | CM2     | CM1   | CM0   | 51                         |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | PORTA D | ata Directio | on Control R | egister |       |       | 52                         |

Legend: Shaded cells are not used with the comparator voltage reference.

**Note 1:** PORTA pins are enabled based on oscillator configuration.

### 22.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

PIC18F2525/2620/4525/4620 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The High/Low-Voltage Detect Control register (Register 22-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 22-1.

### REGISTER 22-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0   | U-0 | R-0   | R/W-0  | R/W-0                 | R/W-1                 | R/W-0                 | R/W-1                 |

|---------|-----|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG | —   | IRVST | HLVDEN | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7   |     |       |        |                       |                       |                       | bit 0                 |

| Legend:           |                            |                                                  |                                                                    |                                                                             |  |  |  |  |

|-------------------|----------------------------|--------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| R = Reada         | able bit                   | W = Writable bit                                 | U = Unimplemented bit                                              | , read as '0'                                                               |  |  |  |  |

| -n = Value at POR |                            | '1' = Bit is set                                 | '0' = Bit is cleared                                               | x = Bit is unknown                                                          |  |  |  |  |

| bit 7             | VDIRMAG                    | G: Voltage Direction Magnitu                     | ide Select bit                                                     |                                                                             |  |  |  |  |

|                   | 1 = Event                  | occurs when voltage equals                       | s or exceeds trip point (HLVDL<br>s or falls below trip point (HLV |                                                                             |  |  |  |  |

| bit 6             | Unimplemented: Read as '0' |                                                  |                                                                    |                                                                             |  |  |  |  |

| bit 5             | IRVST: In                  | ternal Reference Voltage Sta                     | able Flag bit                                                      |                                                                             |  |  |  |  |

|                   | 0 = Indica                 | •                                                | logic will not generate the inte                                   | flag at the specified voltage range<br>errupt flag at the specified voltage |  |  |  |  |

| bit 4             | HLVDEN:                    | HLVDEN: High/Low-Voltage Detect Power Enable bit |                                                                    |                                                                             |  |  |  |  |

|                   | 1 = HLVE<br>0 = HLVE       |                                                  |                                                                    |                                                                             |  |  |  |  |

| bit 3-0           | HLVDL3:                    | HLVDL0: Voltage Detection                        | Limit bits <sup>(1)</sup>                                          |                                                                             |  |  |  |  |

|                   |                            | xternal analog input is used aximum setting      | (input comes from the HLVDI                                        | N pin)                                                                      |  |  |  |  |

|                   | •                          |                                                  |                                                                    |                                                                             |  |  |  |  |

|                   | •                          |                                                  |                                                                    |                                                                             |  |  |  |  |

|                   | •<br>• • • • • •           | inimum setting                                   |                                                                    |                                                                             |  |  |  |  |

Note 1: See Table 26-4 in Section 26.0 "Electrical Characteristics" for the specifications.

The module is enabled by setting the HLVDEN bit. Each time that the HLVD module is enabled, the circuitry requires some time to stabilize. The IRVST bit is a read-only bit and is used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and IRVST is set. The VDIRMAG bit determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

#### REGISTER 23-6: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

|            |                    |                              |               |                    | -                |            |       |

|------------|--------------------|------------------------------|---------------|--------------------|------------------|------------|-------|

| U-0        | U-0                | U-0                          | U-0           | R/C-1              | R/C-1            | R/C-1      | R/C-1 |

| _          | —                  | —                            | —             | CP3 <sup>(1)</sup> | CP2              | CP1        | CP0   |

| bit 7      |                    |                              |               |                    |                  |            | bit 0 |

|            |                    |                              |               |                    |                  |            |       |

| Legend:    |                    |                              |               |                    |                  |            |       |

| R = Readal | ble bit            | C = Clearable                | bit           | U = Unimpler       | mented bit, read | as '0'     |       |

| -n = Value | when device is unp | programmed                   |               | u = Unchang        | ed from program  | nmed state |       |

|            |                    |                              |               |                    |                  |            |       |

| bit 7-4    |                    | ted: Read as '               | )'            |                    |                  |            |       |

| bit 3      | CP3: Code Pr       | rotection bit <sup>(1)</sup> |               |                    |                  |            |       |

|            |                    | 06000-007FFF                 | <i>,</i> .    |                    |                  |            |       |

|            | 0 = Block 3 (0)    | 06000-007FFF                 | h) code-prote | ected              |                  |            |       |

| bit 2      | CP2: Code Pr       | rotection bit                |               |                    |                  |            |       |

|            |                    | 04000-005FFF                 | <i>,</i> .    |                    |                  |            |       |

|            |                    | 04000-005FFF                 | h) code-prote | ected              |                  |            |       |

| bit 1      | CP1: Code Pr       |                              |               |                    |                  |            |       |

|            | •                  | 02000-003FFF                 | <i>'</i> .    |                    |                  |            |       |

|            |                    | 02000-003FFF                 | n) code-prote | ected              |                  |            |       |

| bit 0      | CP0: Code Pr       |                              |               |                    |                  |            |       |

|            |                    | 00800-001FFF                 | <i>,</i> .    |                    |                  |            |       |

|            | 0 = BIOCK  0 (0)   | 00800-001FFF                 | m code-prote  | ecieu              |                  |            |       |

Note 1: Unimplemented in PIC18FX525 devices; maintain this bit set.

### REGISTER 23-7: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1 | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| CPD   | СРВ   | —   | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:                |                   |                                     |  |

|------------------------|-------------------|-------------------------------------|--|

| R = Readable bit       | C = Clearable bit | U = Unimplemented bit, read as '0'  |  |

| -n = Value when device | is unprogrammed   | u = Unchanged from programmed state |  |

| bit 7                  | CPD: Data EEPROM Code Protection bit                                                                                        |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                        | 1 = Data EEPROM not code-protected                                                                                          |

|                        | 0 = Data EEPROM code-protected                                                                                              |

| bit 6                  | CPB: Boot Block Code Protection bit                                                                                         |

|                        | <ul><li>1 = Boot block (000000-0007FFh) not code-protected</li><li>0 = Boot block (000000-0007FFh) code-protected</li></ul> |

| <b>h</b> :+ <b>r</b> 0 | Unimplemented, Dood op (0)                                                                                                  |

bit 5-0 Unimplemented: Read as '0'

| INCI        | FSZ                                      | Increment f, Skip if 0                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                |  |  |  |  |

|-------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Synta       | ax:                                      | INCFSZ f                                                                                                                                                                                                                                                          | INCFSZ f {,d {,a}}                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                |  |  |  |  |

| Oper        | ands:                                    | $0 \le f \le 255$<br>d $\in [0,1]$<br>a $\in [0,1]$                                                                                                                                                                                                               | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                |  |  |  |  |

| Oper        | ation:                                   | .,                                                                                                                                                                                                                                                                | (f) + 1 $\rightarrow$ dest,<br>skip if result = 0                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                |  |  |  |  |

| Statu       | is Affected:                             | None                                                                                                                                                                                                                                                              | None                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                |  |  |  |  |

| Enco        | oding:                                   | 0011                                                                                                                                                                                                                                                              | 0011 11da ffff ffff                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |

| Desc        | sription:                                | incremented<br>placed in W<br>placed back<br>If the result<br>which is alre<br>and a NOP i<br>it a two-cycl<br>If 'a' is '0', th<br>If 'a' is '1', th<br>GPR bank.<br>If 'a' is '0' an<br>set is enabl<br>in Indexed I<br>mode when<br>Section 24.<br>Bit-Oriente | ts of register 'f<br>d. If 'd' is '0', th<br>'. If 'd' is '1', th<br>k in register 'f'<br>is '0', the next<br>eady fetched,<br>s executed ins<br>le instruction.<br>The Access Bar<br>he BSR is use<br>and the extended<br>ed, this instruct<br>Literal Offset A<br>ever $f \le 95$ (5F<br>2.3 "Byte-Ori<br>d Instruction<br>set Mode" for | he result is<br>e result is<br>(default).<br>t instruction,<br>is discarded<br>stead, making<br>hk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>addressing<br>Fh). See<br>iented and<br>s in Indexed |  |  |  |  |

| Word        | ls.                                      | 1                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                |  |  |  |  |

| Cycle       | es:                                      |                                                                                                                                                                                                                                                                   | cles if skip and<br>2-word instruc                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                |  |  |  |  |

| QC          | ycle Activity:                           |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                |  |  |  |  |

|             | Q1                                       | Q2                                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                         | Q4                                                                                                                                                                                                                             |  |  |  |  |

|             | Decode                                   | Read<br>register 'f'                                                                                                                                                                                                                                              | Process<br>Data                                                                                                                                                                                                                                                                                                                            | Write to<br>destination                                                                                                                                                                                                        |  |  |  |  |

| lf sk       | ip:                                      |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                |  |  |  |  |

|             | Q1                                       | Q2                                                                                                                                                                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                         | Q4                                                                                                                                                                                                                             |  |  |  |  |

|             | No                                       | No                                                                                                                                                                                                                                                                | No                                                                                                                                                                                                                                                                                                                                         | No                                                                                                                                                                                                                             |  |  |  |  |

|             | operation                                | operation                                                                                                                                                                                                                                                         | operation                                                                                                                                                                                                                                                                                                                                  | operation                                                                                                                                                                                                                      |  |  |  |  |

| If SK       | ip and followed                          | •                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                            | 04                                                                                                                                                                                                                             |  |  |  |  |

|             | Q1<br>No                                 | Q2<br>No                                                                                                                                                                                                                                                          | Q3<br>No                                                                                                                                                                                                                                                                                                                                   | Q4<br>No                                                                                                                                                                                                                       |  |  |  |  |

|             | operation                                | operation                                                                                                                                                                                                                                                         | operation                                                                                                                                                                                                                                                                                                                                  | operation                                                                                                                                                                                                                      |  |  |  |  |

|             | No                                       | No                                                                                                                                                                                                                                                                | No                                                                                                                                                                                                                                                                                                                                         | No                                                                                                                                                                                                                             |  |  |  |  |

|             | operation                                | operation                                                                                                                                                                                                                                                         | operation operation                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |

| <u>Exan</u> | nple:                                    | HERE I<br>NZERO :<br>ZERO :                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                            | IT, 1, 0                                                                                                                                                                                                                       |  |  |  |  |

|             | Before Instruc<br>PC<br>After Instructic | = Address                                                                                                                                                                                                                                                         | (HERE)                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                |  |  |  |  |

|             | CNT<br>If CNT<br>PC                      | = CNT + 1<br>= 0;<br>= Address                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                |  |  |  |  |

|             | If CNT<br>PC                             | ≠ 0;                                                                                                                                                                                                                                                              | (NZERO)                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                |  |  |  |  |

| INFS        | SNZ                     | Incremer               | nt f, Skip if N                         | lot 0                    |  |  |  |  |

|-------------|-------------------------|------------------------|-----------------------------------------|--------------------------|--|--|--|--|

| Synta       | ax:                     | INFSNZ                 | INFSNZ f {,d {,a}}                      |                          |  |  |  |  |

|             | ands:                   | $0 \le f \le 255$      | $0 \le f \le 255$                       |                          |  |  |  |  |

|             |                         | d ∈ [0,1]<br>a ∈ [0,1] |                                         |                          |  |  |  |  |

| Oper        | ation:                  |                        | (f) + 1 $\rightarrow$ dest,             |                          |  |  |  |  |

|             |                         | skip if resu           | skip if result ≠ 0                      |                          |  |  |  |  |

| Statu       | is Affected:            | None                   |                                         |                          |  |  |  |  |

| Enco        | oding:                  | 0100                   | 10da ff                                 | ff ffff                  |  |  |  |  |

| Desc        | cription:               | The conter             | nts of register                         | f' are                   |  |  |  |  |

|             |                         |                        | ed. If 'd' is '0',                      |                          |  |  |  |  |

|             |                         |                        | V. If 'd' is '1', t<br>k in register 'f |                          |  |  |  |  |

|             |                         |                        | t is not '0', the                       |                          |  |  |  |  |

|             |                         | instruction            | , which is alrea                        | ady fetched, is          |  |  |  |  |

|             |                         |                        | and a NOP is e                          |                          |  |  |  |  |

|             |                         | instead, m             | aking it a two-                         | cycle                    |  |  |  |  |

|             |                         |                        |                                         | ink is selected.         |  |  |  |  |

|             |                         |                        |                                         | ed to select the         |  |  |  |  |