Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 48KB (24K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4525-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

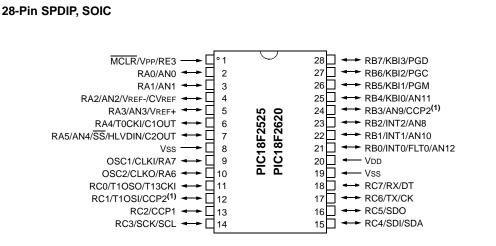

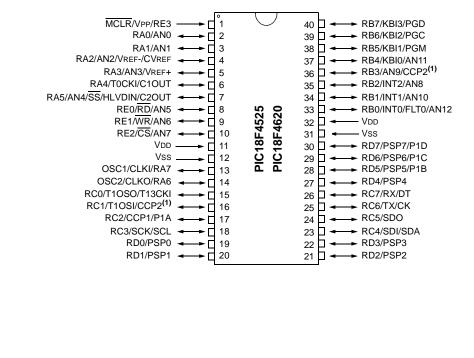

### **Pin Diagrams**

40-Pin PDIP

Note 1: RB3 is the alternate pin for CCP2 multiplexing.

## 4.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The MCLR pin is not driven low by any internal Resets, including the WDT.

In PIC18F2525/2620/4525/4620 devices, the MCLR input can be disabled with the MCLRE Configuration bit. When MCLR is disabled, the pin becomes a digital input. See Section 9.5 "PORTE, TRISE and LATE Registers" for more information.

## 4.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

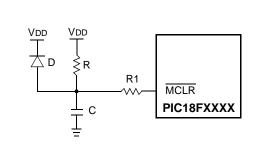

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any POR.

### FIGURE 4-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

| Register                 | Register Applicable Devices |        | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |           |                       |

|--------------------------|-----------------------------|--------|------------------------------------|------------------------------------------------------------------|---------------------------------|-----------|-----------------------|

| TOSU 2525 2620 4525 4620 |                             | 0 0000 | 0 0000                             | 0 uuuu <b>(3)</b>                                                |                                 |           |                       |

| TOSH                     | 2525                        | 2620   | 4525                               | 4620                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu <b>(3)</b>  |

| TOSL                     | 2525                        | 2620   | 4525                               | 4620                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu <b>(3)</b>  |

| STKPTR                   | 2525                        | 2620   | 4525                               | 4620                                                             | 00-0 0000                       | uu-0 0000 | uu-u uuuu <b>(3)</b>  |

| PCLATU                   | 2525                        | 2620   | 4525                               | 4620                                                             | 0 0000                          | 0 0000    | u uuuu                |

| PCLATH                   | 2525                        | 2620   | 4525                               | 4620                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu             |

| PCL                      | 2525                        | 2620   | 4525                               | 4620                                                             | 0000 0000                       | 0000 0000 | PC + 2 <sup>(2)</sup> |

| TBLPTRU                  | 2525                        | 2620   | 4525                               | 4620                                                             | 00 0000                         | 00 0000   | uu uuuu               |

| TBLPTRH                  | 2525                        | 2620   | 4525                               | 4620                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu             |

| TBLPTRL                  | 2525                        | 2620   | 4525                               | 4620                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu             |

| TABLAT                   | 2525                        | 2620   | 4525                               | 4620                                                             | 0000 0000                       | 0000 0000 | uuuu uuuu             |

| PRODH                    | 2525                        | 2620   | 4525                               | 4620                                                             | XXXX XXXX                       | uuuu uuuu | uuuu uuuu             |

| PRODL                    | 2525                        | 2620   | 4525                               | 4620                                                             | XXXX XXXX                       | uuuu uuuu | uuuu uuuu             |

| INTCON                   | 2525                        | 2620   | 4525                               | 4620                                                             | 0000 000x                       | 0000 000u | uuuu uuuu <b>(1)</b>  |

| INTCON2                  | 2525                        | 2620   | 4525                               | 4620                                                             | 1111 -1-1                       | 1111 -1-1 | uuuu -u-u <b>(1)</b>  |

| INTCON3                  | 2525                        | 2620   | 4525                               | 4620                                                             | 11-0 0-00                       | 11-0 0-00 | uu-u u-uu <b>(1)</b>  |

| INDF0                    | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| POSTINC0                 | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| POSTDEC0                 | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| PREINC0                  | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| PLUSW0                   | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| FSR0H                    | 2525                        | 2620   | 4525                               | 4620                                                             | 0000                            | 0000      | uuuu                  |

| FSR0L                    | 2525                        | 2620   | 4525                               | 4620                                                             | XXXX XXXX                       | uuuu uuuu | uuuu uuuu             |

| WREG                     | 2525                        | 2620   | 4525                               | 4620                                                             | XXXX XXXX                       | uuuu uuuu | uuuu uuuu             |

| INDF1                    | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| POSTINC1                 | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| POSTDEC1                 | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| PREINC1                  | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

| PLUSW1                   | 2525                        | 2620   | 4525                               | 4620                                                             | N/A                             | N/A       | N/A                   |

### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 4-3 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

NOTES:

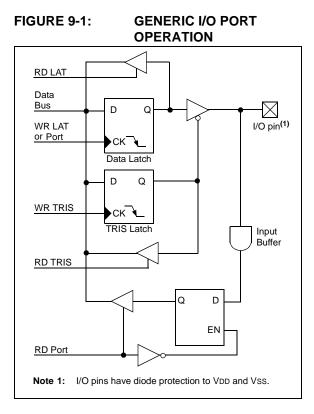

## 9.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 9-1.

## 9.1 PORTA, TRISA and LATA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 23.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA3:RA0 and RA5 as A/D converter inputs is selected by clearing or setting the control bits in the ADCON1 register (A/D Control Register 1).

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CMCON register. To use RA3:RA0 as digital inputs, it is also necessary to turn off the comparators.

| Note: | On a Power-on Reset, RA5 and RA3:RA0          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels. All PORTA pins have full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| EXAMPL  | E 9-1: |   | INITIALIZING PORTA        |

|---------|--------|---|---------------------------|

| CLRF 1  | PORTA  | ; | Initialize PORTA by       |

|         |        | ; | clearing output           |

|         |        | ; | data latches              |

| CLRF 1  | LATA   | ; | Alternate method          |

|         |        | ; | to clear output           |

|         |        | ; | data latches              |

| MOVLW   | 07h    | ; | Configure A/D             |

| MOVWF 2 | ADCON1 | ; | for digital inputs        |

| MOVWF   | 07h    | ; | Configure comparators     |

| MOVWF   | CMCON  | ; | for digital input         |

| MOVLW   | 0CFh   | ; | Value used to             |

|         |        | ; | initialize data           |

|         |        | ; | direction                 |

| MOVWF   | TRISA  | ; | Set RA<7:6,3:0> as inputs |

|         |        | ; | RA<5:4> as outputs        |

| Pin            | Function            | TRIS<br>Setting | I/O | l/O<br>Type          | Description                                                                                                                               |

|----------------|---------------------|-----------------|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/     | RC0                 | 0               | 0   | DIG                  | LATC<0> data output.                                                                                                                      |

| T13CKI         |                     | 1               | Ι   | ST                   | PORTC<0> data input.                                                                                                                      |

|                | T1OSO               | х               | 0   | ANA                  | Timer1 oscillator output; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                |

|                | T13CKI              | 1               | Ι   | ST                   | Timer1/Timer3 counter input.                                                                                                              |

| RC1/T1OSI/CCP2 | RC1                 | 0               | 0   | DIG                  | LATC<1> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<1> data input.                                                                                                                      |

|                | T1OSI               | x               | Ι   | ANA                  | Timer1 oscillator input; enabled when Timer1 oscillator enabled.<br>Disables digital I/O.                                                 |

|                | CCP2 <sup>(1)</sup> | 0               | 0   | DIG                  | CCP2 compare and PWM output; takes priority over port data.                                                                               |

|                |                     | 1               | Ι   | ST                   | CCP2 capture input.                                                                                                                       |

| RC2/CCP1/P1A   | RC2                 | 0               | 0   | DIG                  | LATC<2> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<2> data input.                                                                                                                      |

|                | CCP1                | 0               | 0   | DIG                  | ECCP1 compare or PWM output; takes priority over port data.                                                                               |

|                |                     | 1               | Ι   | ST                   | ECCP1 capture input.                                                                                                                      |

|                | P1A <sup>(2)</sup>  | 0               | 0   | DIG                  | ECCP1 Enhanced PWM output, channel A. May be configured for tri-state during Enhanced PWM shutdown events. Takes priority over port data. |

| RC3/SCK/SCL    | RC3                 | 0               | 0   | DIG                  | LATC<3> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<3> data input.                                                                                                                      |

|                | SCK                 | 0               | 0   | DIG                  | SPI clock output (MSSP module); takes priority over port data.                                                                            |

|                |                     | 1               |     | ST                   | SPI clock input (MSSP module).                                                                                                            |

|                | SCL                 | 0               | 0   | DIG                  | I <sup>2</sup> C <sup>™</sup> clock output (MSSP module); takes priority over port data.                                                  |

|                |                     | 1               | Ι   | I <sup>2</sup> C/SMB | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting                                                          |

| RC4/SDI/SDA    | RC4                 | 0               | 0   | DIG                  | LATC<4> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<4> data input.                                                                                                                      |

|                | SDI                 | 1               | Ι   | ST                   | SPI data input (MSSP module).                                                                                                             |

|                | SDA                 | 0               | 0   | DIG                  | I <sup>2</sup> C data output (MSSP module); takes priority over port data.                                                                |

|                |                     | 1               | Ι   | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.                                                          |

| RC5/SDO        | RC5                 | 0               | 0   | DIG                  | LATC<5> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<5> data input.                                                                                                                      |

|                | SDO                 | 0               | 0   | DIG                  | SPI data output (MSSP module); takes priority over port data.                                                                             |

| RC6/TX/CK      | RC6                 | 0               | 0   | DIG                  | LATC<6> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<6> data input.                                                                                                                      |

|                | ТΧ                  | 0               | 0   | DIG                  | Asynchronous serial transmit data output (EUSART module);<br>takes priority over port data. User must configure as output.                |

|                | СК                  | 0               | 0   | DIG                  | Synchronous serial clock output (EUSART module); takes priority over port data.                                                           |

|                |                     | 1               | Ι   | ST                   | Synchronous serial clock input (EUSART module).                                                                                           |

| RC7/RX/DT      | RC7                 | 0               | 0   | DIG                  | LATC<7> data output.                                                                                                                      |

|                |                     | 1               | Ι   | ST                   | PORTC<7> data input.                                                                                                                      |

|                | RX                  | 1               | Ι   | ST                   | Asynchronous serial receive data input (EUSART module).                                                                                   |

|                | DT                  | 0               | 0   | DIG                  | Synchronous serial data output (EUSART module); takes priority over port data.                                                            |

|                |                     | 1               | Ι   | ST                   | Synchronous serial data input (EUSART module). User must configure as an input.                                                           |

## TABLE 9-5: PORTC I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set. Alternate assignment is RB3.

2: Enhanced PWM output is available only on PIC18F4525/4620 devices.

## 9.5 PORTE, TRISE and LATE Registers

Depending on the particular PIC18F2525/2620/4525/ 4620 device selected, PORTE is implemented in two different ways.

For 40/44-pin devices, PORTE is a 4-bit wide port. Three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/ AN7) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On  | а    | Power-on     | Reset,    | RE2:RE0 | are |

|-------|-----|------|--------------|-----------|---------|-----|

|       | con | figu | ired as anal | log input | s.      |     |

The upper four bits of the TRISE register also control the operation of the Parallel Slave Port. Their operation is explained in Register 9-1.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register, read and write the latched output value for PORTE.

The fourth pin of PORTE ( $\overline{\text{MCLR}}/\text{VPP}/\text{RE3}$ ) is an input only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RE3 is enabled as |

|-------|----------------------------------------|

|       | a digital input only if Master Clear   |

|       | functionality is disabled.             |

### EXAMPLE 9-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by |

|-------|--------|-----------------------|

|       |        | ; clearing output     |

|       |        | ; data latches        |

| CLRF  | LATE   | ; Alternate method    |

|       |        | ; to clear output     |

|       |        | ; data latches        |

| MOVLW | 0Ah    | ; Configure A/D       |

| MOVWF | ADCON1 | ; for digital inputs  |

| MOVLW | 03h    | ; Value used to       |

|       |        | ; initialize data     |

|       |        | ; direction           |

| MOVWF | TRISE  | ; Set RE<0> as inputs |

|       |        | ; RE<1> as outputs    |

|       |        | ; RE<2> as inputs     |

|       |        |                       |

## 9.5.1 PORTE IN 28-PIN DEVICES

For 28-pin devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In these cases, PORTE is a single bit, input only port comprised of RE3 only. The pin operates as previously described.

## 10.5 RCON Register

The RCON register contains flag bits which are used to determine the cause of the last Reset or wake-up from Idle or Sleep modes. RCON also contains the IPEN bit which enables interrupt priorities.

The operation of the SBOREN bit and the Reset flag bits is discussed in more detail in **Section 4.1 "RCON Register"**.

## REGISTER 10-10: RCON: RESET CONTROL REGISTER

| R/W-0 | R/W-1 <sup>(1)</sup> | U-0 | R/W-1 | R-1 | R-1 | R/W-0 <sup>(1)</sup> | R/W-0 |

|-------|----------------------|-----|-------|-----|-----|----------------------|-------|

| IPEN  | SBOREN               | _   | RI    | TO  | PD  | POR                  | BOR   |

| bit 7 |                      |     |       |     |     |                      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | IPEN: Interrupt Priority Enable bit                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Enable priority levels on interrupts</li> <li>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode)</li> </ul> |

| bit 6 | SBOREN: Software BOR Enable bit <sup>(1)</sup>                                                                                                 |

|       | For details of bit operation, see Register 4-1.                                                                                                |

| bit 5 | Unimplemented: Read as '0'                                                                                                                     |

| bit 4 | RI: RESET Instruction Flag bit                                                                                                                 |

|       | For details of bit operation, see Register 4-1.                                                                                                |

| bit 3 | TO: Watchdog Timer Time-out Flag bit                                                                                                           |

|       | For details of bit operation, see Register 4-1.                                                                                                |

| bit 2 | PD: Power-Down Detection Flag bit                                                                                                              |

|       | For details of bit operation, see Register 4-1.                                                                                                |

| bit 1 | <b>POR:</b> Power-on Reset Status bit <sup>(1)</sup>                                                                                           |

|       | For details of bit operation, see Register 4-1.                                                                                                |

| bit 0 | BOR: Brown-out Reset Status bit                                                                                                                |

|       | For details of bit operation, see Register 4-1.                                                                                                |

|       |                                                                                                                                                |

**Note 1:** Actual Reset values are determined by device configuration and the nature of the device Reset. See Register 4-1 for additional information.

## 17.4 I<sup>2</sup>C Mode

The MSSP module in  $I^2C$  mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCL) RC3/SCK/SCL

- Serial data (SDA) RC4/SDI/SDA

The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

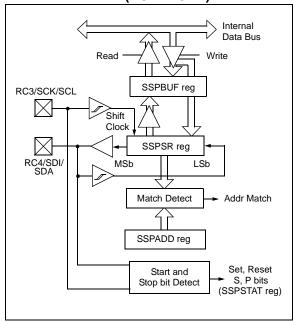

#### FIGURE 17-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

## 17.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON1, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON1 and SSPCON2 registers are readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPADD act as the Baud Rate Generator reload value.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

## 18.0 ENHANCED UNIVERSAL SYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of the two serial I/O modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a halfduplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of the Enhanced USART are multiplexed with PORTC. In order to configure RC6/TX/CK and RC7/RX/DT as a USART:

- SPEN bit (RCSTA<7>) must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be set (= 1)

| Note: | The EUSART control will automatically                  |

|-------|--------------------------------------------------------|

|       | reconfigure the pin from input to output as<br>needed. |

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 18-1, Register 18-2 and Register 18-3, respectively.

## 20.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins RA0 through RA5, as well as the on-chip voltage reference (see Section 21.0 "Comparator Voltage Reference Module"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register.

The CMCON register (Register 20-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 20-1.

### **REGISTER 20-1: CMCON: COMPARATOR CONTROL REGISTER**

| R-0      | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 | R/W-1 | R/W-1 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| C2OUT    | C1OUT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   |

| bit 7    |       |       |       |       |       |       | bit 0 |

|          |       |       |       |       |       |       |       |

| l egend. |       |       |       |       |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | C2OUT: Comparator 2 Output bit                                             |

|---------|----------------------------------------------------------------------------|

|         | When $C2INV = 0$ :                                                         |

|         | 1 = C2 VIN + > C2 VIN -                                                    |

|         | 0 = C2 VIN + < C2 VIN -                                                    |

|         | <u>When C2INV = 1:</u>                                                     |

|         | 1 = C2  VIN+ < C2  VIN-                                                    |

|         | 0 = C2  VIN+ > C2  VIN-                                                    |

| bit 6   | C1OUT: Comparator 1 Output bit                                             |

|         | $\frac{\text{When C1INV} = 0}{1 - 24}$                                     |

|         | 1 = C1 VIN+ > C1 VIN-<br>0 = C1 VIN+ < C1 VIN-                             |

|         | When $C1INV = 1$ :                                                         |

|         | 1 = C1 VIN+ < C1 VIN-                                                      |

|         | 0 = C1  Vin + > C1  Vin                                                    |

| bit 5   | C2INV: Comparator 2 Output Inversion bit                                   |

|         | 1 = C2 output inverted                                                     |

|         | 0 = C2 output not inverted                                                 |

| bit 4   | C1INV: Comparator 1 Output Inversion bit                                   |

|         | 1 = C1 output inverted                                                     |

|         | 0 = C1 output not inverted                                                 |

| bit 3   | CIS: Comparator Input Switch bit                                           |

|         | $\frac{\text{When CM2:CM0} = 110:}{2}$                                     |

|         | 1 = C1  VIN- connects to RA3/AN3/VREF+                                     |

|         | C2 VIN- connects to RA2/AN2/VREF-/CVREF<br>0 = C1 VIN- connects to RA0/AN0 |

|         | C2 VIN- connects to RA1/AN1                                                |

| bit 2-0 | CM2:CM0: Comparator Mode bits                                              |

|         | Figure 20-1 shows the Comparator modes and the CM2:CM0 bit settings.       |

|         | о                                                                          |

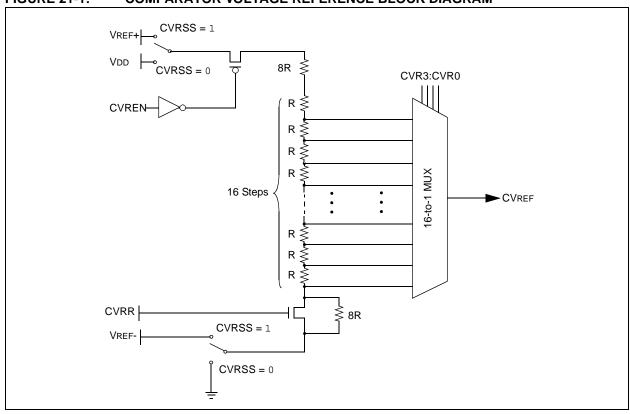

## FIGURE 21-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

## 21.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 21-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 26.0 "Electrical Characteristics"**.

## 21.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 21.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

## 21.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RA2 as a digital output with CVRSS enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 21-2 shows an example buffering technique.

### TABLE 24-2: PIC18FXXXX INSTRUCTION SET

| Mnemo    | onic,                           | Description                              | Cualas     | 16-  | Bit Instr | uction W | /ord | Status          | Nataa      |

|----------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

| Opera    | nds                             | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| BYTE-ORI | BYTE-ORIENTED OPERATIONS        |                                          |            |      |           |          |      |                 |            |

| ADDWF    | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF    | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1,2        |

| CLRF     | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| COMF     | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ   | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| CPFSGT   | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| CPFSLT   | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| DECF     | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ   | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INCF     | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ   | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| INFSNZ   | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2       |

| IORWF    | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |

| MOVF     | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1          |

| MOVFF    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff     | ffff | None            |            |

|          |                                 | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff     | ffff |                 |            |

| MOVWF    | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |            |

| MULWF    | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None            | 1, 2       |

| NEGF     | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N |            |

| RLCF     | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     | ffff | C, Z, N         | 1, 2       |

| RLNCF    | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff | Z, N            |            |

| RRCF     | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N         |            |

| RRNCF    | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff | Z, N            |            |

| SETF     | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None            | 1, 2       |

| SUBFWB   | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101 | 01da      | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWF    | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB   | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da      | ffff     | ffff | C, DC, Z, OV, N |            |

|          | , ,                             | Borrow                                   |            |      |           |          |      |                 |            |

| SWAPF    | f, d, a                         | Swap Nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4          |

| TSTFSZ   | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None            | 1, 2       |

| XORWF    | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001 | 10da      | ffff     | ffff | Z, N            | ĺ          |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| ΒZ                             |                                                     | Branch if                                                                 | Zero                                                                                                                                                                                             |        |            |  |  |  |

|--------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|--|--|--|

| Synt                           | ax:                                                 | BZ n                                                                      |                                                                                                                                                                                                  |        |            |  |  |  |

| Ope                            | rands:                                              | -128 ≤ n ≤ ′                                                              | 127                                                                                                                                                                                              |        |            |  |  |  |

| Ope                            | ration:                                             |                                                                           | if Zero bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                            |        |            |  |  |  |

| Statu                          | us Affected:                                        | None                                                                      | None                                                                                                                                                                                             |        |            |  |  |  |

| Enco                           | oding:                                              | 1110                                                                      | 0000                                                                                                                                                                                             | nnnn   | nnnn       |  |  |  |

| Desc                           | cription:                                           | will branch.<br>The 2's con<br>added to th<br>have incren<br>instruction, | The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a |        |            |  |  |  |

| Word                           | ds:                                                 | 1                                                                         |                                                                                                                                                                                                  |        |            |  |  |  |

| Cycl                           | es:                                                 | 1(2)                                                                      |                                                                                                                                                                                                  |        |            |  |  |  |

|                                | cycle Activity:<br>ump:                             |                                                                           |                                                                                                                                                                                                  |        | _          |  |  |  |

|                                | Q1                                                  | Q2                                                                        | Q3                                                                                                                                                                                               |        | Q4         |  |  |  |

|                                | Decode                                              | Read literal<br>'n'                                                       | Proce:<br>Data                                                                                                                                                                                   |        | rite to PC |  |  |  |

|                                | No                                                  | No                                                                        | No                                                                                                                                                                                               |        | No         |  |  |  |

|                                | operation                                           | operation                                                                 | operati                                                                                                                                                                                          | ion o  | peration   |  |  |  |

| If N                           | o Jump:                                             |                                                                           |                                                                                                                                                                                                  |        |            |  |  |  |

|                                | Q1                                                  | Q2                                                                        | Q3                                                                                                                                                                                               | -      | Q4         |  |  |  |

|                                | Decode                                              | Read literal                                                              | Proces                                                                                                                                                                                           |        | No         |  |  |  |

|                                |                                                     | ʻn'                                                                       | Data                                                                                                                                                                                             | 1 O    | peration   |  |  |  |

|                                |                                                     |                                                                           |                                                                                                                                                                                                  |        |            |  |  |  |

| Exar                           | <u>mple:</u>                                        | HERE                                                                      | BZ J                                                                                                                                                                                             | lamp   |            |  |  |  |

|                                | Before Instruc<br>PC<br>After Instructio<br>If Zero | = ad                                                                      | dress (H                                                                                                                                                                                         | ERE)   |            |  |  |  |

| If Zero<br>PC<br>If Zero<br>PC |                                                     |                                                                           | dress (J                                                                                                                                                                                         | iumn ) |            |  |  |  |

| Curtary                                                        |                                                                              |                                      |                                  |                                                         |          |  |

|----------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------|----------------------------------|---------------------------------------------------------|----------|--|

| Syntax:                                                        | CALL k {,s}                                                                  |                                      |                                  |                                                         |          |  |

| Operands:                                                      | $0 \le k \le 1048575$<br>s $\in [0,1]$                                       |                                      |                                  |                                                         |          |  |

| Operation:                                                     | $(PC) + 4 \rightarrow$                                                       |                                      |                                  |                                                         |          |  |

|                                                                | $k \rightarrow PC < 20$<br>if s = 1,                                         | ):1>;                                |                                  |                                                         |          |  |

|                                                                | $(W) \rightarrow WS,$                                                        |                                      |                                  |                                                         |          |  |

|                                                                | (STATUS) -                                                                   |                                      | JSS,                             |                                                         |          |  |

| <b>.</b>                                                       | $(BSR) \rightarrow B$                                                        | SRS                                  |                                  |                                                         |          |  |

| Status Affected:                                               | None                                                                         |                                      |                                  | - T                                                     |          |  |

| Encoding:<br>1st word (k<7:0>)                                 | 1110                                                                         | 110s                                 | le lele                          | 1. 1.1.1.1.1                                            | -        |  |

| 2nd word(k<19:8>)                                              |                                                                              | k <sub>19</sub> kkk                  | k <sub>7</sub> kk<br>kkkł        |                                                         | 0        |  |

| Words:                                                         | respective s<br>STATUSS a<br>update occi<br>20-bit value<br>CALL is a t<br>2 | and BSR<br>urs (defa<br>e 'k' is loa | S. If 's'<br>ult). Th<br>ded int | = 0, no<br>ien, the<br>o PC<20:                         | 1:       |  |

| Cycles:                                                        | 2                                                                            |                                      |                                  |                                                         |          |  |

|                                                                |                                                                              |                                      |                                  |                                                         |          |  |

| Q Cycle Activity:                                              |                                                                              |                                      |                                  |                                                         |          |  |

| Q Cycle Activity:                                              | Q2                                                                           | Q3                                   | 8                                | Q4                                                      |          |  |

|                                                                | Read literal                                                                 | PUSHF                                | PC to                            | Read liter                                              |          |  |

| Q1                                                             |                                                                              | 1                                    | PC to                            | Read liter<br>'k'<19:8>                                 | >,       |  |

| Q1                                                             | Read literal                                                                 | PUSHF                                | PC to<br>k                       | Read liter                                              | >,       |  |

| Q1<br>Decode                                                   | Read literal<br>'k'<7:0>,                                                    | PUSH F<br>stac                       | PC to<br>k                       | Read liter<br>'k'<19:8><br>Write to F                   | >,<br>>( |  |

| Q1<br>Decode<br>No                                             | Read literal<br>'k'<7:0>,<br>No                                              | PUSH F<br>stac                       | PC to<br>k                       | Read liter<br>'k'<19:8><br>Write to F<br>No<br>operatio | >,<br>>( |  |

| Q1<br>Decode<br>No<br>operation<br>Example:<br>Before Instruct | Read literal<br>'k'<7:0>,<br>No<br>operation<br>HERE<br>tion                 | PUSH F<br>stac<br>No<br>opera        | PC to<br>k<br>tion<br>THER:      | Read liter<br>'k'<19:8><br>Write to F<br>No<br>operatio | >,<br>>( |  |

| Q1<br>Decode<br>No<br>operation<br>Example:                    | Read literal<br>'k'<7:0>,<br>No<br>operation<br>HERE<br>tion<br>= address    | PUSH F<br>stac<br>No<br>opera        | PC to<br>k<br>tion<br>THER:      | Read liter<br>'k'<19:8><br>Write to F<br>No<br>operatio | >,<br>>( |  |

| RCA   | LL             | Relative                                                  | Call                                                          |                 |       |           | R          | ES   |  |

|-------|----------------|-----------------------------------------------------------|---------------------------------------------------------------|-----------------|-------|-----------|------------|------|--|

| Synta | ax:            | RCALL n                                                   | RCALL n                                                       |                 |       |           |            |      |  |

| Oper  | ands:          | -1024 ≤ n ≤                                               | 1023                                                          |                 |       |           | 0          | ре   |  |

| Oper  | ation:         | · · /                                                     | $(PC) + 2 \rightarrow TOS,$<br>(PC) + 2 + 2n $\rightarrow$ PC |                 |       |           |            |      |  |

| Statu | is Affected:   | None                                                      |                                                               |                 |       |           | St         | tati |  |

| Enco  | oding:         | 1101                                                      | 1nnn                                                          | nnr             | n     | nnnn      | Er         | nco  |  |

| Desc  | cription:      | Subroutine<br>from the cu                                 |                                                               |                 | • •   |           | De         | es   |  |

|       |                | address (P<br>stack. Ther                                 | C + 2) is                                                     | pushe           | ed or | nto the   | W          | or   |  |

|       |                | number '2n                                                |                                                               |                 |       |           | C          | ycl  |  |

|       |                | have increr<br>instruction,<br>PC + 2 + 2<br>two-cycle ir | the new<br>n. This ir                                         | addre<br>struct | SS W  | /ill be   | C          | QC   |  |

| Word  | ls:            | 1                                                         |                                                               |                 |       |           |            |      |  |

| Cycle |                | 2                                                         |                                                               |                 |       |           | <u>E</u> 2 | xar  |  |

| QC    | ycle Activity: |                                                           |                                                               |                 |       |           |            |      |  |

|       | Q1             | Q2                                                        | Q                                                             | 3               |       | Q4        |            |      |  |

|       | Decode         | Read literal<br>'n'                                       | Proce<br>Dat                                                  |                 | Wr    | ite to PC |            |      |  |

|       |                | PUSH PC to stack                                          |                                                               |                 |       |           |            |      |  |

|       |                |                                                           |                                                               |                 |       |           |            |      |  |

No

operation

No

operation

Example: HERE RCALL Jump

No

operation

Before Instruction PC = Address (HERE) After Instruction

No

operation

PC = Address (Jump) TOS = Address (HERE + 2)

| RES       | ET             | Reset                    |                                                                  |      |                 |  |  |  |

|-----------|----------------|--------------------------|------------------------------------------------------------------|------|-----------------|--|--|--|

| Synta     | ax:            | RESET                    |                                                                  |      |                 |  |  |  |

| Oper      | ands:          | None                     |                                                                  |      |                 |  |  |  |

| Oper      | ation:         |                          | Reset all registers and flags that are affected by a MCLR Reset. |      |                 |  |  |  |

| Statu     | s Affected:    | All                      | All                                                              |      |                 |  |  |  |

| Encoding: |                | 0000                     | 0000                                                             | 1111 | 1111            |  |  |  |

| Desc      | ription:       | This instru<br>execute a |                                                                  |      |                 |  |  |  |

| Word      | ls:            | 1                        |                                                                  |      |                 |  |  |  |

| Cycle     | es:            | 1                        |                                                                  |      |                 |  |  |  |

| QC        | ycle Activity: |                          |                                                                  |      |                 |  |  |  |

|           | Q1             | Q2                       | Q3                                                               | 8    | Q4              |  |  |  |

|           | Decode         | Start<br>Reset           | No<br>opera                                                      |      | No<br>operation |  |  |  |

xample:

After Instruction

| Registers = | Reset Value |

|-------------|-------------|

| Flags* =    | Reset Value |

RESET

| RRNCF                                                                                                                           | CF Rotate Right f (No Carry)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                               |                |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|----------------|--|--|

| Syntax:                                                                                                                         | RRNCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | f {,d {,a}}                                              |                               |                |  |  |

| Operands:                                                                                                                       | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                        |                               |                |  |  |