Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 48KB (24K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4525t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                                                                                                        | Pi   | n Numb | ber  | Pin  | Buffer | Description                                                                                                                                      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                                                                                                                                        | PDIP | QFN    | TQFP | Туре | Туре   | Description                                                                                                                                      |  |

| MCLR/VPP/RE3<br>MCLR                                                                                                                                            | 1    | 18     | 18   | I    | ST     | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.            |  |

| VPP                                                                                                                                                             |      |        |      | Р    |        | Programming voltage input.                                                                                                                       |  |

| RE3                                                                                                                                                             |      |        |      | Ι    | ST     | Digital input.                                                                                                                                   |  |

| OSC1/CLKI/RA7<br>OSC1                                                                                                                                           | 13   | 32     | 30   | I    | ST     | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode; |  |

| CLKI                                                                                                                                                            |      |        |      | I    | CMOS   | analog otherwise.<br>External clock source input. Always associated with<br>pin function OSC1. (See related OSC1/CLKI,<br>OSC2/CLKO pins.)       |  |

| RA7                                                                                                                                                             |      |        |      | I/O  | TTL    | General purpose I/O pin.                                                                                                                         |  |

| OSC2/CLKO/RA6<br>OSC2                                                                                                                                           | 14   | 33     | 31   | 0    | _      | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                |  |

| CLKO                                                                                                                                                            |      |        |      | 0    | _      | In RC mode, OSC2 pin outputs CLKO which has 1/4 the frequency of OSC1 and denotes                                                                |  |

| RA6                                                                                                                                                             |      |        |      | I/O  | TTL    | the instruction cycle rate.<br>General purpose I/O pin.                                                                                          |  |

| Legend:       TTL = TTL compatible input       CMOS = CMOS compatible input or output         ST = Schmitt Trigger input with CMOS levels       I       = Input |      |        |      |      |        |                                                                                                                                                  |  |

#### **TABLE 1-3:** PIC18F4525/4620 PINOUT I/O DESCRIPTIONS

Ρ = Power

O = Output Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

3: For the QFN package, it is recommended that the bottom pad be connected to Vss.

## 2.0 OSCILLATOR CONFIGURATIONS

### 2.1 Oscillator Types

PIC18F2525/2620/4525/4620 devices can be operated in ten different oscillator modes. The user can program the Configuration bits, FOSC3:FOSC0, in Configuration Register 1H to select one of these ten modes:

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. HSPLL High-Speed Crystal/Resonator with PLL Enabled

- 5. RC External Resistor/Capacitor with Fosc/4 Output on RA6

- 6. RCIO External Resistor/Capacitor with I/O on RA6

- 7. INTIO1 Internal Oscillator with Fosc/4 Output on RA6 and I/O on RA7

- 8. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 9. EC External Clock with Fosc/4 Output

- 10. ECIO External Clock with I/O on RA6

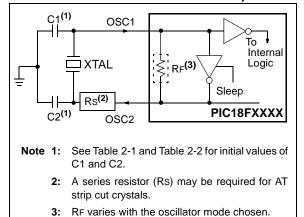

### 2.2 Crystal Oscillator/Ceramic Resonators

In XT, LP, HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 2-1 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

**Note:** Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

FIGURE 2-1:

#### CRYSTAL/CERAMIC RESONATOR OPERATION (XT, LP, HS OR HSPLL CONFIGURATION)

# TABLE 2-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Typical Capacitor Values Used: |          |       |       |  |  |  |  |

|--------------------------------|----------|-------|-------|--|--|--|--|

| Mode                           | Freq     | OSC1  | OSC2  |  |  |  |  |

| XT                             | 3.58 MHz | 15 pF | 15 pF |  |  |  |  |

|                                | 4.19 MHz | 15 pF | 15 pF |  |  |  |  |

|                                | 4 MHz    | 30 pF | 30 pF |  |  |  |  |

|                                | 4 MHz    | 50 pF | 50 pF |  |  |  |  |

#### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following Table 2-2 for additional information.

### 2.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 2-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS1:SCS0, select the clock source. The available clock sources are the primary clock (defined by the FOSC3:FOSC0 Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits (IRCF2:IRCF0) select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31.25 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the internal oscillator block is set at 1 MHz.

When a nominal output frequency of 31 kHz is selected (IRCF2:IRCF0 = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable. The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 3.0** "**Power-Managed Modes**".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before selecting the secondary clock source or a very long delay may occur while the Timer1 oscillator starts.

#### 2.7.2 OSCILLATOR TRANSITIONS

PIC18F2525/2620/4525/4620 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes"**.

#### 5.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 5.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL | SUB1, FAST        | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|------|-------------------|---------------------------------------------------------|

| SUB1 | •                 |                                                         |

|      | •<br>RETURN, FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

# 5.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF<br>CALL | OFFSET,<br>TABLE | W |

|-------|--------------|------------------|---|

| ORG   | nn00h        |                  |   |

| TABLE | ADDWF        | PCL              |   |

|       | RETLW        | nnh              |   |

|       | RETLW        | nnh              |   |

|       | RETLW        | nnh              |   |

|       | •            |                  |   |

|       | •            |                  |   |

|       | •            |                  |   |

#### 5.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 7.1 "Table Reads and Table Writes".

#### TABLE 9-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name    | Bit 7                                 | Bit 6                                                    | Bit 5 | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|---------------------------------------|----------------------------------------------------------|-------|---------|--------|--------|--------|--------|----------------------------|

| PORTD   | RD7                                   | RD6                                                      | RD5   | RD4     | RD3    | RD2    | RD1    | RD0    | 52                         |

| LATD    | PORTD Da                              | PORTD Data Latch Register (Read and Write to Data Latch) |       |         |        |        |        | 52     |                            |

| TRISD   | PORTD Data Direction Control Register |                                                          |       |         |        |        | 52     |        |                            |

| TRISE   | IBF                                   | OBF                                                      | IBOV  | PSPMODE | _      | TRISE2 | TRISE1 | TRISE0 | 52                         |

| CCP1CON | P1M1                                  | P1M0                                                     | DC1B1 | DC1B0   | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 51                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

#### 9.5 PORTE, TRISE and LATE Registers

Depending on the particular PIC18F2525/2620/4525/ 4620 device selected, PORTE is implemented in two different ways.

For 40/44-pin devices, PORTE is a 4-bit wide port. Three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/ AN7) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On  | а                | Power-on | Reset,    | RE2:RE0 | are |

|-------|-----|------------------|----------|-----------|---------|-----|

|       | con | nfigured as anal |          | log input | s.      |     |

The upper four bits of the TRISE register also control the operation of the Parallel Slave Port. Their operation is explained in Register 9-1.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register, read and write the latched output value for PORTE.

The fourth pin of PORTE ( $\overline{\text{MCLR}}/\text{VPP}/\text{RE3}$ ) is an input only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RE3 is enabled as |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|

|       | a digital input only if Master Clear   |  |  |  |  |  |

|       | functionality is disabled.             |  |  |  |  |  |

#### EXAMPLE 9-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by |

|-------|--------|-----------------------|

|       |        | ; clearing output     |

|       |        | ; data latches        |

| CLRF  | LATE   | ; Alternate method    |

|       |        | ; to clear output     |

|       |        | ; data latches        |

| MOVLW | 0Ah    | ; Configure A/D       |

| MOVWF | ADCON1 | ; for digital inputs  |

| MOVLW | 03h    | ; Value used to       |

|       |        | ; initialize data     |

|       |        | ; direction           |

| MOVWF | TRISE  | ; Set RE<0> as inputs |

|       |        | ; RE<1> as outputs    |

|       |        | ; RE<2> as inputs     |

|       |        |                       |

#### 9.5.1 PORTE IN 28-PIN DEVICES

For 28-pin devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In these cases, PORTE is a single bit, input only port comprised of RE3 only. The pin operates as previously described.

## **10.0 INTERRUPTS**

The PIC18F2525/2620/4525/4620 devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupts will interrupt any low-priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

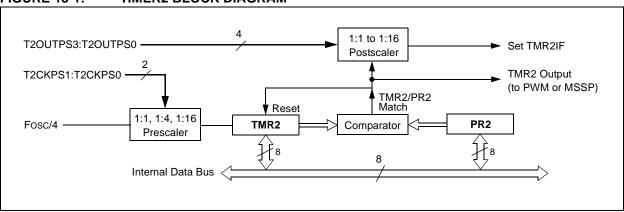

#### 13.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/ postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS3:T2OUTPS0 (T2CON<6:3>).

### 13.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 17.0 "Master Synchronous Serial Port (MSSP) Module".

#### FIGURE 13-1: TIMER2 BLOCK DIAGRAM

#### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                | Bit 6       | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |

|--------|----------------------|-------------|----------|----------|----------|--------|---------|---------|----------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL   | TMR0IE   | INTOIE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 49                         |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF     | TXIF     | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 52                         |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE     | TXIE     | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 52                         |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP        | RCIP     | TXIP     | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 52                         |

| TMR2   | Timer2 Register      |             |          |          |          |        |         | 50      |                            |

| T2CON  |                      | T2OUTPS3    | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 50                         |

| PR2    | Timer2 Peri          | od Register |          |          |          |        |         |         | 50                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

#### 15.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 15.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

# TABLE 15-1:CCP MODE – TIMER<br/>RESOURCES

| CCP/ECCP Mode | Timer Resource   |

|---------------|------------------|

| Capture       | Timer1 or Timer3 |

| Compare       | Timer1 or Timer3 |

| PWM           | Timer2           |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the T3CON register (Register 14-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 15-1 and Figure 15-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

#### 15.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (capture input, compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                                                                                                         |

|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                     |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare            | Capture            | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                              |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                          |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                                                                                                                |

| PWM <sup>(1)</sup> | PWM                | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

#### TABLE 15-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

Note 1: Includes standard and Enhanced PWM operation.

#### 16.4.6 PROGRAMMABLE DEAD-BAND DELAY

| Note: | Programmable          | dead-band | delay is | not  |  |

|-------|-----------------------|-----------|----------|------|--|

|       | implemented           | in 28-pin | devices  | with |  |

|       | standard CCP modules. |           |          |      |  |

In half-bridge applications where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shootthrough current*) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the nonactive state to the active state. See Figure 16-4 for illustration. Bits PDC6:PDC0 of the PWM1CON register (Register 16-2) set the delay period in terms of micro-controller instruction cycles (TcY or 4 ToSc). These bits are not available on 28-pin devices as the standard CCP module does not support half-bridge operation.

#### 16.4.7 ENHANCED PWM AUTO-SHUTDOWN

When the CCP1 is programmed for any of the Enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the Enhanced PWM output pins into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by either of the comparator modules, a low level on the Fault input pin (FLT0) or any combination of these three sources. The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a low digital signal on FLT0 can also trigger a shutdown. The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCPAS2:ECCPAS0 bits (ECCP1AS<6:4>).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits (ECCP1AS<3:0>). Each pin pair (P1A/P1C and P1B/ P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCPASE bit (ECCP1AS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0               | R/W-0               | R/W-0               | R/W-0                                    | R/W-0               | R/W-0               | R/W-0               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|------------------------------------------|---------------------|---------------------|---------------------|

| PRSEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PDC6 <sup>(1)</sup> | PDC5 <sup>(1)</sup> | PDC4 <sup>(1)</sup> | PDC3 <sup>(1)</sup>                      | PDC2 <sup>(1)</sup> | PDC1 <sup>(1)</sup> | PDC0 <sup>(1)</sup> |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |                     |                     |                                          |                     |                     | bit 0               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                     |                     |                                          |                     |                     |                     |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |                     |                     |                                          |                     |                     |                     |

| R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e bit               | W = Writable        | bit                 | U = Unimplem                             | nented bit, read    | l as '0'            |                     |

| -n = Value at                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | POR                 | '1' = Bit is set    |                     | 0' = Bit is cleared $x = Bit is unknown$ |                     |                     | iown                |

| bit 7       PRSEN: PWM Restart Enable bit         1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away; the PWM restarts automatically         0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM         bit 6-0       PDC6:PDC0: PWM Delay Count bits <sup>(1)</sup> Delay time, in number of Fosc/4 (4 * Tosc) cycles, between the scheduled and actual time for a PWM signal to transition to active. |                     |                     |                     |                                          |                     |                     |                     |

| Note 1: Ur                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nimplemented o      | on 28-pin device    | es; bits read as    | <b>s</b> '0'.                            |                     |                     |                     |

#### REGISTER 16-2: PWM1CON: PWM CONFIGURATION REGISTER

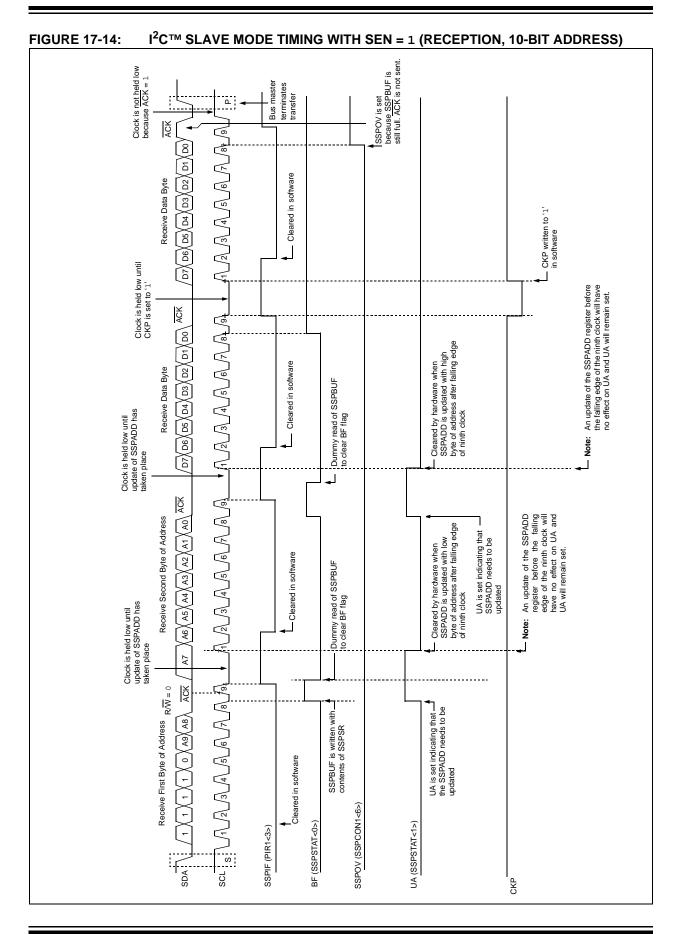

### 17.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 17.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register.

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register.

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

NOTES:

| Bit Test File, Skip if Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|

| BTFSC f, b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |  |  |  |

| $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |  |  |  |

| skip if (f <b>) = 0</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |  |  |  |

| None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |  |  |  |

| 1011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bbba ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ff ffff                                                |  |  |  |

| If bit 'b' in register 'f' is '0', then the next<br>instruction is skipped. If bit 'b' is '0', then<br>the next instruction fetched during the<br>current instruction execution is discarded<br>and a NOP is executed instead, making<br>this a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected. If<br>'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates in<br>Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh).<br>See Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |  |  |  |

| by a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-word instruc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        |  |  |  |