#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

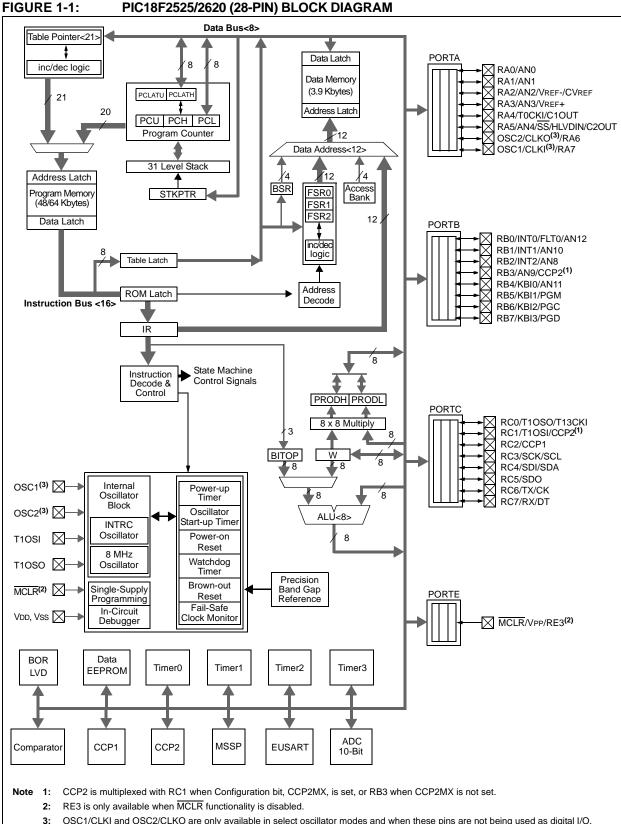

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4620-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 2-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq                     |                                  | acitor Values<br>ted:                     |

|----------|-------------------------------------|----------------------------------|-------------------------------------------|

|          | Fieq                                | C1                               | C2                                        |

| LP       | 32 kHz                              | 30 pF                            | 30 pF                                     |

| XT       | 1 MHz<br>4 MHz                      | 15 pF<br>15 pF                   | 15 pF<br>15 pF                            |

| HS       | 4 MHz<br>10 MHz<br>20 MHz<br>25 MHz | 15 pF<br>15 pF<br>15 pF<br>15 pF | 15 pF<br>15 pF<br>15 pF<br>15 pF<br>15 pF |

#### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- **Note 1:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- Rs may be required to avoid overdriving crystals with low drive level specification.

- **5:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

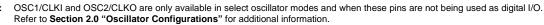

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 2-2.

## 2.3 External Clock Input

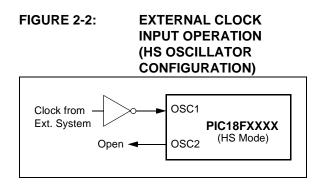

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-3 shows the pin connections for the EC Oscillator mode.

#### EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

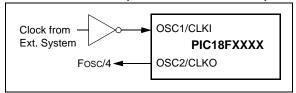

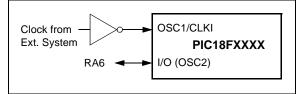

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-4 shows the pin connections for the ECIO Oscillator mode.

FIGURE 2-4:

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

### 4.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI, TO, PD, POR and BOR, are set or cleared differently in different Reset situations, as indicated in Table 4-3. These bits are used in software to determine the nature of the Reset. Table 4-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

|                                                             | Program               |              | RCC | N Reg | gister |     |     | STKPTR | Register |

|-------------------------------------------------------------|-----------------------|--------------|-----|-------|--------|-----|-----|--------|----------|

| Condition                                                   | Counter               | SBOREN       | RI  | то    | PD     | POR | BOR | STKFUL | STKUNF   |

| Power-on Reset                                              | 0000h                 | 1            | 1   | 1     | 1      | 0   | 0   | 0      | 0        |

| RESET Instruction                                           | 0000h                 | u <b>(2)</b> | 0   | u     | u      | u   | u   | u      | u        |

| Brown-out Reset                                             | 0000h                 | u <b>(2)</b> | 1   | 1     | 1      | u   | 0   | u      | u        |

| MCLR during power-managed<br>Run Modes                      | 0000h                 | ս <b>(2)</b> | u   | 1     | u      | u   | u   | u      | u        |

| MCLR during power-managed<br>Idle modes and Sleep mode      | 0000h                 | ս <b>(2)</b> | u   | 1     | 0      | u   | u   | u      | u        |

| WDT time-out during full power<br>or power-managed Run mode | 0000h                 | u <b>(2)</b> | u   | 0     | u      | u   | u   | u      | u        |

| MCLR during full-power execution                            | 0000h                 | ս <b>(2)</b> | u   | u     | u      | u   | u   | u      | u        |

| Stack Full Reset (STVREN = 1)                               | 0000h                 | u <b>(2)</b> | u   | u     | u      | u   | u   | 1      | u        |

| Stack Underflow Reset<br>(STVREN = 1)                       | 0000h                 | u <b>(2)</b> | u   | u     | u      | u   | u   | u      | 1        |

| Stack Underflow Error (not an actual Reset, STVREN = 0)     | 0000h                 | u <b>(2)</b> | u   | u     | u      | u   | u   | u      | 1        |

| WDT time-out during<br>power-managed Idle or Sleep<br>modes | PC + 2                | ս <b>(2)</b> | u   | 0     | 0      | u   | u   | u      | u        |

| Interrupt exit from<br>power-managed modes                  | PC + 2 <sup>(1)</sup> | u <b>(2)</b> | u   | u     | 0      | u   | u   | u      | u        |

## TABLE 4-3:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION<br/>FOR RCON REGISTER

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for POR and unchanged for all other Resets when software BOR is enabled (BOREN1:BOREN0 Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is '0'.

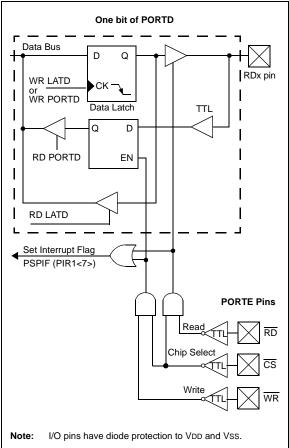

#### 9.6 Parallel Slave Port

| Note: | The Parallel Slave Port is only available on |

|-------|----------------------------------------------|

|       | 40/44-pin devices.                           |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 9-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation as long as the Enhanced CCP module is not operating in dual output or quad output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit, PSPMODE, enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the  $\overline{WR}$  input and RE2 is the  $\overline{CS}$  (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PFCG3:PFCG0 (ADCON1<3:0>), must also be set to a value in the range of '1010' through '1111'.

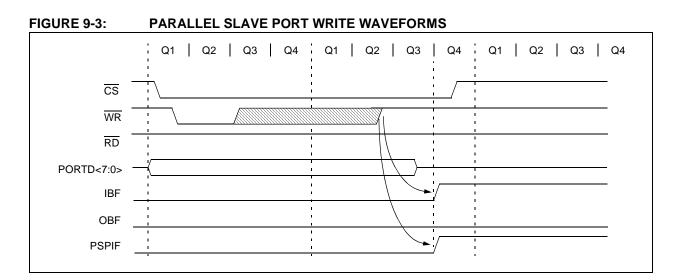

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

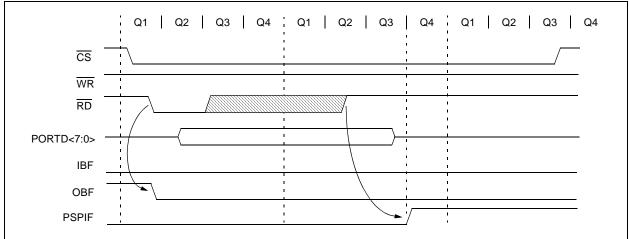

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$ lines are first detected low. The data in PORTD is read out and the OBF bit is clear. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  lines are detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP; when this happens, the IBF and OBF bits can be polled and the appropriate action taken.

The timing for the control signals in Write and Read modes is shown in Figure 9-3 and Figure 9-4, respectively.

#### FIGURE 9-4: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 9-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7                | Bit 6          | Bit 5        | Bit 4        | Bit 3       | Bit 2     | Bit 1       | Bit 0  | Reset<br>Values<br>on page |

|--------|----------------------|----------------|--------------|--------------|-------------|-----------|-------------|--------|----------------------------|

| PORTD  | RD7                  | RD6            | RD5          | RD4          | RD3         | RD2       | RD1         | RD0    | 52                         |

| LATD   | PORTD Da             | ta Latch Reg   | jister (Read | and Write to | Data Latch) | )         |             |        | 52                         |

| TRISD  | PORTD Da             | ta Direction ( | Control Reg  | jister       |             |           |             |        | 52                         |

| PORTE  | —                    | —              | —            | —            | RE3         | RE2       | RE1         | RE0    | 52                         |

| LATE   | —                    | —              | _            | _            | —           | LATE Data | Output bits |        | 52                         |

| TRISE  | IBF                  | OBF            | IBOV         | PSPMODE      | —           | TRISE2    | TRISE1      | TRISE0 | 52                         |

| INTCON | GIE/GIEH             | PEIE/GIEL      | TMR0IF       | INTOIE       | RBIE        | TMR0IF    | INT0IF      | RBIF   | 49                         |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF           | RCIF         | TXIF         | SSPIF       | CCP1IF    | TMR2IF      | TMR1IF | 52                         |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE           | RCIE         | TXIE         | SSPIE       | CCP1IE    | TMR2IE      | TMR1IE | 52                         |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP           | RCIP         | TXIP         | SSPIP       | CCP1IP    | TMR2IP      | TMR1IP | 52                         |

| ADCON1 | _                    | _              | VCFG1        | VCFG0        | PCFG3       | PCFG2     | PCFG1       | PCFG0  | 51                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

Note 1: These bits are unimplemented on 28-pin devices and read as '0'.

### 12.2 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 high byte buffer. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. The Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

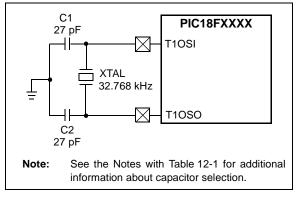

### 12.3 Timer1 Oscillator

An on-chip crystal oscillator circuit is incorporated between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting the Timer1 Oscillator Enable bit, T1OSCEN (T1CON<3>). The oscillator is a low-power circuit rated for 32 kHz crystals. It will continue to run during all power-managed modes. The circuit for a typical LP oscillator is shown in Figure 12-3. Table 12-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

#### FIGURE 12-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

## TABLE 12-1:CAPACITOR SELECTION FOR<br/>THE TIMER OSCILLATOR

| Osc Type | Freq                                                                                                     | C1                             | C2                            |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|--|--|--|

| LP       | 32 kHz                                                                                                   | 27 pF <sup>(1)</sup>           | 27 pF <sup>(1)</sup>          |  |  |  |

| Note 1:  | Microchip sug<br>starting point<br>circuit.                                                              | 0                              |                               |  |  |  |

| 2:       | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. |                                |                               |  |  |  |

| 3:       | Since each rescharacteristics<br>the resonator,<br>appropriate<br>components.                            | , the user sh<br>/crystal manu | ould consult<br>ufacturer for |  |  |  |

| 4:       | Capacitor valuonity.                                                                                     | es are for des                 | ign guidance                  |  |  |  |

#### 12.3.1 USING TIMER1 AS A CLOCK SOURCE

The Timer1 oscillator is also available as a clock source in power-managed modes. By setting the clock select bits, SCS1:SCS0 (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode; both the CPU and peripherals are clocked from the Timer1 oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in **Section 3.0 "Power-Managed Modes"**.

Whenever the Timer1 oscillator is providing the clock source, the Timer1 system clock status flag, T1RUN (T1CON<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source being currently used by the Fail-Safe Clock Monitor. If the Clock Monitor is enabled and the Timer1 oscillator fails while providing the clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

### 12.3.2 LOW-POWER TIMER1 OPTION

The Timer1 oscillator can operate at two distinct levels of power consumption based on device configuration. When the LPT1OSC Configuration bit is set, the Timer1 oscillator operates in a low-power mode. When LPT1OSC is not set, Timer1 operates at a higher power level. Power consumption for a particular mode is relatively constant, regardless of the device's operating mode. The default Timer1 configuration is the higher power mode.

As the low-power Timer1 mode tends to be more sensitive to interference, high noise environments may cause some oscillator instability. The low-power option is, therefore, best suited for low noise applications where power conservation is an important design consideration.

| R/W-0         | R/W-0                                                                                                 | R/W-0                                                                       | R/W-0                                                                              | R/W-0                                                  | R/W-0                                     | R/W-0            | R/W-0          |

|---------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|------------------|----------------|

| WCOL          | SSPOV                                                                                                 | SSPEN <sup>(1)</sup>                                                        | CKP                                                                                | SSPM3                                                  | SSPM2                                     | SSPM1            | SSPM0          |

| bit 7         |                                                                                                       |                                                                             |                                                                                    |                                                        |                                           |                  | bit            |

| Lonondi       |                                                                                                       |                                                                             |                                                                                    |                                                        |                                           |                  |                |

| Legend:       |                                                                                                       |                                                                             | .,                                                                                 |                                                        |                                           |                  |                |

| R = Readabl   |                                                                                                       | W = Writable k                                                              | Dit                                                                                | -                                                      | nented bit, read                          |                  |                |

| -n = Value at | t POR                                                                                                 | '1' = Bit is set                                                            |                                                                                    | '0' = Bit is clea                                      | ared                                      | x = Bit is unkr  | nown           |

| bit 7         | WCOL: Write                                                                                           | e Collision Detec                                                           | t bit                                                                              |                                                        |                                           |                  |                |

|               | In Master Tra                                                                                         |                                                                             |                                                                                    |                                                        |                                           |                  |                |

|               |                                                                                                       | to the SSPBUF                                                               |                                                                                    |                                                        |                                           | nditions were i  | not valid for  |

|               |                                                                                                       | sion to be starte                                                           | d (must be cl                                                                      | eared in softwa                                        | re)                                       |                  |                |

|               | 0 = No  collis                                                                                        |                                                                             |                                                                                    |                                                        |                                           |                  |                |

|               | In Slave Tran                                                                                         | PBUF register is                                                            | written while                                                                      | it is still transm                                     | itting the previo                         | ous word (mus    | t he cleared i |

|               | software                                                                                              |                                                                             |                                                                                    |                                                        | intering the provide                      |                  |                |

|               | 0 = No collis                                                                                         | ion                                                                         |                                                                                    |                                                        |                                           |                  |                |

|               |                                                                                                       | ode (Master or S                                                            | <u>Slave modes)</u>                                                                | <u>:</u>                                               |                                           |                  |                |

|               | This is a "dor                                                                                        | n't care" bit.                                                              |                                                                                    |                                                        |                                           |                  |                |

| bit 6         |                                                                                                       | eive Overflow Ir                                                            | dicator bit                                                                        |                                                        |                                           |                  |                |

|               | In Receive m                                                                                          |                                                                             |                                                                                    |                                                        |                                           |                  |                |

|               | 1 = A byte is software                                                                                | s received while                                                            | the SSPBUF                                                                         | register is still h                                    | olding the prev                           | ious byte (mus   | t be cleared i |

|               | 0 = No overf                                                                                          | /                                                                           |                                                                                    |                                                        |                                           |                  |                |

|               | In Transmit n                                                                                         | node:                                                                       |                                                                                    |                                                        |                                           |                  |                |

|               |                                                                                                       | n't care" bit in Tra                                                        | ansmit mode.                                                                       |                                                        |                                           |                  |                |

| bit 5         | SSPEN: Mas                                                                                            | ster Synchronous                                                            | s Serial Port E                                                                    | Enable bit <sup>(1)</sup>                              |                                           |                  |                |

|               |                                                                                                       | the serial port ar                                                          |                                                                                    |                                                        | CL pins as the                            | serial port pins | i              |

|               | 0 = Disables                                                                                          | serial port and c                                                           | onfigures the                                                                      | se pins as I/O p                                       | oort pins                                 |                  |                |

| bit 4         | CKP: SCK R                                                                                            | elease Control b                                                            | oit                                                                                |                                                        |                                           |                  |                |

|               | In Slave mod                                                                                          |                                                                             |                                                                                    |                                                        |                                           |                  |                |

|               | 1 = Releases                                                                                          |                                                                             |                                                                                    |                                                        | ture time e                               |                  |                |

|               | In Master mo                                                                                          | ock low (clock str                                                          | etch), used to                                                                     | o ensure data se                                       | etup time                                 |                  |                |

|               | Unused in th                                                                                          |                                                                             |                                                                                    |                                                        |                                           |                  |                |

|               |                                                                                                       |                                                                             |                                                                                    |                                                        | (0)                                       |                  |                |

| bit 3-0       | SSPM3:SSP                                                                                             | M0: Master Svn                                                              | chronous Ser                                                                       | ial Port Mode S                                        | elect bits <sup>(2)</sup>                 |                  |                |

| bit 3-0       |                                                                                                       | <b>M0:</b> Master Syn<br>Slave mode, 10-b                                   |                                                                                    |                                                        |                                           | enabled          |                |

| bit 3-0       | $1111 = I^2 C S$<br>$1110 = I^2 C S$                                                                  | Slave mode, 10-b<br>Slave mode, 7-bi                                        | oit address wi<br>t address with                                                   | th Start and Ston<br>Start and Stop                    | p bit interrupts<br>bit interrupts e      |                  |                |

| bit 3-0       | $1111 = I^2CS$<br>$1110 = I^2CS$<br>$1011 = I^2CF$                                                    | Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Contro                     | oit address wi<br>t address with<br>lled Master m                                  | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |

| bit 3-0       | $1111 = I^{2}C S$<br>$1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C N$                      | Blave mode, 10-b<br>Blave mode, 7-bi<br>Firmware Contro<br>Master mode, clo | bit address wi<br>t address with<br>lled Master m<br>lock = FOSC/(4                | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |

| bit 3-0       | $1111 = I^{2}C S$<br>$1110 = I^{2}C S$<br>$1011 = I^{2}C F$<br>$1000 = I^{2}C N$<br>$0111 = I^{2}C S$ | Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Contro                     | bit address wi<br>t address with<br>lled Master m<br>lock = Fosc/(4<br>bit address | th Start and Sto<br>Start and Stop<br>ode (Slave Idle) | p bit interrupts<br>bit interrupts e<br>) |                  |                |

## REGISTER 17-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

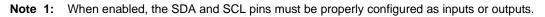

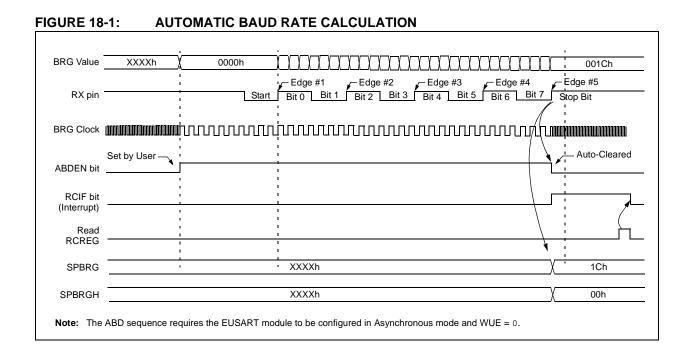

### 18.1.3 AUTO-BAUD RATE DETECT

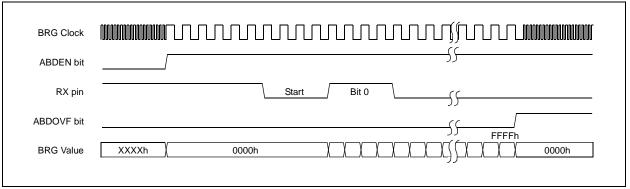

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 18-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value, 55h (ASCII "U", which is also the LIN bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG begins counting up, using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGH:SPBRG register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCON<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 18-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRG and SPBRGH will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGH register. Refer to Table 18-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. The contents of RCREG should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

#### TABLE 18-4: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/128          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

|       |      |                   |

**Note:** During the ABD sequence, SPBRG and SPBRGH are both used as a 16-bit counter, independent of BRG16 setting.

#### 18.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREG cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

### FIGURE 18-2: BRG OVERFLOW SEQUENCE

## 19.8 Use of the CCP2 Trigger

An A/D conversion can be started by the Special Event Trigger of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D acquisition and conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH:ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition period is either timed by the user, or an appropriate TACQ time selected before the Special Event Trigger sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the Special Event Trigger will be ignored by the A/D module but will still reset the Timer1 (or Timer3) counter.

| Name                 | Bit 7                 | Bit 6                 | Bit 5       | Bit 4          | Bit 3              | Bit 2    | Bit 1        | Bit 0  | Reset<br>Values<br>on page |

|----------------------|-----------------------|-----------------------|-------------|----------------|--------------------|----------|--------------|--------|----------------------------|

| INTCON               | GIE/GIEH              | PEIE/GIEL             | TMR0IE      | INTOIE         | RBIE               | TMR0IF   | INT0IF       | RBIF   | 49                         |

| PIR1                 | PSPIF <sup>(1)</sup>  | ADIF                  | RCIF        | TXIF           | SSPIF              | CCP1IF   | TMR2IF       | TMR1IF | 52                         |

| PIE1                 | PSPIE <sup>(1)</sup>  | ADIE                  | RCIE        | TXIE           | SSPIE              | CCP1IE   | TMR2IE       | TMR1IE | 52                         |

| IPR1                 | PSPIP <sup>(1)</sup>  | ADIP                  | RCIP        | TXIP           | SSPIP              | CCP1IP   | TMR2IP       | TMR1IP | 52                         |

| PIR2                 | OSCFIF                | CMIF                  | _           | EEIF           | BCLIF              | HLVDIF   | TMR3IF       | CCP2IF | 52                         |

| PIE2                 | OSCFIE                | CMIE                  | _           | EEIE           | BCLIE              | HLVDIE   | TMR3IE       | CCP2IE | 52                         |

| IPR2                 | OSCFIP                | CMIP                  | _           | EEIP           | BCLIP              | HLVDIP   | TMR3IP       | CCP2IP | 52                         |

| ADRESH               | A/D Result            | Register Hig          | gh Byte     |                |                    |          |              |        | 51                         |

| ADRESL               | A/D Result            | Register Lov          | w Byte      |                |                    |          |              |        | 51                         |

| ADCON0               | _                     | _                     | CHS3        | CHS2           | CHS1               | CHS0     | GO/DONE      | ADON   | 51                         |

| ADCON1               | _                     | _                     | VCFG1       | VCFG0          | PCFG3              | PCFG2    | PCFG1        | PCFG0  | 51                         |

| ADCON2               | ADFM                  | _                     | ACQT2       | ACQT1          | ACQT0              | ADCS2    | ADCS1        | ADCS0  | 51                         |

| PORTA                | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5         | RA4            | RA3                | RA2      | RA1          | RA0    | 52                         |

| TRISA                | TRISA7 <sup>(2)</sup> | TRISA6 <sup>(2)</sup> | PORTA Da    | ta Direction C | Control Reg        | ister    |              |        | 52                         |

| PORTB                | RB7                   | RB6                   | RB5         | RB4            | RB3                | RB2      | RB1          | RB0    | 52                         |

| TRISB                | PORTB Dat             | a Direction 0         | Control Reg | ister          |                    |          |              |        | 52                         |

| LATB                 | PORTB Dat             | a Latch Reg           | ister (Read | and Write to   | Data Latch)        | )        |              |        | 52                         |

| PORTE <sup>(4)</sup> | —                     |                       |             |                | RE3 <sup>(3)</sup> | RE2      | RE1          | RE0    | 52                         |

| TRISE <sup>(4)</sup> | IBF                   | OBF                   | IBOV        | PSPMODE        |                    | TRISE2   | TRISE1       | TRISE0 | 52                         |

| LATE <sup>(4)</sup>  | —                     | —                     | —           |                |                    | PORTE Da | ata Latch Re | gister | 52                         |

TABLE 19-2:

REGISTERS ASSOCIATED WITH A/D OPERATION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These bits are unimplemented on 28-pin devices; always maintain these bits clear.

2: PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

3: RE3 port bit is available only as an input pin when the MCLRE Configuration bit is '0'.

4: These registers are not implemented on 28-pin devices.

## 22.1 Operation

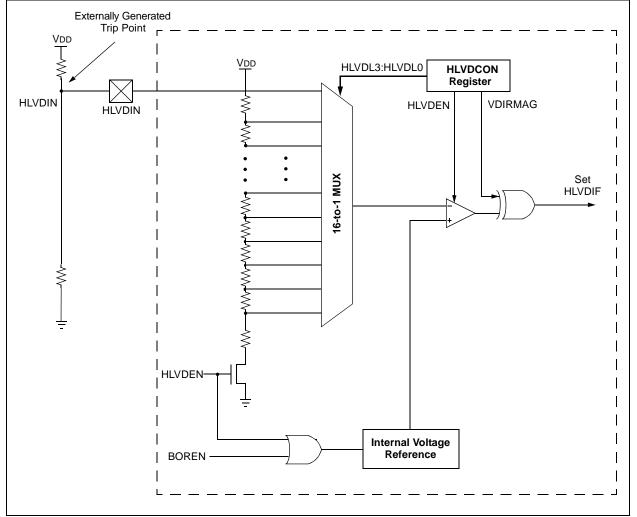

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module. When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit. The trip point voltage is software programmable to any one of 16 values. The trip point is selected by programming the HLVDL3:HLVDL0 bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits HLVDL3:HLVDL0 are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users flexibility because it allows them to configure the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

### 22.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

### 22.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG  | _         | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 50                         |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 49                         |

| PIR2    | OSCFIF   | CMIF      | —      | EEIF   | BCLIF  | HLVDIF | TMR3IF | CCP2IF | 52                         |

| PIE2    | OSCFIE   | CMIE      | —      | EEIE   | BCLIE  | HLVDIE | TMR3IE | CCP2IE | 52                         |

| IPR2    | OSCFIP   | CMIP      |        | EEIP   | BCLIP  | HLVDIP | TMR3IP | CCP2IP | 52                         |

#### TABLE 22-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

### REGISTER 23-8: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0   | U-0 | U-0 | U-0 | R/C-1               | R/C-1 | R/C-1 | R/C-1 |

|-------|-----|-----|-----|---------------------|-------|-------|-------|

| —     | —   | —   | —   | WRT3 <sup>(1)</sup> | WRT2  | WRT1  | WRT0  |

| bit 7 |     |     |     |                     |       |       | bit 0 |

| Legend:      |                                                                         |                                                                                     |                                     |

|--------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------|

| R = Readal   | R = Readable bitC = Clearable bit-n = Value when device is unprogrammed |                                                                                     | U = Unimplemented bit, read as '0'  |

| -n = Value v |                                                                         |                                                                                     | u = Unchanged from programmed state |

| bit 7-4      | Unimple                                                                 | mented: Read as '0'                                                                 |                                     |

| bit 3        | WRT3: \                                                                 | Vrite Protection bit <sup>(1)</sup>                                                 |                                     |

|              |                                                                         | k 3 (006000-007FFFh) not wr<br>k 3 (006000-007FFFh) write-r                         |                                     |

| bit 2        | WRT2: \                                                                 | Vrite Protection bit                                                                |                                     |

|              |                                                                         | k 2 (004000-005FFFh) not wr<br>k 2 (004000-005FFFh) write-r                         | •                                   |

| bit 1        | WRT1: \                                                                 | Vrite Protection bit                                                                |                                     |

|              |                                                                         | k 1 (002000-003FFFh) not wr<br>k 1 (002000-003FFFh) write-p                         |                                     |

| bit 0        | 1 = Bloc                                                                | Vrite Protection bit<br>k 0 (000800-001FFFh) not wr<br>k 0 (000800-001FFFh) write-p |                                     |

**Note 1:** Unimplemented in PIC18FX525 devices; maintain this bit set.

#### REGISTER 23-9: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| R/C-1 | R/C-1 | R/C-1               | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|---------------------|-----|-----|-----|-----|-------|

| WRTD  | WRTB  | WRTC <sup>(1)</sup> | _   | —   | —   | —   | —     |

| bit 7 |       |                     |     |     |     |     | bit 0 |

| Legend:                                |                                                                                               |                                     |  |  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|

| R = Read                               | lable bit C = Clearable bit                                                                   | U = Unimplemented bit, read as '0'  |  |  |  |  |

| -n = Value when device is unprogrammed |                                                                                               | u = Unchanged from programmed state |  |  |  |  |

| bit 7                                  | WRTD: Data EEPROM Write Protect<br>1 = Data EEPROM not write-protecte                         |                                     |  |  |  |  |

| bit 6                                  | <ul><li>0 = Data EEPROM write-protected</li><li>WRTB: Boot Block Write Protection b</li></ul> | bit                                 |  |  |  |  |

|                                        | 1 = Boot block (000000-0007FFh) no                                                            | ot write-protected                  |  |  |  |  |

|     | DOOL | DIOOK | (00000 | 0 000  | , , , , ,,, |           | protocicc |

|-----|------|-------|--------|--------|-------------|-----------|-----------|

| 0 = | Boot | block | (00000 | 0-0007 | 7FFh)       | write-pro | tected    |

- bit 5 WRTC: Configuration Register Write Protection bit<sup>(1)</sup>

- 1 = Configuration registers (300000-3000FFh) not write-protected

- 0 = Configuration registers (300000-3000FFh) write-protected

- bit 4-0 Unimplemented: Read as '0'

Note 1: This bit is read-only in normal execution mode; it can be written only in Program mode.

| Mnemo     | onic,   | 5                              |            | 16-  | Bit Instr | uction W | /ord | Status                 |       |

|-----------|---------|--------------------------------|------------|------|-----------|----------|------|------------------------|-------|

| Opera     | nds     | Description                    | Cycles     | MSb  |           |          | LSb  | Affected               | Notes |

| BIT-ORIEN | ITED OP | ERATIONS                       |            |      |           |          |      |                        |       |

| BCF       | f, b, a | Bit Clear f                    | 1          | 1001 | bbba      | ffff     | ffff | None                   | 1, 2  |

| BSF       | f, b, a | Bit Set f                      | 1          | 1000 | bbba      | ffff     | ffff | None                   | 1, 2  |

| BTFSC     | f, b, a | Bit Test f, Skip if Clear      | 1 (2 or 3) | 1011 | bbba      | ffff     | ffff | None                   | 3, 4  |

| BTFSS     | f, b, a | Bit Test f, Skip if Set        | 1 (2 or 3) | 1010 | bbba      | ffff     | ffff | None                   | 3, 4  |

| BTG       | f, b, a | Bit Toggle f                   | 1          | 0111 | bbba      | ffff     | ffff | None                   | 1, 2  |

| CONTROL   | OPERA   | TIONS                          |            |      |           |          |      |                        |       |

| вС        | n       | Branch if Carry                | 1 (2)      | 1110 | 0010      | nnnn     | nnnn | None                   |       |

| BN        | n       | Branch if Negative             | 1 (2)      | 1110 | 0110      | nnnn     | nnnn | None                   |       |

| BNC       | n       | Branch if Not Carry            | 1 (2)      | 1110 | 0011      | nnnn     | nnnn | None                   |       |

| BNN       | n       | Branch if Not Negative         | 1 (2)      | 1110 | 0111      | nnnn     | nnnn | None                   |       |

| BNOV      | n       | Branch if Not Overflow         | 1 (2)      | 1110 | 0101      | nnnn     | nnnn | None                   |       |

| BNZ       | n       | Branch if Not Zero             | 1 (2)      | 1110 | 0001      | nnnn     | nnnn | None                   |       |

| BOV       | n       | Branch if Overflow             | 1 (2)      | 1110 | 0100      | nnnn     | nnnn | None                   |       |

| BRA       | n       | Branch Unconditionally         | 2          | 1101 | 0nnn      | nnnn     | nnnn | None                   |       |

| BZ        | n       | Branch if Zero                 | 1 (2)      | 1110 | 0000      | nnnn     | nnnn | None                   |       |

| CALL      | n, s    | Call Subroutine 1st word       | 2          | 1110 | 110s      | kkkk     | kkkk | None                   |       |

|           |         | 2nd word                       |            | 1111 | kkkk      | kkkk     | kkkk |                        |       |

| CLRWDT    | _       | Clear Watchdog Timer           | 1          | 0000 | 0000      | 0000     | 0100 | TO, PD                 |       |

| DAW       | _       | Decimal Adjust WREG            | 1          | 0000 | 0000      | 0000     | 0111 | С                      |       |

| GOTO      | n       | Go to Address 1st word         | 2          | 1110 | 1111      | kkkk     | kkkk | None                   |       |

|           |         | 2nd word                       |            | 1111 | kkkk      | kkkk     | kkkk |                        |       |

| NOP       | —       | No Operation                   | 1          | 0000 | 0000      | 0000     | 0000 | None                   |       |

| NOP       | —       | No Operation                   | 1          | 1111 | xxxx      | xxxx     | xxxx | None                   | 4     |

| POP       | —       | Pop Top of Return Stack (TOS)  | 1          | 0000 | 0000      | 0000     | 0110 | None                   |       |

| PUSH      | _       | Push Top of Return Stack (TOS) | 1          | 0000 | 0000      | 0000     | 0101 | None                   |       |

| RCALL     | n       | Relative Call                  | 2          | 1101 | 1nnn      | nnnn     | nnnn | None                   |       |

| RESET     |         | Software Device Reset          | 1          | 0000 | 0000      | 1111     | 1111 | All                    |       |

| RETFIE    | S       | Return from Interrupt Enable   | 2          | 0000 | 0000      | 0001     | 000s | GIE/GIEH,<br>PEIE/GIEL |       |

| RETLW     | k       | Return with Literal in WREG    | 2          | 0000 | 1100      | kkkk     | kkkk | None                   |       |

| RETURN    | S       | Return from Subroutine         | 2          | 0000 | 0000      | 0001     | 001s | None                   |       |

| SLEEP     | _       | Go into Standby mode           | 1          | 0000 | 0000      | 0000     | 0011 | TO, PD                 |       |

#### TABLE 24-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| BTG                                                  | Bit Toggle f                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BOV                                                                                           | Branch if Overflow                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                              | BTG f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Syntax:                                                                                       | BOV n                                                                                                                                                                                                                                                                                                                       |

| Operands:                                            | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Operands:                                                                                     | $-128 \le n \le 127$                                                                                                                                                                                                                                                                                                        |

|                                                      | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Operation:                                                                                    | if Overflow bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                                                   |

| Operation:                                           | $(f < b >) \rightarrow f < b >$                                                                                                                                                                                                                                                                                                                                                                                                                                          | Status Affected:                                                                              | None                                                                                                                                                                                                                                                                                                                        |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Encoding:                                                                                     | 1110 0100 nnnn nnnn                                                                                                                                                                                                                                                                                                         |

| Encoding:<br>Description:                            | 0111bbbaffffffffBit 'b' in data memory location 'f' is<br>inverted.If 'a' is '0', the Access Bank is selected.If 'a' is '0', the BSR is used to select the<br>GPR bank.GPR bank.If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. | Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>If Jump:                            | <ul> <li>If the Overflow bit is '1', then the program will branch.</li> <li>The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a two-cycle instruction.</li> <li>1</li> <li>1(2)</li> </ul> |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q1                                                                                            | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                    |

| Cycles:<br>Q Cycle Activity:                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Decode                                                                                        | Read literal<br>'n'         Process         Write to PC                                                                                                                                                                                                                                                                     |

| Q Cycle Activity.<br>Q1                              | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | No                                                                                            | No No No                                                                                                                                                                                                                                                                                                                    |

| Decode                                               | Read Process Write<br>register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                     | operation<br>If No Jump:<br>Q1                                                                | operation     operation     operation       Q2     Q3     Q4                                                                                                                                                                                                                                                                |

| Example:                                             | BTG PORTC, 4, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Decode                                                                                        | Read literal Process No<br>'n' Data operation                                                                                                                                                                                                                                                                               |

| Before Instruc<br>PORTC<br>After Instructic<br>PORTC | = 0111 0101 <b>[75h]</b><br>on:                                                                                                                                                                                                                                                                                                                                                                                                                                          | Example:<br>Before Instruct<br>PC<br>After Instructio<br>If Overflo<br>PC<br>If Overflo<br>PC | HERE BOV Jump<br>ction<br>= address (HERE)<br>on<br>bw = 1;<br>= address (Jump)                                                                                                                                                                                                                                             |

### 24.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, PIC18F2525/2620/4525/4620 devices also provide an optional extension to the core CPU functionality. The added features include eight additional instructions that augment indirect and indexed addressing operations and the implementation of Indexed Literal Offset Addressing mode for many of the standard PIC18 instructions.

The additional features of the extended instruction set are disabled by default. To enable them, users must set the XINST Configuration bit.

The instructions in the extended set (with the exception of CALLW, MOVSF and MOVSS) can all be classified as literal operations, which either manipulate the File Select Registers, or use them for Indexed Addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- Function Pointer invocation

- Software Stack Pointer manipulation

- manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 24-3. Detailed descriptions are provided in **Section 24.2.2** "**Extended Instruction Set**". The opcode field descriptions in Table 24-1 (page 268) apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

### 24.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of indexed addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. The MPASM<sup>TM</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byteoriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 24.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

| Mnemo   | onic,                           | Description                              | Cycles | 16-E | Bit Instru | uction V | Vord | Status   |

|---------|---------------------------------|------------------------------------------|--------|------|------------|----------|------|----------|

| Opera   | nds                             | Description                              | Cycles | MSb  |            |          | LSb  | Affected |

| ADDFSR  | f, k                            | Add Literal to FSR                       | 1      | 1110 | 1000       | ffkk     | kkkk | None     |

| ADDULNK | k                               | Add Literal to FSR2 and Return           | 2      | 1110 | 1000       | 11kk     | kkkk | None     |

| CALLW   |                                 | Call Subroutine using WREG               | 2      | 0000 | 0000       | 0001     | 0100 | None     |

| MOVSF   | z <sub>s</sub> , f <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110 | 1011       | 0zzz     | ZZZZ | None     |

|         |                                 | f <sub>d</sub> (destination)2nd word     |        | 1111 | ffff       | ffff     | ffff |          |

| MOVSS   | z <sub>s</sub> , z <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110 | 1011       | lzzz     | ZZZZ | None     |

|         | 0 u                             | z <sub>d</sub> (destination)2nd word     |        | 1111 | xxxx       | XZZZ     | ZZZZ |          |

| PUSHL   | k                               | Store Literal at FSR2,                   | 1      | 1110 | 1010       | kkkk     | kkkk | None     |

|         |                                 | Decrement FSR2                           |        |      |            |          |      |          |

| SUBFSR  | f, k                            | Subtract Literal from FSR                | 1      | 1110 | 1001       | ffkk     | kkkk | None     |

| SUBULNK | k                               | Subtract Literal from FSR2 and Return    | 2      | 1110 | 1001       | 11kk     | kkkk | None     |

### TABLE 24-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

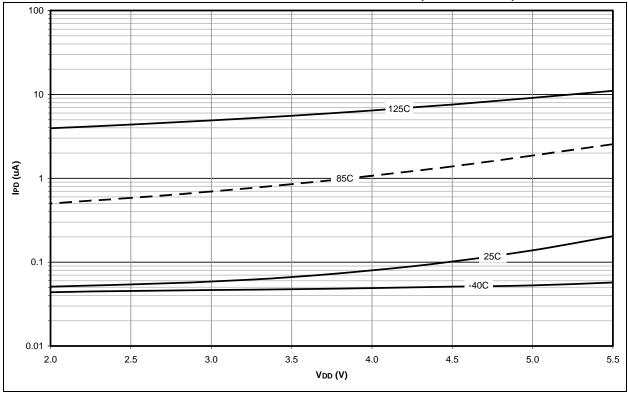

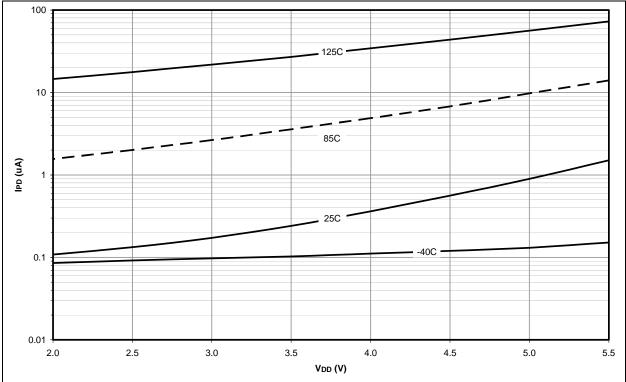

### FIGURE 27-2: TYPICAL IPD vs. VDD ACROSS TEMPERATURE (SLEEP MODE)