Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

#### Details

XF

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Active                                                                      |

| Applications            | USB Microcontroller                                                         |

| Core Processor          | M8C                                                                         |

| Program Memory Type     | FLASH (8kB)                                                                 |

| Controller Series       | CY7C643xx                                                                   |

| RAM Size                | 1K x 8                                                                      |

| Interface               | I <sup>2</sup> C, SPI, USB                                                  |

| Number of I/O           | 25                                                                          |

| Voltage - Supply        | 3V ~ 5.5V                                                                   |

| Operating Temperature   | 0°C ~ 70°C                                                                  |

| Mounting Type           | Surface Mount                                                               |

| Package / Case          | 32-UFQFN Exposed Pad                                                        |

| Supplier Device Package | 32-QFN (5x5)                                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c64343-32lqxc |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Functional Overview**

The enCoRe V family of devices are designed to replace multiple traditional full-speed USB microcontroller system components with one, low cost single-chip programmable component. Communication peripherals (I<sup>2</sup>C/SPI), a fast CPU, Flash program memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts.

The architecture for this device family, as illustrated in the enCoRe V Block Diagram on page 1, consists of two main areas: the CPU core and the system resources. Depending on the enCoRe V package, up to 36 GPIO are also included.

This product is an enhanced version of Cypress's successful full speed-USB peripheral controllers. Enhancements include faster CPU at lower voltage operation, lower current consumption, twice the RAM and Flash, hot-swappable I/Os, I<sup>2</sup>C hardware address recognition, new very low current sleep mode, and new package options.

#### The enCoRe V Core

The enCoRe V Core is a powerful engine that supports a rich instruction set. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers, and IMO and ILO. The CPU core, called the M8C, is a powerful processor with speeds up to 24 MHz. The M8C is a four-MIPS, 8-bit Harvard architecture microprocessor.

During USB operation, the CPU speed can be set to any setting. Be aware that USB throughput decreases with a decrease in CPU speed. For maximum throughput, the CPU clock should be made equal to the system clock. The system clock must be 24 MHz for USB operation.

System resources provide additional capability, such as a configurable I<sup>2</sup>C slave and SPI master-slave communication interface and various system resets supported by the M8C.

### Full-Speed USB

The enCoRe V USB system resource adheres to the USB 2.0 Specification for full speed devices operating at 12 Mb/second with one upstream port and one USB address. enCoRe V USB consists of these components:

- Serial interface engine (SIE) block.

- PSoC memory arbiter (PMA) block.

- 512 bytes of dedicated SRAM.

- A full-speed USB Transceiver with internal regulator and two dedicated USB pins.

#### Figure 1. USB Transceiver Regulator

At the enCoRe V system level, the full-speed USB system resource interfaces to the rest of the enCoRe V by way of the M8C's register access instructions and to the outside world by way of the two USB pins. The SIE supports nine endpoints including a bidirectional control endpoint (endpoint 0) and eight unidirectional data endpoints (endpoints 1 to 8). The unidirectional data endpoints are individually configurable as either IN or OUT.

Low value series resistors  $R_{EXT}$  (22  $\Omega$ ) must be added externally to the D+ and D– lines to meet the driving impedance requirement for full-speed USB.

The USB Serial Interface Engine (SIE) allows the enCoRe V device to communicate with the USB host at full speed data rates (12 Mb/s). The SIE simplifies the interface to USB traffic by automatically handling the following USB processing tasks without firmware intervention:

- Translates the encoded received data and formats the data to be transmitted on the bus.

- Generates and checks cyclical redundancy checks (CRCs). Incoming packets failing checksum verification are ignored.

- Checks addresses. Ignores all transactions not addressed to the device.

- Sends appropriate ACK/NAK/Stall handshakes.

- Identifies token type (SETUP, IN, OUT) and sets the appropriate token bit once a valid token in received.

- Identifies Start-of-Frame (SOF) and saves the frame count.

- Sends data to or retrieves data from the USB SRAM, by way of the PSoC Memory Arbiter (PMA).

# Additional System Resources

System resources, some of which have been previously listed, provide additional capability useful to complete systems. Additional resources include low voltage detection and power on reset. The following statements describe the merits of each system resource.

- Low voltage detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced POR (power on reset) circuit eliminates the need for a system supervisor.

- The 5 V maximum input, 1.8, 2.5, or 3 V selectable output, LDO regulator provides regulation for I/Os. A register controlled bypass mode enables the user to disable the LDO.

- Standard Cypress PSoC IDE tools are available for debugging the enCoRe V family of parts.

# **Getting Started**

The quickest path to understanding the enCoRe V silicon is by reading this data sheet and using the PSoC Designer Integrated Development Environment (IDE). This datasheet is an overview of the PSoC integrated circuit and presents specific pin, register, and electrical specifications. For in-depth information, along with detailed programming information, see the enCoRe<sup>TM</sup> V CY7C643xx, enCoRe<sup>TM</sup> V LV CY7C604xx Technical Reference Manual (TRM) for this PSoC device.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device data sheets on the web at http://www.cypress.com.

#### Application Notes

Application notes are an excellent introduction to the wide variety of possible PSoC designs and are available at http://www.cypress.com.

#### **Development Kits**

PSoC development kits are available online from Cypress at http://www.cypress.com and through a growing number of regional and global distributors, including Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

#### Training

Free PSoC technical training (on demand, webinars, and workshops) is available online at http://www.cypress.com. The training covers a wide variety of topics and skill levels to assist you in your designs.

#### **CYPros Consultants**

Certified PSoC Consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC Consultant, go to http://www.cypress.com and look for CYPros Consultants.

#### **Solutions Library**

Visit our growing library of solution-focused designs at http://www.cypress.com. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

#### **Technical Support**

For assistance with technical issues, search KnowledgeBase articles and forums at http://www.cypress.com. If you cannot find an answer to your question, call technical support at 1-800-541-4736.

# **Pin Information**

The enCoRe V USB device is available in a variety of packages which are listed and illustrated in the subsequent tables.

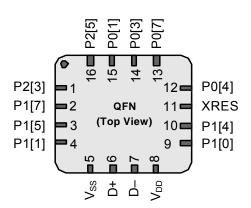

# 16-pin part pinout

Figure 6. CY7C64315/CY7C64316 16-pin enCoRe V USB Device

# **Pin Definitions**

16-pin part pinout (QFN)

| Pin No. | Туре     | Name                    | Description                                           |

|---------|----------|-------------------------|-------------------------------------------------------|

| 1       | I/O      | P2[3]                   | Digital I/O, crystal input (Xin)                      |

| 2       | I/OHR    | P1[7]                   | Digital I/O, SPI SS, I <sup>2</sup> C SCL             |

| 3       | I/OHR    | P1[5]                   | Digital I/O, SPI MISO, I <sup>2</sup> C SDA           |

| 4       | I/OHR    | P1[1] <sup>[1, 2]</sup> | Digital I/O, ISSP CLK, I <sup>2</sup> C SCL, SPI MOSI |

| 5       | Power    | V <sub>SS</sub>         | Ground connection                                     |

| 6       | USB line | D+                      | USB PHY                                               |

| 7       | USB line | D-                      | USB PHY                                               |

| 8       | Power    | V <sub>DD</sub>         | Supply                                                |

| 9       | I/OHR    | P1[0] <sup>[1, 2]</sup> | Digital I/O, ISSP DATA, I <sup>2</sup> C SDA, SPI CLK |

| 10      | I/OHR    | P1[4]                   | Digital I/O, optional external clock input (EXTCLK)   |

| 11      | Input    | XRES                    | Active high external reset with internal pull-down    |

| 12      | I/OH     | P0[4]                   | Digital I/O                                           |

| 13      | I/OH     | P0[7]                   | Digital I/O                                           |

| 14      | I/OH     | P0[3]                   | Digital I/O                                           |

| 15      | I/OH     | P0[1]                   | Digital I/O                                           |

| 16      | I/O      | P2[5]                   | Digital I/O, crystal output (Xout)                    |

LEGEND I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output

#### Notes

During power up or reset event, device P1[0] and P1[1] may disturb the I<sup>2</sup>C bus. Use alternate pins if issues are encountered.

These are the in-system serial programming (ISSP) pins that are not High Z at power on reset (POR).

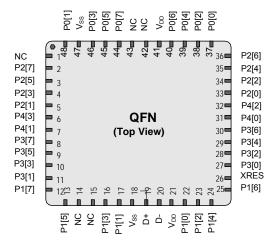

# **48-pin Part Pinout**

#### Figure 8. CY7C64355/CY7C64356 48-pin enCoRe V USB Device

#### **Pin Definitions**

48-pin Part Pinout (QFN)

| Pin No. | Туре  | Pin Name                | Description                                           |

|---------|-------|-------------------------|-------------------------------------------------------|

| 1       | NC    | NC                      | No connection                                         |

| 2       | I/O   | P2[7]                   | Digital I/O                                           |

| 3       | I/O   | P2[5]                   | Digital I/O, crystal out (Xout)                       |

| 4       | I/O   | P2[3]                   | Digital I/O, crystal in (Xin)                         |

| 5       | I/O   | P2[1]                   | Digital I/O                                           |

| 6       | I/O   | P4[3]                   | Digital I/O                                           |

| 7       | I/O   | P4[1]                   | Digital I/O                                           |

| 8       | I/O   | P3[7]                   | Digital I/O                                           |

| 9       | I/O   | P3[5]                   | Digital I/O                                           |

| 10      | I/O   | P3[3]                   | Digital I/O                                           |

| 11      | I/O   | P3[1]                   | Digital I/O                                           |

| 12      | I/OHR | P1[7]                   | Digital I/O, I <sup>2</sup> C SCL, SPI SS             |

| 13      | I/OHR | P1[5]                   | Digital I/O, I <sup>2</sup> C SDA, SPI MISO           |

| 14      | NC    | NC                      | No connection                                         |

| 15      | NC    | NC                      | No connection                                         |

| 16      | I/OHR | P1[3]                   | Digital I/O, SPI CLK                                  |

| 17      | I/OHR | P1[1] <sup>[5, 6]</sup> | Digital I/O, ISSP CLK, I <sup>2</sup> C SCL, SPI MOSI |

| 18      | Power | V <sub>SS</sub>         | Supply ground                                         |

| 19      | I/O   | D+                      | USB                                                   |

| 20      | I/O   | D-                      | USB                                                   |

| 21      | Power | V <sub>DD</sub>         | Supply voltage                                        |

| 22      | I/OHR | P1[0] <sup>[5, 6]</sup> | Digital I/O, ISSP DATA, I <sup>2</sup> C SDA, SPI CLK |

| 23      | I/OHR | P1[2]                   | Digital I/O                                           |

#### Notes

During power up or reset event, device P1[0] and P1[1] may disturb the I<sup>2</sup>C bus. Use alternate pins if issues are encountered.

These are the in-system serial programming (ISSP) pins that are not High Z at power on reset (POR).

# **Register Reference**

The section discusses the registers of the enCoRe V device. It lists all the registers in mapping tables, in address order.

# **Register Conventions**

The register conventions specific to this section are listed in the following table.

#### Table 1. Register Conventions

| Convention | Description                |

|------------|----------------------------|

| R          | Read register or bits      |

| W          | Write register or bits     |

| L          | Logical register or bits   |

| С          | Clearable register or bits |

| #          | Access is bit specific     |

# **Register Mapping Tables**

The enCoRe V device has a total register address space of 512 bytes. The register space is also referred to as I/O space and is broken into two parts: Bank 0 (user space) and Bank 1 (configuration space). The XIO bit in the Flag register (CPU\_F) determines which bank the user is currently in. When the XIO bit is set, the user is said to be in the "extended" address space or the "configuration" registers.

# Table 2. Register Map Bank 0 Table: User Space

| Name                   | Addr (0, Hex)       |         |                    | Addr (0, Hex)   | A           | Nomo                   | Addr (0, Hex) | A        | Name      | Addr (0, Hex) | Access |

|------------------------|---------------------|---------|--------------------|-----------------|-------------|------------------------|---------------|----------|-----------|---------------|--------|

| PRTODR                 | аааг (0, нех)<br>00 | RW      | Name<br>EP1 CNT0   | 40              | Access<br># | Name                   | 80            | Access   | Name      | C0            | Access |

| PRTOIE                 | 01                  | RW      | EP1 CNT1           | 40              | RW          |                        | 81            |          |           | C1            |        |

|                        | 02                  |         | EP2 CNT0           | 42              | #           |                        | 82            |          |           | C2            |        |

|                        | 03                  |         | EP2 CNT1           | 43              | RW          |                        | 83            |          |           | C3            |        |

| PRT1DR                 | 04                  | RW      | EP3_CNT0           | 44              | #           |                        | 84            |          |           | C4            |        |

| PRT1IE                 | 05                  | RW      | EP3_CNT1           | 45              | RW          |                        | 85            |          |           | C5            |        |

|                        | 06                  |         | EP4_CNT0           | 46              | #           |                        | 86            |          |           | C6            |        |

|                        | 07                  |         | EP4_CNT1           | 47              | RW          |                        | 87            |          |           | C7            |        |

| PRT2DR                 | 08                  | RW      | EP5_CNT0           | 48              | #           |                        | 88            |          | I2C_XCFG  | C8            | RW     |

| PRT2IE                 | 09                  | RW      | EP5_CNT1           | 49              | RW          |                        | 89            |          | I2C_XSTAT | C9            | R      |

|                        | 0A                  |         | EP6_CNT0           | 4A              | #           |                        | 8A            |          | I2C_ADDR  | CA            | RW     |

|                        | 0B                  |         | EP6_CNT1           | 4B              | RW          |                        | 8B            |          | I2C_BP    | CB            | R      |

| PRT3DR                 | 0C                  | RW      | EP7_CNT0           | 4C              | #           |                        | 8C            |          | I2C_CP    | CC            | R      |

| PRT3IE                 | 0D                  | RW      | EP7_CNT1           | 4D              | RW          |                        | 8D            |          | CPU_BP    | CD            | RW     |

|                        | 0E                  |         | EP8_CNT0           | 4E              | #           |                        | 8E            |          | CPU_CP    | CE            | R      |

| -                      | 0F                  |         | EP8_CNT1           | 4F              | RW          |                        | 8F            |          | I2C_BUF   | CF            | RW     |

| PRT4DR                 | 10                  | RW      |                    | 50              |             |                        | 90            |          | CUR_PP    | D0            | RW     |

| PRT4IE                 | 11                  | RW      |                    | 51              |             |                        | 91            |          | STK_PP    | D1            | RW     |

|                        | 12                  |         |                    | 52              |             |                        | 92            |          |           | D2            |        |

|                        | 13                  |         |                    | 53              |             |                        | 93            |          | IDX_PP    | D3            | RW     |

|                        | 14                  |         |                    | 54              |             |                        | 94            |          | MVR_PP    | D4            | RW     |

|                        | 15                  |         |                    | 55              |             |                        | 95            |          | MVW_PP    | D5            | RW     |

|                        | 16                  |         |                    | 56              |             |                        | 96            |          | I2C_CFG   | D6            | RW     |

|                        | 17                  |         |                    | 57              | 514/        |                        | 97            |          | I2C_SCR   | D7            | #      |

|                        | 18                  |         | PMA0_DR            | 58              | RW          |                        | 98            | -        | I2C_DR    | D8            | RW     |

|                        | 19<br>1A            |         | PMA1_DR<br>PMA2 DR | 59<br>5A        | RW<br>RW    |                        | 99<br>9A      |          | INT CLR0  | D9<br>DA      | RW     |

|                        | 1A<br>1B            |         | PMA2_DR<br>PMA3_DR | 5A<br>5B        | RW          |                        | 9A<br>9B      |          | INT_CLR0  | DA            | RW     |

|                        | 1D<br>1C            |         | PMA3_DR<br>PMA4_DR | 5D<br>5C        | RW          |                        | 9D<br>9C      |          | INT_CLR1  | DB            | RW     |

|                        | 10<br>1D            |         | PMA4_DR<br>PMA5_DR | 5D              | RW          |                        | 90<br>9D      |          |           | DD            | INVV   |

|                        | 1E                  |         | PMA6 DR            | 5E              | RW          |                        | 9E            |          | INT MSK2  | DE            | RW     |

|                        | 1F                  |         | PMA7 DR            | 5F              | RW          |                        | 9F            |          | INT MSK1  | DF            | RW     |

|                        | 20                  |         |                    | 60              |             |                        | A0            |          | INT_MSK0  | E0            | RW     |

|                        | 21                  |         |                    | 61              |             |                        | A1            |          | INT_SW_EN | E1            | RW     |

|                        | 22                  |         |                    | 62              |             |                        | A2            |          | INT VC    | E2            | RC     |

|                        | 23                  |         |                    | 63              |             |                        | A3            |          | RES_WDT   | E3            | W      |

|                        | 24                  |         | PMA8 DR            | 64              | RW          |                        | A4            |          | -         | E4            |        |

|                        | 25                  |         | PMA9_DR            | 65              | RW          |                        | A5            |          |           | E5            |        |

|                        | 26                  |         | PMA10_DR           | 66              | RW          |                        | A6            |          |           | E6            |        |

|                        | 27                  |         | PMA11_DR           | 67              | RW          |                        | A7            |          |           | E7            |        |

|                        | 28                  |         | PMA12_DR           | 68              | RW          |                        | A8            |          |           | E8            |        |

| SPI_TXR                | 29                  | W       | PMA13_DR           | 69              | RW          |                        | A9            |          |           | E9            |        |

| SPI_RXR                | 2A                  | R       | PMA14_DR           | 6A              | RW          |                        | AA            |          |           | EA            |        |

| SPI_CR                 | 2B                  | #       | PMA15_DR           | 6B              | RW          |                        | AB            |          |           | EB            |        |

|                        | 2C                  |         | TMP_DR0            | 6C              | RW          |                        | AC            |          |           | EC            |        |

|                        | 2D                  |         | TMP_DR1            | 6D              | RW          |                        | AD            |          |           | ED            |        |

| -                      | 2E                  |         | TMP_DR2            | 6E              | RW          |                        | AE            |          |           | EE            |        |

|                        | 2F                  |         | TMP_DR3            | 6F              | RW          |                        | AF            |          |           | EF            |        |

|                        | 30                  |         |                    | 70              |             | PT0_CFG                | B0            | RW       |           | F0            |        |

| USB_SOF0               | 31                  | R       |                    | 71              |             | PT0_DATA1              | B1            | RW       |           | F1            |        |

| USB_SOF1               | 32                  | R       |                    | 72              |             | PT0_DATA0              | B2            | RW       |           | F2            |        |

| USB_CR0                | 33                  | RW      |                    | 73              |             | PT1_CFG<br>PT1_DATA1   | B3            | RW       |           | F3            |        |

| USBIO_CR0<br>USBIO_CR1 | 34                  | #       |                    | 74<br>75        |             | PT1_DATA1<br>PT1_DATA0 | B4            | RW       |           | F4<br>F5      |        |

| EP0 CR                 | 35<br>36            | #       |                    | 75              |             | PT1_DATA0<br>PT2_CFG   | B5<br>B6      | RW<br>RW |           | F5<br>F6      |        |

| EP0_CR<br>EP0_CNT0     | 30                  | #       |                    | 76              |             | PT2_CFG<br>PT2_DATA1   | во<br>В7      | RW       | CPU F     | F6<br>F7      | RL     |

| EP0_CNT0<br>EP0_DR0    | 38                  | #<br>RW |                    | 78              |             | PT2_DATA1<br>PT2_DATA0 | B7<br>B8      | RW       |           | F7<br>F8      | πL     |

| EP0_DR0                | 39                  | RW      |                    | 78              |             |                        | B0<br>B9      | 1.17     |           | F0<br>F9      |        |

| EP0_DR1<br>EP0_DR2     | 39<br>3A            | RW      |                    | 79<br>7A        |             |                        | BA            |          |           | F9<br>FA      |        |

| EP0_DR2<br>EP0_DR3     | 3A<br>3B            | RW      |                    | 7A<br>7B        |             |                        | BB            |          |           | FA            |        |

| EP0_DR3                | 3D<br>3C            | RW      |                    | 7B<br>7C        |             |                        | BC            |          |           | FC            |        |

| EP0 DR5                | 3D                  | RW      |                    | 70<br>7D        |             |                        | BD            |          |           | FD            |        |

| EP0_DR6                | 3E                  | RW      |                    | 76<br>7E        |             |                        | BE            |          | CPU SCR1  | FE            | #      |

| EP0 DR7                | 3F                  | RW      |                    | 7E<br>7F        |             |                        | BF            |          | CPU SCR0  | FF            | #      |

|                        | e reserved; do i    |         | hoso fields        | # Access is bit | specific    |                        |               |          |           |               |        |

# **DC Electrical Characteristics**

#### DC Chip Level Specifications

Table 6 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 6. DC Chip Level Specifications

| Symbol              | Description                                    | Conditions                                                                                                                            | Min  | Тур | Max  | Units |

|---------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>DD</sub>     | Operating voltage <sup>[7, 9]</sup>            | No USB activity.                                                                                                                      | 3.0  | _   | 5.5  | V     |

| I <sub>DD24,3</sub> | Supply current, CPU = 24 MHz                   | Conditions are $V_{DD}$ = 3.0 V, $T_A$ = 25 °C,<br>CPU = 24 MHz,<br>No USB/I <sup>2</sup> C/SPI.                                      | -    | 2.9 | 4.0  | mA    |

| I <sub>DD12,3</sub> | Supply current, CPU = 12 MHz                   | Conditions are $V_{DD}$ = 3.0 V, $T_A$ = 25 °C,<br>CPU = 12 MHz,<br>No USB/I <sup>2</sup> C/SPI.                                      | -    | 1.7 | 2.6  | mA    |

| I <sub>DD6,3</sub>  | Supply current, CPU = 6 MHz                    | Conditions are $V_{DD}$ = 3.0 V, $T_A$ = 25 °C,<br>CPU = 6 MHz,<br>No USB/I <sup>2</sup> C/SPI.                                       | -    | 1.2 | 1.8  | mA    |

| I <sub>SB1,3</sub>  | Standby current with POR, LVD, and sleep timer | $V_{DD}$ = 3.0 V, T <sub>A</sub> = 25 °C, I/O regulator turned off.                                                                   | -    | 1.1 | 1.5  | μA    |

| I <sub>SB0,3</sub>  | Deep sleep current                             | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C, I/O regulator<br>turned off.                                                         | -    | 0.1 | -    | μA    |

| V <sub>DDUSB</sub>  | Operating voltage                              | USB activity, USB regulator enabled                                                                                                   | 4.35 | -   | 5.25 | V     |

| I <sub>DD24,5</sub> | Supply current, CPU = 24 MHz                   | Conditions are V <sub>DD</sub> = 5.0 V, T <sub>A</sub> = 25 °C,<br>CPU = 24 MHz, IMO = 24 MHz<br>USB Active, No I <sup>2</sup> C/SPI. | -    | 7.1 | -    | mA    |

| I <sub>DD12,5</sub> | Supply current, CPU = 12 MHz                   | Conditions are V <sub>DD</sub> = 5.0 V, T <sub>A</sub> = 25 °C,<br>CPU = 12 MHz, IMO = 24 MHz<br>USB Active, No I <sup>2</sup> C/SPI. | -    | 6.2 | _    | mA    |

| I <sub>DD6,5</sub>  | Supply current, CPU = 6 MHz                    | Conditions are V <sub>DD</sub> = 5.0 V, T <sub>A</sub> = 25 °C,<br>CPU = 6 MHz, IMO = 24 MHz<br>USB Active, No I <sup>2</sup> C/SPI   | -    | 5.8 | -    | mA    |

| I <sub>SB1,5</sub>  | Standby current with POR, LVD, and sleep timer | $V_{DD}$ = 5.0 V, T <sub>A</sub> = 25 °C, I/O regulator turned off.                                                                   | _    | 1.1 | -    | μA    |

| I <sub>SB0,5</sub>  | Deep sleep current                             | $V_{DD}$ = 5.0 V, T <sub>A</sub> = 25 °C, I/O regulator turned off.                                                                   | -    | 0.1 | -    | μA    |

| V <sub>DDUSB</sub>  | Operating voltage                              | USB activity, USB regulator bypassed                                                                                                  | 3.15 | 3.3 | 3.60 | V     |

Notes

<sup>10.</sup> Higher storage temperatures reduce data retention time. Recommended storage temperature is +25 °C ± 25 °C. Extended duration storage temperatures above 85 °C degrade reliability.

<sup>11.</sup> The temperature rise from ambient to junction is package specific. See Package Handling on page 31. The user must limit the power consumption to comply with this requirement.

## Table 7. DC Characteristics – USB Interface

| Symbol | Description                          | Conditions                  | Min   | Тур  | Max   | Units |

|--------|--------------------------------------|-----------------------------|-------|------|-------|-------|

| Rusbi  | USB D+ pull-up resistance            | With idle bus               | 0.900 | -    | 1.575 | kΩ    |

| Rusba  | USB D+ pull-up resistance            | While receiving traffic     | 1.425 | -    | 3.090 | kΩ    |

| Vohusb | Static output high                   |                             | 2.8   | -    | 3.6   | V     |

| Volusb | Static output low                    |                             | -     | -    | 0.3   | V     |

| Vdi    | Differential input sensitivity       |                             | 0.2   | -    | -     | V     |

| Vcm    | Differential input common mode range |                             | 0.8   | -    | 2.5   | V     |

| Vse    | Single-ended receiver threshold      |                             | 0.8   | -    | 2.0   | V     |

| Cin    | Transceiver capacitance              |                             |       | -    | 50    | pF    |

| lio    | High Z state data Line Leakage       | On D+ or D– line            | -10   | -    | +10   | μA    |

| Rps2   | PS/2 Pull Up Resistance              |                             | 3     | 5    | 7     | kΩ    |

| Rext   | External USB Series Resistor         | In series with each USB pin | 21.78 | 22.0 | 22.22 | Ω     |

### ADC Electrical Specifications

# Table 8. ADC User Module Electrical Specifications

| Symbol                 | Description                  | Conditions                                                                                     | Min                      | Тур                      | Max                      | Units |

|------------------------|------------------------------|------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-------|

| Input                  |                              | I                                                                                              |                          |                          |                          |       |

| V <sub>IN</sub>        | Input voltage range          |                                                                                                | 0                        | -                        | VREFADC                  | V     |

| C <sub>IIN</sub>       | Input capacitance            |                                                                                                | _                        | -                        | 5                        | pF    |

| R <sub>IN</sub>        | Input resistance             | Equivalent switched cap input resistance for 8-, 9-, or 10-bit resolution                      | 1/(500fF*<br>Data Clock) | 1/(400fF*<br>Data Clock) | 1/(300fF*<br>Data Clock) | Ω     |

| Reference              |                              | I                                                                                              | 1                        |                          | I                        |       |

| V <sub>REFADC</sub>    | ADC reference voltage        |                                                                                                | 1.14                     | -                        | 1.26                     | V     |

| <b>Conversion Rate</b> | )                            | I                                                                                              | 1                        |                          | I                        |       |

| F <sub>CLK</sub>       | Data clock                   | Source is chip's internal main<br>oscillator. See AC Chip-Level<br>Specifications for accuracy | 2.25                     | _                        | 6                        | MHz   |

| S8                     | 8-bit sample rate            | Data Clock set to 6 MHz.<br>Sample Rate = 0.001/<br>(2^Resolution/Data Clock)                  | _                        | 23.4375                  | _                        | ksps  |

| S10                    | 10-bit sample rate           | Data Clock set to 6 MHz.<br>Sample Rate = 0.001/<br>(2^Resolution/Data Clock)                  | _                        | 5.859                    | _                        | ksps  |

| DC Accuracy            |                              | I                                                                                              | 1                        |                          | I                        |       |

| RES                    | Resolution                   | Can be set to 8-, 9-, or 10-bit                                                                | 8                        | _                        | 10                       | bits  |

| DNL                    | Differential nonlinearity    |                                                                                                | -1                       | _                        | +2                       | LSB   |

| INL                    | Integral nonlinearity        |                                                                                                | -2                       | -                        | +2                       | LSB   |

| E <sub>Offset</sub>    | Offset error                 | 8-bit resolution                                                                               | 0                        | 3.2                      | 19.2                     | LSB   |

|                        |                              | 10-bit resolution                                                                              | 0                        | 12.8                     | 76.8                     | LSB   |

| E <sub>gain</sub>      | Gain error                   | For any resolution                                                                             | -5                       | -                        | +5                       | %FSR  |

| Power                  |                              |                                                                                                |                          |                          |                          |       |

| I <sub>ADC</sub>       | Operating current            |                                                                                                | -                        | 2.1                      | 2.6                      | mA    |

| PSRR                   | Power supply rejection ratio | PSRR (V <sub>DD</sub> > 3.0 V)                                                                 | -                        | 24                       | -                        | dB    |

|                        |                              | PSRR (V <sub>DD</sub> < 3.0 V)                                                                 | _                        | 30                       | -                        | dB    |

## DC General Purpose I/O Specifications

Table 9 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and package specific temperature range. Typical parameters apply to 5 V and 3.3 V at 25 °C. These are for design guidance only.

| Table 9. | 3.0 V and 5.5 | <b>V DC GPIO</b> | Specifications |

|----------|---------------|------------------|----------------|

|----------|---------------|------------------|----------------|

| Symbol            | Description                                                                  | Conditions                                                                                                                                                                                             | Min                   | Тур   | Max  | Units |

|-------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|-------|

| R <sub>PU</sub>   | Pull-up resistor                                                             |                                                                                                                                                                                                        | 4                     | 5.6   | 8    | kΩ    |

| V <sub>OH1</sub>  | High output voltage<br>Port 2 or 3 pins                                      | $I_{OH} \le 10 \ \mu$ A, maximum of 10 mA source current in all I/Os.                                                                                                                                  | V <sub>DD</sub> -0.2  | I     | -    | V     |

| V <sub>OH2</sub>  | High output voltage<br>Port 2 or 3 Pins                                      | I <sub>OH</sub> = 1 mA, maximum of 20 mA source current in all I/Os.                                                                                                                                   | V <sub>DD</sub> – 0.9 | _     | -    | V     |

| V <sub>OH3</sub>  | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>disabled       | $I_{OH}$ < 10 µA, maximum of 10 mA source current in all I/Os.                                                                                                                                         | V <sub>DD</sub> – 0.2 | _     | -    | V     |

| V <sub>OH4</sub>  | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>disabled       | I <sub>OH</sub> = 5 mA, maximum of 20 mA source current in all I/Os.                                                                                                                                   | V <sub>DD</sub> – 0.9 | _     | -    | V     |

| V <sub>OH5</sub>  | High output voltage<br>Port 1 pins with LDO regulator enabled<br>for 3 V Out | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 3.1 V, maximum of 4 I/Os all sourcing 5 mA                                                                                                                    | 2.85                  | 3.00  | 3.3  | V     |

| V <sub>OH6</sub>  | High output voltage<br>Port 1 pins with LDO regulator enabled<br>for 3 V out | $I_{OH}$ = 5 mA, $V_{DD}$ > 3.1 V, maximum of<br>20 mA source current in all I/Os                                                                                                                      | 2.20                  | _     | -    | V     |

| V <sub>OH7</sub>  | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V<br>out         | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 3.0 V, maximum of 20 mA source current in all I/Os                                                                                                            | 2.35                  | 2.50  | 2.75 | V     |

| V <sub>OH8</sub>  | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V<br>out         | I <sub>OH</sub> = 2 mA, V <sub>DD</sub> > 3.0 V, maximum of<br>20 mA source current in all I/Os                                                                                                        | 1.90                  | _     | -    | V     |

| V <sub>OH9</sub>  | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V<br>out         | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 3.0 V, maximum of 20 mA source current in all I/Os                                                                                                            | 1.60                  | 1.80  | 2.1  | V     |

| V <sub>OH10</sub> | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V<br>out         | I <sub>OH</sub> = 1 mA, V <sub>DD</sub> > 3.0 V, maximum of<br>20 mA source current in all I/Os                                                                                                        | 1.20                  | _     | _    | V     |

| V <sub>OL</sub>   | Low output voltage                                                           | $I_{OL}$ = 25 mA, $V_{DD}$ > 3.3 V, maximum of<br>60 mA sink current on even port pins<br>(for example, P0[2] and P1[4]) and 60<br>mA sink current on odd port pins (for<br>example, P0[3] and P1[5]). | -                     | -     | 0.75 | V     |

| V <sub>IL</sub>   | Input low voltage                                                            |                                                                                                                                                                                                        | -                     | -     | 0.8  | V     |

| V <sub>IH</sub>   | Input high voltage                                                           |                                                                                                                                                                                                        | 2.0                   | _     | -    | V     |

| V <sub>H</sub>    | Input hysteresis voltage                                                     |                                                                                                                                                                                                        | -                     | 80    | _    | mV    |

| I <sub>IL</sub>   | Input leakage (absolute value)                                               |                                                                                                                                                                                                        | -                     | 0.001 | 1    | μA    |

| C <sub>PIN</sub>  | Pin capacitance                                                              | Package and pin dependent.<br>Temp = 25 °C.                                                                                                                                                            | 0.5                   | 1.7   | 5    | pF    |

#### DC POR and LVD Specifications

Table 10 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 10. DC POR and LVD Specifications

| Symbol                                                               | Description                                                                                                                                                                                                                        | Conditions | Min                                   | Тур                                    | Max                                    | Units |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------|----------------------------------------|----------------------------------------|-------|

| V <sub>PPOR</sub>                                                    | V <sub>DD</sub> value for PPOR trip <sup>[12]</sup><br>PORLEV[1:0] = 10b                                                                                                                                                           |            | _                                     | 2.82                                   | 2.95                                   | V     |

| VLVD0<br>VLVD1<br>VLVD2<br>VLVD3<br>VLVD4<br>VLVD5<br>VLVD6<br>VLVD7 | $\begin{array}{l} V_{DD} \text{ value for LVD trip} \\ VM[2:0] = 000b \\ VM[2:0] = 001b \\ VM[2:0] = 010b \\ VM[2:0] = 011b \\ VM[2:0] = 100b \\ VM[2:0] = 101b \\ VM[2:0] = 101b \\ VM[2:0] = 110b \\ VM[2:0] = 111b \end{array}$ |            | -<br>2.85<br>2.95<br>3.06<br><br>4.62 | -<br>2.92<br>3.02<br>3.13<br>-<br>4.73 | -<br>2.99<br>3.09<br>3.20<br>-<br>4.83 |       |

#### DC Programming Specifications

Table 11 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

## Table 11. DC Programming Specifications

| Symbol                | Description                                                                                     | Conditions                                                        | Min                         | Тур | Max                         | Units  |

|-----------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------|-----|-----------------------------|--------|

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operations                                                       |                                                                   | 1.71                        | -   | 5.25                        | V      |

| I <sub>DDP</sub>      | Supply current during programming<br>or verify                                                  |                                                                   | -                           | 5   | 25                          | mA     |

| V <sub>ILP</sub>      | Input low voltage during<br>programming or verify                                               | See appropriate DC<br>General Purpose I/O<br>Specifications table | _                           | -   | V <sub>IL</sub>             | V      |

| V <sub>IHP</sub>      | Input high voltage during<br>programming or verify                                              |                                                                   | 1.71                        | -   | V <sub>DDIWRITE</sub> + 0.3 | V      |

| I <sub>ILP</sub>      | Input current when applying Vilp to P1[0] or P1[1] during programming or verify <sup>[13]</sup> |                                                                   | -                           | -   | 0.2                         | mA     |

| I <sub>IHP</sub>      | Input current when applying Vihp to P1[0] or P1[1] during programming or verify <sup>[13]</sup> |                                                                   | -                           | -   | 1.5                         | mA     |

| V <sub>OLP</sub>      | Output low voltage during<br>programming or verify                                              |                                                                   | -                           | -   | V <sub>SS</sub> + 0.75      | V      |

| V <sub>OHP</sub>      | Output high voltage during<br>programming or verify                                             |                                                                   | V <sub>DDIWRITE</sub> – 0.9 | -   | V <sub>DDIWRITE</sub>       | V      |

| Flash <sub>ENPB</sub> | Flash write endurance <sup>[14]</sup>                                                           |                                                                   | 50,000                      | -   | -                           | Cycles |

| Flash <sub>DR</sub>   | Flash data retention <sup>[15]</sup>                                                            |                                                                   | 10                          | 20  | -                           | Years  |

#### Notes

- 12. Always greater than 50 mV above  $V_{PPOR}$  (PORLEV = 10) for falling supply.

- 13. Driving internal pull down resistor.

- 14. Erase/write cycles per block.

- 15. Following maximum Flash write cycles at Tamb = 55 °C and Tj = 70 °C.

# **AC Electrical Characteristics**

#### AC Chip Level Specifications

The following tables list guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 12. AC Chip Level Specifications

| Symbol                 | Description                                                                  | Conditions                    | Min  | Тур | Max  | Units |

|------------------------|------------------------------------------------------------------------------|-------------------------------|------|-----|------|-------|

| F <sub>CPU</sub>       | Processing frequency <sup>[16]</sup>                                         |                               | 5.7  | -   | 25.2 | MHz   |

| F <sub>32K1</sub>      | Internal low-speed oscillator (ILO) frequency                                | Trimmed <sup>[17]</sup>       | 19   | 32  | 50   | kHz   |

| F <sub>32К U</sub>     | ILO untrimmed frequency)                                                     |                               | 13   | 32  | 82   | kHz   |

| F <sub>32K2</sub>      | ILO frequency                                                                | Untrimmed                     | 13   | 32  | 82   | kHz   |

| F <sub>IMO24</sub>     | Internal main oscillator (IMO) stability for 24 MHz $\pm$ 5% <sup>(12)</sup> |                               | 22.8 | 24  | 25.2 | MHz   |

| F <sub>IMO12</sub>     | IMO stability for 12 MHz <sup>[17]</sup>                                     |                               | 11.4 | 12  | 12.6 | MHz   |

| F <sub>IMO6</sub>      | IMO stability for 6 MHz <sup>[17]</sup>                                      |                               | 5.7  | 6.0 | 6.3  | MHz   |

| DC <sub>IMO</sub>      | Duty cycle of IMO                                                            |                               | 40   | 50  | 60   | %     |

| DC <sub>ILO</sub>      | ILO duty cycle                                                               |                               | 40   | 50  | 60   | %     |

| SR <sub>POWER_UP</sub> | Power supply slew rate                                                       |                               | _    | -   | 250  | V/ms  |

| T <sub>XRST</sub>      | External reset pulse width at power-up                                       | After supply voltage is valid | 1    | -   | -    | ms    |

| T <sub>XRST2</sub>     | External reset pulse width after power-up <sup>[18]</sup>                    | Applies after part has booted | 10   | -   | _    | μS    |

#### Table 13. AC Characteristics – USB Data Timings

| Symbol | Description                                          | Conditions         | Min   | Тур | Max   | Units |

|--------|------------------------------------------------------|--------------------|-------|-----|-------|-------|

| Tdrate | Full speed data rate                                 | Average bit rate   | 11.97 | 12  | 12.03 | MHz   |

| Tdjr1  | Receiver data jitter tolerance                       | To next transition | -18.5 | _   | 18.5  | ns    |

| Tdjr2  | Receiver data jitter tolerance                       | To pair transition | -9    | -   | 9     | ns    |

| Tudj1  | Driver differential jitter                           | To next transition | -3.5  | _   | 3.5   | ns    |

| Tudj2  | Driver differential jitter                           | To pair transition | -4.0  | -   | 4.0   | ns    |

| Tfdeop | Source jitter for differential transition            | To SE0 transition  | -2    | _   | 5     | ns    |

| Tfeopt | Source SE0 interval of EOP                           |                    | 160   | -   | 175   | ns    |

| Tfeopr | Receiver SE0 interval of EOP                         |                    | 82    | -   | -     | ns    |

| Tfst   | Width of SE0 interval during differential transition |                    | -     | -   | 14    | ns    |

# Table 14. AC Characteristics – USB Driver

| Symbol             | Description                     | Conditions | Min   | Тур | Max   | Units |

|--------------------|---------------------------------|------------|-------|-----|-------|-------|

| Tr                 | Transition rise time            | 50 pF      | 4     | -   | 20    | ns    |

| Tf                 | Transition fall time            | 50 pF      | 4     | -   | 20    | ns    |

| TR <sup>[19]</sup> | Rise/fall time matching         |            | 90.00 | -   | 111.1 | %     |

| Vcrs               | Output signal crossover voltage |            | 1.3   | -   | 2.0   | V     |

Notes

16. V<sub>DD</sub> = 3.0 V and T<sub>J</sub> = 85 °C, CPU speed.

17. Trimmed for 3.3 V operation using factory trim values.

18. The minimum required XRES pulse length is longer when programming the device (see Table 17 on page 24).

19. Errata: Rising to falling rate matching of the USB D+ and D- lines has a corner case issue when operating voltage is below 3.3 V. Refer to "Errata" on page 35 for more details.

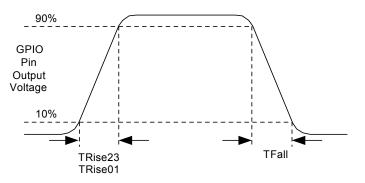

# AC General Purpose I/O Specifications

Table 15 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

| Symbol            | Description                          | Conditions                                   | Min | Тур | Max | Units |

|-------------------|--------------------------------------|----------------------------------------------|-----|-----|-----|-------|

| F <sub>GPIO</sub> | GPIO operating frequency             | Normal strong mode,<br>Ports 0, 1            | -   | -   | 12  | MHz   |

| TRise23           | Rise time, strong mode<br>Ports 2, 3 | V <sub>DD</sub> = 3.0 to 3.6 V,<br>10% - 90% | 15  | -   | 80  | ns    |

| TRise01           | Rise time, strong mode<br>Ports 0, 1 | V <sub>DD</sub> = 3.0 to 3.6 V,<br>10% - 90% | 10  | -   | 50  | ns    |

| TFall             | Fall time, strong mode<br>All Ports  | V <sub>DD</sub> = 3.0 to 3.6 V,<br>10% - 90% | 10  | -   | 50  | ns    |

#### Table 15. AC GPIO Specifications

Figure 11. GPIO Timing Diagram

## AC External Clock Specifications

Table 16 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 16. AC External Clock Specifications

| Symbol  | Description            | Conditions | Min   | Тур | Max  | Units |

|---------|------------------------|------------|-------|-----|------|-------|

| FOSCEXT | Frequency              |            | 0.750 | -   | 25.2 | MHz   |

| -       | High period            |            | 20.6  | -   | 5300 | ns    |

| -       | Low period             |            | 20.6  | -   | -    | ns    |

| _       | Power-up IMO to switch |            | 150   | _   | _    | μs    |

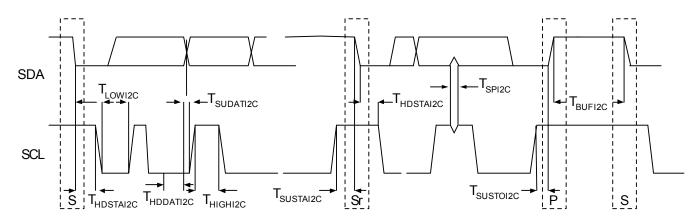

# AC I<sup>2</sup>C Specifications

Table 18 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

| Symbol                | ol Description –                                                                            |     | d Mode | Fast                | Mode | Units |

|-----------------------|---------------------------------------------------------------------------------------------|-----|--------|---------------------|------|-------|

| Symbol                |                                                                                             |     | Max    | Min                 | Max  | Units |

| F <sub>SCLI2C</sub>   | SCL clock frequency                                                                         | 0   | 100    | 0                   | 400  | kHz   |

| T <sub>HDSTAI2C</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated |     | -      | 0.6                 | -    | μS    |

| T <sub>LOWI2C</sub>   | LOW period of the SCL clock                                                                 | 4.7 | -      | 1.3                 | -    | μS    |

| T <sub>HIGHI2C</sub>  | HIGH period of the SCL clock                                                                | 4.0 | -      | 0.6                 | -    | μS    |

| T <sub>SUSTAI2C</sub> | Setup time for a repeated START condition                                                   | 4.7 | -      | 0.6                 | -    | μS    |

| T <sub>HDDATI2C</sub> | Data hold time                                                                              | 0   | -      | 0                   | -    | μS    |

| T <sub>SUDATI2C</sub> | Data setup time                                                                             | 250 | -      | 100 <sup>[20]</sup> | -    | ns    |

| T <sub>SUSTOI2C</sub> | Setup time for STOP condition                                                               | 4.0 | -      | 0.6                 | -    | μS    |

| T <sub>BUFI2C</sub>   | Bus free time between a STOP and START condition                                            |     | -      | 1.3                 | -    | μS    |

| T <sub>SPI2C</sub>    | Pulse width of spikes are suppressed by the input filter                                    | _   | -      | 0                   | 50   | ns    |

Figure 13. Definition of Timing for Fast/Standard Mode on the I<sup>2</sup>C Bus

<sup>20.</sup> A Fast mode I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but the requirement t<sub>SUDAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SUDAT</sub> = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

# Table 19. SPI Master AC Specifications

| Symbol               | Description             | Conditions | Min | Тур | Max | Units |

|----------------------|-------------------------|------------|-----|-----|-----|-------|

| F <sub>SCLK</sub>    | SCLK clock frequency    |            | -   | -   | 6   | MHz   |

| DC                   | SCLK duty cycle         |            | -   | 50  | -   | %     |

| T <sub>SETUP</sub>   | MISO to SCLK setup time |            | 60  | -   | -   | ns    |

| T <sub>HOLD</sub>    | SCLK to MISO hold time  |            | 40  | -   | -   | ns    |

| T <sub>OUT_VAL</sub> | SCLK to MOSI valid time |            | -   | -   | 40  | ns    |

| T <sub>OUT_H</sub>   | SCLK to MOSI hold time  |            | 40  | _   | _   | ns    |

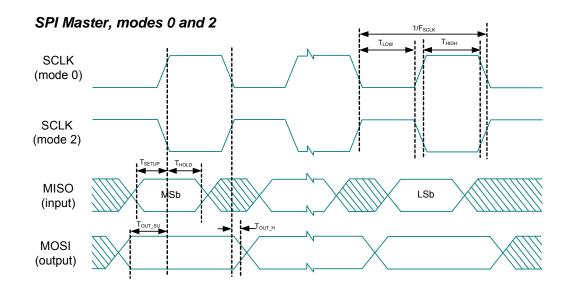

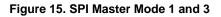

Figure 14. SPI Master Mode 0 and 2

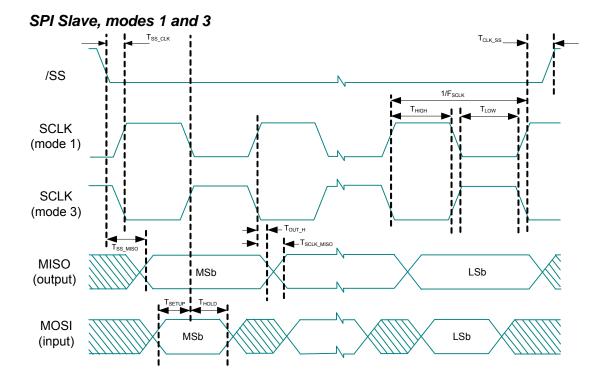

# Table 20. SPI Slave AC Specifications

| Symbol                 | Description                    | Conditions | Min                 | Тур | Max | Units |

|------------------------|--------------------------------|------------|---------------------|-----|-----|-------|

| F <sub>SCLK</sub>      | SCLK clock frequency           |            | 0.0469              | -   | 12  | MHz   |

| T <sub>LOW</sub>       | SCLK low time                  |            | 41.67               | -   | -   | ns    |

| T <sub>HIGH</sub>      | SCLK high time                 |            | 41.67               | -   | -   | ns    |

| T <sub>SETUP</sub>     | MOSI to SCLK setup time        |            | 30                  | -   | -   | ns    |

| T <sub>HOLD</sub>      | SCLK to MOSI hold time         |            | 50                  | -   | -   | ns    |

| T <sub>SS_MISO</sub>   | SS low to MISO valid           |            | -                   | -   | 153 | ns    |

| T <sub>SCLK_MISO</sub> | SCLK to MISO valid             |            | -                   | -   | 125 | ns    |

| T <sub>SS_HIGH</sub>   | SS high time                   |            | 50                  | -   | -   | ns    |

| T <sub>SS_CLK</sub>    | Time from SS low to first SCLK |            | 2/F <sub>SCLK</sub> | -   | -   | ns    |

| T <sub>CLK_SS</sub>    | Time from last SCLK to SS high |            | 2/F <sub>SCLK</sub> | -   | _   | ns    |

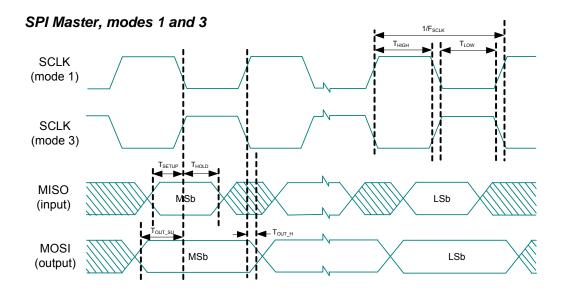

| Figure | 16. | SPI | Slave | Mode | 0 | and 2 |

|--------|-----|-----|-------|------|---|-------|

| Iguie  | 10. | 011 | Olave | Moue | v |       |

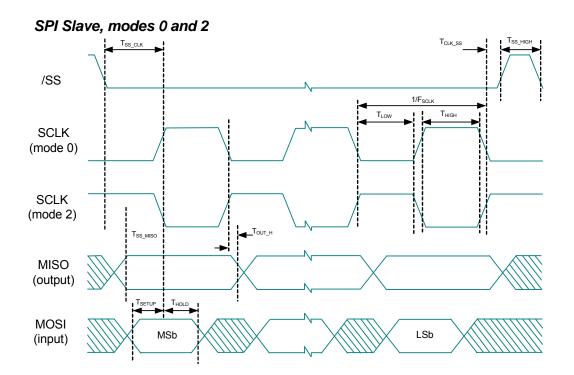

## Figure 17. SPI Slave Mode 1 and 3

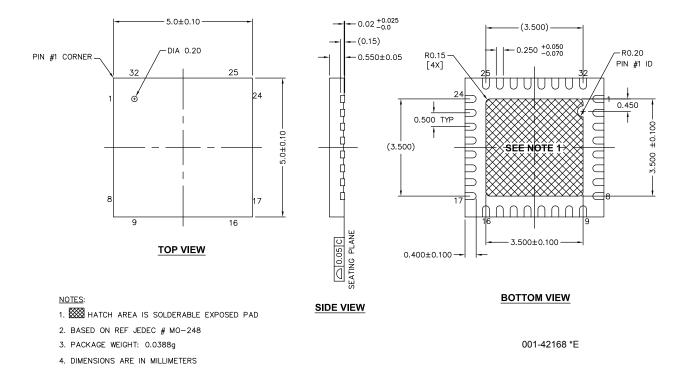

#### Figure 19. 32-pin QFN (5 × 5 × 0.55 mm) LQ32 3.5 × 3.5 E-Pad (Sawn) Package Outline, 001-42168

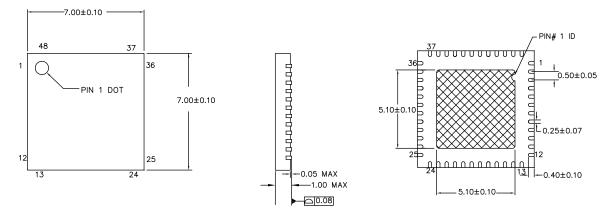

#### Figure 20. 48-pin QFN (7 × 7 × 1.00 mm) LT48A 5.1 × 5.1 E-Pad (Sawn) Package Outline, 001-13191

TOP VIEW

<u>SIDE VIEW</u>

BOTTOM VIEW

NOTES:

- 1. 🗱 HATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT:  $13 \pm 1$  mg

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-13191 \*H

# **Package Handling**

Some IC packages require baking before they are soldered onto a PCB to remove moisture that may have been absorbed after leaving the factory. A label on the package has details about the actual bake temperature and the minimum bake time to remove this moisture. The maximum bake time is the aggregate time that the parts exposed to the bake temperature. Exceeding this exposure may degrade device reliability.

#### Table 21. Package Handling

| Parameter | Description      | Minimum           | Typical | Maximum           | Unit  |

|-----------|------------------|-------------------|---------|-------------------|-------|

| TBAKETEMP | Bake temperature | -                 | 125     | See package label | °C    |

| TBAKETIME | Bake time        | See package label | -       | 72                | hours |

#### **Thermal Impedances**

#### Table 22. Thermal Impedances per Package

| Package                    | Typical θ <sub>JA</sub> <sup>[21]</sup> |

|----------------------------|-----------------------------------------|

| 16-pin QFN                 | 32.69 °C / W                            |

| 32-pin QFN <sup>[22]</sup> | 19.51 °C / W                            |

| 48-pin QFN <sup>[22]</sup> | 17.68 °C / W                            |

#### **Capacitance on Crystal Pins**

#### Table 23. Typical Package Capacitance on Crystal Pins

| Package    | Package Capacitance |

|------------|---------------------|

| 32-pin QFN | 3.2 pF              |

| 48-pin QFN | 3.3 pF              |

#### **Solder Reflow Peak Temperature**

Following is the minimum solder reflow peak temperature to achieve good solderability.

#### Table 24. Solder Reflow Peak Temperature

| Package    | Minimum Peak Temperature <sup>[23]</sup> | Maximum Peak Temperature |  |  |

|------------|------------------------------------------|--------------------------|--|--|

| 16-pin QFN | 240 °C                                   | 260 °C                   |  |  |

| 32-pin QFN | 240 °C                                   | 260 °C                   |  |  |

| 48-pin QFN | 240 °C                                   | 260 °C                   |  |  |

<sup>21.</sup>  $T_J = T_A + Power \times \theta_{JA}$ . 22. To achieve the thermal impedance specified for the package, solder the center thermal pad to the PCB ground plane.

<sup>23.</sup> Higher temperatures may be required based on the solder melting point. Typical temperatures for solder are 220 ± 5 °C with Sn-Pb or 245 ± 5 °C with Sn-Ag-Cu paste. Refer to the solder manufacturer specifications.

# Document History Page (continued)

| Rev. | ECN No. | Orig. of<br>Change     | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|---------|------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *F   | 2583853 | TYJ /<br>PYRS /<br>HMT | 10/10/08           | Converted from Preliminary to Final<br>Added operating voltage ranges with USB<br>ADC resolution changed from 10-bit to 8-bit<br>Rephrased battery monitoring clause in page 1 to include "with external<br>components"<br>Included ADC specifications table<br>Included Voh7, Voh8, Voh9, Voh10 specs<br>Flash data retention – condition added to Note [11]<br>Input leakage spec changed to 25 nA max<br>Under AC Char, Frequency accuracy of ILO corrected<br>GPIO rise time for ports 0,1 and ports 2,3 made common<br>AC Programming specifications updated<br>Included AC Programming cycle timing diagram<br>AC SPI specification updated<br>Spec change for 32-QFN package<br>Input Leakage Current maximum value changed to 1 μA<br>Updated V <sub>OHV</sub> parameter in Table 13<br>Updated thermal impedances for the packages<br>Update Development Tools, add Designing with PSoC Designer. Edit, fix link<br>and table format. Update TMs. |

| *G   | 2653717 | DVJA /<br>PYRS         | 02/04/09           | Updated Features, Functional Overview, Development Tools, and Designing<br>with PSoC Designer sections with edits.<br>Removed 'GUI - graphical user interface' from Document Conventions<br>acronym table.<br>Removed 'O - Only a read/write register or bits' in Table 4<br>Edited Table 8: removed 10-bit resolution information and corrected units<br>column.<br>Added package handling section<br>Added 8K part 'CY7C64343-32LQXC' to Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *H   | 2714694 | DVJA /<br>AESA         | 06/04/2009         | Updated Block Diagram.<br>Added Full Speed USB, 10-bit ADC, SPI, and I2C Slave sections.<br>ADC Resolution changed from 8-bit to 10-bit<br>Updated Table 9 DC Chip Level Specs<br>Updated Table10 DC Char - USB Interface<br>Updated Table 12 DC POR and LDV Specs<br>Changed operating temperature from Commercial to Industrial<br>Changed Temperature Range to Industrial: -40 to 85°C<br>Figure 9: Changed minimum CPU Frequency from 750 kHz to 5.7 MHz<br>Table 14: Removed "Maximum" from the F <sub>CPU</sub> description<br>Ordering Information: Replaced 'C' with 'I' in all part numbers to denote<br>Industrial Temp Range                                                                                                                                                                                                                                                                                                                    |

| *    | 2764460 | DVJA /<br>AESA         | 09/16/2009         | Changed Table 12: ADC Specs<br>Added $F_{32K2}$ (Untrimmed) spec to Table 16: AC Chip level Specs<br>Changed $T_{RAMP}$ spec to $SR_{POWER\_UP}$ in Table 16: AC Chip Level Specs<br>Added Table 27: Typical Package Capacitance on Crystal Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *J   | 2811903 | DVJA                   | 11/20/2009         | Added USB-IF TID number in Features on page 1. Added Note 5 on page 18 Changed $V_{IHP}$ in Table 12 on page 22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# Document History Page (continued)

|      | Document Title: CY7C6431x/CY7C6434x/CY7C6435x, enCoRe™ V Full Speed USB Controller<br>Document Number: 001-12394 |                    |                    |                                                                                                                                                                                                                                                                                                                                 |  |

|------|------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Rev. | ECN No.                                                                                                          | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                           |  |

| *S   | 4578605                                                                                                          | GINS               | 12/11/2014         | Updated Pin Information:<br>Updated 32-pin part pinout:<br>Updated Figure 7 (No change in figure, included CY7C64346 in figure caption).<br>Updated Package Diagrams:<br>spec 001-09116 – Changed revision from *I to *J.<br>Updated Ordering Information:<br>Updated Table 25:<br>Updated part numbers.                        |  |

| *Т   | 5548557                                                                                                          | ANKC               | 12/12/2016         | Updated Cypress Logo, Sales Page and Disclaimer.<br>Updated Figure 20 (spec 001-13191 *G to *H) in Package Diagrams.<br>Removed the following obsolete part numbers (Table 26) in Ordering<br>Information: CY7C64343-32LQXI, CY7C64343-32LQXIT,<br>CY7C64345-32LQXI, CY7C64345-32LQXIT, CY7C64356-48LTXI,<br>CY7C64356-48LTXIT. |  |