Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 24MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, SIO, SPI, UART/USART, USB                                        |

| Peripherals                | DMA, LVD, POR, WDT                                                                 |

| Number of I/O              | 48                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-LQFP                                                                            |

| Supplier Device Package    | 64-LQFP (10x10)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/toshiba-semiconductor-and-storage/tmpm066fwug |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 12.5 Each Operation Mode Description                      |     |

|-----------------------------------------------------------|-----|

| 12.5.1 16-bit Programmable Rectangular Pulse Output (PPG) |     |

| 12.5.1.1 PPG mode                                         |     |

| 12.5.1.2 Interlock PPG Mode                               |     |

| 12.5.1.3 Setting Range of Compare Register                |     |

| 12.5.2 Each Operation Mode and Interrupts                 | 241 |

# 13. Serial Channel with 4bytes FIFO (SIO/UART)

| 13.1 Overview                                              |     |

|------------------------------------------------------------|-----|

| 13.2 Configuration                                         | 244 |

| 13.3 Registers Description                                 |     |

| 13.3.1 Registers List                                      |     |

| 13.3.2 SCxEN (Enable Register)                             |     |

| 13.3.3 SCxBUF (Buffer Register)                            |     |

| 13.3.4 SCxCR (Control Register)                            |     |

| 13.3.5 SCxMOD0 (Mode Control Register 0)                   | 250 |

| 13.3.6 SCxMOD1 (Mode Control Register 1)                   |     |

| 13.3.7 SCxMOD2 (Mode Control Register 2)                   |     |

| 13.3.8 SCxBRCR (Baud Rate Generator Control Register)      |     |

| 13.3.9 SCxBRADD (Baud Rate Generator Control Register 2)   |     |

| 13.3.10 SCxFCNF (FIFO Configuration Register)              |     |

| 13.3.11 SCxRFC (Receive FIFO Configuration Register)       |     |

| 13.3.12 SCxTFC (Transmit FIFO Configuration Register)      |     |

| 13.3.13 SCxRST (Receive FIFO Status Register)              |     |

| 13.3.14 SCxTST (Transmit FIFO Status Register)             |     |

| 13.3.15 SCxDMA (DMA request enable register)               |     |

| 13.4 Operation in Each Mode                                |     |

| 13.5 Data Format                                           |     |

|                                                            |     |

| 13.5.1 Data Format List                                    |     |

| 13.5.2 Parity Control<br>13.5.2.1 Transmission             |     |

| 13.5.2.2 Reception                                         |     |

| 13.5.3 STOP Bit Length                                     | 265 |

| 13.6 Clock Control                                         |     |

|                                                            |     |

| 13.6.1 Prescaler<br>13.6.2 Serial Clock Generation Circuit |     |

| 13.6.2.1 Baud Rate Generator                               |     |

| 13.6.2.2 Clock Selection Circuit                           |     |

| 13.6.3 Transmit/Receive Buffer and FIFO                    |     |

| 13.6.3.1 Configuration                                     |     |

| 13.6.3.2 Transmit/Receive Buffer                           |     |

| 13.6.3.3 Initialize Transmit Buffer                        |     |

| 13.6.3.4 FIFO                                              |     |

| 13.7 Status Flag                                           |     |

| 13.8 Error Flag                                            |     |

| 13.8.1 OERR Flag                                           |     |

| 13.8.2 PERR Flag                                           |     |

| 13.8.3 FERR Flag                                           |     |

| 13.9 Receive                                               | 274 |

| 13.9.1 Receive Counter                                     |     |

| 13.9.2 Receive Control Unit                                |     |

| 13.9.2.1 I/O interface mode                                |     |

| 13.9.2.2 UART Mode                                         |     |

| 13.9.3 Receive Operation                                   |     |

| 13.9.3.1 Receive Buffer                                    |     |

| 13.9.3.2 Receive FIFO Operation                            |     |

| 13.9.3.3 I/O interface mode with clock output mode         |     |

| 13.9.3.4Read Received Data13.9.3.5Wake-up Function         |     |

| 13.9.3.5 Wake-up Function<br>13.9.3.6 Overrun Error        |     |

| 13.10 Transmit                                             | 770 |

|                                                            |     |

| 13.10.1 Transmit Counter                                   | 2/8 |

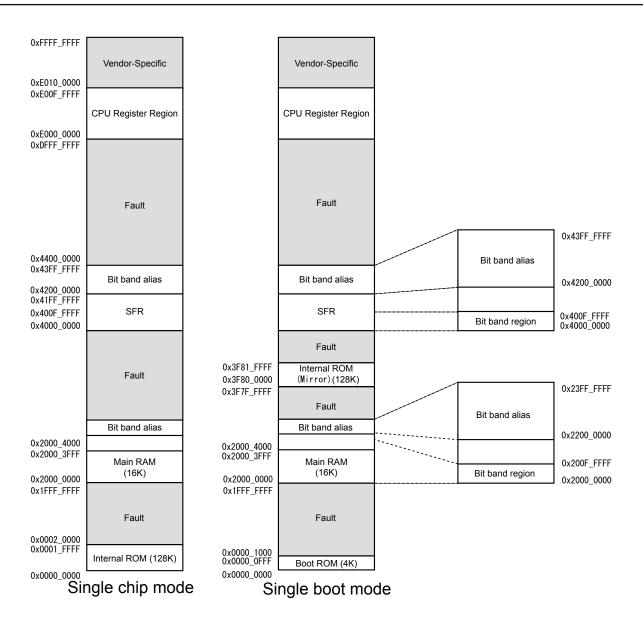

Figure 4-1 TMPM066/067/068 Memory Map

|                           | 31                       | 30                       | 29                       | 28                       | 27                       | 26                       | 25                       | 24                       |

|---------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| bit symbol                | SETENA<br>(Interrupt 31) | SETENA<br>(Interrupt 30) | SETENA<br>(Interrupt 29) | SETENA<br>(Interrupt 28) | SETENA<br>(Interrupt 27) | SETENA<br>(Interrupt 26) | SETENA<br>(Interrupt 25) | SETENA<br>(Interrupt 24) |

| After reset               | 0                        | 0                        | 0                        | 0                        | 0                        | 0                        | 0                        | 0                        |

|                           | 23                       | 22                       | 21                       | 20                       | 19                       | 18                       | 17                       | 16                       |

| bit symbol                | SETENA<br>(Interrupt 23) | SETENA<br>(Interrupt 22) | SETENA<br>(Interrupt 21) | SETENA<br>(Interrupt 20) | SETENA<br>(Interrupt 19) | SETENA<br>(Interrupt 18) | SETENA<br>(Interrupt 17) | SETENA<br>(Interrupt 16) |

| After reset               | 0                        | 0                        | 0                        | 0                        | 0                        | 0                        | 0                        | 0                        |

|                           | 15                       | 14                       | 13                       | 12                       | 11                       | 10                       | 9                        | 8                        |

|                           |                          |                          |                          |                          |                          |                          |                          |                          |

| bit symbol                | SETENA<br>(Interrupt 15) | SETENA<br>(Interrupt 14) | SETENA<br>(Interrupt 13) | SETENA<br>(Interrupt 12) | SETENA<br>(Interrupt 11) | SETENA<br>(Interrupt 10) | SETENA<br>(Interrupt 9)  | SETENA<br>(Interrupt 8)  |

| bit symbol<br>After reset |                          |                          |                          |                          |                          |                          |                          |                          |

|                           | (Interrupt 15)           | (Interrupt 14)           | (Interrupt 13)           | (Interrupt 12)           | (Interrupt 11)           | (Interrupt 10)           | (Interrupt 9)            | (Interrupt 8)            |

|                           | (Interrupt 15)<br>0      | (Interrupt 14)<br>0      | (Interrupt 13)<br>0      | (Interrupt 12)<br>0      | (Interrupt 11)<br>0      | (Interrupt 10)<br>0      | (Interrupt 9)            | (Interrupt 8)<br>0       |

# 7.6.2.5 Interrupt Set-Enable Register 1

| Bit  | Bit Symbol | Туре | Function                                                                                              |

|------|------------|------|-------------------------------------------------------------------------------------------------------|

| 31-0 | SETENA     | R/W  | Interrupt number [31:0]                                                                               |

|      |            |      | [Write]                                                                                               |

|      |            |      | 1: Enable                                                                                             |

|      |            |      | [Read]                                                                                                |

|      |            |      | 0: Disabled                                                                                           |

|      |            |      | 1: Enabled                                                                                            |

|      |            |      | Each bit corresponds to the specified number of interrupts.                                           |

|      |            |      | Writing "1" to a bit in this register enables the corresponding interrupt. Writing "0" has no effect. |

|      |            |      | Reading the bits can see the enable/disable condition of the corresponding interrupts.                |

Note:<SETENA> and <CLRENA> cannot be set simultaneously. The latter setting is valid.

|             | 31             | 30             | 29             | 28             | 27             | 26             | 25             | 24             |

|-------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| bit symbol  | CLRPEND        |

| bit symbol  | (Interrupt 31) | (Interrupt 30) | (Interrupt 29) | (Interrupt 28) | (Interrupt 27) | (Interrupt 26) | (Interrupt 25) | (Interrupt 24) |

| After reset | Undefined      |

|             | 23             | 22             | 21             | 20             | 19             | 18             | 17             | 16             |

| bit symbol  | CLRPEND        |

| bit symbol  | (Interrupt 23) | (Interrupt 22) | (Interrupt 21) | (Interrupt 20) | (Interrupt 19) | (Interrupt 18) | (Interrupt 17) | (Interrupt 16) |

| After reset | Undefined      |

|             | 15             | 14             | 13             | 12             | 11             | 10             | 9              | 8              |

| hit ovmbol  | CLRPEND        |

| bit symbol  | (Interrupt 15) | (Interrupt 14) | (Interrupt 13) | (Interrupt 12) | (Interrupt 11) | (Interrupt 10) | (Interrupt 9)  | (Interrupt 8)  |

| After reset | Undefined      |

|             | 7              | 6              | 5              | 4              | 3              | 2              | 1              | 0              |

| hit ovmbol  | CLRPEND        |

| bit symbol  | (Interrupt 7)  | (Interrupt 6)  | (Interrupt 5)  | (Interrupt 4)  | (Interrupt 3)  | (Interrupt 2)  | (Interrupt 1)  | (Interrupt 0)  |

| After reset | Undefined      |

## 7.6.2.8 Interrupt Clear-Pending Register 1

| Bit  | Bit Symbol | Туре | Function                   |

|------|------------|------|----------------------------|

| 31-0 | CLRPEND    | R/W  | Interrupt number [31:0]    |

|      |            |      | [Write]                    |

|      |            |      | 1: Clear pending interrupt |

|      |            |      | [Read]                     |

|      |            |      | 0: Not pending             |

|      |            |      | 1: Pending                 |

Note 1: <SETPEND> and <CLRPEND> cannot be set simultaneously. The latter setting is valid.

- Note 2: When the external interrupt is used, the user needs special consideration. When INTxxEN="0" (release for low-power consumption mode is unused), if IEx="0" is set, the CPU receives a "High" signal; therefore, an interrupt signal is considered to be exist. When the external interrupts are used, set IEx="1"(input is enable) to clear a suspended interrupt signal.

- Note 3: Each bit corresponds to the specified number can force interrupts into the pending state and determines which interrupts are currently pending. Writing "1" to a bit in this register clears the corresponding pending interrupt. However, writing "1" has no effect on an interrupt that is already being serviced. Writing "0" has no effect. Reading the bit returns the current state of the corresponding interrupts

|             | 31 | 30 | 29 | 28 | 27 | 26      | 25     | 24     |

|-------------|----|----|----|----|----|---------|--------|--------|

| bit symbol  | -  | -  | -  | -  | -  | -       | -      | -      |

| After reset | 0  | 0  | 0  | 0  | 0  | 0       | 0      | 0      |

|             | 23 | 22 | 21 | 20 | 19 | 18      | 17     | 16     |

| bit symbol  | -  | -  | -  | -  | -  | -       | -      | -      |

| After reset | 0  | 0  | 0  | 0  | 0  | 0       | 0      | 0      |

|             | 15 | 14 | 13 | 12 | 11 | 10      | 9      | 8      |

| bit symbol  | -  | -  | -  | -  | -  | -       | -      | -      |

| After reset | 0  | 0  | 0  | 0  | 0  | 0       | 0      | 0      |

|             | 7  | 6  | 5  | 4  | 3  | 2       | 1      | 0      |

| bit symbol  | -  | -  | -  | -  | -  | INTTBOF | INTTB1 | INTTB0 |

| After reset | 0  | 0  | 0  | 0  | 0  | 0       | 0      | 0      |

# 10.3.7 TBxST (Status Register)

| Bit  | Bit Symbol | Туре | Function                                                                                                                                                                        |

|------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-3 | -          | R    | Read as "0".                                                                                                                                                                    |

| 2    | INTTBOF    | R    | Overflow interrupt request flag<br>0: No overflow occurs<br>1: Overflow occurs<br>When an up-counter is overflow, "1" is set.                                                   |

| 1    | INTTB1     | R    | Match (TBxRG1) interrupt request flag<br>0: No match is detected.<br>1: Detects a match with TBxRG1<br>When a match with the timer register 1 (TBxRG1) is detected, "1" is set. |

| 0    | INTTB0     | R    | Match(TBxRG0) interrupt request flag<br>0: No match is detected<br>1: Detects a match with TBxRG0<br>When a match with the timer register 0 (TBxRG0) is detected, "1" is set.   |

Note 1: Even if mask configuration by TBxIM register is valid, the status is set to TBxST register.

Note 2: When the interrupt mask configuration is disabled by the corresponding bit of TBxIM register, the interrupt is issued to the CPU.

Note 3: To clear the flag, read TBxST register.

[Main process] Allocates a corresponding port to TBxEN<TBEN> = "1" TBxRUN<TBPRUN><TBRUN> = "00" TBxRG0 = 0x\*\*\*\* TBxRG1 = 0x\*\*\*\* TBxFFCR<TBC1T1><TBC0T1><TBE1T1><TBE0T1> = "0011" TBxFFCR<TBF0C[1:0]> = "10"

Stops prescaler and counter. Sets a counter value. (3 ms/φT1 Sets a cycle. ((3+2)ms/φT1) Sets TBxFF0 to invert the signal by detection of a match between TBxRG0 or TBxRG1 and the up-counter; sets TBxFF0 not to reverse by capturing TBxCP0 or TBxCP1. Sets an initial value of TBxFF0 to "0".

Sets a source clock to  $\phi$ T1. Disables the capture function.

TBxMOD<TBCPM[2:0]> = "000" TBxMOD<TBCP> = "1" TBxMOD<TBCLE> = "1" TBxMOD<TBCLK[2:0]> = "001" Allocates a corresponding port to TBxOUT. TBxIM<TBIMOF><TBIM1><TBIM0> = "101"

Capture enable set register = 0x\*\*\*\*\*\*\*

TBxRUN<TBPRUN><TBRUN> = "11" [Process in INTTBx interrupt service routine] TBxFFCR<TBE1T1><TBE0T1> = "00" TBxRUN<TBPRUN><TBRUN> = "00" Masks interrupts except one caused by a match with TBxRG1. Permits INTTBx interrupt by setting the corresponding bit to "1".

Starts prescaler and counter.

Enables TMRBx operation.

Disables TBxFF0 reverse trigger setting. Stops prescaler and counter.

Note:\*; Optional value

# 15.3.2 TSPIxCR0 (TSPI Control Register 0)

|             | 31  | 30  | 29 | 28 | 27 | 26 | 25 | 24    |

|-------------|-----|-----|----|----|----|----|----|-------|

| bit symbol  | -   | -   | -  | -  | -  | -  | -  | -     |

| After reset | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0     |

|             | 23  | 22  | 21 | 20 | 19 | 18 | 17 | 16    |

| bit symbol  | -   | -   | -  | -  | -  | -  | -  | -     |

| After reset | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0     |

|             | 15  | 14  | 13 | 12 | 11 | 10 | 9  | 8     |

| bit symbol  | -   | -   | -  | -  | -  | -  | -  | -     |

| After reset | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0     |

|             | 7   | 6   | 5  | 4  | 3  | 2  | 1  | 0     |

| bit symbol  | SW  | RST | -  | -  | -  | -  | _  | TSPIE |

| After reset | 0 0 |     | 0  | 0  | 0  | 0  | 0  | 0     |

| Bit  | Bit Symbol | Туре | Function                                                                                                                                                                                                                                                                                                   |

|------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-8 | -          | R    | Read as "0".                                                                                                                                                                                                                                                                                               |

| 7-6  | SWRST[1:0] | W    | TSPI software reset (Note)<br>Software reset occurs by writing "10" $\rightarrow$ "01".                                                                                                                                                                                                                    |

|      |            |      | If "10" $\rightarrow$ "01" is consecutively written to <swrst[1:0]> bit, software reset occurs. Software reset initial-<br/>izes control registers, transmit/receive FIFO, transmit/receive shift registers and all internal circuits. Howev-<br/>er, <tspie> bit is not initialized.</tspie></swrst[1:0]> |

| 5-1  | -          | R    | Read as "0".                                                                                                                                                                                                                                                                                               |

| 0    | TSPIE      | R/W  | TSPI operation control<br>0: Stop<br>1: Operation<br><tspie> controls a whole operation of TSPI to start/stop (clock shutdown). When <tspie>=0(stop) is set,</tspie></tspie>                                                                                                                               |

|      |            |      | a clock is not fed into TSPI internally. Set <tspie>=1(operation) to start operation first. Then perform initial-<br/>ization and communications.<br/><tspie> is not initialized by software reset.</tspie></tspie>                                                                                        |

Note: Completion of software reset takes two clocks after an instruction is executed.

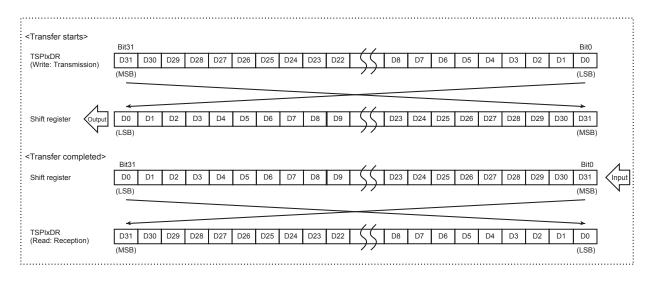

## (3) LSB First Transfer (32-bit data without a parity bit, 32-bit frame length)

Figure 15-5 shows a 32-bit data length transmit/receive operation when parity function is disabled.

In the transmission, data in the transmit FIFO is sorted bit by bit when the data is copied to the shift register. Transmit data copied to shift register is transferred from D0 until reaching 32-bit shifted data on serial clock.

In the reception, receive data is stored in the D0 of the shift register. Shift operation repeats on serial clock. If the shift register stores 32-bit reception data, data is sorted bit by bit and copied to receive FIFO.

Figure 15-5 LSB first (32-bit data without a parity bit)

# 15.4.2 Transfer Format

TSPI has one chip select signal outputs (TSPIxCSO) that enable communication with one type of external slave devices.

It also has one chip select signal (TSPIxCSIN) that enables communication with one type of master device.

A polarity of serial clock can be selected.

In the SPI mode, a polarity of TSPIxCSO and the generation timing can also be selected.

TSPIxTXD is selected in the idle mode, in which no communication is made.

## 15.4.2.1 Polarity of TSPIxCS Signal and Generation Timing

TSPIxCSO can select its polarity.

A logic of TSPIxCSO is set by TSPIxFMTR0<CS0POL>.

If TSPIxFMTR0<CS0POL> is set to "0", negative logic is selected.; if TSPIxFMTR0<CS0POL> is set to "1", positive logic is selected.

A generation timing of TSPIxCSO can be set. The following four timings are settable.

1. Serial clock delay

$t_A$  is a delay time from the time when TSPIxCSO is asserted until the transmit clock (TSPIxSCK) changes. To set a serial clock delay time, set TSPIxFMTR0<CSSCKDL>.

2. TSPIxCSO negate delay

$t_B$  is a delay time from the time when TSPIxCSO is negated after serial transfer completion. To set a TSPIxCSO negate delay time, set TSPIxFMTR0<SCKCSDL>.

3. Interval time between frames in the burst transfer

$t_{C}$  is an interval time between frames in the burst transfer. To set an interval time between frames, set TSPIxFMTR0<FINT>.

4. Minimum idle time

t<sub>D</sub> is a minimum wait time from the time when TSPIxCSO is negated and then until TSPIxC-SO is asserted again. To set minimum idle time, set TSPIxFMTR0<CSINT>.

|             | 31        | 30                   | 29         | 28        | 27          | 26        | 25        | 24        |

|-------------|-----------|----------------------|------------|-----------|-------------|-----------|-----------|-----------|

| bit symbol  | -         | -                    | -          | -         | -           | -         | -         | -         |

| After reset | 0         | 0                    | 0          | 0         | 0           | 0         | 0         | 0         |

|             | 23        | 22                   | 21         | 20        | 19          | 18        | 17        | 16        |

| bit symbol  | -         | -                    | -          | -         | -           | -         | -         | -         |

| After reset | 0         | 0                    | 0          | 0         | 0           | 0         | 0         | 0         |

|             | 15        | 14                   | 13         | 12        | 11          | 10        | 9         | 8         |

| bit symbol  | -         | -                    | -          | -         | -           | -         | -         | -         |

| After reset | 0         | 0                    | 0          | 0         | 0           | 0         | 0         | 0         |

|             | 7         | 6                    | 5          | 4         | 3           | 2         | 1         | 0         |

| bit symbol  | wakeup_en | phy_re-<br>mote_wkup | phy_resetb | suspend_x | phy_suspend | pw_detect | pw_resetb | usb_reset |

| After reset | 0         | 0                    | 1          | 1         | 0           | 0         | 1         | 0         |

# 16.4.1.20 UDFSPWCTL(Power Detect Control Register)

|             | 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| bit symbol  | -     | -     | -     | -     | -     | -     | -     | -     |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             | 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

| bit symbol  | -     | -     | -     | -     | -     | -     | -     | -     |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

| bit symbol  | -     | -     | -     | -     | -     | -     | -     | -     |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| bit symbol  | m_ep7 | m_ep6 | m_ep5 | m_ep4 | m_ep3 | m_ep2 | m_ep1 | m_ep0 |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

# 16.4.2.12 UDFS2INTEPMSK(INT\_EP\_MASK register)

| Bit   | Bit Symbol        | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-16 | -                 | R    | Read as undefined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15-8  | Reserved          | R/W  | Write as "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7-0   | m_ep7 to<br>m_ep0 | R/W  | Mask control of flag output.<br>0 : output<br>1: no output<br>Sets whether or not to output flags of UDFS2INTEP and UDFS2INTRX0 to the int_ep pin and the<br>int_rx_zero pin respectively. When an EP is masked, each bit of UDFS2INTEP will be set when the trans-<br>fer of the relevant EP has successfully finished, but the int_ep pin will not be asserted. Similarly, when an<br>EP is masked, each bit of UDFS2INTRX0 will be set when Zero-Length data is received at the relevant<br>EP, but the int_rx_zero pin will not be asserted. However, bit 0 is only valid for UDFS2INTRX0. |

## (1) How to use UDFS2INT / UDFS2INTEP / UDFS2INTEPMSK

An example of using UDFS2INT / UDFS2INTEP / UDFS2INTEPMSK is provided for EP1 to 3.

1. When using EP 1 and EP 2 with DMA (EP I/F) and using only EP3 via PVCI-I/F

|                    | <i_ep></i_ep>   | Used as the interrupt source of EP3. This bit is also used when clearing. |

|--------------------|-----------------|---------------------------------------------------------------------------|

| UDFS2INT           | <m_ep></m_ep>   | Used as the mask of the interrupt source of EP3.                          |

|                    | <i_ep1></i_ep1> | Don't care                                                                |

| UDFS2INTEP         | <i_ep2></i_ep2> | Don't care                                                                |

|                    | <i_ep3></i_ep3> | Don't care                                                                |

|                    | <m_ep1></m_ep1> | Set 1 to mask the bit.                                                    |

| UDFS2IN-<br>TEPMSK | <m_ep2></m_ep2> | Set 1 to mask the bit.                                                    |

|                    | <m_ep3></m_ep3> | Write 0.                                                                  |

2. When using EP2 and EP3 via PVCI-I/F and using EP1 with DMA

After initialization, set 1 to UDFS2INTEPMSK of the EP to be used with DMA to mask it. When making interrupt responses for more than one EPs, be sure to use UDFS2INTEP. Ignore UDFS2INT<i\_ep> and always enable  $<m_ep>$  as 0.

## 16.5.7.2 Resuming from suspended state (resuming from the USB host)

The procedures to resume from the suspended state is performed based o the condition of the CLK\_H. When resuming is recognized, make settings again for restarting master transfers.

1. Stopping the CLK\_H

The procedures to stop the CLH\_H and the signal variation are as shown below.

|                                                                                                                  | á      | a b  | c c  | d e | f     | g | h | ,i | j k | ζ. |

|------------------------------------------------------------------------------------------------------------------|--------|------|------|-----|-------|---|---|----|-----|----|

| suspend_x                                                                                                        |        |      |      |     | /     |   |   |    |     |    |

| <suspend_resume_en>,<br/><power_detect_en><br/>suspend_resume interrupt re</power_detect_en></suspend_resume_en> | auest  |      |      |     |       |   |   |    |     |    |

| <pre></pre>                                                                                                      |        |      |      |     |       |   |   |    |     |    |

| WAKEUP                                                                                                           |        |      |      |     |       |   |   |    |     |    |

| INTUSBWKUP interrupt reg                                                                                         | uest   |      |      |     | *     |   |   |    |     |    |

| VBUSPOWER                                                                                                        | "H"    |      |      |     |       |   |   |    |     |    |

| <pw_detect></pw_detect>                                                                                          | "H"    |      |      |     |       |   |   |    |     |    |

| power_detect interrupt req                                                                                       | uest   |      |      |     |       |   |   |    |     |    |

| <phy_suspend> .</phy_suspend>                                                                                    |        |      | 4    |     |       | ۱ |   |    |     |    |

| PHYSUSPEND                                                                                                       |        |      |      |     |       | _ |   |    |     |    |

| CGEXTENDO0 <usbena></usbena>                                                                                     |        |      |      |     |       | j |   |    |     |    |

| CLK_U                                                                                                            | mmmm   | hnnh | ЛЛ   | η_  |       |   |   |    |     |    |

|                                                                                                                  | nnnnnn | hnnh | أرار | ЛЛ  | :<br> | j | M |    |     |    |

# Figure 16-17 Signal operations when suspended and resumed (when CLK\_H is stopped)

- a. The suspend\_x of the UDC2 is asserted to zero by detecting the suspend state on the USB bus, and the INTUSB(suspend\_resume) interrupt occurs.

- b. The service routine of the INTUSB(suspend\_resume) interrupt clears the interrupt factor.

- c. Set the UDFSPWCTL<phy\_suspend> to "1". Setting the <phy\_suspend> to "1" asserts the PHYSUSPEND output signal to "0".

Zero clear the CGEXTENDO0<USBENA> of the clock/mode control circuit to stop the CLK\_U.

- d. Set the UDFSPWCTL<wakeup\_en> to "1". Zero clear the UDFSINTENB<power\_detect\_en><suspend\_resume\_en> not to generate the INTUSB(power\_detect, suspend\_resumu) interrupt.

- e. With the INTUSBWKUP interrupt, the operation mode moves into the low-power consumption mode and stops the CLK\_H.

· Configured state:

| <recipient> = Device :</recipient>   | Write the information on the device (Table 16-3) to UDFS2EP0FIFO.                                           |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------|

| <recipient> = Interface:</recipient> | If the interface specified by lwIndex, write the information on the interface (Table 16-4) to UDFS2EP0FIFO. |

| <recipient> = EP :</recipient>       | If the EP specified by wIndex, <u>write the information on the relevant EP(Table 16-5) to UDFS2EP0FIFO.</u> |

### Table 16-3 Information on the device to be returned by Get Status request

| D15 | D14 | D13 | D12 | D11 | D10 | D9               | D8              |

|-----|-----|-----|-----|-----|-----|------------------|-----------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0                | 0               |

| D7  | D6  | D5  | D4  | D3  | D2  | D1               | D0              |

| 0   | 0   | 0   | 0   | 0   | 0   | Remote<br>Wakeup | Self<br>Powered |

RemoteWakeup 0 indicates the bus power while 1 indicates the selfpower.

(D1)

SelfPowered (D0)

0 indicates the remote wakeup function is disabled while 1 indicates it is enabled.

### Table 16-4 Information on the interface to be returned by Get Status

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 |

|-----|-----|-----|-----|-----|-----|----|----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  |

| D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0 |

| 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  |

Please note that all bits are 0.

## Table 16-5 Information on the EP to be returned by Get Status request

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8   |

|-----|-----|-----|-----|-----|-----|----|------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0    |

| D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0  | Halt |

Halt If this bit is 1, it indicates that the relevant EP is in the "Halt" state. (D1)

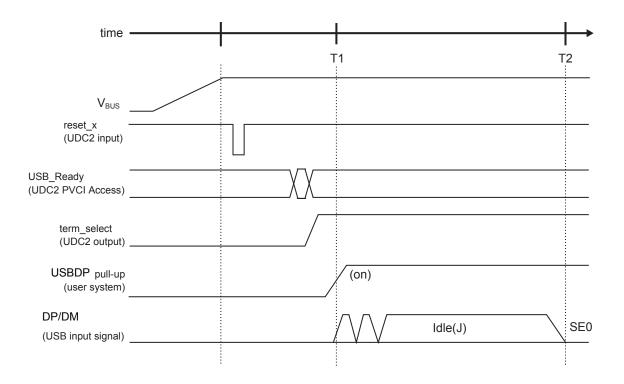

### 16.9.1.1 Connect / Disconnect Operations

• T0: VBUS detection

When VBUS is detected, a system reset (reset\_x input) should be applied to UDC2.

xcvr\_select is "High" and term\_select is "Low".

• T1: Device connect (no later than 100ms after T0)

The device must enable DP no later than 100 ms after VBUS detection (T0) to notify the host of the connected state. Therefore, when VBUS is detected and the device is ready to communicate with the host, the system should access the UDFS2CMD in UDC2 to set the USB\_Ready command. After that, the user system sets the port using software to enable the DP pull-up.

T2:USB Reset Start (more than 100ms after 100ms)

## (2) Disconnect Operation

When a disconnected state is detected, it is recommended to apply a system reset to UDC2.

| HPADCH[3:0]           | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 |

|-----------------------|------|------|------|------|------|------|------|------|

| Conversion<br>channel | AIN0 | AIN1 | AIN2 | AIN3 | AIN4 | AIN5 | AIN6 | AIN7 |

| Selection of analog input | channel |

|---------------------------|---------|

|---------------------------|---------|

| HPADCH[3:0]           | 1000 | 1001 | 1010  | 1011  | 1100  | 1101  | 1110  | 1111  |

|-----------------------|------|------|-------|-------|-------|-------|-------|-------|

| Conversion<br>channel | AIN8 | AIN9 | AIN10 | AIN11 | AIN12 | AIN13 | AIN14 | AIN15 |

# 18.3 Operation

# 18.3.1 Selecting detection voltage and enabling voltage detection operation

Voltage detection is enabled when voltage to be detected is selected by setting the register LVDCRn<LVL [2:0]> and "1" is set to the LVDCRn<EN>.

# 18.3.2 Reset by Detecting a supply voltage

Reset occurs when "1" is set to the LVDCRx<RSTEN> and the supply voltage falls under the set detection voltage.

It needs approximately 100 µs to detect voltage reduction and generate reset. If the period that the supply voltage falls under the detected voltage is short, reset may not occur.

# 18.3.3 Interrupt by Detecting a supply voltage

A interrupt (INTLVD) occurs When "0" is set to LVDCEn<RSTEN> and "1" is set to LVDCRn<INTEN> if the supply voltage falls under or over the set detection voltage level.

The Interrupt condition can be set by LVDCRn<INTSEL>.

An interrupt occurs when "0" is set to the LVDCRx<INTSEL> and the supply voltage falls under the set detection voltage.

An interrupt occurs when "1" is set to the LVDCRx<INTSEL> and the supply voltage falls under or over the set detection voltage.

It needs approximately 100  $\mu$ s to detect voltage reduction and generate a interrupt. If the period that the supply voltage falls under the detected voltage is short, an interrupt may not occur.

# 18.3.4 Detecting Status

Reading the LVDCRn<SR> can be confirmed the Detecting status of low voltage detection.

When the LVDCRn<ST> is "0", the voltage is the same as detection voltage or higher.

When the LVDCRn<ST> is "1", the voltage is the same as detection voltage or lower.

In the Interrupt service routine (ISR) of low voltage detection (LVD), to read the status of LVDCRn<ST> after detection is known stably the shift of the voltage

#### 20.2.5.4 Automatic Protect Bit Program

### (1) Operation Description

The automatic protect bit program writes "1" to a protect bit at a time. To set "0" to a protect bit, use the automatic protect bit erase command.

For detail of the protect function, refer to "20.1.5 Protect/Security Function".

#### (2) How to Set

The 1st to 6th bus write cycles indicate the automatic protect bit program command. In the 7th bus write cycle, the protect bit to be written is specified. After the command sequence is input, the automatic protect bit program starts. Check whether write operation is normally terminated with FCPSRA<BLK>.

### 20.2.5.5 Auto Protect Bit Erase

### (1) Operation Description

The automatic protect bit erase command operation depends on the security status. For detail of security status, refer to "20.1.5 Protect/Security Function".

• Non-security status

Clear the specified protect bit to "0". Protect bit erase is performed in 4-bit unit.

Security status

Erase all protect bits after all addresses of Flash memory are erased.

#### (2) How to Set

The 1st to 6th bus write cycles indicate the automatic protect bit erase command. In the 7th bus write cycle, the protect bit to be erased is specified. After the command sequence is input, the automatic protect bit erase operation starts.

In the non-security status, specified protect bit is erased. Check whether erase operation is normally terminated with FCPSRA<BLK>.

In the security status, all addresses and all protect of Flash memory bits are erased. Confirm if data and protect bits are erased normally. If necessary, execute the automatic protect bit erase, automatic chip erase or automatic block erase.

All cases are the same as other commands, FCSR<RDY\_BSY> becomes "0" during the automatic protect bit erase command operation. After the operation is complete, FCSR<RDY\_BSY> becomes "1" and Flash memory will return to the read mode. To abort the operation, a hardware reset is required.

## 20.2.5.6 ID-Read

## (1) Operation Description

The ID-Read command can read information including Flash memory type and three types of codes such as a maker code, device code and macro code.

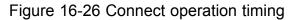

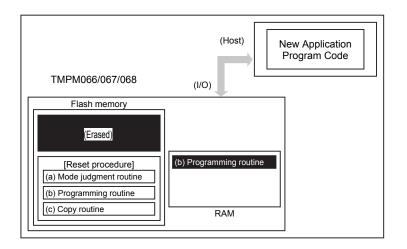

## 20.4.1.4 Step-4

Jump to the reprogramming routine in the built-in RAM to release the write/erase protection for the old application program, and to erase a flash in block unit.

### 20.4.1.5 Step-5

Continue to execute the flash programming routine to download new program data from the host controller and program it into the erased flash block. When the programming is complete, the write/erase protection of that flash block in the user program area must be set.

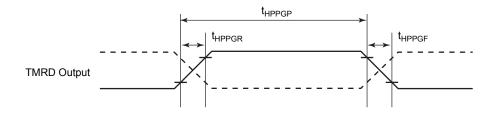

# 23.5.6 High Resolution 16-bit Timer (TMRD Ver.C) PPG output

## 23.5.6.1 AC Measurement Condition

The AC characteristics data of this chapter is measured under the following conditions.

- Output levels: High =  $0.8 \times \text{DVDD3}$ , Low =  $0.2 \times \text{DVDD3}$

- Load capacity: CL = 30pF

|                                   |                    |         | DVDD3 = 2. | 7V to 3.6V |  |

|-----------------------------------|--------------------|---------|------------|------------|--|

| Deremeter                         | Symbol             | TMRDCLK | ( = 96 MHz | Unit       |  |

| Parameter                         | Symbol             | Min.    | Max.       |            |  |

| Minimum pulse width of PPG output | t <sub>HPPGP</sub> | 104.2   | -          |            |  |

| Rising time of PPG output         | t <sub>HPPGR</sub> | -       | 15         | ns         |  |

| Falling time of PPG output        | t <sub>HPPGF</sub> | -       | 15         |            |  |