#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20MHz                                                                           |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                        |

| Peripherals                | PWM, WDT                                                                        |

| Number of I/O              | 79                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                    |

| Data Converters            | <u>.</u>                                                                        |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | PG-TQFP-100-5                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc164n-32f20f-bb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **XC164N Revision History:**

Previous Version(s):

| Page | Subjects (major changes since last revision) |  |  |  |  |

|------|----------------------------------------------|--|--|--|--|

| raye | Subjects (major changes since last revision) |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

|      |                                              |  |  |  |  |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

# 16-Bit Single-Chip Microcontroller with C166SV2 Core XC166 Family

# **1** Summary of Features

- High Performance 16-bit CPU with 5-Stage Pipeline

- 25 ns Instruction Cycle Time at 40 MHz CPU Clock (Single-Cycle Execution)

- 1-Cycle Multiplication (16  $\times$  16 bit), Background Division (32 / 16 bit) in 21 Cycles

- 1-Cycle Multiply-and-Accumulate (MAC) Instructions

- Enhanced Boolean Bit Manipulation Facilities

- Zero-Cycle Jump Execution

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Fast Context Switching Support with Two Additional Local Register Banks

- 16 Mbytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area (C166 Family Compatible)

- 16-Priority-Level Interrupt System with up to 75 Sources, Sample-Rate down to 50 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC), 24-Bit Pointers Cover Total Address Space

- Clock Generation via on-chip PLL (factors 1:0.15 ... 1:10), or via Prescaler (factors 1:1 ... 60:1)

- On-Chip Memory Modules

- 2 Kbytes On-Chip Dual-Port RAM (DPRAM)

- 4 Kbytes On-Chip Data SRAM (DSRAM)<sup>1)</sup>

- 6 Kbytes On-Chip Program/Data SRAM (PSRAM)

- 256 Kbytes On-Chip Program Memory (Flash Memory or Mask ROM)<sup>1)</sup>

- On-Chip Peripheral Modules

- Two 16-Channel General Purpose Capture/Compare Units (12 Input/Output Pins)

- Capture/Compare Unit for flexible PWM Signal Generation (CAPCOM6) (3/6 Capture/Compare Channels and 1 Compare Channel)

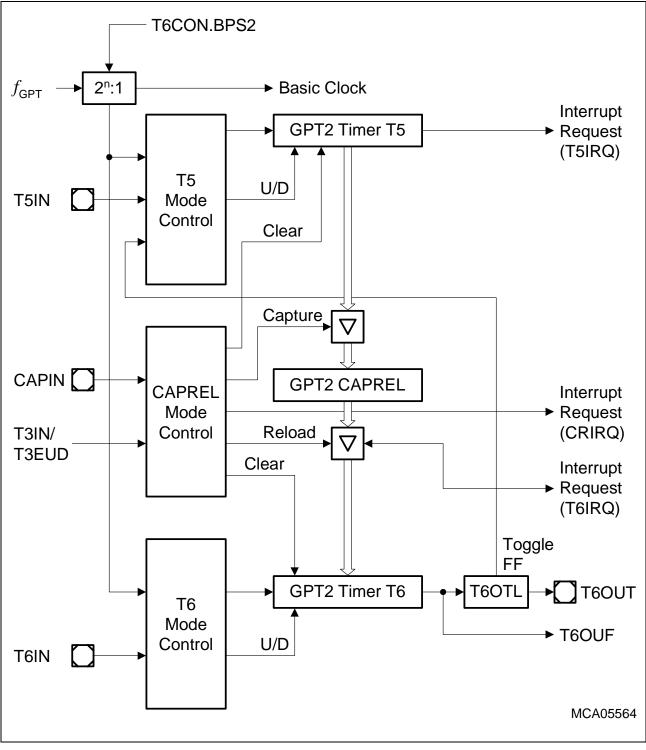

- Multi-Functional General Purpose Timer Unit with 5 Timers

- Two Synchronous/Asynchronous Serial Channels (USARTs)

- Two High-Speed-Synchronous Serial Channels

- On-Chip Real Time Clock

- Idle, Sleep, and Power Down Modes with Flexible Power Management

- Programmable Watchdog Timer and Oscillator Watchdog

- Up to 12 Mbytes External Address Space for Code and Data

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses

<sup>1)</sup> Depends on the respective derivative. The derivatives are listed in Table 1.

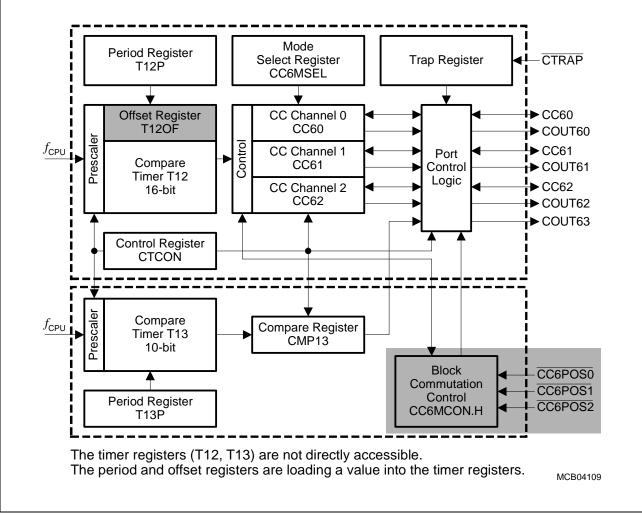

## 3.7 The Capture/Compare Unit CAPCOM6

The CAPCOM6 unit supports generation and trool of timing sequences on up to three 16-bit capture/compareachels plus one independentO-bit compare channel. In compare mode the CAPCOM6 unit provide two output signate channel which have inverted polarity and moverlapping pulse transitions (deadtime control). The compare channel can generate single PWM output signate and is further used to modulate the capture/opare output signals.

In capture mode the contentscompare timer T12 is storied the capture registers upon a signal trasition at pins CCx.

Compare timers T12 (16-bit) and T13 (10 abit) free running timers which are clocked by the prescaled system clock.

#### Figure 6 CAPCOM6 Block Diagram

For motor control applications the subunity nyagenerate versatile nultichannel PWM signals which are basically eightcontrolled by compareneir T12 or by a typical hall sensor pattern at the interrimptute (block commutation).

## Functional Description

| Table 7 | Summary of the XC164N s Parallel Ports         |                                                                                                                                                      |  |  |  |

|---------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Port    | Control                                        | Alternate Functions                                                                                                                                  |  |  |  |

| PORTO   | Pad drivers                                    | Address/Dationes or data lines                                                                                                                       |  |  |  |

| PORT1   | Pad drivers                                    | Address lines                                                                                                                                        |  |  |  |

|         |                                                | Capture inputs or compare outputs,<br>Serial interface lines,<br>Fast external interrupt inputs                                                      |  |  |  |

| Port 3  | Pad drivers,<br>Open drain,<br>Input threshold | Timer control signalsserial interface lines,<br>Optional bus combl signal BHE/WRH,<br>System clock output CLKOUT (or FOUT),<br>Debug interface lines |  |  |  |

| Port 4  | Pad drivers,<br>Open drain,<br>Input threshold | Segment address lines                                                                                                                                |  |  |  |

|         |                                                | Optional chip select signals                                                                                                                         |  |  |  |

| Port 5  |                                                | Timer control signals                                                                                                                                |  |  |  |

| Port 9  | Pad drivers,<br>Open drain,<br>Input threshold | Capture inputs or compare outputs                                                                                                                    |  |  |  |

| Port 20 | Pad drivers,<br>Open drain                     | Bus control signals RDWR/WRL, ALE,<br>External access enabl <u>e pin EA</u><br>Reset indication output RSTOUT                                        |  |  |  |

1) For multiplexed bus cycles.

2) For demultiplexed bus cycles.

3) For more than 64 Kbytes of external resources.

## 3.15 Power Management

The XC164N provides several eans to control the over it consumes either at a given time or averaged over a certain timespeare mechanisms can be used (partly in parallel):

Power Saving Modes switch the XC164N into a siple operating mode (control via instructions).

Idle Mode stops the CPWhile the peripherals pacontinue to operate.

Sleep Mode and Power Down Molestop all clock signals all operation (RTC may optionally continue running) leep Mode can be termined by external interrupt signals.

Clock Generation Management controls the distribution and the frequency of internal and externation of signals. While the clock signals for currently inactive parts of logic are disabled automially, the user can reduce the XC164N s CPU clock frequency which drastically duces the consumed power.

External circuitry can be controllized the programmable requency output FOUT. Peripheral Management permits temporary disabling peripheral modules (control via register SYSCON3). Each peripheral can separally be disabled/enabled.

The on-chip RTC supports intredittent operation of MC2164N by generating cyclic wake-up signals. This offerfull performance to quicklyace on action requests while the intermittent sleep phases beauty reduce the average over consumption of the system.

# 3.16 Instruction Set Summary

Table 8 lists the instructions of X16164N in a condensed way.

The various addressing modes theatin be used with a specifine struction, the operation of the instructions, parameteous conditional exection of instructions and the opcodes for each instructionan be found in the instruction Set Manual.

This document also provides a dietal description of each instruction.

|                                     | uction set summary                                                                            |       |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------|-------|--|--|

| Mnemonic                            | Description                                                                                   |       |  |  |

| ADD(B)                              | Add word (byet) operands                                                                      |       |  |  |

| ADDC(B)                             | Add word (byte)perands with Carry                                                             |       |  |  |

| SUB(B)                              | SUB(B) Subtract word (byte) operands                                                          |       |  |  |

| SUBC(B)                             | Subtract word (byte)perands with Carry                                                        | 2 / 4 |  |  |

| MUL(U)                              | (Un)Signed multiply dect GPR by direct GPR (16- u16-bit)                                      |       |  |  |

| DIV(U)                              | /(U) (Un)Signed divide register/IDL by direct GPR (16-/16-                                    |       |  |  |

| DIVL(U)                             | (Un)Signed longdivide reg. MD by dicet GPR (32-/16-b                                          | t) 2  |  |  |

| CPL(B)                              | Complement direct word (byte) GPR                                                             | 2     |  |  |

| NEG(B)                              | Negate direct word (byte) GPR                                                                 |       |  |  |

| AND(B)                              | ND(B) Bitwise AND, (word/byte operands)                                                       |       |  |  |

| OR(B)                               | Bitwise OR, (word/byte operands)                                                              |       |  |  |

| XOR(B)                              | Bitwise exclusive OR(word/byte operands)                                                      | 2 / 4 |  |  |

| BCLR/BSET                           | Clear/Set direct bit                                                                          |       |  |  |

| BMOV(N)                             | Move (negated) dice bit to direct bit                                                         |       |  |  |

| BAND/BOR/BXOR                       | AND/OR/XOR direct bit with direct bit                                                         | 4     |  |  |

| BCMP                                | BCMP Compare direct bit to direct bit                                                         |       |  |  |

| BFLDH/BFLDL                         | Bitwise modify masked high/low byte of bit-addressab direct word memory ith immediate data    | e4    |  |  |

| CMP(B) Compare word (byte) operands |                                                                                               | 2 / 4 |  |  |

| CMPD1/2                             | CMPD1/2 Compare word data to GARd decrement GPR by 1/2                                        |       |  |  |

| CMPI1/2                             | 1/2Compare word data to GBRd increment GPR by 1/2                                             |       |  |  |

| PRIOR                               | Determine number of shtifcycles to normalize direct word GPR and store result direct word GPR | 2     |  |  |

| SHL/SHR                             | Shift left/right direct word GPR                                                              | 2     |  |  |

Table 8 Instruction Set Summary

#### **Electrical Parameters**

#### Operating Conditions

The following operating condits must not be exceeded ensure correct operation of the XC164N. All parameters spiced in the following seculis refer to these operating conditions, unlespitherwise noticed.

| Description Cumbel Limit Values Unit Nates |                        |              |                      |      |                                                   |  |

|--------------------------------------------|------------------------|--------------|----------------------|------|---------------------------------------------------|--|

| Parameter                                  | Symbol                 | Limit Values |                      | Unit | Notes                                             |  |

|                                            |                        | Min.         | Max.                 |      |                                                   |  |

| Digital supply voltage for the core        | V <sub>DDI</sub>       | 2.35         | 2.7                  | V    | Active mode,<br>$f_{CPU} = f_{CPUmax}^{1}$        |  |

| Digital supply voltage for<br>IO pads      | V <sub>DDP</sub>       | 4.4          | 5.5                  | V    | Active mode <sup>3)</sup>                         |  |

| Supply Voltage Differenc                   | e 'V <sub>DD</sub>     | -0.5         |                      | V    | V <sub>DDP</sub> - V <sub>DDI</sub> <sup>4)</sup> |  |

| Digital ground voltage                     | $V_{SS}$               | 0            |                      | V    | Reference voltage                                 |  |

| Overload current                           | I <sub>ov</sub>        | -5           | 5                    | mA   | Per IO piħ <sup>)6)</sup>                         |  |

|                                            |                        | -2           | 5                    | mA   | Per Port 5 input<br>pin <sup>5)6)</sup>           |  |

| Overload current couplin                   | gK <sub>ova</sub>      |              | 1.0 u10 <sup>4</sup> |      | I <sub>OV</sub> > 0                               |  |

| factor for Port 5 inputs                   |                        |              | 1.5 u10 <sup>3</sup> |      | I <sub>OV</sub> < 0                               |  |

| Overload current couplin                   |                        |              | 5.0 u10 <sup>3</sup> |      | I <sub>OV</sub> > 0                               |  |

| factor for digital I/O pins                | 6                      |              | 1.0 u10 <sup>2</sup> |      | I <sub>OV</sub> < 0                               |  |

| Absolute sum of overload currents          | al ¢al <sub>ov</sub> ∣ |              | 50                   | mA   | 6)                                                |  |

| External Load<br>Capacitance               | CL                     |              | 50                   | pF   | Pin drivers in default mode <sup>8)</sup>         |  |

| Ambient temperature                        | T <sub>A</sub>         |              |                      | Ģ    | see Table 1                                       |  |

## Table 10Operating Condition Parameters

1)  $f_{CPUmax} = 40 \text{ MHz}$  for devices marked  $40f_{CPUmax} = 20 \text{ MHz}$  for devices marked 20F.

2) External circuitry mustageantee low-level at the RSTIpin at least until both power supply voltages have reached the operating range.

3) The specified voltage range is allowed for operation. The range limits may be reached under extreme operating conditions. However, specified parameters has leakage currents, refer to the standard operating voltage range  $\forall f_{DP} = 4.75 \text{ V}$  to 5.25 V.

4) This limitation must be fulfilled under all operatingitions including power-ramp-up, power-ramp-down, and power-save modes.

www.infineon.com

Published by Infineon Technologies AG