#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40MHz                                                                           |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                        |

| Peripherals                | PWM, WDT                                                                        |

| Number of I/O              | 79                                                                              |

| Program Memory Size        | 256КВ (256К х 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | <u>.</u>                                                                        |

| RAM Size                   | 12K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                    |

| Data Converters            | -                                                                               |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | PG-TQFP-100-5                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc164n-32f40f-bb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **General Device Information**

# 2.2 Pin Configuration and Definition

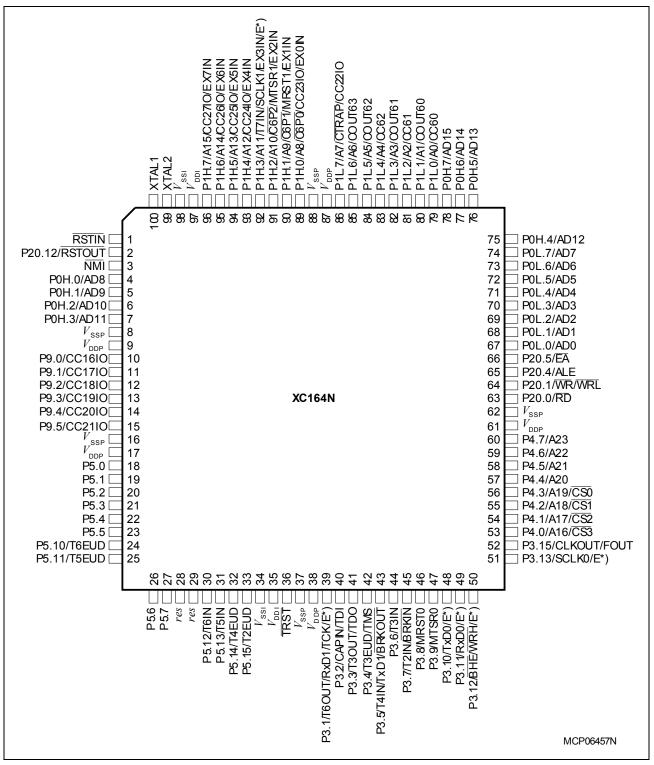

The pins of the XC164N are described in detail in **Table 1**, including all their alternate functions. **Figure 2** summarizes all pins in a condensed way, showing their location on the package. E\*) mark pins to be used as alternate external interrupt inputs.

Figure 2Pin Configuration (top view)

# **General Device Information**

| Table 2 | Pir         | n Definit      | ions and Fu                              | unctions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-------------|----------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin<br>Num. | Input<br>Outp. | Function                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P20     |             | IO             | programme<br>state) or ou<br>(standard o | a 5-bit bidirectional I/O port. Each pin can be<br>ed for input (output driver in high-impedance<br>utput. The input threshold of Port 20 is selectable<br>or special).<br>Ing Port 20 pins also serve for alternate functions:                                                                                                                                                                                                                                |

| P20.0   | 63          | 0              | RD                                       | External Memory Read Strobe, activated for<br>every external instruction or data read access.                                                                                                                                                                                                                                                                                                                                                                  |

| P20.1   | 64          | 0              | WR/WRL                                   | External Memory Write Strobe.<br>In WR-mode this pin is activated for every<br>external data write access.<br>In WRL-mode this pin is activated for low byte<br>data write accesses on a 16-bit bus, and for<br>every data write access on an 8-bit bus.                                                                                                                                                                                                       |

| P20.4   | 65          | 0              | ALE                                      | Address Latch Enable Output.<br>Can be used for latching the address into<br>external memory or an address latch in the<br>multiplexed bus modes.                                                                                                                                                                                                                                                                                                              |

| P20.5   | 66          | 1              | ĒĀ                                       | <ul> <li>External Access Enable pin.</li> <li>A low level at this pin during and after Reset forces the XC164N to latch the configuration from PORT0 and pin RD, and to begin instruction execution out of external memory.</li> <li>A high level forces the XC164N to latch the configuration from pins RD, ALE, and WR, and to begin instruction execution out of the internal program memory. "ROMless" versions must have this pin tied to '0'.</li> </ul> |

| P20.12  | 2           | 0              | RSTOUT                                   | Internal Reset Indication Output.<br><b>Is activated</b> asynchronously with an external<br>hardware reset. It may also be activated<br>(selectable) synchronously with an internal<br>software or watchdog reset.<br><b>Is deactivated</b> upon the execution of the EINIT<br>instruction, optionally at the end of reset, or at<br>any time (before EINIT) via user software.<br>20 pins may input configuration values (see EA).                            |

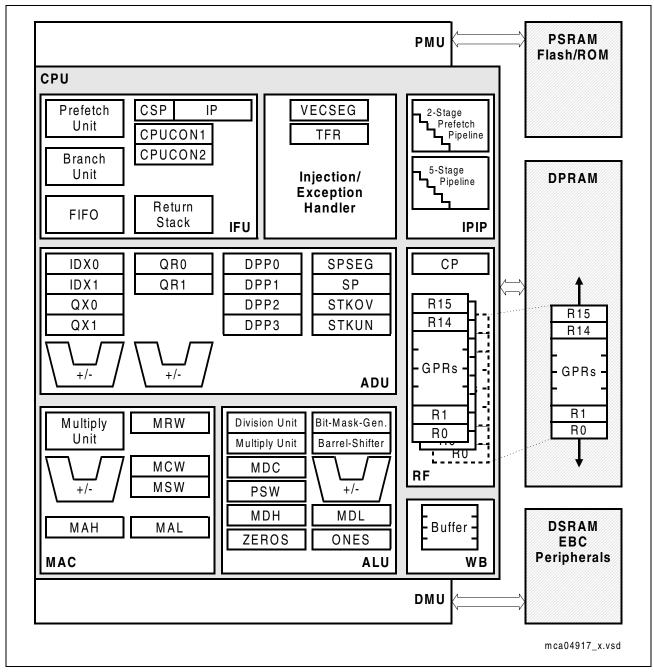

# 3.3 Central Processing Unit (CPU)

The main core of the CPU consists of a 5-stage execution pipeline with a 2-stage instruction-fetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply and divide unit, a bit-mask generator, and a barrel shifter.

## Figure 4 CPU Block Diagram

Based on these hardware provisions, most of the XC164N's instructions can be executed in just one machine cycle which requires 25 ns at 40 MHz CPU clock. For

example, shift and rotate instructions are always processed during one machine cycle independent of the number of bits to be shifted. Also multiplication and most MAC instructions execute in one single cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast as well: for example, a division algorithm is performed in 18 to 21 CPU cycles, depending on the data and division type. Four cycles are always visible, the rest runs in the background. Another pipeline optimization, the branch target prediction, allows eliminating the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 wordwide GPRs each at its disposal. The global register bank is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active global register bank to be accessed by the CPU at any time. The number of register banks is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided as a storage for temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area), and it is accessed by the CPU via the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared against the stack pointer value upon each stack access for the detection of a stack overflow or underflow.

The high performance offered by the hardware implementation of the CPU can efficiently be utilized by a programmer via the highly efficient XC164N instruction set which includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

# Table 4XC164N Interrupt Nodes

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM Register 0                             | CC1_CC0IC           | xx'0040 <sub>H</sub>             | 10 <sub>H</sub> / 16 <sub>D</sub> |

| CAPCOM Register 1                             | CC1_CC1IC           | xx'0044 <sub>H</sub>             | 11 <sub>H</sub> / 17 <sub>D</sub> |

| CAPCOM Register 2                             | CC1_CC2IC           | xx'0048 <sub>H</sub>             | 12 <sub>H</sub> / 18 <sub>D</sub> |

| CAPCOM Register 3                             | CC1_CC3IC           | xx'004C <sub>H</sub>             | 13 <sub>H</sub> / 19 <sub>D</sub> |

| CAPCOM Register 4                             | CC1_CC4IC           | xx'0050 <sub>H</sub>             | 14 <sub>H</sub> / 20 <sub>D</sub> |

| CAPCOM Register 5                             | CC1_CC5IC           | xx'0054 <sub>H</sub>             | 15 <sub>H</sub> / 21 <sub>D</sub> |

| CAPCOM Register 6                             | CC1_CC6IC           | xx'0058 <sub>H</sub>             | 16 <sub>H</sub> / 22 <sub>D</sub> |

| CAPCOM Register 7                             | CC1_CC7IC           | xx'005C <sub>H</sub>             | 17 <sub>H</sub> / 23 <sub>D</sub> |

| CAPCOM Register 8                             | CC1_CC8IC           | xx'0060 <sub>H</sub>             | 18 <sub>H</sub> / 24 <sub>D</sub> |

| CAPCOM Register 9                             | CC1_CC9IC           | xx'0064 <sub>H</sub>             | 19 <sub>H</sub> / 25 <sub>D</sub> |

| CAPCOM Register 10                            | CC1_CC10IC          | xx'0068 <sub>H</sub>             | 1A <sub>H</sub> / 26 <sub>D</sub> |

| CAPCOM Register 11                            | CC1_CC11IC          | xx'006C <sub>H</sub>             | 1B <sub>H</sub> / 27 <sub>D</sub> |

| CAPCOM Register 12                            | CC1_CC12IC          | xx'0070 <sub>H</sub>             | 1C <sub>H</sub> / 28 <sub>D</sub> |

| CAPCOM Register 13                            | CC1_CC13IC          | xx'0074 <sub>H</sub>             | 1D <sub>H</sub> / 29 <sub>D</sub> |

| CAPCOM Register 14                            | CC1_CC14IC          | xx'0078 <sub>H</sub>             | 1E <sub>H</sub> / 30 <sub>D</sub> |

| CAPCOM Register 15                            | CC1_CC15IC          | xx'007C <sub>H</sub>             | 1F <sub>H</sub> / 31 <sub>D</sub> |

| CAPCOM Register 16                            | CC2_CC16IC          | xx'00C0 <sub>H</sub>             | 30 <sub>H</sub> / 48 <sub>D</sub> |

| CAPCOM Register 17                            | CC2_CC17IC          | xx'00C4 <sub>H</sub>             | 31 <sub>H</sub> / 49 <sub>D</sub> |

| CAPCOM Register 18                            | CC2_CC18IC          | xx'00C8 <sub>H</sub>             | 32 <sub>H</sub> / 50 <sub>D</sub> |

| CAPCOM Register 19                            | CC2_CC19IC          | xx'00CC <sub>H</sub>             | 33 <sub>H</sub> / 51 <sub>D</sub> |

| CAPCOM Register 20                            | CC2_CC20IC          | xx'00D0 <sub>H</sub>             | 34 <sub>H</sub> / 52 <sub>D</sub> |

| CAPCOM Register 21                            | CC2_CC21IC          | xx'00D4 <sub>H</sub>             | 35 <sub>H</sub> / 53 <sub>D</sub> |

| CAPCOM Register 22                            | CC2_CC22IC          | xx'00D8 <sub>H</sub>             | 36 <sub>H</sub> / 54 <sub>D</sub> |

| CAPCOM Register 23                            | CC2_CC23IC          | xx'00DC <sub>H</sub>             | 37 <sub>H</sub> / 55 <sub>D</sub> |

| CAPCOM Register 24                            | CC2_CC24IC          | xx'00E0 <sub>H</sub>             | 38 <sub>H</sub> / 56 <sub>D</sub> |

| CAPCOM Register 25                            | CC2_CC25IC          | xx'00E4 <sub>H</sub>             | 39 <sub>H</sub> / 57 <sub>D</sub> |

| CAPCOM Register 26                            | CC2_CC26IC          | xx'00E8 <sub>H</sub>             | 3A <sub>H</sub> / 58 <sub>D</sub> |

| CAPCOM Register 27                            | CC2_CC27IC          | xx'00EC <sub>H</sub>             | 3B <sub>H</sub> / 59 <sub>D</sub> |

| CAPCOM Register 28                            | CC2_CC28IC          | xx'00F0 <sub>H</sub>             | 3C <sub>H</sub> / 60 <sub>D</sub> |

# Table 4XC164N Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM Register 29                            | CC2_CC29IC          | xx'0110 <sub>H</sub>             | 44 <sub>H</sub> / 68 <sub>D</sub> |

| CAPCOM Register 30                            | CC2_CC30IC          | xx'0114 <sub>H</sub>             | 45 <sub>H</sub> / 69 <sub>D</sub> |

| CAPCOM Register 31                            | CC2_CC31IC          | xx'0118 <sub>H</sub>             | 46 <sub>H</sub> / 70 <sub>D</sub> |

| CAPCOM Timer 0                                | CC1_T0IC            | xx'0080 <sub>H</sub>             | 20 <sub>H</sub> / 32 <sub>D</sub> |

| CAPCOM Timer 1                                | CC1_T1IC            | xx'0084 <sub>H</sub>             | 21 <sub>H</sub> / 33 <sub>D</sub> |

| CAPCOM Timer 7                                | CC2_T7IC            | xx'00F4 <sub>H</sub>             | 3D <sub>H</sub> / 61 <sub>D</sub> |

| CAPCOM Timer 8                                | CC2_T8IC            | xx'00F8 <sub>H</sub>             | 3E <sub>H</sub> / 62 <sub>D</sub> |

| GPT1 Timer 2                                  | GPT12E_T2IC         | xx'0088 <sub>H</sub>             | 22 <sub>H</sub> / 34 <sub>D</sub> |

| GPT1 Timer 3                                  | GPT12E_T3IC         | xx'008C <sub>H</sub>             | 23 <sub>H</sub> / 35 <sub>D</sub> |

| GPT1 Timer 4                                  | GPT12E_T4IC         | xx'0090 <sub>H</sub>             | 24 <sub>H</sub> / 36 <sub>D</sub> |

| GPT2 Timer 5                                  | GPT12E_T5IC         | xx'0094 <sub>H</sub>             | 25 <sub>H</sub> / 37 <sub>D</sub> |

| GPT2 Timer 6                                  | GPT12E_T6IC         | xx'0098 <sub>H</sub>             | 26 <sub>H</sub> / 38 <sub>D</sub> |

| GPT2 CAPREL Register                          | GPT12E_CRIC         | xx'009C <sub>H</sub>             | 27 <sub>H</sub> / 39 <sub>D</sub> |

| Unassigned node                               | -                   | xx'00A0 <sub>H</sub>             | 28 <sub>H</sub> / 40 <sub>D</sub> |

| Unassigned node                               | -                   | xx'00A4 <sub>H</sub>             | 29 <sub>H</sub> / 41 <sub>D</sub> |

| ASC0 Transmit                                 | ASC0_TIC            | xx'00A8 <sub>H</sub>             | 2A <sub>H</sub> / 42 <sub>D</sub> |

| ASC0 Transmit Buffer                          | ASC0_TBIC           | xx'011C <sub>H</sub>             | 47 <sub>H</sub> / 71 <sub>D</sub> |

| ASC0 Receive                                  | ASC0_RIC            | xx'00AC <sub>H</sub>             | 2B <sub>H</sub> / 43 <sub>D</sub> |

| ASC0 Error                                    | ASC0_EIC            | xx'00B0 <sub>H</sub>             | 2C <sub>H</sub> / 44 <sub>D</sub> |

| ASC0 Autobaud                                 | ASC0_ABIC           | xx'017C <sub>H</sub>             | 5F <sub>H</sub> / 95 <sub>D</sub> |

| SSC0 Transmit                                 | SSC0_TIC            | xx'00B4 <sub>H</sub>             | 2D <sub>H</sub> / 45 <sub>D</sub> |

| SSC0 Receive                                  | SSC0_RIC            | xx'00B8 <sub>H</sub>             | 2E <sub>H</sub> / 46 <sub>D</sub> |

| SSC0 Error                                    | SSC0_EIC            | xx'00BC <sub>H</sub>             | 2F <sub>H</sub> / 47 <sub>D</sub> |

| PLL/OWD                                       | PLLIC               | xx'010C <sub>H</sub>             | 43 <sub>H</sub> / 67 <sub>D</sub> |

| ASC1 Transmit                                 | ASC1_TIC            | xx'0120 <sub>H</sub>             | 48 <sub>H</sub> / 72 <sub>D</sub> |

| ASC1 Transmit Buffer                          | ASC1_TBIC           | xx'0178 <sub>H</sub>             | 5E <sub>H</sub> / 94 <sub>D</sub> |

| ASC1 Receive                                  | ASC1_RIC            | xx'0124 <sub>H</sub>             | 49 <sub>H</sub> / 73 <sub>D</sub> |

| ASC1 Error                                    | ASC1_EIC            | xx'0128 <sub>H</sub>             | 4A <sub>H</sub> / 74 <sub>D</sub> |

| ASC1 Autobaud                                 | ASC1_ABIC           | xx'0108 <sub>H</sub>             | 42 <sub>H</sub> / 66 <sub>D</sub> |

| End of PEC Subchannel                         | EOPIC               | xx'0130 <sub>H</sub>             | 4C <sub>H</sub> / 76 <sub>D</sub> |

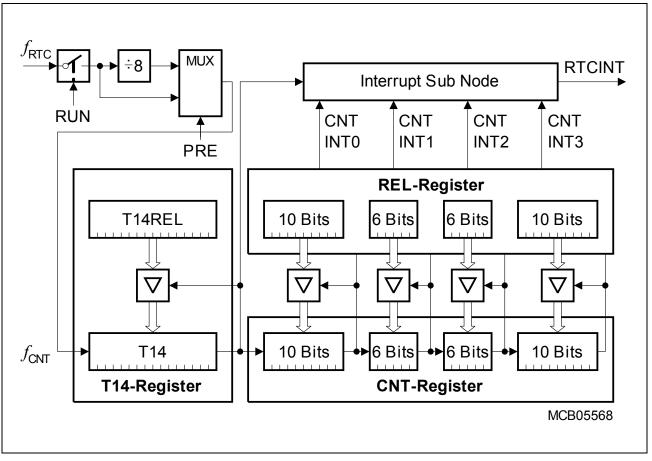

# 3.9 Real Time Clock

The Real Time Clock (RTC) module of the XC164N is directly clocked via a separate clock driver with the prescaled on-chip main oscillator frequency ( $f_{\text{RTC}} = f_{\text{OSCm}}/32$ ). It is therefore independent from the selected clock generation mode of the XC164N.

The RTC basically consists of a chain of divider blocks:

- a selectable 8:1 divider (on off)

- the reloadable 16-bit timer T14

- the 32-bit RTC timer block (accessible via registers RTCH and RTCL), made of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

### Figure 9 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to maintain the correct system time even when intermediate resets are executed.

The RTC module can be used for different purposes:

- System clock to determine the current time and date, optionally during idle mode, sleep mode, and power down mode.

- Cyclic time based interrupt, to provide a system time tick independent of CPU frequency and other resources, e.g. to wake up regularly from idle mode.

- 48-bit timer for long term measurements (maximum timespan is >> 100 years).

- Alarm interrupt for wake-up on a defined time.

# 3.11 High Speed Synchronous Serial Channels (SSC0/SSC1)

The High Speed Synchronous Serial Channels SSC0/SSC1 support full-duplex and halfduplex synchronous communication. It may be configured so it interfaces with serially linked peripheral components, full SPI functionality is supported.

A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling three separate interrupt vectors are provided.

The SSC transmits or receives characters of 2 ... 16 bits length synchronously to a shift clock which can be generated by the SSC (master mode) or by an external master (slave mode). The SSC can start shifting with the LSB or with the MSB and allows the selection of shifting and latching clock edges as well as the clock polarity.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. Transmit error and receive error supervise the correct handling of the data buffer. Phase error and baudrate error detect incorrect serial data.

# Summary of Features

- Master or Slave mode operation

- Full-duplex or Half-duplex transfers

- Baudrate generation from 20 Mbit/s to 305.18 bit/s (@ 40 MHz)

- Flexible data format

- Programmable number of data bits: 2 to 16 bits

- Programmable shift direction: LSB-first or MSB-first

- Programmable clock polarity: idle low or idle high

- Programmable clock/data phase: data shift with leading or trailing clock edge

- Loop back option available for testing purposes

- Interrupt generation on transmitter buffer empty condition, receive buffer full condition, error condition (receive, phase, baudrate, transmit error)

- Three pin interface with flexible SSC pin configuration

| Table 8 Inst | ruction Set Summary (cont'd)                                                             |       |

|--------------|------------------------------------------------------------------------------------------|-------|

| Mnemonic     | Description                                                                              | Bytes |

| ROL/ROR      | Rotate left/right direct word GPR                                                        | 2     |

| ASHR         | Arithmetic (sign bit) shift right direct word GPR                                        | 2     |

| MOV(B)       | Move word (byte) data                                                                    | 2/4   |

| MOVBS/Z      | Move byte operand to word op. with sign/zero extension                                   | 2/4   |

| JMPA/I/R     | Jump absolute/indirect/relative if condition is met                                      | 4     |

| JMPS         | Jump absolute to a code segment                                                          | 4     |

| JB(C)        | Jump relative if direct bit is set (and clear bit)                                       | 4     |

| JNB(S)       | Jump relative if direct bit is not set (and set bit)                                     | 4     |

| CALLA/I/R    | Call absolute/indirect/relative subroutine if condition is met                           | 4     |

| CALLS        | Call absolute subroutine in any code segment                                             | 4     |

| PCALL        | Push direct word register onto system stack and call absolute subroutine                 | 4     |

| TRAP         | Call interrupt service routine via immediate trap number                                 | 2     |

| PUSH/POP     | Push/pop direct word register onto/from system stack                                     | 2     |

| SCXT         | Push direct word register onto system stack and update register with word operand        | 4     |

| RET(P)       | Return from intra-segment subroutine<br>(and pop direct word register from system stack) | 2     |

| RETS         | Return from inter-segment subroutine                                                     | 2     |

| RETI         | Return from interrupt service subroutine                                                 | 2     |

| SBRK         | Software Break                                                                           | 2     |

| SRST         | Software Reset                                                                           | 4     |

| IDLE         | Enter Idle Mode                                                                          | 4     |

| PWRDN        | Enter Power Down Mode (supposes NMI-pin being low)                                       | 4     |

| SRVWDT       | Service Watchdog Timer                                                                   | 4     |

| DISWDT/ENWDT | Disable/Enable Watchdog Timer                                                            | 4     |

| EINIT        | End-of-Initialization Register Lock                                                      | 4     |

| ATOMIC       | Begin ATOMIC sequence                                                                    | 2     |

| EXTR         | Begin EXTended Register sequence                                                         | 2     |

| EXTP(R)      | Begin EXTended Page (and Register) sequence                                              | 2/4   |

| EXTS(R)      | Begin EXTended Segment (and Register) sequence                                           | 2/4   |

| Table 8Instruction Set Summary (cont'd) |                                     |       |  |  |  |

|-----------------------------------------|-------------------------------------|-------|--|--|--|

| Mnemonic                                | Description                         | Bytes |  |  |  |

| NOP                                     | Null operation                      | 2     |  |  |  |

| CoMUL/CoMAC                             | Multiply (and accumulate)           | 4     |  |  |  |

| CoADD/CoSUB                             | Add/Subtract                        | 4     |  |  |  |

| Co(A)SHR                                | (Arithmetic) Shift right            | 4     |  |  |  |

| CoSHL                                   | Shift left                          | 4     |  |  |  |

| CoLOAD/STORE                            | Load accumulator/Store MAC register | 4     |  |  |  |

| CoCMP                                   | Compare                             | 4     |  |  |  |

| CoMAX/MIN                               | Maximum/Minimum                     | 4     |  |  |  |

| CoABS/CoRND                             | Absolute value/Round accumulator    | 4     |  |  |  |

| CoMOV                                   | Data move                           | 4     |  |  |  |

| CoNEG/NOP                               | Negate accumulator/Null operation   | 4     |  |  |  |

## **Operating Conditions**

The following operating conditions must not be exceeded to ensure correct operation of the XC164N. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

| Parameter                                 | Symbol              | Limit | Values                 | Unit | Notes                                            |

|-------------------------------------------|---------------------|-------|------------------------|------|--------------------------------------------------|

|                                           |                     | Min.  | Max.                   |      |                                                  |

| Digital supply voltage for the core       | V <sub>DDI</sub>    | 2.35  | 2.7                    | V    | Active mode,<br>$f_{CPU} = f_{CPUmax}^{1)(2)}$   |

| Digital supply voltage for<br>IO pads     | V <sub>DDP</sub>    | 4.4   | 5.5                    | V    | Active mode <sup>2)3)</sup>                      |

| Supply Voltage Difference                 | $\Delta V_{\rm DD}$ | -0.5  | -                      | V    | $V_{\rm DDP}$ - $V_{\rm DDI}^{4)}$               |

| Digital ground voltage                    | V <sub>SS</sub>     |       | 0                      | V    | Reference voltage                                |

| Overload current                          | I <sub>OV</sub>     | -5    | 5                      | mA   | Per IO pin <sup>5)6)</sup>                       |

|                                           |                     | -2    | 5                      | mA   | Per Port 5 input pin <sup>5)6)</sup>             |

| Overload current coupling                 | K <sub>OVA</sub>    | -     | 1.0 × 10 <sup>-4</sup> | _    | <i>I</i> <sub>OV</sub> > 0                       |

| factor for Port 5 inputs <sup>7)</sup>    |                     | -     | 1.5 × 10 <sup>-3</sup> | _    | <i>I</i> <sub>OV</sub> < 0                       |

| Overload current coupling                 | K <sub>OVD</sub>    | -     | 5.0 × 10 <sup>-3</sup> | _    | <i>I</i> <sub>OV</sub> > 0                       |

| factor for digital I/O pins <sup>7)</sup> |                     | _     | 1.0 × 10 <sup>-2</sup> | _    | I <sub>OV</sub> < 0                              |

| Absolute sum of overload currents         | $\Sigma  I_{OV} $   | _     | 50                     | mA   | 6)                                               |

| External Load<br>Capacitance              | CL                  | _     | 50                     | pF   | Pin drivers in <b>default</b> mode <sup>8)</sup> |

| Ambient temperature                       | T <sub>A</sub>      | -     | -                      | °C   | see Table 1                                      |

## Table 10 Operating Condition Parameters

1)  $f_{CPUmax}$  = 40 MHz for devices marked ... 40F,  $f_{CPUmax}$  = 20 MHz for devices marked ... 20F.

2) External circuitry must guarantee low-level at the RSTIN pin at least until both power supply voltages have reached the operating range.

- 3) The specified voltage range is allowed for operation. The range limits may be reached under extreme operating conditions. However, specified parameters, such as leakage currents, refer to the standard operating voltage range of  $V_{\text{DDP}}$  = 4.75 V to 5.25 V.

- 4) This limitation must be fulfilled under all operating conditions including power-ramp-up, power-ramp-down, and power-save modes.

5) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range:  $V_{OV} > V_{DDP} + 0.5 \vee (I_{OV} > 0)$  or  $V_{OV} < V_{SS} - 0.5 \vee (I_{OV} < 0)$ . The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltages must remain within the specified limits.

Proper operation is not guaranteed if overload conditions occur on functional pins such as XTAL1,  $\overline{RD}$ ,  $\overline{WR}$ , etc.

- 6) Not subject to production test verified by design/characterization.

- 7) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it.

The total current through a pin is  $|I_{TOT}| = |I_{OZ}| + (|I_{OV}| \times K_{OV})$ .

8) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability ( $C_L$ ).

## Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the XC164N and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the XC164N will provide signals with the respective characteristics.

### **SR** (System Requirement):

The external system must provide signals with the respective characteristics to the XC164N.

| Table 11 | DC Characteristics ( | Operating | Conditions | apply) <sup>1)</sup> | (cont'd) |

|----------|----------------------|-----------|------------|----------------------|----------|

|----------|----------------------|-----------|------------|----------------------|----------|

| Parameter                                                  | Symbol                          |    | Limit Values |      | Unit | <b>Test Condition</b>               |  |

|------------------------------------------------------------|---------------------------------|----|--------------|------|------|-------------------------------------|--|

|                                                            |                                 |    | Min.         | Max. |      |                                     |  |

| Level inactive hold current <sup>13)</sup>                 | I <sub>LHI</sub> <sup>10)</sup> |    | -            | -10  | μA   | $V_{\rm OUT}$ = 0.5 × $V_{\rm DDP}$ |  |

| Level active hold current <sup>13)</sup>                   | $I_{\rm LHA}^{11)}$             |    | -100         | -    | μA   | V <sub>OUT</sub> = 0.45 V           |  |

| XTAL1 input current                                        | I <sub>IL</sub>                 | CC | _            | ±20  | μA   | $0 V < V_{IN} < V_{DDI}$            |  |

| Pin capacitance <sup>14)</sup><br>(digital inputs/outputs) | C <sub>IO</sub>                 | CC | -            | 10   | pF   | -                                   |  |

1) Keeping signal levels within the limits specified in this table, ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

2) If XTAL1 is driven by a crystal, reaching an amplitude (peak to peak) of  $0.4 \times V_{DDI}$  is sufficient.

3) This parameter is tested for P3, P4, P9.

4) The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 12, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

- 5) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are guaranteed.

- 6) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- 7) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- 8) The driver of P3.15 is designed for faster switching, because this pin can deliver the reference clock for the bus interface (CLKOUT). The maximum leakage current for P3.15 is, therefore, increased to 1  $\mu$ A.

- 9) This specification is valid during Reset for configuration on RD, WR, EA, PORTO

- 10) The maximum current may be drawn while the respective signal line remains inactive.

- 11) The minimum current must be drawn to drive the respective signal line active.

- 12) This specification is valid during Reset for configuration on ALE.

- 13) This specification is valid during Reset for pins P4.3-0, which can act as  $\overline{CS}$  outputs, and for P3.12.

- 14) Not subject to production test verified by design/characterization.

| Port Output Driver<br>Mode | Maximum Output Current $(I_{OLmax}, -I_{OHmax})^{1}$ | Nominal Output Current<br>( <i>I</i> <sub>OLnom</sub> , - <i>I</i> <sub>OHnom</sub> ) |

|----------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|

| Strong driver              | 10 mA                                                | 2.5 mA                                                                                |

| Medium driver              | 4.0 mA                                               | 1.0 mA                                                                                |

| Weak driver                | 0.5 mA                                               | 0.1 mA                                                                                |

#### Table 12 Current Limits for Port Output Drivers

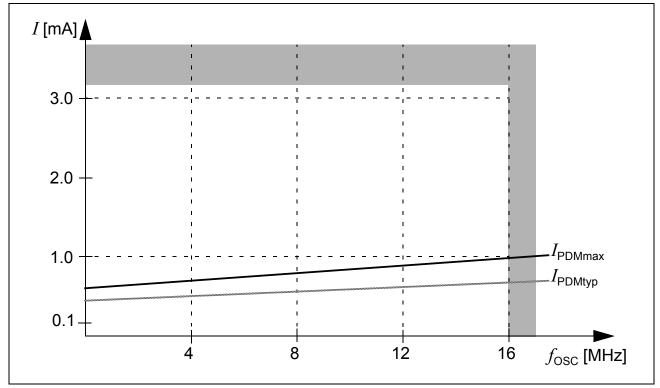

Figure 11 Sleep and Power Down Supply Current due to RTC and Oscillator Running, as a Function of Oscillator Frequency

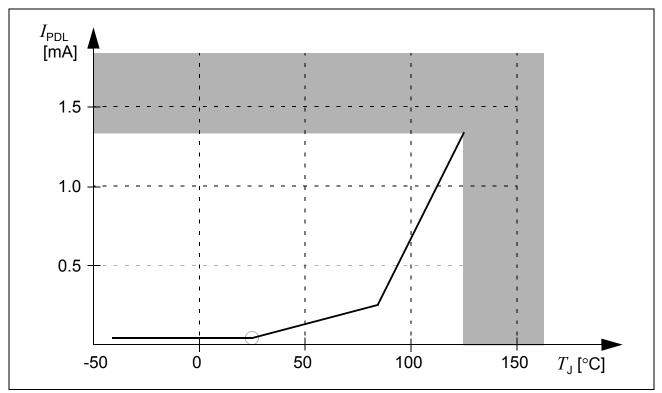

Figure 12 Sleep and Power Down Leakage Supply Current as a Function of Temperature

CPU and EBC are clocked with the CPU clock signal  $f_{CPU}$ . The CPU clock can have the same frequency as the master clock ( $f_{CPU} = f_{MC}$ ) or can be the master clock divided by two:  $f_{CPU} = f_{MC}$  / 2. This factor is selected by bit CPSYS in register SYSCON1.

The specification of the external timing (AC Characteristics) depends on the period of the CPU clock, called "TCP".

The other peripherals are supplied with the system clock signal  $f_{SYS}$  which has the same frequency as the CPU clock signal  $f_{CPU}$ .

## **Bypass Operation**

When bypass operation is configured (PLLCTRL =  $0x_B$ ) the master clock is derived from the internal oscillator (input clock signal XTAL1) through the input- and output-prescalers:

$f_{MC} = f_{OSC} / ((PLLIDIV+1) \times (PLLODIV+1)).$

If both divider factors are selected as '1' (PLLIDIV = PLLODIV = '0') the frequency of  $f_{MC}$  directly follows the frequency of  $f_{OSC}$  so the high and low time of  $f_{MC}$  is defined by the duty cycle of the input clock  $f_{OSC}$ .

The lowest master clock frequency is achieved by selecting the maximum values for both divider factors:

$f_{\rm MC} = f_{\rm OSC} / ((3 + 1) \times (14 + 1)) = f_{\rm OSC} / 60.$

## Phase Locked Loop (PLL)

When PLL operation is configured (PLLCTRL =  $11_B$ ) the on-chip phase locked loop is enabled and provides the master clock. The PLL multiplies the input frequency by the factor **F** ( $f_{MC} = f_{OSC} \times F$ ) which results from the input divider, the multiplication factor, and the output divider (**F** = PLLMUL+1 / (PLLIDIV+1 × PLLODIV+1)). The PLL circuit synchronizes the master clock to the input clock. This synchronization is done smoothly, i.e. the master clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{\rm MC}$  is constantly adjusted so it is locked to  $f_{\rm OSC}$ . The slight variation causes a jitter of  $f_{\rm MC}$  which also affects the duration of individual TCMs.

The timing listed in the AC Characteristics refers to TCPs. Because  $f_{\rm CPU}$  is derived from  $f_{\rm MC}$ , the timing must be calculated using the minimum TCP possible under the respective circumstances.

The actual minimum value for TCP depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency so it corresponds to the applied input frequency (crystal or oscillator) the relative deviation for periods of more than one TCP is lower than for one single TCP (see formula and Figure 14).

This is especially important for bus cycles using waitstates and e.g. for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train

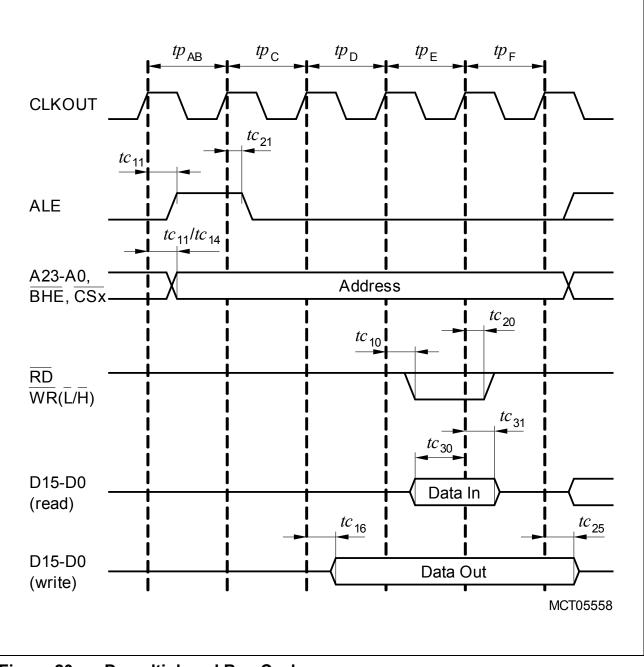

# 4.3.5 External Bus Timing

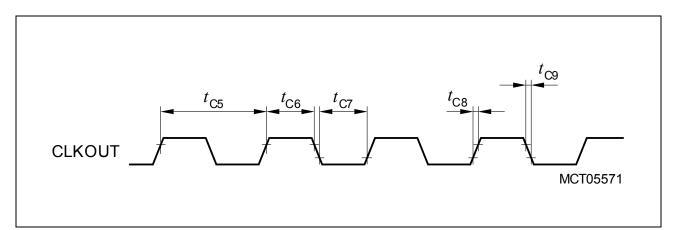

# Table 18CLKOUT Reference Signal

| Parameter         | Syml                   | bol | Lin                    | Unit |    |

|-------------------|------------------------|-----|------------------------|------|----|

|                   |                        |     | Min.                   | Max. |    |

| CLKOUT cycle time | tc <sub>5</sub>        | CC  | 40/30/25 <sup>1)</sup> |      | ns |

| CLKOUT high time  | tc <sub>6</sub>        | CC  | 8                      | _    | ns |

| CLKOUT low time   | <i>tc</i> <sub>7</sub> | CC  | 6                      | _    | ns |

| CLKOUT rise time  | tc <sub>8</sub>        | CC  | _                      | 4    | ns |

| CLKOUT fall time  | tc <sub>9</sub>        | CC  | _                      | 4    | ns |

1) The CLKOUT cycle time is influenced by the PLL jitter (given values apply to  $f_{CPU}$  = 25/33/40 MHz). For longer periods the relative deviation decreases (see PLL deviation formula).

Figure 18 CLKOUT Signal Timing

Figure 20 Demultiplexed Bus Cycle

## Package and Reliability

# 5.2 Flash Memory Parameters

The data retention time of the XC164N's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

# Table 22Flash Parameters (XC164N, 256 Kbytes)

| Parameter             | Symbol           | Limit Values         |      | I Limit Values |                                      | mbol Limit Values |  | Unit | Notes |

|-----------------------|------------------|----------------------|------|----------------|--------------------------------------|-------------------|--|------|-------|

|                       |                  | Min.                 | Max. |                |                                      |                   |  |      |       |

| Data retention time   | t <sub>RET</sub> | 15                   | -    | years          | 10 <sup>3</sup> erase/program cycles |                   |  |      |       |

| Flash Erase Endurance | $N_{ER}$         | 20 × 10 <sup>3</sup> | _    | cycles         | data retention time<br>5 years       |                   |  |      |       |