Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorMSP430 CPUXV2Core Size16-BitSpeed25MHzConnectivityPC, IrDA, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, POR, PWM, WDTNumber of I/O37Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-Nutage - Supply (Vcc/Vdd)18V ~ 3.6VVoltage - Supply (Vcc/Vdd)18V ~ 3.6VOperating Temperature-Qoerating Temperature40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)Purchase UBLInter://www.exfl.com/product-detail/texas-instruments/msp430f5244irgzt |                            |                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------|

| Core Size16-BitSpeed25MHzConnectivityPC, IrDA, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, POR, PWM, WDTNumber of I/O37Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadNome Merce Package48-VFQFN (x77)                                                                                                                               | Product Status             | Active                                                                  |

| Speed25MHzConnectivityI°C, IrDA, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, POR, PWM, WDTNumber of I/O37Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VFQFN (7x7)                                                                                                                                        | Core Processor             | MSP430 CPUXV2                                                           |

| ConnectivityIPC, IrDA, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, POR, PWM, WDTNumber of I/O37Program Memory Size128KB (128K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K × 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VoFN (7x7)                                                                                                                                                                          | Core Size                  | 16-Bit                                                                  |

| PeripheralsBrown-out Detect/Reset, DMA, POR, PWM, WDTNumber of I/O37Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type84-VEQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                    | Speed                      | 25MHz                                                                   |

| Number of I/O37Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                                              | Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                                                             | Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                                                                                                | Number of I/O              | 37                                                                      |

| EEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                        | Program Memory Size        | 128KB (128K x 8)                                                        |

| RAM Size8K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                    | Program Memory Type        | FLASH                                                                   |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                  | EEPROM Size                | <u>.</u>                                                                |

| Data ConvertersA/D 10x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                                                       | RAM Size                   | 8K x 8                                                                  |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-VFQFN Exposed PadSupplier Device Package48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                | Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     48-VFQFN Exposed Pad       Supplier Device Package     48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                                                              | Data Converters            | A/D 10x10b                                                              |

| Mounting Type     Surface Mount       Package / Case     48-VFQFN Exposed Pad       Supplier Device Package     48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                | Oscillator Type            | Internal                                                                |

| Package / Case     48-VFQFN Exposed Pad       Supplier Device Package     48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Supplier Device Package     48-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mounting Type              | Surface Mount                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Package / Case             | 48-VFQFN Exposed Pad                                                    |

| Purchase URL https://www.e-xfl.com/product-detail/texas-instruments/msp430f5244irgzt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Supplier Device Package    | 48-VQFN (7x7)                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Purchase URL               | https://www.e-xfl.com/product-detail/texas-instruments/msp430f5244irgzt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

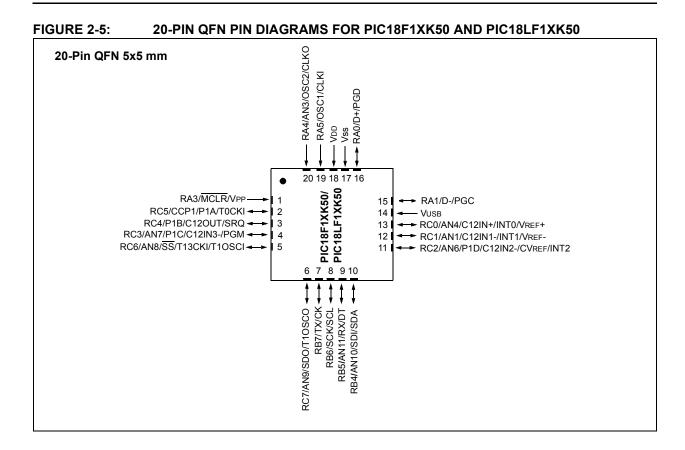

#### 2.1.1 LOW-VOLTAGE ICSP PROGRAMMING

In Low-Voltage ICSP mode, the PIC18F1XK50/ PIC18LF1XK50 devices can be programmed using a single VDD source in the operating range. The MCLR/ VPP/RA3 does not have to be brought to a different voltage, but can instead be left at the normal operating voltage. Refer to Section 8.1 "AC/DC Characteristics Timing Requirements for Program/Verify Test Mode" for additional hardware parameters.

#### 2.1.1.1 Single-Supply ICSP Programming

The LVP bit in Configuration register, CONFIG4L, enables single-supply (low-voltage) ICSP programming. The LVP bit defaults to a '1' (enabled) from the factory.

If Single-Supply Programming mode is not used, the LVP bit can be programmed to a '0' and RC3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed by entering the High-Voltage ICSP mode, where MCLR/VPP/RA3 is raised to VIHH. Once the LVP bit is programmed to a '0', only the High-Voltage ICSP mode is available and only the High-Voltage ICSP mode can be used to program the device.

- Note 1: The High-Voltage ICSP mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR/ VPP/RA3 pin.

- 2: While in Low-Voltage ICSP mode, the RC3 pin can no longer be used as a general purpose I/O.

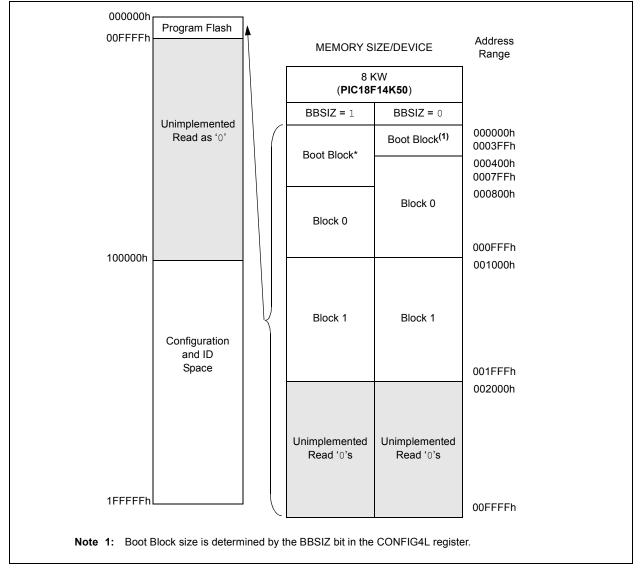

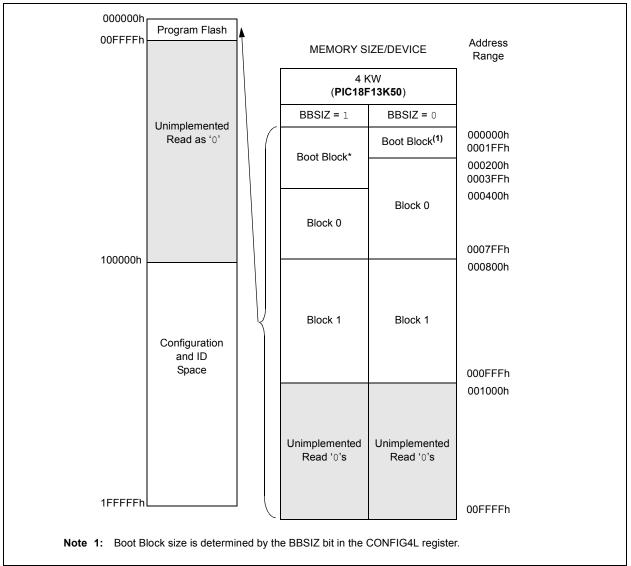

### 3.0 MEMORY MAPS

For the PIC18F14K50/PIC18LF14K50 device, the program Flash space extends from 0000h to 03FFFh (16 Kbytes) in two 8-Kbyte blocks. For the PIC18F13K50/PIC18LF13K50 device, the program Flash space extends from 0000h to 01FFFh (8 Kbytes) in two 4-Kbyte blocks.

For the PIC18F14K50/PIC18LF14K50 addresses 0000h through 0FFFh, however, define a "Boot Block" region that is treated separately from Block 0. For the PIC18F13K50/PIC18LF13K50 addresses 0000h through 07FFh, define the "Boot Block" region. All of these blocks define code protection boundaries within the program Flash space. The size of the Boot Block in the PIC18F14K50/PIC18LF14K50 devices can be configured as 2K, or 4 Kbyte (see Figure 3-1). The size of the Boot Block in the PIC18F13K50/PIC18LF13K50 devices can be configured as 1K, or 2 Kbytes, as illustrated in Figure 3-1. This is done through the BBSIZ bit in the Configuration register, CONFIG4L. It is important to note that increasing the size of the Boot Block decreases the size of the Block 0.

#### TABLE 3-1: IMPLEMENTATION OF PROGRAM FLASH

| Device                       | Program Flash Size (Words) |  |  |

|------------------------------|----------------------------|--|--|

| PIC18F13K50/<br>PIC18LF13K50 | 000000h-000FFFh (4K)       |  |  |

| PIC18F14K50/<br>PIC18LF14K50 | 000000h-001FFFh (8K)       |  |  |

#### FIGURE 3-1: MEMORY MAP AND THE PROGRAM FLASH SPACE FOR PIC18F14K50/ PIC18LF14K50 DEVICES

#### FIGURE 3-2: MEMORY MAP AND THE PROGRAM FLASH SPACE FOR PIC18F13K50/ PIC18LF13K50 DEVICES

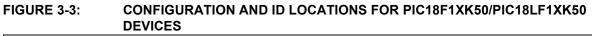

In addition to the program Flash space, there are three blocks in the Configuration and ID space that are accessible to the user through table reads and table writes. Their locations in the memory map are shown in Figure 3-3.

Users may store identification information (ID) in eight ID registers. These ID registers are mapped in addresses 200000h through 200007h. The ID locations read out normally, even after code protection is applied.

Locations 300000h through 30000Dh are reserved for the Configuration bits. These bits select various device options and are described in **Section 6.0 "Configuration Word**". These Configuration bits read out normally, even after code protection.

Locations 3FFFEh and 3FFFFh are reserved for the device ID bits. These bits may be used by the programmer to identify what device type is being programmed, and are described in **Section 6.0 "Configuration Word"**. These device ID bits read out normally, even after code protection.

### 3.1 Memory Address Pointer

Memory in the address space, 0000000h to 3FFFFh, is addressed via the Table Pointer register, which is comprised of three Pointer registers:

- TBLPTRU, at RAM address 0FF8h

- TBLPTRH, at RAM address 0FF7h

- TBLPTRL, at RAM address 0FF6h

| TBLPTRU     | TBLPTRH    | TBLPTRL   |

|-------------|------------|-----------|

| Addr[21:16] | Addr[15:8] | Addr[7:0] |

The 4-bit command, '0000' (core instruction), is used to load the Table Pointer prior to using any read or write operations.

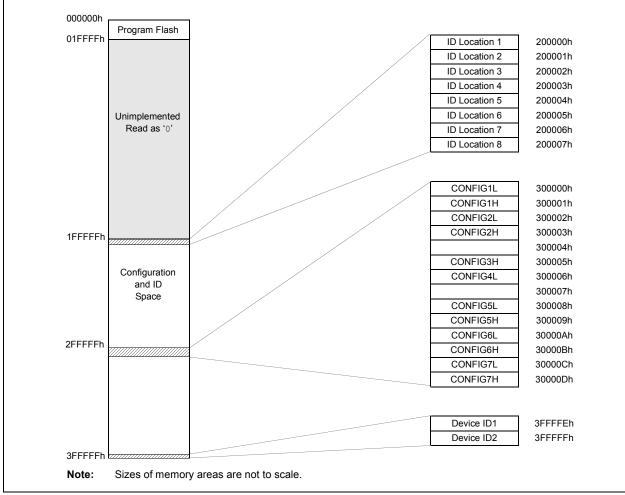

#### 3.2 High-Level Overview of the Programming Process

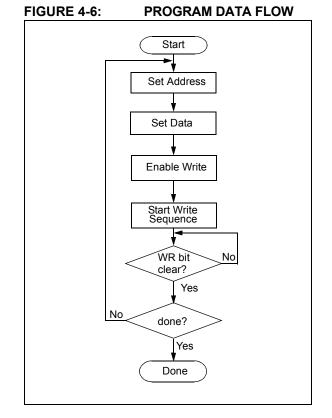

Figure 3-4 shows the high-level overview of the programming process. First, a Bulk Erase is performed. Next, the program Flash, ID locations and data EEPROM are programmed. These memories are then verified to ensure that programming was successful. If no errors are detected, the Configuration bits are then programmed and verified.

FIGURE 3-4: HIGH-LEVEL PROGRAMMING FLOW

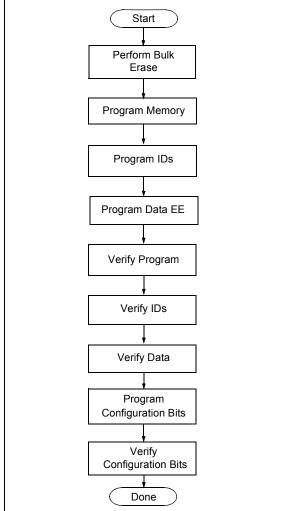

### 3.3 Entering and Exiting High-Voltage ICSP Program/Verify Mode

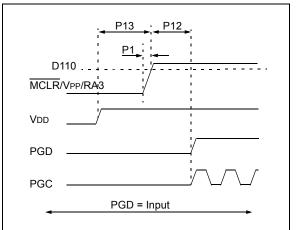

As shown in Figure 3-6, the High-Voltage ICSP Program/Verify mode is entered by holding PGC and PGD low and then raising MCLR/VPP/RA3 to VIHH (high voltage). Once in this mode, the program Flash, data EEPROM, ID locations and Configuration bits can be accessed and programmed in serial fashion. Figure 3-7 shows the exit sequence.

The sequence that enters the device into the Program/ Verify mode places all unused I/Os in the high-impedance state.

FIGURE 3-6:

VDD-FIRST PROGRAM/ VERIFY MODE ENTRY

#### 4.1.2 LOW-VOLTAGE ICSP BULK ERASE

When using low-voltage ICSP, the part must be supplied by the voltage specified in parameter D111 if a Bulk Erase is to be executed. All other Bulk Erase details, as described above, apply.

If it is determined that a program memory erase must be performed at a supply voltage below the Bulk Erase limit, refer to the erase methodology described in Section 4.1.3 "ICSP Row Erase" and Section 4.2.1 "Modifying Program Flash".

If it is determined that a data EEPROM erase must be performed at a supply voltage below the Bulk Erase limit, follow the methodology described in **Section 4.3** "**Data EEPROM Programming**" and write '1's to the array.

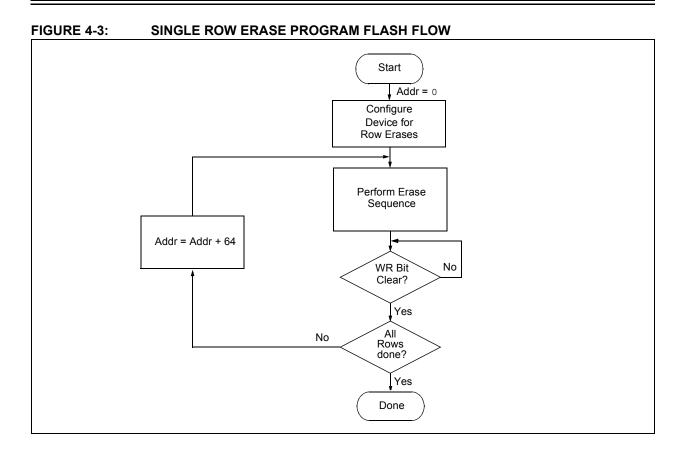

### 4.1.3 ICSP ROW ERASE

Regardless of whether high or low-voltage ICSP is used, it is possible to erase one row (64 bytes of data), provided the block is not code or write-protected. Rows are located at static boundaries, beginning at program memory address 000000h, extending to the internal program memory limit (see **Section 3.0 "Memory Maps"**).

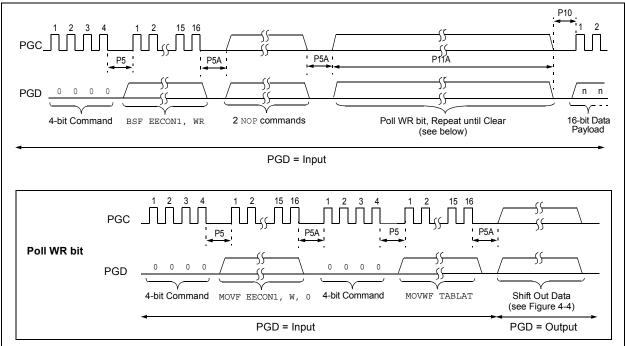

The Row Erase duration is self-timed. After the WR bit in EECON1 is set, two NOPs are issued. Erase starts upon the 4th PGC of the second NOP. It ends when the WR bit is cleared by hardware.

The code sequence to Row Erase a PIC18F1XK50/ PIC18LF1XK50 device is shown in Table 4-3. The flowchart shown in Figure 4-3 depicts the logic necessary to completely erase the PIC18F1XK50/PIC18LF1XK50 devices. The timing diagram for Row Erase is identical to the data EEPROM write timing, shown in Figure 4-7.

| Note 1: | The TBLPTR register can point at any    |  |  |  |  |

|---------|-----------------------------------------|--|--|--|--|

|         | byte within the row intended for erase. |  |  |  |  |

2: ICSP row erase of the User ID locations is also possible using the technique described in Section 4.1.3 "ICSP Row Erase". The address argument used should be 0x200000. A row erase of the User ID locations is required when VDD is below the Bulk Erase threshold.

| 4-bit<br>Command                         | Data Payload                                      | Core Instruction                                                                                   |  |  |  |  |

|------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Step 1: Direct a                         | ccess to program Fla                              | sh and enable writes.                                                                              |  |  |  |  |

| 0000<br>0000<br>0000<br>Step 2: Point to | 8E A6<br>9C A6<br>84 A6<br>first row in program F | BSF EECON1, EEPGD<br>BCF EECON1, CFGS<br>BSF EECON1, WREN<br>Flash.                                |  |  |  |  |

| 0000<br>0000<br>0000                     | 6A F8<br>6A F7<br>6A F6                           | CLRF TBLPTRU<br>CLRF TBLPTRH<br>CLRF TBLPTRL                                                       |  |  |  |  |

| Step 3: Enable e                         | erase and erase sing                              | e row.                                                                                             |  |  |  |  |

| 0000<br>0000<br>0000<br>0000             | 88 A6<br>82 A6<br>00 00<br>00 00                  | BSF EECON1, FREE<br>BSF EECON1, WR<br>NOP<br>NOP Erase starts on the 4th clock of this instruction |  |  |  |  |

| Step 4: Poll WR                          | bit. Repeat until bit is                          | s clear.                                                                                           |  |  |  |  |

| 0000<br>0000<br>0000<br>0010             | 50 A6<br>6E F5<br>00 00<br><msb><lsb></lsb></msb> | MOVF EECON1, W, 0<br>MOVWF TABLAT<br>NOP<br>Shift out data <sup>(1)</sup>                          |  |  |  |  |

| Step 5: Hold PG                          | Step 5: Hold PGC low for time P10.                |                                                                                                    |  |  |  |  |

| Step 6: Repeat                           | step 3 with Address F                             | Pointer incremented by 64 until all rows are erased.                                               |  |  |  |  |

| Step 7: Disable                          | writes.                                           |                                                                                                    |  |  |  |  |

| 0000                                     | 94 A6                                             | BCF EECON1, WREN                                                                                   |  |  |  |  |

#### TABLE 4-3: ERASE PROGRAM FLASH CODE SEQUENCE

Note 1: See Figure 5-4 for details on shift out data timing.

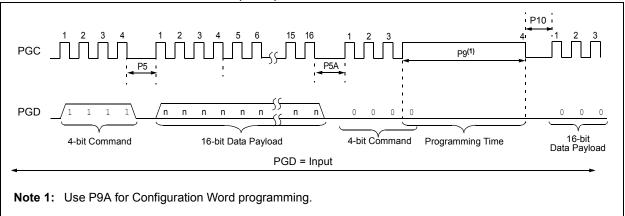

#### FIGURE 4-5: TABLE WRITE AND START PROGRAMMING INSTRUCTION TIMING DIAGRAM (1111)

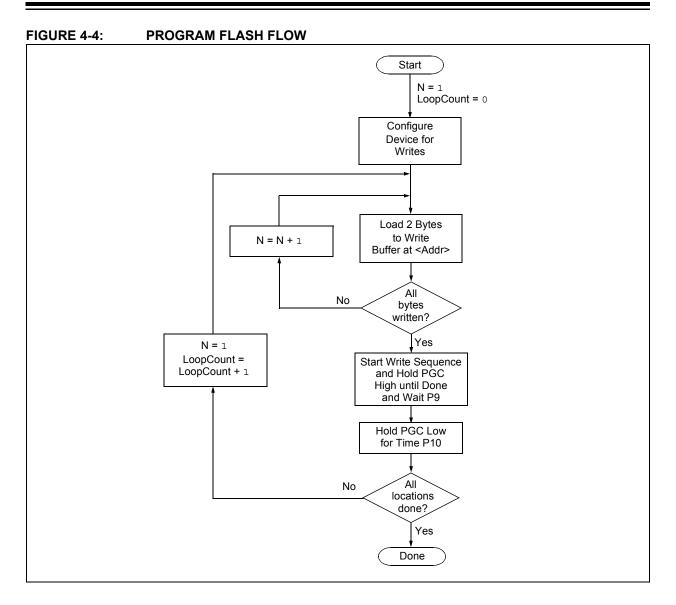

#### 4.2.1 MODIFYING PROGRAM FLASH

The previous programming example assumed that the device has been Bulk Erased prior to programming (see **Section 4.1.1 "High-Voltage ICSP Bulk Erase"**). It may be the case, however, that the user wishes to modify only a section of an already programmed device.

The appropriate number of bytes required for the erase buffer must be read out of program Flash (as described in **Section 5.2 "Verify Program Flash and ID Locations**") and buffered. Modifications can be made on this buffer. Then, the block of program Flash that was read out must be erased and rewritten with the modified data.

The WREN bit must be set if the WR bit in EECON1 is used to initiate a write sequence.

| 4-bit<br>Command                    | Data Payload                   | Core Instruction                                                                                                                                                               |

|-------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1: Direct acc                  | ess to program Flash.          | <u>.</u>                                                                                                                                                                       |

| 0000                                | 8E A6                          | BSF EECON1, EEPGD                                                                                                                                                              |

| 0000                                | 9C A6                          | BCF EECON1, CFGS                                                                                                                                                               |

| Step 2: Read prog                   | gram Flash into buffer (Sec    | tion 5.1 "Read Program Flash, ID Locations and Configuration Bits").                                                                                                           |

| Step 3: Set the Ta                  | ble Pointer for the block to   | be erased.                                                                                                                                                                     |

| 0000                                | 0E <addr[21:16]></addr[21:16]> | MOVLW <addr[21:16]></addr[21:16]>                                                                                                                                              |

| 0000                                | 6E F8                          | MOVWF TBLPTRU                                                                                                                                                                  |

| 0000                                | 0E <addr[8:15]></addr[8:15]>   | MOVLW <addr[8:15]></addr[8:15]>                                                                                                                                                |

| 0000                                | 6E F7                          | MOVWF TBLPTRH                                                                                                                                                                  |

| 0000                                | 0E <addr[7:0]></addr[7:0]>     | MOVLW <addr[7:0]></addr[7:0]>                                                                                                                                                  |

| 0000                                | 6E F6                          | MOVWF TBLPTRL                                                                                                                                                                  |

| Step 4: Enable me                   | emory writes and setup an      | erase.                                                                                                                                                                         |

| 0000                                | 84 A6                          | BSF EECON1, WREN                                                                                                                                                               |

| 0000                                | 88 A6                          | BSF EECON1, FREE                                                                                                                                                               |

| Step 5: Initiate era                | ase.                           |                                                                                                                                                                                |

| 0000                                | 88 A6                          | BSF EECON1, FREE                                                                                                                                                               |

| 0000                                | 82 A6                          | BSF EECON1, WR                                                                                                                                                                 |

| 0000                                | 00 00                          | NOP                                                                                                                                                                            |

| 0000                                | 00 00                          | NOP Erase starts on the 4th clock of this instruction                                                                                                                          |

| Step 6: Poll WR b                   | it. Repeat until bit is clear. |                                                                                                                                                                                |

| 0000                                | 50 A6                          | MOVF EECON1, W, O                                                                                                                                                              |

| 0000                                | 6E F5                          | MOVWF TABLAT                                                                                                                                                                   |

| 0000                                | 00 00                          | NOP                                                                                                                                                                            |

| 0000                                | <msb><lsb></lsb></msb>         | Shift out data <sup>(1)</sup>                                                                                                                                                  |

| Step 7: Load write                  | buffer. The correct bytes      | will be selected based on the Table Pointer.                                                                                                                                   |

| 0000                                | 0E <addr[21:16]></addr[21:16]> | MOVLW <addr[21:16]></addr[21:16]>                                                                                                                                              |

| 0000                                | 6E F8                          | MOVWF TBLPTRU                                                                                                                                                                  |

| 0000                                | 0E <addr[8:15]></addr[8:15]>   | MOVLW <addr[8:15]></addr[8:15]>                                                                                                                                                |

| 0000                                | 6E F7                          | MOVWF TBLPTRH                                                                                                                                                                  |

| 0000                                | 0E <addr[7:0]></addr[7:0]>     | MOVLW <addr[7:0]></addr[7:0]>                                                                                                                                                  |

| 0000                                | 6E F6                          | MOVWF TBLPTRL                                                                                                                                                                  |

| 1101                                | <msb><lsb></lsb></msb>         | Write 2 bytes and post-increment address by 2.                                                                                                                                 |

| •                                   | •                              |                                                                                                                                                                                |

| •                                   | •                              | Repeat as many times as necessary to fill the write buffer                                                                                                                     |

| •                                   | •                              | Write 2 bytes and start programming.                                                                                                                                           |

| 1111                                | <msb><lsb></lsb></msb>         | NOP - hold PGC high for time P9 and low for time P10.                                                                                                                          |

| 0000                                | 00 00                          |                                                                                                                                                                                |

| (see Table 4-4) at<br>erase buffer. | each iteration of the loop.    | arough 6, where the Address Pointer is incremented by the appropriate number of byte<br>The write cycle must be repeated enough times to completely rewrite the contents of th |

| Step 8: Disable w                   | rites.                         |                                                                                                                                                                                |

|                                     | 94 A6                          | BCF EECON1, WREN                                                                                                                                                               |

#### TABLE 4-6: MODIFYING PROGRAM FLASH

### 4.3 Data EEPROM Programming

Data EEPROM is accessed one byte at a time via an Address Pointer (register pair EEADRH:EEADR) and a data latch (EEDATA). Data EEPROM is written by loading EEADRH:EEADR with the desired memory location, EEDATA, with the data to be written and initiating a memory write by appropriately configuring the EECON1 register. A byte write automatically erases the location and writes the new data (erase-before-write).

When using the EECON1 register to perform a data EEPROM write, both the EEPGD and CFGS bits must be cleared (EECON1<7:6> = 00). The WREN bit must be set (EECON1<2> = 1) to enable writes of any sort and this must be done prior to initiating a write sequence. The write sequence is initiated by setting the WR bit (EECON1<1> = 1).

The write begins on the falling edge of the 24th PGC after the WR bit is set. It ends when the WR bit is cleared by hardware.

After the programming sequence terminates, PGC must be held low for the time specified by parameter P10 to allow high-voltage discharge of the memory array.

#### FIGURE 4-7: DATA EEPROM WRITE TIMING DIAGRAM

### 5.0 READING THE DEVICE

## 5.1 Read Program Flash, ID Locations and Configuration Bits

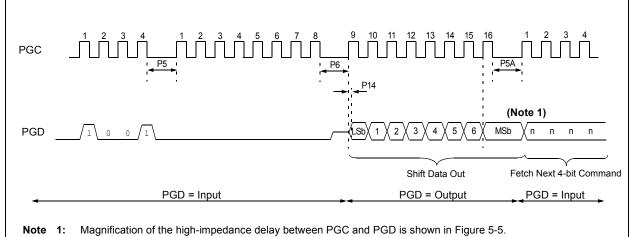

Program Flash is accessed one byte at a time via the 4-bit command, '1001' (table read, post-increment). The contents of memory pointed to by the Table Pointer (TBLPTRU:TBLPTRH:TBLPTRL) are serially output on PGD.

The 4-bit command is shifted in LSb first. The read is executed during the next 8 clocks, then shifted out on PGD during the last 8 clocks, LSb to MSb. A delay of P6 must be introduced after the falling edge of the 8th PGC of the operand to allow PGD to transition from an input to an output. During this time, PGC must be held low, as illustrated in Figure 5-1. This operation also increments the Table Pointer by one, pointing to the next byte in program Flash for the next read.

This technique will work to read any memory in the 000000h to 3FFFFh address space, so it also applies to the reading of the ID and Configuration registers.

| 4-bit<br>Command | Data Payload                   | Core Instruction                |

|------------------|--------------------------------|---------------------------------|

| Step 1: Set Tab  | le Pointer                     |                                 |

| 0000             | 0E <addr[21:16]></addr[21:16]> | MOVLW Addr[21:16]               |

| 0000             | 6E F8                          | MOVWF TBLPTRU                   |

| 0000             | 0E <addr[15:8]></addr[15:8]>   | MOVLW <addr[15:8]></addr[15:8]> |

| 0000             | 6E F7                          | MOVWF TBLPTRH                   |

| 0000             | 0E <addr[7:0]></addr[7:0]>     | MOVLW <addr[7:0]></addr[7:0]>   |

| 0000             | 6E F6                          | MOVWF TBLPTRL                   |

| Step 2: Read m   | nemory and then shift ou       | t on PGD, LSb to MSb            |

| 1001             | 00 00                          | TBLRD *+                        |

TABLE 5-1: READ PROGRAM FLASH SEQUENCE

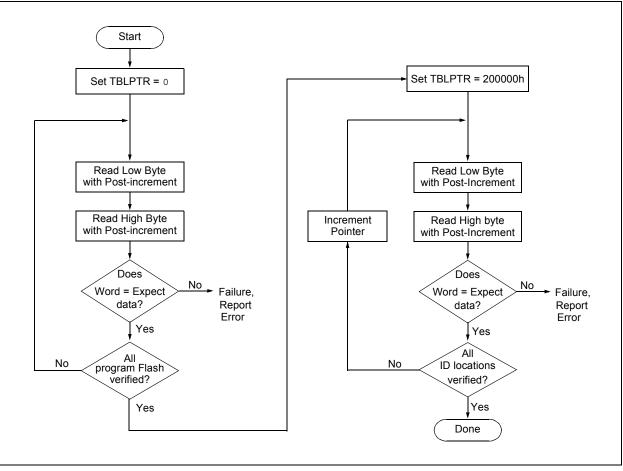

## 5.2 Verify Program Flash and ID Locations

The verify step involves reading back the program Flash space and comparing it against the copy held in the programmer's buffer. Memory reads occur a single byte at a time, so two bytes must be read to compare against the word in the programmer's buffer. Refer to **Section 5.1 "Read Program Flash, ID Locations and Configuration Bits"** for implementation details of reading program Flash. The Table Pointer must be manually set to 20000h (base address of the ID locations) once the program Flash has been verified. The post-increment feature of the Table Read 4-bit command can not be used to increment the Table Pointer beyond the program Flash space. In a 64-Kbyte device, for example, a post-increment read of address FFFFh will wrap the Table Pointer back to 000000h, rather than point to unimplemented address, 010000h.

#### FIGURE 5-2: VERIFY PROGRAM FLASH FLOW

| Bit Name   | Configuration<br>Words | Description                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BOREN<1:0> | CONFIG2L               | <ul> <li>Brown-out Reset Enable bits</li> <li>11 = Brown-out Reset enabled in hardware only (SBOREN is disabled)</li> <li>10 = Brown-out Reset enabled in hardware only and disabled in Sleep mode<br/>SBOREN is disabled)</li> <li>01 = Brown-out Reset enabled and controlled by software (SBOREN is enabled)</li> <li>00 = Brown-out Reset disabled in hardware and software</li> </ul> |  |  |  |

| PWRTEN     | CONFIG2L               | Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                                                                                                                         |  |  |  |

| WDTPS<3:0> | CONFIG2H               | Watchdog Timer Postscaler Select bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>1101 = 1:8,192<br>1100 = 1:4,096<br>1011 = 1:2,048<br>1010 = 1:1,024<br>1001 = 1:512<br>1000 = 1:256<br>0111 = 1:128<br>0110 = 1:64<br>0101 = 1:32<br>0100 = 1:16<br>0011 = 1:2<br>0000 = 1:1                                                                                                               |  |  |  |

| WDTEN      | CONFIG2H               | Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled (control is placed on SWDTEN bit)                                                                                                                                                                                                                                                                                         |  |  |  |

| MCLRE      | CONFIG3H               | MCLR Pin Enable bit         1 = MCLR pin enabled, RA3 input pin disabled         0 = RA3 input pin enabled, MCLR pin disabled                                                                                                                                                                                                                                                              |  |  |  |

| HFOFST     | CONFIG3H               | HFINTOSC Fast Start<br>1 = HFINTOSC output is not delayed<br>0 = HFINTOSC output is delayed until oscillator is stable (IOFS = 1)                                                                                                                                                                                                                                                          |  |  |  |

| XINST      | CONFIG4L               | Extended Instruction Set Enable bit<br>1 = Instruction set extension and Indexed Addressing mode enabled<br>0 = Instruction set extension and Indexed Addressing mode disabled<br>(Legacy mode)                                                                                                                                                                                            |  |  |  |

| BBSIZ      | CONFIG4L               | <ul> <li>Boot Block Size Select bit</li> <li>1 = 2 kW Boot Block size for PIC18F14K50 (1 kW Boot Block size for PIC18F13K50)</li> <li>0 = 1 kW Boot Block size for PIC18F14K50 (512 W Boot Block size for PIC18F13K50)</li> </ul>                                                                                                                                                          |  |  |  |

| LVP        | CONFIG4L               | Low-Voltage Programming Enable bit<br>1 = Low-Voltage Programming enabled, RC3 is the PGM pin<br>0 = Low-Voltage Programming disabled, RC3 is an I/O pin                                                                                                                                                                                                                                   |  |  |  |

#### TABLE 6-3: PIC18F1XK50/PIC18LF1XK50 BIT DESCRIPTIONS (CONTINUED)

#### TABLE 7-1: CHECKSUM COMPUTATION

| Device      | Code-Protect<br>BBSIZ = 0 | Checksum                                                                                                                                                                                                                                                                                               | Blank<br>Value | 0xAA at 0<br>and Max<br>Address |

|-------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------|

|             | None                      | SUM[0000:01FFF]+SUM[2000:3FFF]+<br>(CONFIG1L & 38h)+(CONFIG1H & FFh)+(CONFIG2L & 1Fh)+<br>(CONFIG2H & 1F)+(CONFIG3L & 00h)+(CONFIG3H & 88h)+<br>(CONFIG4L & 4Dh)+(CONFIG4H & 00h)+(CONFIG5L & 03h)+<br>(CONFIG5H & C0h)+(CONFIG6L & 03h)+(CONFIG6H & E0h)+<br>(CONFIG7L & 03h)+(CONFIG7H & 40h)        | C2DB           | C231                            |

| PIC18F14K50 | Boot Block                | SUM[0800:1FFF]+SUM[2000:3FFF]+<br>(CONFIG1L & 38h)+(CONFIG1H & FFh)+(CONFIG2L & 1Fh)+<br>(CONFIG2H & 1F)+(CONFIG3L & 00h)+ (CONFIG3H & 88h)+<br>(CONFIG4L & 4Dh)+(CONFIG4H & 00h)+(CONFIG5L & 03h)+<br>(CONFIG5H & C0h)+(CONFIG6L & 03h)+(CONFIG6H & E0h)+<br>(CONFIG7L & 03h)+(CONFIG7H & 40h)+SUM_ID | CAC1           | CA58                            |

|             | Boot/<br>Block 0          | SUM[2000:3FFF]+<br>(CONFIG1L & 38h)+(CONFIG1H & FFh)+(CONFIG2L & 1Fh)+<br>(CONFIG2H & 1F)+(CONFIG3L & 00h)+(CONFIG3H & 88h)+<br>(CONFIG4L & 4Dh)+(CONFIG4H & 00h)+(CONFIG5L & 03h)+<br>(CONFIG5H & C0h)+(CONFIG6L & 03h)+(CONFIG6H & E0h)+<br>(CONFIG7L & 03h)+(CONFIG7H & 40h)+SUM_ID                 | E2C0           | E257                            |

|             | All                       | (CONFIG1L & 38h)+(CONFIG1H & FFh)+(CONFIG2L & 1Fh)+<br>(CONFIG2H & 1F)+(CONFIG3L & 00h)+(CONFIG3H & 88h)+<br>(CONFIG4L & 4Dh)+(CONFIG4H & 00h)+(CONFIG5L & 03h)+<br>(CONFIG5H & C0h)+(CONFIG6L & 03h)+(CONFIG6H & E0h)+<br>(CONFIG7L & 03h)+(CONFIG7H & 40h)+SUM_ID                                    | 02BE           | 02AA                            |

|             | None                      | SUM[0000:0FFF]+SUM[1000:1FFF]+<br>(CONFIG1L & 38h)+(CONFIG1H & FFh)+(CONFIG2L & 1Fh)+<br>(CONFIG2H & 1F)+(CONFIG3L & 00h)+(CONFIG3H & 88h)+<br>(CONFIG4L & 4Dh)+(CONFIG4H & 00h)+(CONFIG5L & 03h)+<br>(CONFIG5H & C0h)+(CONFIG6L & 03h)+(CONFIG6H & E0h)+<br>(CONFIG7L & 03h)+(CONFIG7H & 40h)         | E2DB           | E231                            |

| PIC18F13K50 | Boot Block                | SUM[0400:0FFF]+SUM[1000:1FFF]+<br>(CONFIG1L & 38h)+(CONFIG1H & FFh)+(CONFIG2L & 1Fh)+<br>(CONFIG2H & 1F)+(CONFIG3L & 00h)+ (CONFIG3H & 88h)+<br>(CONFIG4L & 4Dh)+(CONFIG4H & 00h)+(CONFIG5L & 03h)+<br>(CONFIG5H & C0h)+(CONFIG6L & 03h)+(CONFIG6H & E0h)+<br>(CONFIG7L & 03h)+(CONFIG7H & 40h)+SUM_ID | E6C3           | E65A                            |

|             | Boot/<br>Block 0          | SUM[1000:1FFF]+<br>(CONFIG1L & 38h)+(CONFIG1H & FFh)+(CONFIG2L & 1Fh)+<br>(CONFIG2H & 1F)+(CONFIG3L & 00h)+(CONFIG3H & 88h)+<br>(CONFIG4L & 4Dh)+(CONFIG4H & 00h)+(CONFIG5L & 03h)+<br>(CONFIG5H & C0h)+(CONFIG6L & 03h)+(CONFIG6H & E0h)+<br>(CONFIG7L & 03h)+(CONFIG7H & 40h)+SUM_ID                 | F2C2           | F259                            |

|             | All                       | (CONFIG1L & 38h)+(CONFIG1H & FFh)+(CONFIG2L & 1Fh)+<br>(CONFIG2H & 1F)+(CONFIG3L & 00h)+(CONFIG3H & 88h)+<br>(CONFIG4L & 4Dh)+(CONFIG4H & 00h)+(CONFIG5L & 03h)+<br>(CONFIG5H & C0h)+(CONFIG6L & 03h)+(CONFIG6H & E0h)+                                                                                | 02C0           | 02AC                            |

& = Bit-wise AND

### 8.1 AC/DC Characteristics Timing Requirements for Program/Verify Test Mode

| Standard Operating Conditions<br>Operating Temperature: 25°C is recommended |        |                                                                                                  |                 |         |       |                                        |  |

|-----------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------|-----------------|---------|-------|----------------------------------------|--|

| Param<br>No.                                                                | Sym.   | Characteristic                                                                                   | Min.            | Max.    | Units | Conditions                             |  |

| D110                                                                        | Vінн   | High-Voltage Programming Voltage on<br>MCLR/VPP/RA3                                              | 8               | 9       | V     |                                        |  |

| D110A                                                                       | Vihl   | Low-Voltage Programming Voltage on<br>MCLR/VPP/RA3                                               | 1.80            | Vdd     | V     |                                        |  |

| D111                                                                        | Vdd    | PIC18F1XK50 (includes Bulk Erase)                                                                | 2.70            | 5.50    | V     |                                        |  |

|                                                                             |        | PIC18LF1XK50 (includes Bulk Erase)                                                               | 2.70            | 3.60    | V     |                                        |  |

| D112                                                                        | IPP    | Programming Current on MCLR/VPP/RA3                                                              | _               | 5       | mA    |                                        |  |

| D113                                                                        | IDDP   | Supply Current During Programming                                                                | _               | 5       | mA    |                                        |  |

| D031                                                                        | VIL    | Input Low Voltage                                                                                | Vss             | 0.2 Vdd | V     |                                        |  |

| D041                                                                        | VIH    | Input High Voltage                                                                               | 0.8 Vdd         | Vdd     | V     | Except RA0 and RA1                     |  |

| D042                                                                        | VIH    | Input High Voltage on RA0 and RA1 pins only                                                      | 0.8 Vdd         | Vdd     | V     | VDD < 3.6V                             |  |

| D080                                                                        | Vol    | Output Low Voltage                                                                               | _               | 0.6     | V     | IOL = 3.0 mA @ 2.7V                    |  |

| D090                                                                        | Vон    | Output High Voltage                                                                              | VDD - 0.7       | _       | V     | Іон = -2.0 mA @ 2.7V                   |  |

| D091                                                                        | Vон    | Output High Voltage on RA0 pin only                                                              | VUSB-0.7<br>Min | _       | V     |                                        |  |

| D012                                                                        | Сю     | Capacitive Loading on I/O pin (PGD)                                                              | _               | 50      | рF    | To meet AC specifications              |  |

|                                                                             |        |                                                                                                  |                 |         |       |                                        |  |

| P1                                                                          | TR     | MCLR/VPP/RA3 Rise Time to enter<br>Program/Verify mode                                           | _               | 1.0     | μS    | (Note 1)                               |  |

| P2                                                                          | TPGC   | Serial Clock (PGC) Period                                                                        | 100             | _       | ns    | VDD = 3.6V                             |  |

|                                                                             |        |                                                                                                  | 1               | —       | μS    | VDD = 1.8V                             |  |

| P2A                                                                         | TPGCL  | Serial Clock (PGC) Low Time                                                                      | 40              | —       | ns    | VDD = 3.6V                             |  |

|                                                                             |        |                                                                                                  | 400             | —       | ns    | VDD = 1.8V                             |  |

| P2B                                                                         | TPGCH  | Serial Clock (PGC) High Time                                                                     | 40              | —       | ns    | VDD = 3.6V                             |  |

|                                                                             |        |                                                                                                  | 400             |         | ns    | VDD = 1.8V                             |  |

| P3                                                                          | TSET1  | Input Data Setup Time to Serial Clock $\downarrow$                                               | 15              | —       | ns    |                                        |  |

| P4                                                                          | THLD1  | Input Data Hold Time from PGC $\downarrow$                                                       | 15              | —       | ns    |                                        |  |

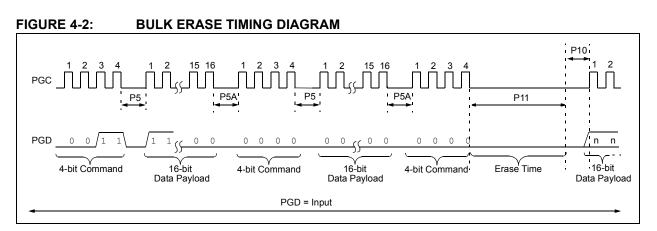

| P5                                                                          | TDLY1  | Delay between 4-bit Command and Command<br>Operand                                               | 40              | —       | ns    |                                        |  |

| P5A                                                                         | TDLY1A | Delay between 4-bit Command Operand and next<br>4-bit Command                                    | 40              | —       | ns    |                                        |  |

| P6                                                                          | TDLY2  | Delay between Last PGC $\downarrow$ of Command Byte to First PGC $\uparrow$ of Read of Data Word | 20              | —       | ns    |                                        |  |

| P9                                                                          | TDLY5  | PGC High Time (minimum programming time)                                                         | 1               | —       | ms    | Externally Timed                       |  |

| P9A                                                                         | Tdly5a | PGC High Time                                                                                    | 5               |         | ms    | Configuration Word<br>programming time |  |

| P10                                                                         | TDLY6  | PGC Low Time after Programming<br>(high-voltage discharge time)                                  | 100             | —       | μS    |                                        |  |

| P11                                                                         | TDLY7  | Delay to allow Self-Timed Data Write or<br>Bulk Erase to occur                                   | 5               |         | ms    |                                        |  |

**Note 1:** Do not allow excess time when transitioning MCLR between VIL and VIHH; this can cause spurious program executions to occur. The maximum transition time is:

1 TCY + TPWRT (if enabled) + 1024 Tosc (for LP, HS, HS/PLL and XT modes only) + 2 ms (for HS/PLL mode only) + 1.5  $\mu$ s (for EC mode only) where TCY is the instruction cycle time, TPWRT is the Power-up Timer period and Tosc is the oscillator period. For specific values, refer to the Electrical Characteristics section of the device data sheet for the particular device.

### **REVISION HISTORY**

### **Revision A (January 2008)**

Original Programming Specification release.

### **Revision B (September 2008)**

Updated to add VREG to Config 2L. Various minor edits.

### Revision C (January 2009)

Updated to replace some data in Table 8.1. Various minor edits.

#### Revision D (04/2009)

Minor edits.

### **Revision E (05/2010)**

Updated Table 3-1, Figure 3-1 and Figure 3-2.

NOTES:

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

**Santa Clara** Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/05/10