# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0130hh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

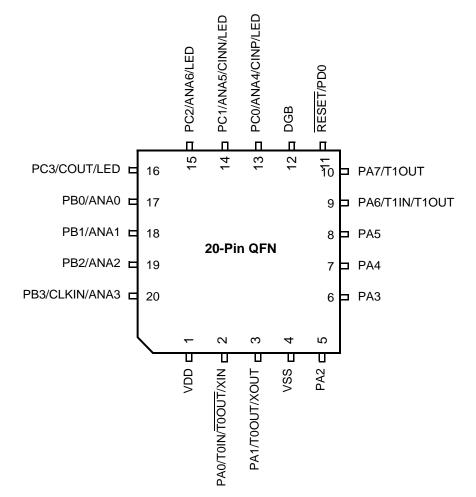

Figure 4. Z8F0830 Series in 20-Pin QFN Package

9

# **Signal Descriptions**

Table 4 describes the Z8 Encore! F0830 Series signals. See the <u>Pin Configurations</u> section on page 7 to determine the signals available for each specific package style.

| Signal<br>Mnemonic                             | I/O       | Description                                                                                                                     |

|------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose                                | I/O Ports | s A–D                                                                                                                           |

| PA[7:0]                                        | I/O       | Port A. These pins are used for general purpose I/O.                                                                            |

| PB[7:0]                                        | I/O       | Port B. These pins are used for general purpose I/O. PB6 and PB7 are available only in those devices without an ADC.            |

| PC[7:0]                                        | I/O       | Port C. These pins are used for general purpose I/O.                                                                            |

| PD[0]                                          | I/O       | Port D. This pin is used for general purpose output only.                                                                       |

| Note: PB6 and PB7<br>placed by AV <sub>I</sub> |           | available in 28-pin packages without ADC. In 28-pin packages with ADC, they are re- $^{\prime}_{\rm SS}$                        |

| Timers                                         |           |                                                                                                                                 |

| T0OUT/T1OUT                                    | 0         | Timer output 0–1. These signals are the output from the timers.                                                                 |

| T0OUT/T1OUT                                    | 0         | Timer complement output 0–1. These signals are output from the timers in PWM DUAL OUTPUT Mode.                                  |

| T0IN/T1IN                                      | I         | Timer Input 0–1. These signals are used as the capture, gating and counte inputs. The T0IN signal is multiplexed T0OUT signals. |

| Comparator                                     |           |                                                                                                                                 |

| CINP/CINN                                      | I         | Comparator inputs. These signals are the positive and negative inputs to the comparator.                                        |

| COUT                                           | 0         | Comparator output. This is the output of the comparator.                                                                        |

| Analog                                         |           |                                                                                                                                 |

| ANA[7:0]                                       | I         | Analog port. These signals are used as inputs to the analog-to-digital converter (ADC).                                         |

| V <sub>REF</sub>                               | I/O       | Analog-to-digital converter reference voltage input.                                                                            |

|                                                |           | <b>Note:</b> When configuring ADC using external $V_{REF}$ , PB5 is used as $V_{REF}$ in 28-pin package.                        |

|                                                |           | nals are available only in the 28-pin packages with ADC. They are replaced by PB6 ages without ADC.                             |

## **Table 4. Signal Descriptions**

# **Data Memory**

The Z8 Encore! F0830 Series does not use the eZ8 CPU's 64KB data memory address space.

# **Flash Information Area**

Table 7 maps the Z8 Encore! F0830 Series Flash information area. The 128-byte information area is accessed, by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash information area is mapped into program memory and overlays these 128 bytes at addresses FE00H to FE7FH. When information area access is enabled, all reads from these program memory addresses return information area data rather than program memory data. Access to the Flash information area is read-only.

| Program<br>Memory<br>Address (Hex) | Function                                                                                 |

|------------------------------------|------------------------------------------------------------------------------------------|

| FE00–FE3F                          | Zilog option bits                                                                        |

| FE40-FE53                          | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH |

| FE54–FE5F                          | Reserved                                                                                 |

| FE60–FE7F                          | Reserved                                                                                 |

| FE80–FFFF                          | Reserved                                                                                 |

#### Table 7. Z8 Encore! F0830 Series Flash Memory Information Area Map

# Interrupt Edge Select Register

The interrupt edge select (IRQES) register determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin. See Table 47.

|         |          |      | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|----------|------|------|------|------|------|------|------|

| Field   | ES7      | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W F   | R/W      | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | <b>I</b> |      |      | FC   | DH   |      |      |      |

#### Table 47. Interrupt Edge Select Register (IRQES)

# Bit Description [7] Interrupt Edge Select x IESx 0 = An interrupt request is generated on the falling edge of the PAx input or PDx. 1 = An interrupt request is generated on the rising edge of the PAx input or PDx. Note: x indicates register bits in the address range 7–0.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the timer input signal. No interrupt is generated by the first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

# **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on Timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the timer low byte register are placed in a holding register. A subsequent read from the timer low byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value when enabled. When the timers are not enabled, a read from the timer low byte register returns the actual value in the counter.

# **Timer Pin Signal Operation**

Timer output is a GPIO port pin alternate function. The timer output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO alternate function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT Mode. For this mode, no timer input is available.

# Comparator

The Z8 Encore! F0830 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or from an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The comparator includes the following features:

- Positive input is connected to a GPIO pin

- Negative input can be connected to either a GPIO pin or a programmable internal reference

- Output can be either an interrupt source or an output to an external pin

# Operation

One of the comparator inputs can be connected to an internal reference that is a user-selectable reference and is user-programmable with 200mV resolution.

The comparator can be powered down to save supply current. For details, see the <u>Power</u> <u>Control Register 0</u> section on page 31.

**Caution:** As a result of the propagation delay of the comparator, Zilog does not recommend enabling the comparator without first disabling interrupts and waiting for the comparator output to settle. This delay prevents spurious interrupts after comparator enabling.

The following example shows how to safely enable the comparator:

```

di

ld cmp0,r0; load some new configuration

nop

nop ; wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

# Flash Page Select Register

The Flash Page Select Register shares address space with the Flash Sector Protect Register. Unless the Flash Controller is locked and written with 5EH, any writes to this address will target the Flash Page Select Register.

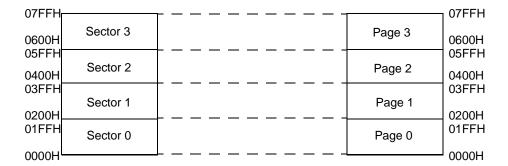

The register selects one of the eight available Flash memory pages to be programmed or erased. Each Flash page contains 512-bytes of Flash memory. During a page erase operation, all Flash memory containing addresses with the most significant 7-bits within FPS[6:0] are chosen for program/erase operations.

| Bit     | 7       | 6   | 5               | 4  | 3    | 2 | 1 | 0   |

|---------|---------|-----|-----------------|----|------|---|---|-----|

| Field   | INFO_EN |     |                 |    | PAGE |   |   |     |

| RESET   | 0       | 0   | 0               | 0  | 0    | 0 | 0 | 0   |

| R/W     | R/W     | R/W | R/W R/W R/W R/W |    |      |   |   | R/W |

| Address |         |     |                 | FF | 9H   |   |   |     |

## Table 74. Flash Page Select Register (FPS)

#### Bit Description

## [7] Information Area Enable

INFO\_EN 0 = Information area is not selected.

1 = Information area is selected. The information area is mapped into the program memory address space at addresses FE00H through FFFFH.

# [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for page erase and page unlocking. Program memory address[15:9] = PAGE[6:0]. For Z8F04xx and Z8F02xx devices, the upper four bits must always be 0. For Z8F01xx devices, the upper five bits must always be 0.

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>VBO_AO | <ul> <li>Voltage Brown-Out Protection Always On</li> <li>0 = Voltage Brown-Out protection is disabled in STOP Mode to reduce total power consumption.</li> <li>1 = Voltage Brown-Out protection is always enabled, even during STOP Mode. This setting is the default setting for unprogrammed (erased) Flash.</li> </ul>                                                                                      |

| [2]<br>FRP    | <ul> <li>Flash Read Protect</li> <li>0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.</li> <li>1 = User program code is accessible. All On-Chip Debugger commands are enabled. This is the default setting for unprogrammed (erased) Flash.</li> </ul>                                                                                              |

| [1]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                                                                           |

| [0]<br>FWP    | <ul> <li>Flash Write Protect</li> <li>This option bit provides Flash program memory protection.</li> <li>0 = Programming and erasure disabled for all Flash program memory. Programming, page erase and mass erase through user code is disabled. Mass erase is available using the On-Chip Debugger.</li> <li>1 = Programming, page erase and mass erase are enabled for all Flash program memory.</li> </ul> |

# Table 82. Flash Options Bits at Program Memory Address 0001H

| Bit       | 7                    | 6            | 5             | 4      | 3        | 2     | 1   | 0   |  |  |  |  |  |

|-----------|----------------------|--------------|---------------|--------|----------|-------|-----|-----|--|--|--|--|--|

| Field     | VBO_RES              | Rese         | erved         | XTLDIS | Reserved |       |     |     |  |  |  |  |  |

| RESET     | U                    | U            | U             | U      | U        | U U U |     | U   |  |  |  |  |  |

| R/W       | R/W                  | R/W          | R/W           | R/W    | R/W      | R/W   | R/W | R/W |  |  |  |  |  |

| Address   | Program Memory 0001H |              |               |        |          |       |     |     |  |  |  |  |  |

| Note: U = | Unchanged b          | y Reset. R/W | / = Read/Writ | ie.    |          |       |     |     |  |  |  |  |  |

| Bit            | Description                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>VBO_RES | Voltage Brown-Out reset<br>1 = VBO detection causes a system reset. This setting is the default setting for unpro-<br>grammed (erased) Flash. |

| [6:5]          | Reserved<br>These bits are reserved and must be programmed to 11.                                                                             |

128

# **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the Byte Write routine ( $0 \times 20B3$ ). At the return from the subroutine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 91. Additionally, user code should pop the address and data bytes off the stack.

The write routine uses 16 bytes of stack space in addition to the two bytes of address and data pushed by the user code. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $136\mu s$  (assuming a 20MHz system clock). For every 200 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 58ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $7\mu$ s execution time.

| Bit              | 7                                                                                                                                                                                                                    | 6               | 5               | 4           | 3 | 2 | 1 | 0 |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-------------|---|---|---|---|--|--|--|--|--|--|--|

| Field            | Reserved FE IGADDR WE                                                                                                                                                                                                |                 |                 |             |   |   |   |   |  |  |  |  |  |  |  |

| Default<br>Value | 0                                                                                                                                                                                                                    | 0 0 0 0 0 0 0 0 |                 |             |   |   |   |   |  |  |  |  |  |  |  |

| Bit              | Descriptio                                                                                                                                                                                                           | n               |                 |             |   |   |   |   |  |  |  |  |  |  |  |

| [7:3]            | <b>Reserved</b><br>These bits are reserved and must be programmed to 00000.                                                                                                                                          |                 |                 |             |   |   |   |   |  |  |  |  |  |  |  |

| [2]<br>FE        | Flash Erro<br>If a Flash e                                                                                                                                                                                           | -               | ted, this bit i | s set to 1. |   |   |   |   |  |  |  |  |  |  |  |

| [1]<br>IGADDR    | Illegal Address<br>R When an NVDS byte writes to invalid addresses occur (those exceeding the NVDS array size),<br>this bit is set to 1.                                                                             |                 |                 |             |   |   |   |   |  |  |  |  |  |  |  |

| [0]<br>WE        | Write Error<br>A failure occurs during data writes to Flash. When writing data into a certain address, a read-<br>back operation is performed. If the read-back value is not the same as the value written, this bit |                 |                 |             |   |   |   |   |  |  |  |  |  |  |  |

#### Table 91. Write Status Byte

is set to 1.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The read program memory command, reads data from program memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

Write Data Memory (0CH). The write data memory command, writes data to data memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG Mode or if the flash read protect option bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Data Memory (0DH).** The read data memory command, reads from data memory. This command is equivalent to the LDE and LDEI instructions. Data can be read from 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Read Program Memory CRC (0EH).** The read program memory CRC command, computes and returns the cyclic redundancy check (CRC) of program memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike the other OCD read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads program memory, calculates the CRC value and returns the result. The delay is a function of program mem-

| Assembly     |                                                                                                                   |     |     |       |   | Address Op<br><u>Mode</u> Code(s) |   |   |   |   | Fla | ags    | Fetch | Instr. |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|-------|---|-----------------------------------|---|---|---|---|-----|--------|-------|--------|

| Mnemonic     | Symbolic Operation                                                                                                | dst | src | (Hex) | С | Ζ                                 | S | ۷ | D | Н |     | Cycles |       |        |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                             | r   |     | 0A–FA | _ | -                                 | _ | _ | _ | _ | 2   | 3      |       |        |

| EI           | IRQCTL[7] ← 1                                                                                                     |     |     | 9F    | _ | _                                 | _ | _ | _ | _ | 1   | 2      |       |        |

| HALT         | HALT Mode                                                                                                         |     |     | 7F    | - | -                                 | _ | _ | - | _ | 1   | 2      |       |        |

| INC dst      | dst ← dst + 1                                                                                                     | R   |     | 20    | _ | *                                 | * | _ | _ | _ | 2   | 2      |       |        |

|              |                                                                                                                   | IR  |     | 21    | _ |                                   |   |   |   |   | 2   | 3      |       |        |

|              |                                                                                                                   | r   |     | 0E-FE |   |                                   |   |   |   |   | 1   | 2      |       |        |

| INCW dst     | dst ← dst + 1                                                                                                     | RR  |     | A0    | _ | *                                 | * | * | - | _ | 2   | 5      |       |        |

|              |                                                                                                                   | IRR |     | A1    |   |                                   |   |   |   |   | 2   | 6      |       |        |

| IRET         | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |     |     | BF    | * | *                                 | * | * | * | * | 1   | 5      |       |        |

| JP dst       | $PC \gets dst$                                                                                                    | DA  |     | 8D    | _ | _                                 | _ | _ | - | _ | 3   | 2      |       |        |

|              |                                                                                                                   | IRR |     | C4    | _ |                                   |   |   |   |   | 2   | 3      |       |        |

| JP cc, dst   | if cc is true<br>PC ← dst                                                                                         | DA  |     | 0D-FD | - | -                                 | - | - | _ | - | 3   | 2      |       |        |

| JR dst       | $PC \gets PC + X$                                                                                                 | DA  |     | 8B    | _ | _                                 | _ | _ | _ | _ | 2   | 2      |       |        |

| JR cc, dst   | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA  |     | 0B–FB | _ | -                                 | _ | - | _ | _ | 2   | 2      |       |        |

# Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| 179 |

|-----|

|-----|

| Assembly      |                                                                                                                        | Addre<br>Mod |             |                  |   |   | Fla | ags |   | Fetch | Instr. |        |

|---------------|------------------------------------------------------------------------------------------------------------------------|--------------|-------------|------------------|---|---|-----|-----|---|-------|--------|--------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst          | src         | Code(s)<br>(Hex) | С | Ζ | S   | ۷   | D | Н     | Cycles | Cycles |

| TM dst, src   | dst AND src                                                                                                            | r            | r           | 72               | - | * | *   | 0   | _ | -     | 2      | 3      |

|               |                                                                                                                        | r            | lr          | 73               | _ |   |     |     |   |       | 2      | 4      |

|               |                                                                                                                        | R            | R           | 74               |   |   |     |     |   |       | 3      | 3      |

|               |                                                                                                                        | R            | IR          | 75               | _ |   |     |     |   |       | 3      | 4      |

|               |                                                                                                                        | R            | IM          | 76               |   |   |     |     |   |       | 3      | 3      |

|               |                                                                                                                        | IR           | IM          | 77               |   |   |     |     |   |       | 3      | 4      |

| TMX dst, src  | dst AND src                                                                                                            | ER           | ER          | 78               | _ | * | *   | 0   | - | _     | 4      | 3      |

|               |                                                                                                                        | ER           | IM          | 79               |   |   |     |     |   |       | 4      | 3      |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |              | Vec-<br>tor | F2               | _ | - | -   | -   | - | -     | 2      | 6      |

| WDT           |                                                                                                                        |              |             | 5F               | - | - | _   | _   | _ | -     | 1      | 2      |

| XOR dst, src  | $dst \gets dst \; XOR \; src$                                                                                          | r            | r           | B2               | _ | * | *   | 0   | - | -     | 2      | 3      |

|               |                                                                                                                        | r            | lr          | B3               |   |   |     |     |   |       | 2      | 4      |

|               |                                                                                                                        | R            | R           | B4               |   |   |     |     |   |       | 3      | 3      |

|               |                                                                                                                        | R            | IR          | B5               |   |   |     |     |   |       | 3      | 4      |

|               |                                                                                                                        | R            | IM          | B6               |   |   |     |     |   |       | 3      | 3      |

|               |                                                                                                                        | IR           | IM          | B7               |   |   |     |     |   |       | 3      | 4      |

| XORX dst, src | $dst \gets dst \; XOR \; src$                                                                                          | ER           | ER          | B8               | - | * | *   | 0   | - | -     | 4      | 3      |

|               |                                                                                                                        | ER           | IM          | B9               | _ |   |     |     |   |       | 4      | 3      |

# Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

## 195

# General Purpose I/O Port Input Data Sample Timing

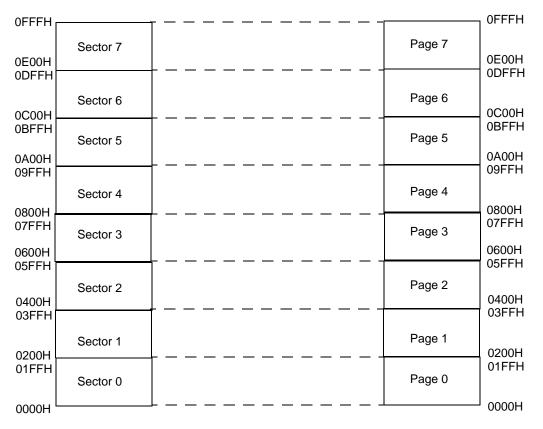

Figure 33 displays timing of the GPIO port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The port value is available to the eZ8 CPU on the second rising clock edge following the change of the port value.

#### Figure 33. Port Input Sample Timing

#### Table 124. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |         |  |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (not pictured)                            | 5          | -       |  |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (not pictured)                             | 0          | -       |  |  |

| T <sub>SMR</sub>    | GPIO port pin pulse width to ensure Stop Mode Recovery (for GPIO port pins enabled as SMR sources) | 1µs        |         |  |  |

# **General Purpose I/O Port Output Timing**

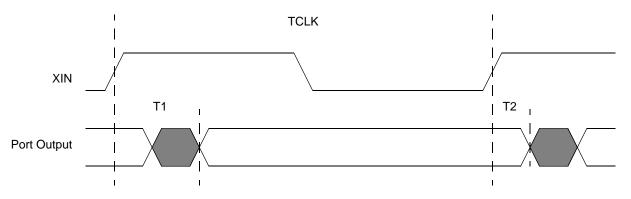

Figure 34 and Table 125 provide timing information for the GPIO port pins.

|                |                                     | Dela    | y (ns)  |  |  |  |  |  |

|----------------|-------------------------------------|---------|---------|--|--|--|--|--|

| Parameter      | Abbreviation                        | Minimum | Maximum |  |  |  |  |  |

| GPIO Port F    | GPIO Port Pins                      |         |         |  |  |  |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _       | 15      |  |  |  |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2       | _       |  |  |  |  |  |

#### Table 125. GPIO Port Output Timing

| Part Number          | Flash      | RAM   | NVDS | ADC<br>Channels | Description                                    |

|----------------------|------------|-------|------|-----------------|------------------------------------------------|

| Z8F0131PJ020SG       | 1KB        | 256   | Yes  | 0               | PDIP 28-pin                                    |

| Z8F0131QJ020SG       | 1KB        | 256   | Yes  | 0               | QFN 28-pin                                     |

| Extended Temperature | : −40°C to | 105°C |      |                 |                                                |

| Z8F0130SH020EG       | 1KB        | 256   | Yes  | 7               | SOIC 20-pin                                    |

| Z8F0130HH020EG       | 1KB        | 256   | Yes  | 7               | SSOP 20-pin                                    |

| Z8F0130PH020EG       | 1KB        | 256   | Yes  | 7               | PDIP 20-pin                                    |

| Z8F0130QH020EG       | 1KB        | 256   | Yes  | 7               | QFN 20-pin                                     |

| Z8F0131SH020EG       | 1KB        | 256   | Yes  | 0               | SOIC 20-pin                                    |

| Z8F0131HH020EG       | 1KB        | 256   | Yes  | 0               | SSOP 20-pin                                    |

| Z8F0131PH020EG       | 1KB        | 256   | Yes  | 0               | PDIP 20-pin                                    |

| Z8F0131QH020EG       | 1KB        | 256   | Yes  | 0               | QFN 20-pin                                     |

| Z8F0130SJ020EG       | 1KB        | 256   | Yes  | 8               | SOIC 28-pin                                    |

| Z8F0130HJ020EG       | 1KB        | 256   | Yes  | 8               | SSOP 28-pin                                    |

| Z8F0130PJ020EG       | 1KB        | 256   | Yes  | 8               | PDIP 28-pin                                    |

| Z8F0130QJ020EG       | 1KB        | 256   | Yes  | 8               | QFN 28-pin                                     |

| Z8F0131SJ020EG       | 1KB        | 256   | Yes  | 0               | SOIC 28-pin                                    |

| Z8F0131HJ020EG       | 1KB        | 256   | Yes  | 0               | SSOP 28-pin                                    |

| Z8F0131PJ020EG       | 1KB        | 256   | Yes  | 0               | PDIP 28-pin                                    |

| Z8F0131QJ020EG       | 1KB        | 256   | Yes  | 0               | QFN 28-pin                                     |

| ZUSBSC00100ZACG      |            |       |      |                 | USB Smart Cable Accessory Kit                  |

| ZUSBOPTSC01ZACG      |            |       |      |                 | Opto-Isolated USB Smart Cable<br>Accessory Kit |

#### Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

# **Part Number Suffix Designations**

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0830SH020SG is an 8-bit 20MHz Flash MCU with 8KB Program Memory and equipped with ADC and NVDS in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

207

Table 129 lists the pin count by package.

|         | Pin Count    |    |  |  |

|---------|--------------|----|--|--|

| Package | 20           | 28 |  |  |

| PDIP    | $\checkmark$ |    |  |  |

| QFN     | $\checkmark$ |    |  |  |

| SOIC    | $\checkmark$ |    |  |  |

| SSOP    | $\checkmark$ |    |  |  |

#### Table 129. Package and Pin Count Description

# Hex Address: F71

This address range is reserved.

## Hex Address: F72

## Table 147. ADC Data High Byte Register (ADCD\_H)

| Bit     | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------|---|---|---|---|---|---|---|--|

| Field   | ADCDH |   |   |   |   |   |   |   |  |

| RESET   | Х     |   |   |   |   |   |   |   |  |

| R/W     | R     |   |   |   |   |   |   |   |  |

| Address | F72H  |   |   |   |   |   |   |   |  |

| Bit   | Description                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | <b>ADC High Byte</b><br>00h–FFh = The last conversion output is held in the data registers until the next ADC conversion is completed. |

## Hex Address: F73

# Table 148. ADC Data Low Bits Register (ADCD\_L)

| Bit     | 7    | 6   | 5 | 4 | 3        | 2 | 1 | 0 |  |

|---------|------|-----|---|---|----------|---|---|---|--|

| Field   | ADO  | CDL |   |   | Reserved |   |   |   |  |

| RESET   | )    | X   |   |   | X        |   |   |   |  |

| R/W     | F    | २   | R |   |          |   |   |   |  |

| Address | F73H |     |   |   |          |   |   |   |  |

| Bit<br>Position | Description                                                                                                                                                                                                                                         |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]           | <b>ADC Low Bits</b><br>00–11b = These bits are the two least significant bits of the 10-bit ADC output. These bits are<br>undefined after a reset. The low bits are latched into this register whenever the ADC Data High<br>Byte Register is read. |

| [5:0]           | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                        |

## Hex Address: F83

#### Table 153. LED Drive Level High Register (LEDLVLH)

| Bit     | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | LEDLVLH[7:0] |     |     |     |     |     |     |     |

| RESET   | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F83H         |     |     |     |     |     |     |     |

## Hex Address: F84

#### Table 154. LED Drive Level Low Register (LEDLVLL)

| Bit     | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | LEDLVLL[7:0] |     |     |     |     |     |     |     |

| RESET   | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F84H         |     |     |     |     |     |     |     |

### Hex Address: F85

This address range is reserved.

# **Oscillator Control**

For more information about the Oscillator Control registers, see the <u>Oscillator Control</u> <u>Register Definitions</u> section on page 154.

#### Hex Address: F86

| Table 155. | Oscillator | Control | Register | (OSCCTL) |

|------------|------------|---------|----------|----------|

|------------|------------|---------|----------|----------|

| Bit     | 7     | 6     | 5     | 4     | 3     | 2      | 1   | 0   |

|---------|-------|-------|-------|-------|-------|--------|-----|-----|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN | SCKSEL |     |     |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0      | 0   | 0   |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W    | R/W | R/W |

| Address | F86H  |       |       |       |       |        |     |     |

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

238

reload high and low byte registers 85 timer control register definitions 83 timer output signal operation 82 timers 0-3 control registers 87, 88 high and low byte registers 83, 86 TM 167 TMX 167 TRAP 169

# V

vector 165 voltage brown-out reset (VBR) 24 voltage measurement timing diagram 100

# W

watch-dog timer approximate time-out delay 92 approximate time-out delays 92, 106, 134, 151, 161 CNTL 24 control register 95, 154 electrical characteristics and timing 194 interrupt in noromal operation 93 interrupt in stop mode 93 operation 92, 106, 134, 151, 161 refresh 93 reload unlock sequence 94 reload upper, high and low registers 96 reset 25 reset in normal operation 94 reset in Stop mode 94 time-out response 93 watchdog timer refresh 168 WDTCTL register 29, 95, 107, 154, 217, 218, 226 WDTH register 96, 227 WDTL register 97, 227 working register 164 working register pair 165 WTDU register 96, 227

# Χ

X 165 XOR 169 XORX 169

# Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2