Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | -                                                         |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 17                                                        |  |

| Program Memory Size        | 1KB (1K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | A/D 7x10b                                                 |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |

| Mounting Type              | Through Hole                                              |  |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0130ph020sg |  |

## Z8 Encore!® F0830 Series Product Specification

vii

| Calibration and Compensation                                 | 101 |

|--------------------------------------------------------------|-----|

| ADC Control Register Definitions                             | 101 |

| ADC Control Register 0                                       | 102 |

| ADC Data High Byte Register                                  | 103 |

| ADC Data Low Bits Register                                   | 103 |

| Sample Settling Time Register                                | 104 |

| Sample Time Register                                         | 105 |

| Comparator                                                   | 106 |

| Operation                                                    | 106 |

| Comparator Control Register Definitions                      | 107 |

| Flash Memory                                                 | 108 |

| Data Memory Address Space                                    | 111 |

| Flash Information Area                                       | 111 |

| Operation                                                    | 112 |

| Flash Operation Timing Using the Flash Frequency Registers   | 114 |

| Flash Code Protection Against External Access                | 114 |

| Flash Code Protection Against Accidental Program and Erasure | 114 |

| Byte Programming                                             | 116 |

| Page Erase                                                   | 117 |

| Mass Erase                                                   | 117 |

| Flash Controller Bypass                                      | 117 |

| Flash Controller Behavior in Debug Mode                      | 117 |

| NVDS Operational Requirements                                | 118 |

| Flash Control Register Definitions                           | 118 |

| Flash Control Register                                       | 119 |

| Flash Status Register                                        |     |

| Flash Page Select Register                                   | 121 |

| Flash Sector Protect Register                                |     |

| Flash Frequency High and Low Byte Registers                  |     |

| Flash Option Bits                                            | 124 |

| Operation                                                    | 124 |

| Option Bit Configuration by Reset                            | 124 |

| Option Bit Types                                             |     |

| Flash Option Bit Control Register Definitions                |     |

| Trim Bit Address Register                                    |     |

| Trim Bit Data Register                                       |     |

| Flash Option Bit Address Space                               |     |

| Trim Bit Address Space                                       |     |

| Nonvolatile Data Storage                                     | 134 |

PS025113-1212 Table of Contents

## Z8 Encore!® F0830 Series Product Specification

xiv

| Table 59. | Watchdog Timer Control Register (WDTCTL)           |

|-----------|----------------------------------------------------|

| Table 60. | Watchdog Timer Reload Upper Byte Register (WDTU)   |

| Table 61. | Watchdog Timer Reload High Byte Register (WDTH) 9  |

| Table 62. | Watchdog Timer Reload Low Byte Register (WDTL) 9   |

| Table 63. | ADC Control Register 0 (ADCCTL0)                   |

| Table 64. | ADC Data High Byte Register (ADCD_H)               |

| Table 65. | ADC Data Low Bits Register (ADCD_L)                |

| Table 66. | Sample Settling Time (ADCSST)                      |

| Table 67. | Sample Time (ADCST)                                |

| Table 68. | Comparator Control Register (CMP0)                 |

| Table 69. | Z8 Encore! F0830 Series Flash Memory Configuration |

| Table 70. | Z8F083 Flash Memory Area Map                       |

| Table 71. | Flash Code Protection using the Flash Option Bits  |

| Table 72. | Flash Control Register (FCTL)                      |

| Table 73. | Flash Status Register (FSTAT)                      |

| Table 74. | Flash Page Select Register (FPS)                   |

| Table 75. | Flash Sector Protect Register (FPROT)              |

| Table 76. | Flash Frequency High Byte Register (FFREQH)        |

| Table 77. | Flash Frequency Low Byte Register (FFREQL)         |

| Table 78. | Trim Bit Address Register (TRMADR)                 |

| Table 79. | Trim Bit Address Map                               |

| Table 80. | Trim Bit Data Register (TRMDR)                     |

| Table 81. | Flash Option Bits at Program Memory Address 0000H  |

| Table 82. | Flash Options Bits at Program Memory Address 0001H |

| Table 83. | Trim Option Bits at 0000H (ADCREF)                 |

| Table 84. | Trim Option Bits at 0001H (TADC_COMP)              |

| Table 85. | Trim Bit Address Space                             |

| Table 86. | Trim Option Bits at 0002H (TIPO)                   |

| Table 87. | Trim Option Bits at 0003H (TVBO)                   |

| Table 88. | VBO Trim Definition                                |

PS025113-1212 List of Tables

Table 8. Register File Address Map (Continued)

| Address (Hex)    | Register Description             | Mnemonic | Reset (Hex) | Page No. |

|------------------|----------------------------------|----------|-------------|----------|

| Interrupt Contro | eller (cont'd)                   |          |             |          |

| FCE              | Shared interrupt select          | IRQSS    | 00          | 66       |

| FCF              | Interrupt control                | IRQCTL   | 00          | 67       |

| GPIO Port A      |                                  |          |             |          |

| FD0              | Port A address                   | PAADDR   | 00          | 39       |

| FD1              | Port A control                   | PACTL    | 00          | 41       |

| FD2              | Port A input data                | PAIN     | XX          | 41       |

| FD3              | Port A output data               | PAOUT    | 00          | 41       |

| GPIO Port B      |                                  |          |             |          |

| FD4              | Port B address                   | PBADDR   | 00          | 39       |

| FD5              | Port B control                   | PBCTL    | 00          | 41       |

| FD6              | Port B input data                | PBIN     | XX          | 41       |

| FD7              | Port B output data               | PBOUT    | 00          | 41       |

| GPIO Port C      |                                  |          |             |          |

| FD8              | Port C address                   | PCADDR   | 00          | 39       |

| FD9              | Port C control                   | PCCTL    | 00          | 41       |

| FDA              | Port C input data                | PCIN     | XX          | 41       |

| FDB              | Port C output data               | PCOUT    | 00          | 41       |

| GPIO Port D      |                                  |          |             |          |

| FDC              | Port D address                   | PDADDR   | 00          | 39       |

| FDD              | Port D control                   | PDCTL    | 00          | 41       |

| FDE              | Reserved                         | _        | XX          |          |

| FDF              | Port D output data               | PDOUT    | 00          | 41       |

| FE0-FEF          | Reserved                         | _        | XX          |          |

| Watchdog Time    | r (WDT)                          |          |             |          |

| FF0              | Reset status                     | RSTSTAT  | XX          | 95       |

|                  | Watchdog Timer control           | WDTCTL   | XX          | 95       |

| FF1              | Watchdog Timer reload upper byte | WDTU     | FF          | 96       |

| FF2              | Watchdog Timer reload high byte  | WDTH     | FF          | 96       |

| FF3              | Watchdog Timer reload low byte   | WDTL     | FF          | 97       |

| FF4–FF5          | Reserved                         | _        | XX          |          |

Note: XX = Undefined.

PS025113-1212 Register Map

### **Reset Sources**

Table 10 lists the possible sources of a system reset.

Table 10. Reset Sources and Resulting Reset Type

| Operating Mode       | Reset Source                                          | Special Conditions                                                  |

|----------------------|-------------------------------------------------------|---------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-Out                      | Reset delay begins after supply voltage exceeds POR level.          |

|                      | Watchdog Timer time-out when configured for reset     | None.                                                               |

|                      | RESET pin assertion                                   | All reset pulses less than four system clocks in width are ignored. |

|                      | On-Chip Debugger initiated reset (OCDCTL[0] set to 1) | System, except the On-Chip Debugger is unaffected by the reset.     |

| STOP Mode            | Power-On Reset/Voltage Brown-Out                      | Reset delay begins after supply voltage exceeds POR level.          |

|                      | RESET pin assertion                                   | All reset pulses less than 12 ns are ignored.                       |

|                      | DBG pin driven Low                                    | None.                                                               |

#### **Power-On Reset**

Each device in the Z8 Encore! F0830 Series contains an internal Power-On Reset circuit. The POR circuit monitors the digital supply voltage and holds the device in the Reset state until the digital supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR counter has timed out. If the crystal oscillator is enabled by the option bits, the timeout is longer.

After the Z8 Encore! F0830 Series device exits the Power-On Reset state, the eZ8 CPU fetches the reset vector. Following the Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1.

Figure 6 displays the Power-On Reset operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the POR threshold voltage  $(V_{POR})$ .

PS025113-1212 Reset Sources

Note:

This register is only reset during a Power-On Reset sequence. Other system reset events do not affect it.

Table 14. Power Control Register 0 (PWRCTL0)

| Bit     | 7        | 6    | 5   | 4   | 3        | 2        | 1    | 0        |

|---------|----------|------|-----|-----|----------|----------|------|----------|

| Field   | Reserved |      |     | VBO | Reserved | Reserved | COMP | Reserved |

| RESET   | 1        | 0    | 0   | 0   | 1        | 0        | 0    | 0        |

| R/W     | R/W      | R/W  | R/W | R/W | R/W      | R/W      | R/W  | R/W      |

| Address |          | F80H |     |     |          |          |      |          |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]       | Reserved These registers are reserved and must be programmed to 000.                                                                                                                                                                                                                                                                         |

| [4]<br>VBO  | Voltage Brown-Out detector disable This bit takes only effect when the VBO_AO Flash option bit is disabled. In STOP Mode, VBO is always disabled when the VBO_AO Flash option bit is disabled. To learn more about the VBO_AO Flash option bit function, see the Flash Option Bits chapter on page 124.  0 = VBO enabled.  1 = VBO disabled. |

| [3]         | Reserved This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                   |

| [2]         | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                   |

| [1]<br>COMP | Comparator Disable 0 = Comparator is enabled. 1 = Comparator is disabled.                                                                                                                                                                                                                                                                    |

| [0]         | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                   |

### Port A-D Stop Mode Recovery Source Enable Subregisters

The Port A–D Stop Mode Recovery Source Enable Subregister, shown in Table 25, is accessed through the Port A–D Control Register by writing 05H to the Port A–D Address Register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable subregisters to 1 configures the specified port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a port pin enabled as a Stop Mode Recovery source initiates a Stop Mode Recovery event.

Table 25. Port A-D Stop Mode Recovery Source Enable Subregisters (PxSMRE)

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Field   | PSMRE7    | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |

| RESET   | 0         | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | If 05H ir | If 05H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |

#### Bit Description

### [7:0] Port Stop Mode Recovery Source Enable

PSMREx 0 = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7–0).

#### Bit Description (Continued)

#### [6] Timer Input/Output Polarity

TPOL Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### **COUNTER Mode**

If the timer is disabled, the timer output signal is set to the value of this bit. If the timer is enabled the timer output signal is complemented after timer reload.

- 0 = Count occurs on the rising edge of the timer input signal.

- 1 = Count occurs on the falling edge of the timer input signal.

#### **PWM SINGLE OUTPUT Mode**

- 0 = Timer output is forced Low (0), when the timer is disabled. The timer output is forced High (1) when the timer is enabled and the PWM count matches and the timer output is forced Low (0) when the timer is enabled and reloaded.

- 1 = Timer output is forced High (1), when the timer is disabled. The timer output is forced low(0), when the timer is enabled and the PWM count matches and forced High (1) when the timer is enabled and reloaded.

#### **CAPTURE Mode**

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### **COMPARE Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### **GATED Mode**

- 0 = Timer counts when the timer input signal is High (1) and interrupts are generated on the falling edge of the timer input.

- 1 = Timer counts when the timer input signal is Low (0) and interrupts are generated on the rising edge of the timer input.

#### **CAPTURE/COMPARE Mode**

- 0 = Counting is started on the first rising edge of the timer input signal. The current count is captured on subsequent rising edges of the timer input signal.

- 1 = Counting is started on the first falling edge of the timer input signal. The current count is captured on subsequent falling edges of the timer input signal.

## **ADC Control Register 0**

The ADC Control 0 Register, shown in Table 63, initiates an A/D conversion and provides ADC status information.

Table 63. ADC Control Register 0 (ADCCTL0)

| Bit     | 7     | 6        | 5     | 4     | 3        | 2   | 1          | 0   |

|---------|-------|----------|-------|-------|----------|-----|------------|-----|

| Field   | START | Reserved | REFEN | ADCEN | Reserved |     | ANAIN[2:0] |     |

| RESET   | 0     | 0        | 0     | 0     | 0        | 0   | 0          | 0   |

| R/W     | R/W1  | R/W      | R/W   | R/W   | R/W      | R/W | R/W        | R/W |

| Address |       | F70h     |       |       |          |     |            |     |

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>START   | <ul> <li>ADC Start/Busy</li> <li>0 = Writing to 0 has no effect; reading a 0 indicates that the ADC is available to begin a conversion.</li> <li>1 = Writing to 1 starts a conversion; reading a 1 indicates that a conversion is currently in progress.</li> </ul>                                                                                                                                                                                                                                                                                 |

| [6]            | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [5]<br>REFEN   | Reference Enable  0 = Internal reference voltage is disabled allowing an external reference voltage to be used by the ADC.  1 = Internal reference voltage for the ADC is enabled. The internal reference voltage can be measured on the V <sub>REF</sub> pin.                                                                                                                                                                                                                                                                                      |

| [4]<br>ADCEN   | ADC Enable 0 = ADC is disabled for low power operation. 1 = ADC is enabled for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [3]            | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [2:0]<br>ANAIN | Analog Input Select  000 = ANA0 input is selected for analog to digital conversion.  001 = ANA1 input is selected for analog to digital conversion.  010 = ANA2 input is selected for analog to digital conversion.  011 = ANA3 input is selected for analog to digital conversion.  100 = ANA4 input is selected for analog to digital conversion.  101 = ANA5 input is selected for analog to digital conversion.  110 = ANA6 input is selected for analog to digital conversion.  111 = ANA7 input is selected for analog to digital conversion. |

### **Sample Settling Time Register**

The <u>Sample Settling Time Register</u>, shown in Table 66, is used to program a delay after the <u>SAMPLE/HOLD</u> signal is asserted and before the START signal is asserted; an ADC conversion then begins. The number of clock cycles required for settling will vary from system to system depending on the system clock period used. The system designer should program this register to contain the number of clocks required to meet a  $0.5\,\mu s$  minimum settling time.

**Table 66. Sample Settling Time (ADCSST)**

| Bit     | 7        | 6 | 5 | 4 | 3 | 2  | 1  | 0 |

|---------|----------|---|---|---|---|----|----|---|

| Field   | Reserved |   |   |   |   | SS | ST |   |

| RESET   | 0        |   |   |   | 1 | 1  | 1  | 1 |

| R/W     |          | F | ₹ |   |   | R/ | W  |   |

| Address | F74H     |   |   |   |   |    |    |   |

| Bit          | Description                                                                            |

|--------------|----------------------------------------------------------------------------------------|

| [7:4]        | Reserved These bits are reserved and must be programmed to 0000.                       |

| [3:0]<br>SST | 0h–Fh = Sample settling time in number of system clock periods to meet 0.5 μs minimum. |

## **Comparator Control Register Definitions**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference. The GPIO pin is always used as positive comparator input.

Table 68. Comparator Control Register (CMP0)

| Bit     | 7        | 6      | 5                   | 4               | 3 | 2 | 1 | 0 |  |  |  |  |  |

|---------|----------|--------|---------------------|-----------------|---|---|---|---|--|--|--|--|--|

| Field   | Reserved | INNSEL |                     | REFLVL Reserved |   |   |   |   |  |  |  |  |  |

| RESET   | 0        | 0      | 0                   | 1               | 0 | 1 | 0 | 0 |  |  |  |  |  |

| R/W     | R/W      | R/W    | R/W R/W R/W R/W R/W |                 |   |   |   |   |  |  |  |  |  |

| Address |          | F90H   |                     |                 |   |   |   |   |  |  |  |  |  |

| Bit             | Description                                                                                                                                                                                                                                                               |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]             | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                |

| [6]<br>INNSEL   | Signal Select for Negative Input 0 = internal reference disabled, GPIO pin used as negative comparator input. 1 = internal reference enabled as negative comparator input.                                                                                                |

| [5:2]<br>REFLVL | Internal Reference Voltage Level This reference is independent of the ADC voltage reference.  0000 = 0.0 V. 0001 = 0.2 V. 0010 = 0.4 V. 0011 = 0.6 V. 0100 = 0.8 V. 0101 = 1.0 V (Default). 0110 = 1.2 V. 0111 = 1.4 V. 1000 = 1.6 V. 1001 = 1.8 V. 1010-1111 = Reserved. |

| [1:0]           | Reserved These bits are reserved and must be programmed to 00.                                                                                                                                                                                                            |

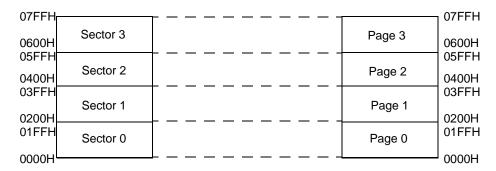

Figure 15. 2K Flash with NVDS

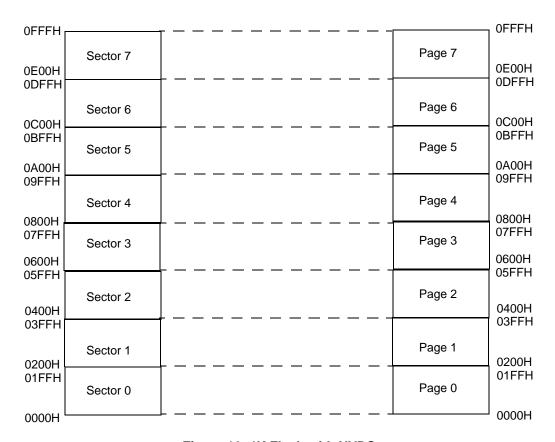

Figure 16. 4K Flash with NVDS

PS025113-1212 Flash Memory

Table 71. Flash Code Protection using the Flash Option Bits

| FHSWP  | FWP | Flash Code Protection Description                                                                                                                                                          |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | Programming and erasing disabled for all Flash program memory. In user code programming, page erase and mass erase are all disabled. Mass erase is available through the On-Chip Debugger. |

| 0 or 1 | 1   | Programming, page erase and mass erase are enabled for all of the Flash program memory.                                                                                                    |

At reset, the Flash Controller is locked to prevent accidental program or erasure of Flash memory. To program or erase Flash memory, first write the target page to the page select register. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The page select register must be rewritten with the same page previously stored there. If the two page select writes do not match, the controller reverts to a Locked state. If the two writes match, the selected page becomes active. See Figure 19 for details.

After unlocking a specific page, you can enable either page program or erase. Writing the value 95H causes a page erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass erase is not allowed in the user code, but is allowed through the debug port.

After unlocking a specific page, the user can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register causes the active page to revert to a Locked state.

#### **Sector Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! devices are divided into maximum number of eight sectors. A sector is one-eighth of the total size of Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal. On Z8 Encore! F0830 Series devices, the sector size is varied according to the Z8 Encore! F0830 Series Flash Memory Configuration shown in Table 69 on page 108 and in Figures 14 through 18, which follow the table

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset and any previously written protection values is lost. User code must write this register in their initialization routine if they want to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

PS025113-1212 Operation

- The Flash Sector Protect Register is ignored for programming and Erase operations.

- Programming operations are not limited to the page selected in the page select register.

- Bits in the Flash Sector Protect Register can be written to one or zero.

- The second write of the page select register to unlock the Flash Controller is not necessary.

- The page select register can be written when the Flash Controller is unlocked.

- The mass erase command is enabled through the Flash Control Register

**Caution:** For security reasons, Flash Controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the Flash Controller must go through the unlock sequence again to select another page.

### **NVDS Operational Requirements**

The device uses a 12 KB Flash memory space, despite the maximum specified Flash size of 8 KB (with the exception of 12 KB mode with non-NVDS). User code accesses the lower 8 KB of Flash, leaving the upper 4 KB for proprietary (for Zilog-only) memory. The NVDS is implemented by using this proprietary memory space for special-purpose routines and for the data required by these routines, which are factory-programmed and cannot be altered by the user. The NVDS operation is described in detail in *the* Nonvolatile Data Storage *chapter on page 134*.

The NVDS routines are triggered by a user code: CALL into proprietary memory. Code executing from this proprietary memory must be able to read and write other locations within proprietary memory. User code must not be able to read or write proprietary memory.

## Flash Control Register Definitions

This section defines the features of the following Flash Control registers.

<u>Flash Control Register</u>: see page 119 <u>Flash Status Register</u>: see page 120

<u>Flash Page Select Register</u>: see page 121 <u>Flash Sector Protect Register</u>: see page 122

Flash Frequency High and Low Byte Registers: see page 123

#### **Power Failure Protection**

NVDS routines employ error-checking mechanisms to ensure that any power failure will only endanger the most recently written byte. Bytes previously written to the array are not perturbed. For this protection to function, the VBO must be enabled (see the <u>Low-Power Modes</u> chapter on page 30) and configured for a threshold voltage of 2.4V or greater (see *the* <u>Trim Bit Address Space</u> *section on page 129*).

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

### **Optimizing NVDS Memory Usage for Execution Speed**

As indicated in Table 93, the NVDS read time varies drastically; this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N as well as the number of writes since the most recent page erase. Neglecting the effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb to consider is that every write since the most recent page erase causes read times of unwritten addresses to increase by  $0.8\mu s$  up to a maximum of  $258\mu s$ .

Table 93. NVDS Read Time

| Operation     | Minimum<br>Latency (µs) | Maximum<br>Latency (µs) |

|---------------|-------------------------|-------------------------|

| Read          | 71                      | 258                     |

| Write         | 126                     | 136                     |

| Illegal Read  | 6                       | 6                       |

| Illegal Write | 7                       | 7                       |

Note:

For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write takes up to 58ms to complete.

If NVDS read performance is critical to your software architecture, you can optimize your code for speed by using either of the two methods listed below.

1. Periodically refresh all addresses that are used; this is the more useful method. The optimal use of NVDS, in terms of speed, is to rotate the writes evenly among all addresses planned for use, thereby bringing all reads closer to the minimum read time.

PS025113-1212 NVDS Code Interface

# Crystal Oscillator

The products in the Z8 Encore! F0830 Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of its on-chip peripherals. Alternatively, the  $X_{\rm IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{\rm OUT}$  pin must remain unconnected. The on-chip crystal oscillator also contains a clock filter function. To see the settings for this clock filter, see Table 90 on page 133. By default, however, this clock filter is disabled; therefore, no divide to the input clock (namely, the frequency of the signal on the  $X_{\rm IN}$  input pin) can determine the frequency of the system clock when using the default settings.

Note:

Although the  $X_{IN}$  pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use. See *the* System Clock Selection section on page 151 for more information.

## **Operating Modes**

The Z8 Encore! F0830 Series products support the following four OSCILLATOR Modes:

- Minimum power for use with very low frequency crystals (32kHz to 1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8 MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The OSCILLATOR Mode is selected using user-programmable Flash option bits. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

## **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Reg-

PS025113-1212 Crystal Oscillator

**Table 105. Arithmetic Instructions (Continued)**

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

**Table 106. Bit Manipulation Instructions**

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| TCM      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| TM       | dst, src    | Test Under Mask                                      |

| TMX      | dst, src    | Test Under Mask using Extended Addressing            |

**Table 107. Block Transfer Instructions**

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

Table 113. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                                     |     | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | Fetch | Instr. |

|---------------|-------------------------------------|-----|-------------|---------------|---|---|-----|-----|---|---|-------|--------|

| Mnemonic      | Symbolic Operation                  | dst | src         | (Hex)         | С | Z | S   | ٧   | D | Н |       | Cycles |

| SRA dst       |                                     | R   |             | D0            | * | * | *   | 0   | _ | _ | 2     | 2      |

|               | D7 D6 D5 D4 D3 D2 D1 D0 C           | IR  |             | D1            | _ |   |     |     |   |   | 2     | 3      |

| SRL dst       | 0 - D7 D6 D5 D4 D3 D2 D1 D0 C       | R   |             | 1F C0         | * | * | 0   | *   | _ | _ | 3     | 2      |

|               | dst                                 | IR  |             | 1F C1         | _ |   |     |     |   |   | 3     | 3      |

| SRP src       | RP ← src                            |     | IM          | 01            | _ | - | -   | -   | - | - | 2     | 2      |

| STOP          | STOP Mode                           |     |             | 6F            | _ | _ | _   | -   | - | _ | 1     | 2      |

| SUB dst, src  | dst ← dst – src                     | r   | r           | 22            | * | * | *   | *   | 1 | * | 2     | 3      |

|               | -                                   | r   | lr          | 23            | _ |   |     |     |   |   | 2     | 4      |

|               | -                                   | R   | R           | 24            | _ |   |     |     |   |   | 3     | 3      |

|               | -<br>-                              | R   | IR          | 25            | _ |   |     |     |   |   | 3     | 4      |

|               | -                                   | R   | IM          | 26            | _ |   |     |     |   |   | 3     | 3      |

|               | -                                   | IR  | IM          | 27            | _ |   |     |     |   |   | 3     | 4      |

| SUBX dst, src | dst ← dst – src                     | ER  | ER          | 28            | * | * | *   | *   | 1 | * | 4     | 3      |

|               |                                     | ER  | IM          | 29            | _ |   |     |     |   |   | 4     | 3      |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$ | R   |             | F0            | Χ | * | *   | Χ   | - | _ | 2     | 2      |

|               | -                                   | IR  |             | F1            | _ |   |     |     |   |   | 2     | 3      |

| TCM dst, src  | (NOT dst) AND src                   | r   | r           | 62            | - | * | *   | 0   | - | - | 2     | 3      |

|               |                                     | r   | lr          | 63            | _ |   |     |     |   |   | 2     | 4      |

|               |                                     | R   | R           | 64            | _ |   |     |     |   |   | 3     | 3      |

|               | -                                   | R   | IR          | 65            | _ |   |     |     |   |   | 3     | 4      |

|               | -                                   | R   | IM          | 66            |   |   |     |     |   |   | 3     | 3      |

|               |                                     | IR  | IM          | 67            |   |   |     |     |   |   | 3     | 4      |

| TCMX dst, src | (NOT dst) AND src                   | ER  | ER          | 68            | _ | * | *   | 0   | - | _ | 4     | 3      |

|               |                                     | ER  | IM          | 69            |   |   |     |     |   |   | 4     | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Figures 29 and 30 provide information about each of the eZ8 CPU instructions.

| Rt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                    |                    |                    |                    |                   |                   | Lo                | ower Nil          | oble (He           | x)                 |          |    |    |    |     |                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|----------|----|----|----|-----|---------------------------|

| BRK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 0                  | 1                  | 2                  | 3                  | 4                 | 5                 | 6                 | 7                 | 8                  | 9                  | Α        | В  | С  | D  | Е   | F                         |

| Table   Tabl   | 0 |                    | SRP                | ADD                | ADD                | ADD               | ADD               | ADD               | ADD               | ADDX               | ADDX               | DJNZ     | JR | LD | JP | INC | 1.2<br><b>NOP</b>         |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | RLC                | RLC                | ADC                | ADC                | ADC               | ADC               | ADC               | ADC               | ADCX               | ADCX               |          |    |    |    |     | See 2nd<br>Op Code<br>Map |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 | INC                | INC                | 2.3<br><b>SUB</b>  | 2.4<br><b>SUB</b>  | 3.3<br><b>SUB</b> | 3.4<br><b>SUB</b> | 3.3<br><b>SUB</b> | 3.4<br><b>SUB</b> | 4.3<br>SUBX        | 4.3<br>SUBX        |          |    |    |    |     | ·                         |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3 | 2.2<br><b>DEC</b>  | 2.3<br><b>DEC</b>  | 2.3<br><b>SBC</b>  | 2.4<br><b>SBC</b>  | 3.3<br><b>SBC</b> | 3.4<br><b>SBC</b> | 3.3<br><b>SBC</b> | 3.4<br><b>SBC</b> | SBCX               | SBCX               |          |    |    |    |     |                           |

| The image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4 | 2.2<br><b>DA</b>   | 2.3<br><b>DA</b>   | 2.3<br><b>OR</b>   | 2.4<br><b>OR</b>   | 3.3<br><b>OR</b>  | 3.4<br><b>OR</b>  | 3.3<br><b>OR</b>  | 3.4<br><b>OR</b>  | 4.3<br><b>ORX</b>  | 4.3<br><b>ORX</b>  |          |    |    |    |     |                           |

| COM   COM   TCM    | 5 | 2.2<br><b>POP</b>  | 2.3<br><b>POP</b>  | 2.3<br><b>AND</b>  | 2.4<br><b>AND</b>  | 3.3<br><b>AND</b> | 3.4<br><b>AND</b> | 3.3<br><b>AND</b> | 3.4<br><b>AND</b> | 4.3<br><b>ANDX</b> | 4.3<br><b>ANDX</b> |          |    |    |    |     | 1.2<br><b>WDT</b>         |

| PUSH PUSH TM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _ | 2.2<br><b>COM</b>  | 2.3<br><b>COM</b>  | 2.3<br><b>TCM</b>  | 2.4<br><b>TCM</b>  | 3.3<br><b>TCM</b> | 3.4<br><b>TCM</b> | 3.3<br><b>TCM</b> | 3.4<br><b>TCM</b> | 4.3<br><b>TCMX</b> | 4.3<br>TCMX        |          |    |    |    |     | stop                      |

| 9 RL RL LDE LDEI LDX LDX LDX LDX LEA LEA R1 IR1 r2,Irr1 Ir2,Irr1 r2,ER1 Ir2,ER1 R2,IRR1 IR2,IRR1 r1,r2,X r1,rr2,X r1,rr2,X r2,5 2.6 2.3 2.4 3.3 3.4 4.3 4.3 4.3 4.3 4.3 4.3 4.3 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7 | 2.2<br><b>PUSH</b> | 2.3<br><b>PUSH</b> | 2.3<br><b>TM</b>   | 2.4<br><b>TM</b>   | 3.3<br><b>TM</b>  | 3.4<br><b>TM</b>  | 3.3<br><b>TM</b>  | 3.4<br><b>TM</b>  | 4.3<br><b>TMX</b>  | 4.3<br><b>TMX</b>  |          |    |    |    |     | 1.2<br>HALT               |

| 9 RL RL LDE LDEI LDX LDX LDX LDX LEA LEA R1 IR1 r2,Irr1   r2,ER1   r2,ER1   r2,ER1   r2,ER1   r1,r2,X   r1,r2,X   r1,r2,X   r1,r2,X   r1,r2,X   r2,5   2.6   2.3   2.4   3.3   3.4   3.3   3.4   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   | 8 | 2.5<br><b>DECW</b> | 2.6<br><b>DECW</b> | 2.5<br><b>LDE</b>  | 2.9<br><b>LDEI</b> | 3.2<br><b>LDX</b> | 3.3<br><b>LDX</b> | 3.4<br><b>LDX</b> | 3.5<br><b>LDX</b> | 3.4<br><b>LDX</b>  | 3.4<br><b>LDX</b>  |          |    |    |    |     | 1.2<br><b>DI</b>          |

| A   2.5   2.6   2.3   2.4   3.3   3.4   3.3   3.4   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4.3   4. |   | 2.2<br><b>RL</b>   | 2.3<br><b>RL</b>   | 2.5<br><b>LDE</b>  | 2.9<br><b>LDEI</b> | 3.2<br><b>LDX</b> | 3.3<br><b>LDX</b> | 3.4<br><b>LDX</b> | 3.5<br><b>LDX</b> | 3.3<br><b>LEA</b>  | 3.5<br><b>LEA</b>  |          |    |    |    |     | 1.2<br><b>El</b>          |

| B CLR CLR XOR XOR XOR XOR XOR XOR XOR XOR XOR XO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Α | 2.5<br>INCW        | 2.6<br>INCW        | 2.3<br><b>CP</b>   | 2.4<br><b>CP</b>   | 3.3<br><b>CP</b>  | 3.4<br><b>CP</b>  | 3.3<br><b>CP</b>  | 3.4<br><b>CP</b>  | 4.3<br><b>CPX</b>  | 4.3<br><b>CPX</b>  |          |    |    |    |     | 1.4<br>RET                |

| C RC RC LDC LDCI JP LDC LDC LDCI R1 IR1 IR1 IR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR1 IR2 IRR1 IR1 IR1 IR1 IR1 IR1 IR1 IR1 IR1 IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | В | 2.2<br><b>CLR</b>  | 2.3<br><b>CLR</b>  | 2.3<br><b>XOR</b>  | 2.4<br><b>XOR</b>  | 3.3<br><b>XOR</b> | 3.4<br><b>XOR</b> | 3.3<br><b>XOR</b> | 3.4<br><b>XOR</b> | XORX               | XORX               |          |    |    |    |     | 1.5<br>IRET               |