# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-VQFN Exposed Pad                                       |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0130qh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Revision History                   | ii |

|------------------------------------|----|

| List of Figures                    | х  |

| List of Tables x                   | ii |

| Overview                           | 1  |

| Features                           | 1  |

| Part Selection Guide               | 2  |

| Block Diagram                      | 3  |

| CPU and Peripheral Overview        | 4  |

| General Purpose Input/Output       | 4  |

| Flash Controller                   | 4  |

| Nonvolatile Data Storage           | 5  |

| Internal Precision Oscillator      | 5  |

| External Crystal Oscillator        | 5  |

| 10-Bit Analog-to-Digital Converter | 5  |

| Analog Comparator                  | 5  |

| Timers                             | 5  |

| Interrupt Controller               | 5  |

| Reset Controller                   | 6  |

| On-Chip Debugger                   | 6  |

| Acronyms and Expansions            | 6  |

| Pin Description                    | 7  |

| Available Packages                 |    |

| Pin Configurations                 | 7  |

| Signal Descriptions                | 1  |

| Pin Characteristics                |    |

| Address Space                      | 4  |

| Register File                      |    |

| Program Memory                     | 5  |

| Data Memory                        |    |

| Flash Information Area 1           |    |

| Register Map 1                     | 7  |

| Reset and Stop Mode Recovery       | 21 |

| Reset Types                        |    |

| Reset Sources                      |    |

| Power-On Reset                     |    |

# **Address Space**

The eZ8 CPU can access the following three distinct address spaces:

- The register file addresses access for the general purpose registers and the eZ8 CPU, peripheral and general purpose I/O port control registers

- The program memory addresses access for all of the memory locations having executable code and/or data

- The data memory addresses access for all of the memory locations containing only the data

The following sections describe these three address spaces. For more information about the eZ8 CPU and its address space, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download at <u>www.zilog.com</u>.

# **Register File**

The register file address space in the Z8 Encore! MCU is 4KB (4096 bytes). The register file consists of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as *source* are read and registers defined as *destinations* are written. The architecture of the eZ8 CPU allows all general purpose registers to function as accumulators, address pointers, index registers, stack areas or scratch pad memory.

The upper 256 bytes of the 4KB register file address space are reserved for controlling the eZ8 CPU, on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256B Control Register section are reserved (unavailable). Reading from a reserved register file address returns an undefined value. Writing to reserved register file addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the register file address space. The Z8 Encore! F0830 Series devices contain up to 256B of on-chip RAM. Reading from register file addresses outside the available RAM addresses (and not within the Control Register address space), returns an undefined value. Writing to these register file addresses has no effect.

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# Architecture

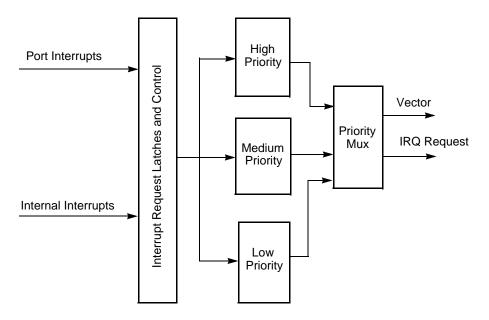

Figure 9 displays the Interrupt Controller block diagram.

Figure 9. Interrupt Controller Block Diagram

# Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 55

Interrupt Vectors and Priority: see page 56

Interrupt Assertion: see page 56

Software Interrupt Assertion: see page 57

# **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables the interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (enable interrupt) instruction

- Execution of an IRET (return from interrupt) instruction

## 73

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer reload in COMPARATOR COUNTER Mode, counting always begins at the reset value 0001H. Generally, in COMPARATOR COUNTER Mode, the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions is calculated with the following equation:

Comparator Output Transitions = Current Count Value – Start Value

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines whether the capture occurs on a rising edge or a falling edge of the timer input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt has been caused by an input capture event.

If no capture event occurs, the timer counts up to 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

## Watchdog Timer Refresh

Upon first enable, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the Reload operation.

When the Z8 Encore! F0830 Series devices are operating in DEBUG Mode (using the On-Chip Debugger), the Watchdog Timer must be continuously refreshed to prevent any WDT time-outs.

## Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash option bit determines the time-out response of the Watchdog Timer. See *the* <u>Flash Option</u> <u>Bits</u> chapter on page 124 for information about programming the WDT\_RES Flash option bit.

## **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the Interrupt Controller and sets the WDT status bit in the Reset Status Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter resets to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter will not automatically return to its reload value.

The Reset Status Register (see <u>Table 12</u> on page 29) must be read before clearing the WDT interrupt. This read clears the WDT time-out flag and prevents further WDT interrupts occurring immediately.

## WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! F0830 Series devices are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. See *the* <u>Reset and Stop Mode Recovery</u> *chapter on page 21* for more information about Stop Mode Recovery operations.

If interrupts are enabled, following completion of the Stop Mode Recovery, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executes the code from the vector address.

## ADC Data High Byte Register

The ADC Data High Byte Register, listed in Table 64, contains the upper eight bits of the ADC output. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

### Table 64. ADC Data High Byte Register (ADCD\_H)

| Bit     | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-------|---|---|---|---|---|---|---|

| Field   | ADCDH |   |   |   |   |   |   |   |

| RESET   |       | Х |   |   |   |   |   |   |

| R/W     | R     |   |   |   |   |   |   |   |

| Address | F72H  |   |   |   |   |   |   |   |

|         |       |   |   |   |   |   |   |   |

| Bit   | Description                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------|

| [7:0] | ADC High Byte                                                                                                       |

| ADCDH | 00h–FFh = The last conversion output is held in the data registers until the next ADC conver-<br>sion is completed. |

## ADC Data Low Bits Register

The ADC Data Low Bits Register, shown in Table 65, contains the lower bits of the ADC output. Access to the ADC Data Low Bits Register is read-only. Reading the ADC Data High Byte Register latches lower bits of the ADC in the ADC Data Low Bits Register.

| Bit     | 7     | 6 | 5        | 4 | 3 | 2 | 1 | 0 |

|---------|-------|---|----------|---|---|---|---|---|

| Field   | ADCDL |   | Reserved |   |   |   |   |   |

| RESET   | Х     |   | X        |   |   |   |   |   |

| R/W     | F     | २ |          | R |   |   |   |   |

| Address | F73H  |   |          |   |   |   |   |   |

| Table 65. | ADC Data L | ow Bits R | Register (A | ADCD_L) |

|-----------|------------|-----------|-------------|---------|

|-----------|------------|-----------|-------------|---------|

| Bit            | Description                                                                                                                                                                                                                                  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]<br>ADCDL | ADC Low Bits<br>00–11b = These bits are the two least-significant bits of the 10-bit ADC output. These bits are<br>undefined after a reset. The low bits are latched into this register whenever the ADC Data High<br>Byte Register is read. |

| [5:0]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                 |

## Sample Settling Time Register

The <u>Sample Settling</u> Time Register, shown in Table 66, is used to program a delay after the <u>SAMPLE/HOLD</u> signal is asserted and before the START signal is asserted; an ADC conversion then begins. The number of clock cycles required for settling will vary from system to system depending on the system clock period used. The system designer should program this register to contain the number of clocks required to meet a  $0.5 \mu s$  minimum settling time.

| Bit     | 7    | 6    | 5     | 4 | 3 | 2  | 1  | 0 |

|---------|------|------|-------|---|---|----|----|---|

| Field   |      | Rese | erved |   |   | S  | ST |   |

| RESET   | 0    |      |       |   | 1 | 1  | 1  | 1 |

| R/W     |      | F    | २     |   |   | R/ | W  |   |

| Address | F74H |      |       |   |   |    |    |   |

## Table 66. Sample Settling Time (ADCSST)

| Bit          | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                  |

| [3:0]<br>SST | 0h–Fh = Sample settling time in number of system clock periods to meet 0.5 $\mu$ s minimum. |

# Flash Memory

The products in the Z8 Encore! F0830 Series features either 1KB (1024 bytes with NVDS), 2KB (2048 bytes with NVDS), 4KB (4096 bytes with NVDS), 8KB (8192 bytes with NVDS) or 12KB (12288 bytes with no NVDS) of nonvolatile Flash memory with read/write/erase capability. Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F0830 Series, each sector maps to one page (for 1KB, 2KB and 4KB devices), two pages (8KB device) or three pages (12KB device).

The first two bytes of Flash program memory is used as Flash option bits. For more information, see *the* <u>Flash Option Bits</u> chapter on page 124.

Table 69 lists the Flash memory configuration for each device in the Z8 Encore! F0830 Series. Figures 14 through 18 display the memory arrangements for each Flash memory size.

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F123x     | 12 (12,288)              | 24          | 0000H–2FFFH                    | 1536                         |

| Z8F083x     | 8 (8196)                 | 16          | 0000H-1FFFH                    | 1024                         |

| Z8F043x     | 4 (4096)                 | 8           | 0000H–0FFFH                    | 512                          |

| Z8F023x     | 2 (2048)                 | 4           | 0000H–07FFH                    | 512                          |

| Z8F013x     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

Figure 14. 1K Flash with NVDS

<sup>03</sup>FFH

03FFH

03FFH

0200H

Sector 1

Page 1

0200H

01FFH

Sector 0

Page 0

01FFh

0000H

0000H

0000H

0000H

| FHSWP  | FWP | Flash Code Protection Description                                                                                                                                                                  |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | Programming and erasing disabled for all Flash program memory. In user code pro-<br>gramming, page erase and mass erase are all disabled. Mass erase is available<br>through the On-Chip Debugger. |

| 0 or 1 | 1   | Programming, page erase and mass erase are enabled for all of the Flash program memory.                                                                                                            |

#### Table 71. Flash Code Protection using the Flash Option Bits

At reset, the Flash Controller is locked to prevent accidental program or erasure of Flash memory. To program or erase Flash memory, first write the target page to the page select register. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The page select register must be rewritten with the same page previously stored there. If the two page select writes do not match, the controller reverts to a Locked state. If the two writes match, the selected page becomes active. See Figure 19 for details.

After unlocking a specific page, you can enable either page program or erase. Writing the value 95H causes a page erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass erase is not allowed in the user code, but is allowed through the debug port.

After unlocking a specific page, the user can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register causes the active page to revert to a Locked state.

#### **Sector Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! devices are divided into maximum number of eight sectors. A sector is oneeighth of the total size of Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal. On Z8 Encore! F0830 Series devices, the sector size is varied according to the Z8 Encore! F0830 Series Flash Memory Configuration shown in Table 69 on page 108 and in Figures 14 through 18, which follow the table

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset and any previously written protection values is lost. User code must write this register in their initialization routine if they want to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

## Flash Frequency High and Low Byte Registers

The Flash Frequency High and Low Byte registers, shown in Tables 76 and 77, combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$

**Caution:** Flash programming and erasure is not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device.

| Bit     | 7           | 6 | 5   | 4       | 3 | 2   | 1   | 0   |  |  |  |

|---------|-------------|---|-----|---------|---|-----|-----|-----|--|--|--|

| Field   | FFREQH      |   |     |         |   |     |     |     |  |  |  |

| RESET   | 0           | 0 | 0 0 |         | 0 | 0   | 0   | 0   |  |  |  |

| R/W     | R/W R/W R/W |   | R/W | R/W R/W |   | R/W | R/W | R/W |  |  |  |

| Address | FFAH        |   |     |         |   |     |     |     |  |  |  |

| Bit    | Description                                    |

|--------|------------------------------------------------|

| [7:0]  | Flash Frequency High Byte                      |

| FFREQH | High byte of the 16-bit Flash frequency value. |

#### Table 77. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|--------|---|---|---|---|---|---|---|--|--|--|

| Field   | FFREQL |   |   |   |   |   |   |   |  |  |  |

| RESET   | 0      |   |   |   |   |   |   |   |  |  |  |

| R/W     | R/W    |   |   |   |   |   |   |   |  |  |  |

| Address | FFBH   |   |   |   |   |   |   |   |  |  |  |

| Bit    | Description                                   |

|--------|-----------------------------------------------|

| [7:0]  | Flash Frequency High Byte                     |

| FFREQL | Low byte of the 16-bit Flash frequency value. |

| Bit     | 7                    | 6 | 5   | 4       | 3 | 2   | 1   | 0   |  |  |

|---------|----------------------|---|-----|---------|---|-----|-----|-----|--|--|

| Field   | TRMDR: Trim Bit Data |   |     |         |   |     |     |     |  |  |

| RESET   | 0                    | 0 | 0   | 0       | 0 | 0   | 0   | 0   |  |  |

| R/W     | R/W R/W              |   | R/W | R/W R/W |   | R/W | R/W | R/W |  |  |

| Address | FF7H                 |   |     |         |   |     |     |     |  |  |

#### Table 80. Trim Bit Data Register (TRMDR)

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits. See Tables 81 and 82.

| Bit                                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                                                                                                           | 5                                                                                                                                | 4                                                        | 3                                                            | 2                                                           | 1                                                                                 | 0                                |  |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------|--|--|--|--|

| Field                                           | WDT_RES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WDT_AO                                                                                                                      | OSC_S                                                                                                                            | SEL[1:0]                                                 | VBO_AO                                                       | FRP                                                         | Reserved                                                                          | FWP                              |  |  |  |  |

| RESET                                           | U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U                                                                                                                           | U                                                                                                                                | U                                                        | U                                                            | U                                                           | U                                                                                 | U                                |  |  |  |  |

| R/W                                             | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                                                                                                                         | R/W                                                                                                                              | R/W                                                      | R/W                                                          | R/W                                                         | R/W                                                                               | R/W                              |  |  |  |  |

| Address                                         | Program Memory 0000H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                             |                                                                                                                                  |                                                          |                                                              |                                                             |                                                                                   |                                  |  |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                             |                                                                                                                                  |                                                          |                                                              |                                                             |                                                                                   |                                  |  |  |  |  |

| Bit                                             | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                             |                                                                                                                                  |                                                          |                                                              |                                                             |                                                                                   |                                  |  |  |  |  |

| [7]<br>WDT_RES<br>[6]<br>WDT_AO                 | <ul> <li>0 = Watch<br/>enable</li> <li>1 = Watch<br/>gramm</li> <li>Watchdog</li> <li>0 = On ap<br/>Timer</li> <li>1 = Watch<br/>Watch</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                | ed for the eZ<br>dog Timer ti<br>ned (erased<br>g Timer Alw<br>plication of s<br>cannot be d<br>dog Timer is<br>dog Timer o | me-out gen<br>8 CPU to ad<br>me-out caus<br>) Flash.<br><b>rays On</b><br>system pow<br>isabled.<br>s enabled or<br>an only be o | cknowledge<br>ses a syster<br>er, Watchdo<br>n execution | the interrup<br>m reset. This<br>og Timer is a<br>of the WDT | t request.<br>s is the defa<br>utomatically<br>instruction. | ots must be g<br>ault setting fo<br>y enabled. W<br>Once enabl<br>ault setting fo | or unpro-<br>/atchdog<br>ed, the |  |  |  |  |

| [5:4]<br>OSC_SEL                                | <ul> <li>grammed (erased) Flash.</li> <li>OSCILLATOR Mode Selection</li> <li>00 = On-chip oscillator configured for use with external RC networks (&lt;4MHz).</li> <li>01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0MHz).</li> <li>10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 5.0MHz).</li> <li>11 = Maximum power for use with high frequency crystals (5.0MHz to 20.0MHz). This is the default setting for unprogrammed (erased) Flash.</li> </ul> |                                                                                                                             |                                                                                                                                  |                                                          |                                                              |                                                             |                                                                                   |                                  |  |  |  |  |

Table 81. Flash Option Bits at Program Memory Address 0000H

| Description (Continued)                             |  |  |  |  |  |

|-----------------------------------------------------|--|--|--|--|--|

| Filter Select                                       |  |  |  |  |  |

| 2-bit selection for the clock filter mode.          |  |  |  |  |  |

| 00 = No filter.                                     |  |  |  |  |  |

| 01 = Filter low level noise on high level signal.   |  |  |  |  |  |

| 10 = Filter high level noise on low level signal.   |  |  |  |  |  |

| 11 = Filter both.                                   |  |  |  |  |  |

| dicates bit values 3–1; y indicates bit values 1–0. |  |  |  |  |  |

|                                                     |  |  |  |  |  |

**Note:** The bit values used in Table 89 are set at factory and no calibration is required.

| DlyCtl3, DlyCtl2,<br>DlyCtl1 | Low Noise Pulse<br>on High Signal (ns) | High Noise Pulse<br>on Low Signal (ns) |  |  |

|------------------------------|----------------------------------------|----------------------------------------|--|--|

| 000                          | 5                                      | 5                                      |  |  |

| 001                          | 7                                      | 7                                      |  |  |

| 010                          | 9                                      | 9                                      |  |  |

| 011                          | 11                                     | 11                                     |  |  |

| 100                          | 13                                     | 13                                     |  |  |

| 101                          | 17                                     | 17                                     |  |  |

| 110                          | 20                                     | 20                                     |  |  |

| 111                          | 25                                     | 25                                     |  |  |

| Note: The variation is       | about 30%.                             |                                        |  |  |

#### Table 90. ClkFlt Delay Control Definition

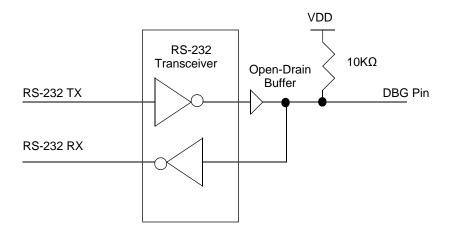

Figure 22. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates, unless the device is in STOP Mode

- All enabled on-chip peripherals operate, unless the device is in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

## **Entering DEBUG Mode**

- The device enters DEBUG Mode after the eZ8 CPU executes a Breakpoint (BRK) instruction

- If the DBG pin is held low during the most recent clock cycle of system reset, the device enters DEBUG Mode on exiting system reset

## **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

|   | Lower Nibble (Hex)      |                          |                              |                                |                            |                             |                            |                                |                               |                              |                            |                          |                           |                           |                  |                           |

|---|-------------------------|--------------------------|------------------------------|--------------------------------|----------------------------|-----------------------------|----------------------------|--------------------------------|-------------------------------|------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|------------------|---------------------------|

|   | 0                       | 1                        | 2                            | 3                              | 4                          | 5                           | 6                          | 7                              | 8                             | 9                            | А                          | В                        | С                         | D                         | Е                | F                         |

| 0 | 1.1<br>BRK              | 2.2<br>SRP<br>IM         | 2.3<br>ADD<br>r1,r2          | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1        | 3.3<br><b>ADD</b><br>R1,IM | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1        | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP                |

| 1 | 2.2<br><b>RLC</b><br>R1 | 2.3<br>RLC<br>IR1        | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1        | 3.4<br>ADC<br>IR2,R1        | 3.3<br>ADC<br>R1,IM        | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1        |                            |                          |                           | 00,271                    |                  | See 2nd<br>Op Code<br>Map |

| 2 | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1        | 2.3<br>SUB<br>r1,r2          | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br>SUB<br>IR2,R1        | 3.3<br>SUB<br>R1,IM        | 3.4<br>SUB<br>IR1,IM           | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br><b>SUBX</b><br>IM,ER1 |                            |                          |                           |                           |                  | map                       |

| 3 | 2.2<br>DEC<br>R1        | 2.3<br>DEC<br>IR1        | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br>SBC<br>R2,R1        | 3.4<br>SBC<br>IR2,R1        | 3.3<br>SBC<br>R1,IM        | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1 |                            |                          |                           |                           |                  |                           |

| 4 | 2.2<br>DA<br>R1         | 2.3<br>DA<br>IR1         | 2.3<br>OR<br>r1,r2           | 2.4<br>OR<br>r1,lr2            | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br>OR<br>IR2,R1         | 3.3<br>OR<br>R1,IM         | 3.4<br>OR<br>IR1,IM            | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1  |                            |                          |                           |                           |                  |                           |

| 5 | 2.2<br>POP<br>R1        | 2.3<br><b>POP</b><br>IR1 | 2.3<br>AND<br>r1,r2          | 2.4<br>AND<br>r1,lr2           | 3.3<br>AND<br>R2,R1        | 3.4<br>AND<br>IR2,R1        | 3.3<br>AND<br>R1,IM        | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1        |                            |                          |                           |                           |                  | 1.2<br>WDT                |

| 6 | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1        | 2.3<br>TCM<br>r1,r2          | 2.4<br>TCM<br>r1,lr2           | 3.3<br>TCM<br>R2,R1        | 3.4<br>TCM<br>IR2,R1        | 3.3<br>TCM<br>R1,IM        | 3.4<br>TCM<br>IR1,IM           | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1 |                            |                          |                           |                           |                  | 1.2<br>STOP               |

| 7 | 2.2<br>PUSH<br>R2       | 2.3<br>PUSH<br>IR2       | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM  | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1  |                            |                          |                           |                           |                  | 1.2<br>HALT               |

| 8 | 2.5<br>DECW<br>RR1      | 2.6<br>DECW<br>IRR1      | 2.5<br>LDE<br>r1,lrr2        | 2.9<br>LDEI<br>Ir1,Irr2        | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2       | 3.4<br>LDX                 | 3.5<br>LDX<br>IRR2,IR1         | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X       |                            |                          |                           |                           |                  | 1.2<br>DI                 |

| 9 | 2.2<br>RL<br>R1         | 2.3<br>RL<br>IR1         | 2.5<br>LDE<br>r2,lrr1        | 2.9<br>LDEI<br>Ir2,Irr1        | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br>LDX                 | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br>LEA<br>r1,r2,X         | 3.5<br>LEA<br>rr1,rr2,X      |                            |                          |                           |                           |                  | 1.2<br>El                 |

| A | 2.5<br>INCW<br>RR1      | 2.6<br>INCW<br>IRR1      | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM  | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1  |                            |                          |                           |                           |                  | 1.4<br>RET                |

| В | 2.2<br><b>CLR</b><br>R1 | 2.3<br><b>CLR</b><br>IR1 | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br>XOR<br>r1,lr2           | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br><b>XOR</b><br>IR2,R1 | 3.3<br><b>XOR</b><br>R1,IM | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1 |                            |                          |                           |                           |                  | 1.5<br>IRET               |

| С | 2.2<br><b>RRC</b><br>R1 | 2.3<br><b>RRC</b><br>IR1 | 2.5<br><b>LDC</b><br>r1,lrr2 | 2.9<br><b>LDCI</b><br>Ir1,Irr2 | 2.3<br><b>JP</b><br>IRR1   | 2.9<br>LDC<br>Ir1,Irr2      |                            | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                              |                            |                          |                           |                           |                  | 1.2<br>RCF                |

| D | 2.2<br><b>SRA</b><br>R1 | 2.3<br><b>SRA</b><br>IR1 | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>Ir2,Irr1 | 2.6                        | 2.2<br><b>BSWAP</b><br>R1   | 3.3<br>CALL<br>DA          | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                              |                            |                          |                           |                           |                  | 1.2<br>SCF                |

| E | 2.2<br><b>RR</b><br>R1  | 2.3<br><b>RR</b><br>IR1  | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM  | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1         |                            |                          |                           |                           |                  | 1.2<br>CCF                |

| F | 2.2<br>SWAP<br>R1       | 2.3<br>SWAP<br>IR1       | 2.6<br>TRAP<br>Vector        | 2.3<br>LD<br>lr1,r2            | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b>          | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               | -                            | V                          | V                        | V                         | ▼                         | ▼                |                           |

## Figures 29 and 30 provide information about each of the eZ8 CPU instructions.

Figure 29. First Op Code Map

Upper Nibble (Hex)

## **General Purpose I/O Port Output Timing**

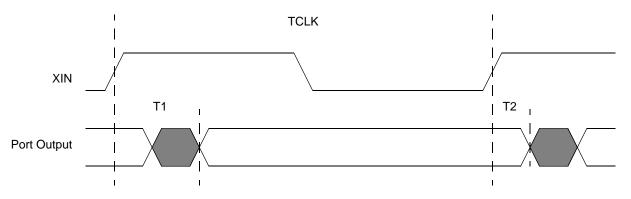

Figure 34 and Table 125 provide timing information for the GPIO port pins.

|                |                                     | Delay (ns) |         |  |  |  |  |  |

|----------------|-------------------------------------|------------|---------|--|--|--|--|--|

| Parameter      | Abbreviation                        | Minimum    | Maximum |  |  |  |  |  |

| GPIO Port Pins |                                     |            |         |  |  |  |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _          | 15      |  |  |  |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | _       |  |  |  |  |  |

### Table 125. GPIO Port Output Timing

207

Table 129 lists the pin count by package.

| Package | Pin Count    |    |

|---------|--------------|----|

|         | 20           | 28 |

| PDIP    | $\checkmark$ |    |

| QFN     | $\checkmark$ |    |

| SOIC    | $\checkmark$ |    |

| SSOP    | $\checkmark$ |    |

### Table 129. Package and Pin Count Description

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

232

compare - extended addressing 166 compare mode 89 compare with carry 166 compare with carry - extended addressing 166 complement 169 complement carry flag 167, 168 condition code 164 continuous mode 89 Control Registers 14, 17 counter modes 89 CP 166 CPC 166 **CPCX 166** CPU and peripheral overview 4 CPU control instructions 168 **CPX 166** current measurement architecture 98 operation 99 Customer Feedback Form 239 Customer Information 239

# D

DA 164, 166 data memory 16 DC characteristics 185 debugger, on-chip 139 **DEC 166** decimal adjust 166 decrement 166 decrement and jump non-zero 169 decrement word 166 **DECW 166** destination operand 165 device, port availability 33 DI 168 direct address 164 disable interrupts 168 **DJNZ 169** dst 165

## Ε

EI 168 electrical characteristics 184 GPIO input data sample timing 195 watch-dog timer 194 electrical noise 98 enable interrupt 168 ER 164 extended addressing register 164 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 166 eZ8 CPU instruction notation 164 eZ8 CPU instruction set 162 eZ8 CPU instruction summary 171

# F

FCTL register 119, 126, 127, 228 features, Z8 Encore! 1 first opcode map 182 FLAGS 165 flags register 165 flash controller 4 option bit address space 127 option bit configuration - reset 124 program memory address 0000H 127 program memory address 0001H 128 flash memory 108 byte programming 116 code protection 114 configurations 108 control register definitions 118, 126 controller bypass 117 flash control register 119, 126, 127, 228 flash option bits 115 flash status register 120 flow chart 113 frequency high and low byte registers 123 mass erase 117 operation 112 operation timing 114 page erase 117

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

read program memory CRC (0EH) 147 read register (09H) 146 read runtime counter (03H) 145 step instruction (10H) 148 stuff instruction (11H) 148 write data memory (0CH) 147 write OCD control register (04H) 145 write program counter (06H) 146 write program memory (0AH) 146 write register (08H) 146 on-chip debugger (OCD) 139 on-chip debugger signals 12 on-chip oscillator 157 one-shot mode 89 opcode map abbreviations 181 cell description 180 first 182 second after 1FH 183 operation 100 current measurement 99 voltage measurement timing diagram 100 Operational Description 21, 30, 33, 53, 68, 92, 98, 106, 108, 124, 134, 139, 151, 157, 161 OR 169 ordering information 200 ORX 169 oscillator signals 12

## Ρ

p 164

Packaging 199

part selection guide 2

PC 165

peripheral AC and DC electrical characteristics 190

pin characteristics 13

Pin Descriptions 7

polarity 164

POP 168

pop using extended addressing 168

POPX 168

port availability, device 33

port input timing (GPIO) 195

port output timing, GPIO 196 power supply signals 12 power-on reset (POR) 23 program control instructions 169 program memory 15 PUSH 168 push using extended addressing 168 PUSHX 168 PWM mode 89, 90 PxADDR register 40, 222, 223, 224, 225 PxCTL register 41, 222, 223, 224, 225

# R

R 165 r 164 RA register address 165 RCF 167, 168 register 165 flash control (FCTL) 119, 126, 127, 228 flash high and low byte (FFREQH and FRE-EQL) 123 flash page select (FPS) 121, 122 flash status (FSTAT) 120 GPIO port A-H address (PxADDR) 40, 222, 223, 224, 225 GPIO port A-H alternate function sub-registers 42 GPIO port A-H control address (PxCTL) 41, 222, 223, 224, 225 GPIO port A-H data direction sub-registers 41 OCD control 148 OCD status 150 watch-dog timer control (WDTCTL) 95, 107, 154, 217, 218, 226 watchdog timer control (WDTCTL) 29 watch-dog timer reload high byte (WDTH) 227 watchdog timer reload high byte (WDTH) 96 watch-dog timer reload low byte (WDTL) 227 watchdog timer reload low byte (WDTL) 97 watch-dog timer reload upper byte (WDTU) 227

236

watchdog timer reload upper byte (WDTU) 96 register file 14 register pair 165 register pointer 165 registers ADC channel 1 102 ADC data high byte 103 ADC data low bit 103, 104, 105 reset and stop mode characteristics 22 and stop mode recovery 21 carry flag 167 sources 23 **RET 169** return 169 RL 169 **RLC 169** rotate and shift instuctions 169 rotate left 169 rotate left through carry 169 rotate right 170 rotate right through carry 170 RP 165 RR 165, 170 rr 165 **RRC** 170

## S

SBC 167 SCF 167, 168 second opcode map after 1FH 183 set carry flag 167, 168 set register pointer 168 shift right arithmatic 170 shift right logical 170 signal descriptions 11 software trap 169 source operand 165 SP 165 SRA 170 src 165 SRL 170 SRP 168 stack pointer 165 **STOP 168** stop mode 30, 168 stop mode recovery sources 26 using a GPIO port pin transition 27, 28 using watch-dog timer time-out 27 **SUB 167** subtract 167 subtract - extended addressing 167 subtract with carry 167 subtract with carry - extended addressing 167 **SUBX 167 SWAP 170** swap nibbles 170 symbols, additional 165

# Т

Table 134. Power Consumption Reference Table 197 **TCM 167 TCMX 167** test complement under mask 167 test complement under mask - extended addressing 167 test under mask 167 test under mask - extended addressing 167 tiing diagram, voltage measurement 100 timer signals 11 timers 68 architecture 68 block diagram 69 capture mode 77, 78, 89, 90 capture/compare mode 81, 89 compare mode 79, 89 continuous mode 70, 89 counter mode 71.72 counter modes 89 gated mode 80, 89 one-shot mode 69, 89 operating mode 69 PWM mode 74, 75, 89, 90 reading the timer count values 82