Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-VQFN                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0130qj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| ADC Control Register Definitions10ADC Control Register 010ADC Data High Byte Register10ADC Data Low Bits Register10Sample Settling Time Register10Sample Time Register10                                                                                                                                                                                                                                                                                                                                                                                                 | )2<br>)3<br>)3<br>)4                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Comparator10Operation10Comparator Control Register Definitions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )6                                              |

| Flash Memory       10         Data Memory Address Space       11         Flash Information Area       11         Operation       11         Flash Operation Timing Using the Flash Frequency Registers       11                                                                                                                                                                                                                                                                                                                                                          | 1<br>1<br>2                                     |

| Flash Code Protection Against External Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                                               |

| Flash Code Protection Against Accidental Program and Erasure11Byte Programming11Page Erase11Mass Erase11Flash Controller Bypass11Flash Controller Behavior in Debug Mode11NVDS Operational Requirements11Flash Control Register Definitions11Flash Control Register Definitions11Flash Status Register12Flash Status Register12Flash Page Select Register12Flash Sector Protect Register12Flash Frequency High and Low Byte Registers12                                                                                                                                  | 6<br>7<br>7<br>7<br>7<br>8<br>8<br>9<br>0<br>21 |

| Flash Option Bits       12.         Operation       12.         Option Bit Configuration by Reset       12.         Option Bit Types       12.         Flash Option Bit Control Register Definitions       12.         Flash Option Bit Control Register Definitions       12.         Flash Option Bit Control Register Definitions       12.         Trim Bit Address Register       12.         Trim Bit Data Register       12.         Flash Option Bit Address Space       12.         Trim Bit Address Space       12.         Nonvolatile Data Storage       13. | 24<br>24<br>25<br>26<br>26<br>26<br>27<br>29    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                               |

Calibration and Compensation ..... 101

#### vii

# **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit CPU, meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 CPU code

- Expanded internal register file allows access up to 4KB

- New instructions improve execution efficiency for code developed using high-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the register file

- Up to 10 MIPS operation

- C Compiler-friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

#### **General Purpose Input/Output**

The Z8 Encore! F0830 Series features up to 25 port pins (Ports A–D) for general-purpose input/output (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable.

## **Flash Controller**

The Flash Controller programs and erases the Flash memory. It also supports protection against accidental programming and erasure.

| Signal<br>Mnemonic | I/O | Description                                                                                                                                                                                                                                                                   |

|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators        |     |                                                                                                                                                                                                                                                                               |

| X <sub>IN</sub>    | I   | External crystal input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| X <sub>OUT</sub>   | 0   | External crystal output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input        |     |                                                                                                                                                                                                                                                                               |

| CLK <sub>IN</sub>  | Ι   | Clock input signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |

| LED Drivers        |     |                                                                                                                                                                                                                                                                               |

| LED                | 0   | Direct LED drive capability. All Port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |

| On-Chip Debugger   | •   |                                                                                                                                                                                                                                                                               |

| DBG                | I/O | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |

|                    |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                                                                                                                                                               |

| Reset              |     |                                                                                                                                                                                                                                                                               |

| RESET              | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                            |

| Power Supply       |     |                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub>    | Ι   | Digital power supply.                                                                                                                                                                                                                                                         |

| AV <sub>DD</sub>   | I   | Analog power supply.                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>    | I   | Digital ground.                                                                                                                                                                                                                                                               |

| AV <sub>SS</sub>   | I   | Analog ground.                                                                                                                                                                                                                                                                |

|                    |     | gnals are available only in the 28-pin packages with ADC. They are replaced by PB6 kages without ADC.                                                                                                                                                                         |

## Table 4. Signal Descriptions (Continued)

| Address (Hex)    | Register Description             | Mnemonic | Reset (Hex) | Page No |

|------------------|----------------------------------|----------|-------------|---------|

| Interrupt Contro | oller (cont'd)                   |          |             |         |

| FCE              | Shared interrupt select          | IRQSS    | 00          | 66      |

| FCF              | Interrupt control                | IRQCTL   | 00          | 67      |

| GPIO Port A      |                                  |          |             |         |

| FD0              | Port A address                   | PAADDR   | 00          | 39      |

| FD1              | Port A control                   | PACTL    | 00          | 41      |

| FD2              | Port A input data                | PAIN     | XX          | 41      |

| FD3              | Port A output data               | PAOUT    | 00          | 41      |

| GPIO Port B      |                                  |          |             |         |

| FD4              | Port B address                   | PBADDR   | 00          | 39      |

| FD5              | Port B control                   | PBCTL    | 00          | 41      |

| FD6              | Port B input data                | PBIN     | XX          | 41      |

| FD7              | Port B output data               | PBOUT    | 00          | 41      |

| GPIO Port C      |                                  |          |             |         |

| FD8              | Port C address                   | PCADDR   | 00          | 39      |

| FD9              | Port C control                   | PCCTL    | 00          | 41      |

| FDA              | Port C input data                | PCIN     | XX          | 41      |

| FDB              | Port C output data               | PCOUT    | 00          | 41      |

| GPIO Port D      |                                  |          |             |         |

| FDC              | Port D address                   | PDADDR   | 00          | 39      |

| FDD              | Port D control                   | PDCTL    | 00          | 41      |

| FDE              | Reserved                         |          | XX          |         |

| FDF              | Port D output data               | PDOUT    | 00          | 41      |

| FE0–FEF          | Reserved                         | _        | XX          |         |

| Watchdog Time    | r (WDT)                          |          |             |         |

| FF0              | Reset status                     | RSTSTAT  | XX          | 95      |

|                  | Watchdog Timer control           | WDTCTL   | XX          | 95      |

| FF1              | Watchdog Timer reload upper byte | WDTU     | FF          | 96      |

| FF2              | Watchdog Timer reload high byte  | WDTH     | FF          | 96      |

| FF3              | Watchdog Timer reload low byte   | WDTL     | FF          | 97      |

| FF4–FF5          | Reserved                         |          | XX          |         |

## Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

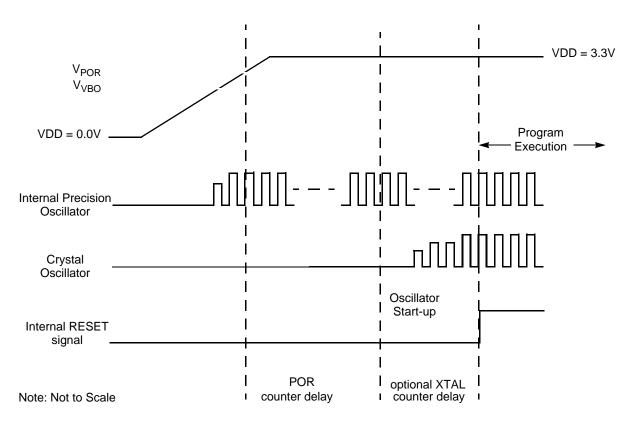

Figure 6. Power-On Reset Operation

## **Voltage Brown-Out Reset**

The devices in the Z8 Encore! F0830 Series provide low Voltage Brown-Out (VBO) protection. The VBO circuit forces the device to the Reset state, when the supply voltage drops below the VBO threshold voltage (unsafe level). While the supply voltage remains below the Power-On Reset threshold voltage ( $V_{POR}$ ), the VBO circuit holds the device in reset.

After the supply voltage exceeds the Power-On Reset threshold voltage, the device progresses through a full system reset sequence, as described in the POR section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 7 displays the Voltage Brown-Out operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

clock and reset signals, the required reset duration may be three or four clock periods. A reset pulse of three clock cycles in duration might trigger a reset and a reset pulse of four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted low, the Z8 Encore! F0830 Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held low beyond the system reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a system reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

## **External Reset Indicator**

During system reset or when enabled by the GPIO logic, the RESET pin functions as an open-drain (active low) RESET mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! F0830 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events. See the <u>Port A–D Control Registers</u> section on page 41.

After an internal Reset event occurs, the internal circuitry begins driving the RESET pin low. The  $\overrightarrow{\text{RESET}}$  pin is held low by the internal circuitry until the appropriate delay listed in <u>Table 9</u> (see page 22) has elapsed.

## **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset, but the remainder of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

# Stop Mode Recovery

The device enters the STOP Mode when the STOP instruction is executed by the eZ8 CPU. See the <u>Low-Power Modes</u> chapter on page 30 for detailed STOP Mode information. During Stop Mode Recovery, the CPU is held in reset for about 66 IPO cycles if the crystal oscillator is disabled or about 5000 cycles if it is enabled.

Stop Mode Recovery does not affect the on-chip registers other than the Reset Status (RSTSTAT) Register and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

#### 31

# HALT Mode

Executing the eZ8 CPU HALT instruction places the device into HALT Mode. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any one of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as digital inputs must be driven to  $V_{DD}$  when pull-up register bit is enabled or to one of power rail ( $V_{DD}$  or GND) when pull-up register bit is disabled.

# **Peripheral Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! F0830 Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

#### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

#### 39

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the input pin signal. Other port pin interrupt sources, generate an interrupt when any edge occurs (both rising and falling). See the <u>Interrupt Controller</u> chapter on page 53 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data and output data; Table 17 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| P <i>x</i> ADDR           | Port A–D Address Register (selects subregisters)            |

| PxCTL                     | Port A–D Control Register (provides access to subregisters) |

| PxIN                      | Port A–D Input Data Register                                |

| P <i>x</i> OUT            | Port A–D Output Data Register                               |

| Port Subregister Mnemonic | Port Register Name                                          |

| PxDD                      | Data Direction                                              |

| P <i>x</i> AF             | Alternate Function                                          |

| PxOC                      | Output Control (open-drain)                                 |

| PxHDE                     | High Drive Enable                                           |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable                            |

| PxPUE                     | Pull-Up Enable                                              |

| PxAFS1                    | Alternate Function Set 1                                    |

| PxAFS2                    | Alternate Function Set 2                                    |

#### Table 17. GPIO Port Registers and Subregisters

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines whether the capture occurs on a rising edge or a falling edge of the timer input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt has been caused by an input capture event.

If no capture event occurs, the timer counts up to 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

Flash information area is mapped into program memory and overlays the 128 bytes in the address range FE00H to FE7FH. When the information area access is enabled, all reads from these program memory addresses return the information area data rather than the program memory data. Access to the Flash information area is read-only.

The trim bits are handled differently than the other Zilog Flash option bits. The trim bits are the hybrid of the user option bits and the standard Zilog option bits. These trim bits must be user-accessible for reading at all times using external registers regardless of the state of bit 7 in the Flash Page Select Register. Writes to the trim space change the value of the Option Bit Holding Register but do not affect the Flash bits, which remain as read-only.

| Program Memory |                                                                                          |

|----------------|------------------------------------------------------------------------------------------|

| Address (Hex)  | Function                                                                                 |

| FE00–FE3F      | Zilog option bits                                                                        |

| FE40–FE53      | Part number<br>20-character ASCII alphanumeric code<br>Left justified and filled with FH |

| FE54–FE5F      | Reserved                                                                                 |

| FE60–FE7F      | Reserved                                                                                 |

Table 70. Z8F083 Flash Memory Area Map

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for byte programming, page erase and mass erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The flowchart in Figure 19 display basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase and Mass Erase) displayed in Figure 19.

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

## Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register. Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased. After setting a bit in the Sector Protect Register, the bit cannot be cleared by the user.

## **Byte Programming**

Flash memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either mass erase or page erase. When the Flash Controller is unlocked and mass erase is successfully enabled, all of the program memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and page erase is successfully enabled, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the page erase or mass erase commands.

Byte programming can be accomplished using the On-Chip Debugger's write memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the <u>eZ8 CPU</u> <u>Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>, for the description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control Register, except the mass erase or page erase commands.

**Caution:** The byte at each address within Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs.

# Operation

The following section describes the operation of the On-Chip Debugging function.

## **OCD** Interface

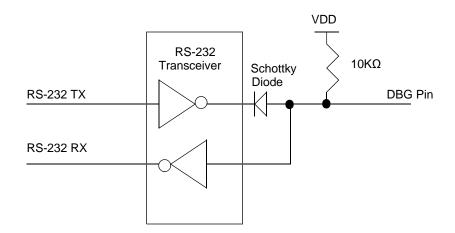

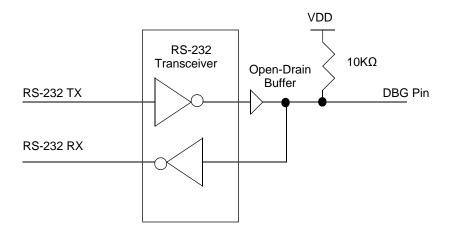

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, which means that transmission and data retrieval cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface between the Z8 Encore! F0830 Series products and the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figures 21 and 22. The recommended method is the buffered implementation depicted in Figure 22. The DBG pin must always be connected to  $V_{DD}$  through an external pull-up resistor.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

#### Figure 21. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

Figure 22. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates, unless the device is in STOP Mode

- All enabled on-chip peripherals operate, unless the device is in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

#### **Entering DEBUG Mode**

- The device enters DEBUG Mode after the eZ8 CPU executes a Breakpoint (BRK) instruction

- If the DBG pin is held low during the most recent clock cycle of system reset, the device enters DEBUG Mode on exiting system reset

#### **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

| Debug Command           | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit |

|-------------------------|-----------------|------------------------------------|----------------------------------------------|

| Read Program Memory CRC | 0EH             | -                                  | -                                            |

| Reserved                | 0FH             | -                                  | -                                            |

| Step Instruction        | 10H             | -                                  | Disabled                                     |

| Stuff Instruction       | 11H             | -                                  | Disabled                                     |

| Execute Instruction     | 12H             | -                                  | Disabled                                     |

| Reserved                | 13H–FFH         | _                                  | _                                            |

#### Table 95. On-Chip Debugger Command Summary (Continued)

In the following bulleted list of OCD commands, data and commands sent from the host to the OCD are identified by DBG  $\leftarrow$  Command/Data. Data sent from the OCD back to the host is identified by DBG Data.

**Read OCD Revision (00H).** The read OCD revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed or changed this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

**Read Runtime Counter (03H).** The runtime counter counts system clock cycles in between breakpoints. The 16-bit runtime counter counts from 0000H and stops at the maximum count of FFFFH. The runtime counter is overwritten during the write memory, read memory, write register, read register, read memory CRC, step instruction, stuff instruction and execute instruction commands.

```

DBG \leftarrow 03H

DBG \rightarrow RuntimeCounter[15:8]

DBG \rightarrow RuntimeCounter[7:0]

```

Write OCD Control Register (04H). The write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash read protect option bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0. To return the device to normal operating mode, the device must be reset.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

| Abbreviation | Description                             | Abbreviation                                      | Description            |

|--------------|-----------------------------------------|---------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                               | Indirect Register Pair |

| CC           | Condition code                          | р                                                 | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displace-<br>ment | r                                                 | 4-bit Working Register |

| DA           | Destination address                     | R                                                 | 8-bit register         |

| ER           | Extended Addressing Register            | r1, R1, Ir1, Irr1,<br>IR1, rr1, RR1,<br>IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address         |

| lr           | Indirect Working Register               | RA                                                | Relative               |

| IR           | Indirect Register                       | rr                                                | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                                | Register Pair          |

#### Table 114. Op Code Map Abbreviations

| Art Number         Flash         RAM         NVDS         Channels         Description           3F0831HH020EG         8KB         256         Yes         0         SCOP 20-pin           3F0831PH020EG         8KB         256         Yes         0         QFN 20-pin           3F0831QH020EG         8KB         256         Yes         8         SOIC 28-pin           3F0830SJ020EG         8KB         256         Yes         8         SOP 28-pin           3F0830RJ020EG         8KB         256         Yes         8         QFN 28-pin           3F0830RJ020EG         8KB         256         Yes         0         SOIC 28-pin           3F0831SJ020EG         8KB         256         Yes         0         SOIP 28-pin           3F0831HJ020EG         8KB         256         Yes         0         QFN 28-pin           3F0431H020SG         4KB         256         Yes <t< th=""><th></th><th></th><th></th><th></th><th>ADC</th><th>-</th></t<>                                |                      |              |       |      | ADC | -           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------|-------|------|-----|-------------|

| BF0831PH020EG         8KB         256         Yes         0         PDIP 20-pin           BF0831QH020EG         8KB         256         Yes         0         QFN 20-pin           BF0830SJ020EG         8KB         256         Yes         8         SOIC 28-pin           BF0830PJ020EG         8KB         256         Yes         8         PDIP 28-pin           BF0830QJ020EG         8KB         256         Yes         0         SOIC 28-pin           BF0831SJ020EG         8KB         256         Yes         0         SOIC 28-pin           BF0831LJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831LJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831LJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831QJ020EG         8KB         256         Yes         7         SOIC 20-pin           BF0430SH020SG         4KB         256         Yes         7         QFN 20-pin           BF0430DH020SG         4KB         256         Yes         0 </th <th>Part Number</th> <th>Flash</th> <th>RAM</th> <th>NVDS</th> <th></th> <th>Description</th>  | Part Number          | Flash        | RAM   | NVDS |     | Description |

| BF0831QH020EG         8KB         256         Yes         0         QFN 20-pin           BF0830SJ020EG         8KB         256         Yes         8         SOIC 28-pin           BF0830PJ020EG         8KB         256         Yes         8         PDIP 28-pin           BF0830QJ020EG         8KB         256         Yes         8         QFN 28-pin           BF0831SJ020EG         8KB         256         Yes         0         SOIC 28-pin           BF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0430SH020SG         4KB         256         Yes         7         SOIC 20-pin           BF0430PH020SG         4KB         256         Yes         7         QFN 20-pin           BF0430PH020SG         4KB         256         Yes         0 <td>Z8F0831HH020EG</td> <td>8KB</td> <td>256</td> <td>Yes</td> <td>0</td> <td>SSOP 20-pin</td>        | Z8F0831HH020EG       | 8KB          | 256   | Yes  | 0   | SSOP 20-pin |

| SF0830SJ020EG         8KB         256         Yes         8         SOIC 28-pin           SF0830HJ020EG         8KB         256         Yes         8         SSOP 28-pin           SF0830PJ020EG         8KB         256         Yes         8         QFN 28-pin           SF0830PJ020EG         8KB         256         Yes         8         QFN 28-pin           SF0831PJ020EG         8KB         256         Yes         0         SOIC 28-pin           SF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           SF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           SF0831QJ020EG         8KB         256         Yes         7         SOIC 20-pin           SF0430SH020SG         4KB         256         Yes         7         QFN 20-pin           SF0430PH020SG         4KB         256         Yes         0 <td>Z8F0831PH020EG</td> <td>8KB</td> <td>256</td> <td>Yes</td> <td>0</td> <td>PDIP 20-pin</td>        | Z8F0831PH020EG       | 8KB          | 256   | Yes  | 0   | PDIP 20-pin |

| SF0830HJ020EG         8KB         256         Yes         8         SSOP 28-pin           SF0830PJ020EG         8KB         256         Yes         8         PDIP 28-pin           SF0830QJ020EG         8KB         256         Yes         0         SOIC 28-pin           SF0831SJ020EG         8KB         256         Yes         0         SOIC 28-pin           SF0831PJ020EG         8KB         256         Yes         0         PDIP 28-pin           SF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           SF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           SF0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           SF0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           SF0831QJ020EG         4KB         256         Yes         7         SOIC 20-pin           SF0430SH020SG         4KB         256         Yes         7         SOIC 20-pin           SF0430PH020SG         4KB         256         Yes         0         SOIC 20-pin           SF0431SH020SG         4KB         256         Yes         0                                                                                                   | Z8F0831QH020EG       | 8KB          | 256   | Yes  | 0   | QFN 20-pin  |

| BF0830PJ020EG         8KB         256         Yes         8         PDIP 28-pin           BF0830QJ020EG         8KB         256         Yes         0         SOIC 28-pin           BF0831SJ020EG         8KB         256         Yes         0         SSOP 28-pin           BF0831HJ020EG         8KB         256         Yes         0         PDIP 28-pin           BF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0431QJ020EG         4KB         256         Yes         7         SOIC 20-pin           BF0430PH020SG         4KB         256         Yes         7         QFN 20-pin           BF0431DH020SG         4KB         256         Yes         0         SOIC 20-pin           BF0431HH020SG         4KB         256         Yes         0 </td <td>Z8F0830SJ020EG</td> <td>8KB</td> <td>256</td> <td>Yes</td> <td>8</td> <td>SOIC 28-pin</td> | Z8F0830SJ020EG       | 8KB          | 256   | Yes  | 8   | SOIC 28-pin |

| BF0830QJ020EG         8KB         256         Yes         8         QFN 28-pin           BF0831SJ020EG         8KB         256         Yes         0         SOIC 28-pin           BF0831HJ020EG         8KB         256         Yes         0         PDIP 28-pin           BF0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           BF0831QJ020EG         8KB         256         Yes         7         SOIC 20-pin           BF0430SH020SG         4KB         256         Yes         7         SOIC 20-pin           BF0430QH020SG         4KB         256         Yes         0         SOIC 20-pin           BF0431H020SG         4KB         256         Yes         0         SOIC 20-pin           BF0431H020SG         4KB         256         Yes         0 <td>Z8F0830HJ020EG</td> <td>8KB</td> <td>256</td> <td>Yes</td> <td>8</td> <td>SSOP 28-pin</td>        | Z8F0830HJ020EG       | 8KB          | 256   | Yes  | 8   | SSOP 28-pin |

| 3F0831SJ020EG         8KB         256         Yes         0         SOIC 28-pin           3F0831HJ020EG         8KB         256         Yes         0         PDIP 28-pin           3F0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           3F0831PJ020EG         8KB         256         Yes         0         QFN 28-pin           3F0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           3F0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           3F0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           3F0430H020SG         4KB         256         Yes         7         SOIC 20-pin           3F0430PH020SG         4KB         256         Yes         7         QFN 20-pin           3F0430QH020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431PH020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431PH020SG         4KB         256         Yes         8 <td>Z8F0830PJ020EG</td> <td>8KB</td> <td>256</td> <td>Yes</td> <td>8</td> <td>PDIP 28-pin</td>       | Z8F0830PJ020EG       | 8KB          | 256   | Yes  | 8   | PDIP 28-pin |

| SF0831HJ020EG         8KB         256         Yes         0         SSOP 28-pin           3F0831PJ020EG         8KB         256         Yes         0         PDIP 28-pin           3F0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           3F0430Ph020SG         4KB         256         Yes         7         SOIC 20-pin           3F0430Ph020SG         4KB         256         Yes         7         QFN 20-pin           3F0430QH020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431H020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431H020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431H020SG         4KB         256         Yes         0 <td>Z8F0830QJ020EG</td> <td>8KB</td> <td>256</td> <td>Yes</td> <td>8</td> <td>QFN 28-pin</td>         | Z8F0830QJ020EG       | 8KB          | 256   | Yes  | 8   | QFN 28-pin  |

| BEROBATP JO20EG         8KB         256         Yes         0         PDIP 28-pin           BEROBATQ JO20EG         8KB         256         Yes         0         QFN 28-pin           BEROOREL F0830 with 4KB Flash         sandard Temperature: 0°C to 70°C         sandard Temperature: 0°C to 70°C         7         SOIC 20-pin           BE0430SH020SG         4KB         256         Yes         7         SOIC 20-pin           BE0430PH020SG         4KB         256         Yes         7         SOP 20-pin           BE0430PH020SG         4KB         256         Yes         7         QFN 20-pin           BE0430PH020SG         4KB         256         Yes         7         QFN 20-pin           BE0430PH020SG         4KB         256         Yes         0         SOIC 20-pin           BE0431PH020SG         4KB         256         Yes         0         SOIC 20-pin           BE0431PH020SG         4KB         256         Yes         0         SOIC 20-pin           BE0431PH020SG         4KB         256         Yes         0         QFN 20-pin           BE0431PH020SG         4KB         256         Yes         8         SOIC 28-pin           BE0430SJ020SG         4KB                                                                    | 28F0831SJ020EG       | 8KB          | 256   | Yes  | 0   | SOIC 28-pin |

| BF0831QJ020EG         8KB         256         Yes         0         QFN 28-pin           B Encore! F0830 with 4KB Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28F0831HJ020EG       | 8KB          | 256   | Yes  | 0   | SSOP 28-pin |

| Bencore! F0830 with 4KB Flash           andard Temperature: 0°C to 70°C           3F0430SH020SG         4KB         256         Yes         7         SOIC 20-pin           3F0430H020SG         4KB         256         Yes         7         SOIC 20-pin           3F0430PH020SG         4KB         256         Yes         7         PDIP 20-pin           3F0430PH020SG         4KB         256         Yes         7         QFN 20-pin           3F0430QH020SG         4KB         256         Yes         7         QFN 20-pin           3F0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431HH020SG         4KB         256         Yes         0         SOIP 20-pin           3F0431PH020SG         4KB         256         Yes         0         QFN 20-pin           3F0431PH020SG         4KB         256         Yes         0         QFN 20-pin           3F0430AJ020SG         4KB         256         Yes         8         SOIC 28-pin           3F0430AJ020SG         4KB         256         Yes         8         SOIC 28-pin           3F0430AJ020SG         4KB         256         Yes         0 <td>Z8F0831PJ020EG</td> <td>8KB</td> <td>256</td> <td>Yes</td> <td>0</td> <td>PDIP 28-pin</td>             | Z8F0831PJ020EG       | 8KB          | 256   | Yes  | 0   | PDIP 28-pin |

| andard Temperature: 0°C to 70°C           3F0430SH020SG         4KB         256         Yes         7         SOIC 20-pin           3F0430H020SG         4KB         256         Yes         7         SSOP 20-pin           3F0430PH020SG         4KB         256         Yes         7         PDIP 20-pin           3F0430PH020SG         4KB         256         Yes         7         QFN 20-pin           3F0430QH020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           3F0431HH020SG         4KB         256         Yes         0         SSOP 20-pin           3F0431PH020SG         4KB         256         Yes         0         QFN 20-pin           3F0431QH020SG         4KB         256         Yes         0         QFN 20-pin           3F0430SJ020SG         4KB         256         Yes         8         SOIC 28-pin           3F0430PJ020SG         4KB         256         Yes         8         QFN 28-pin           3F0430QJ020SG         4KB         256         Yes         0         SOIC 28-pin           3F0431SJ020SG         <                                                                                              | 8F0831QJ020EG        | 8KB          | 256   | Yes  | 0   | QFN 28-pin  |

| 3F0430SH020SG       4KB       256       Yes       7       SOIC 20-pin         3F0430HH020SG       4KB       256       Yes       7       SSOP 20-pin         3F0430PH020SG       4KB       256       Yes       7       PDIP 20-pin         3F0430PH020SG       4KB       256       Yes       7       QFN 20-pin         3F0430PH020SG       4KB       256       Yes       7       QFN 20-pin         3F0431SH020SG       4KB       256       Yes       0       SOIC 20-pin         3F0431PH020SG       4KB       256       Yes       0       SOIC 20-pin         3F0431PH020SG       4KB       256       Yes       0       SOIC 20-pin         3F0431PH020SG       4KB       256       Yes       0       QFN 20-pin         3F0431PH020SG       4KB       256       Yes       0       QFN 20-pin         3F0430J020SG       4KB       256       Yes       8       SOIC 28-pin         3F0430PJ020SG       4KB       256       Yes       8       QFN 28-pin         3F0430J020SG       4KB       256       Yes       0       SOIC 28-pin         3F0431SJ020SG       4KB       256       Yes <td< td=""><td>8 Encore! F0830 witl</td><td>h 4KB Flash</td><td>1</td><td></td><td></td><td></td></td<>                                                                                | 8 Encore! F0830 witl | h 4KB Flash  | 1     |      |     |             |

| BF0430HH020SG         4KB         256         Yes         7         SSOP 20-pin           BF0430PH020SG         4KB         256         Yes         7         PDIP 20-pin           BF0430QH020SG         4KB         256         Yes         7         QFN 20-pin           BF0430QH020SG         4KB         256         Yes         7         QFN 20-pin           BF0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           BF0431HH020SG         4KB         256         Yes         0         SSOP 20-pin           BF0431PH020SG         4KB         256         Yes         0         SSOP 20-pin           BF0431PH020SG         4KB         256         Yes         0         QFN 20-pin           BF0430L002SG         4KB         256         Yes         0         QFN 20-pin           BF0430L002SG         4KB         256         Yes         8         SOIC 28-pin           BF0430DJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0430DJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431DJ020SG         4KB         256         Yes         0 <td>standard Temperatur</td> <td>e: 0°C to 70</td> <td>°C</td> <td></td> <td></td> <td></td>         | standard Temperatur  | e: 0°C to 70 | °C    |      |     |             |

| BF0430PH020SG         4KB         256         Yes         7         PDIP 20-pin           BF0430QH020SG         4KB         256         Yes         7         QFN 20-pin           BF0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           BF0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           BF0431HH020SG         4KB         256         Yes         0         SSOP 20-pin           BF0431PH020SG         4KB         256         Yes         0         PDIP 20-pin           BF0431PH020SG         4KB         256         Yes         0         QFN 20-pin           BF0431QH020SG         4KB         256         Yes         0         QFN 20-pin           BF0430SJ020SG         4KB         256         Yes         8         SOIC 28-pin           BF0430PJ020SG         4KB         256         Yes         8         PDIP 28-pin           BF0431SJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431PJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431PJ020SG         4KB         256         Yes                                                                                                            | 28F0430SH020SG       | 4KB          | 256   | Yes  | 7   | SOIC 20-pin |

| BF0430QH020SG         4KB         256         Yes         7         QFN 20-pin           BF0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           BF0431HH020SG         4KB         256         Yes         0         SSOP 20-pin           BF0431PH020SG         4KB         256         Yes         0         PDIP 20-pin           BF0431PH020SG         4KB         256         Yes         0         QFN 20-pin           BF0431QH020SG         4KB         256         Yes         0         QFN 20-pin           BF0430SJ020SG         4KB         256         Yes         0         QFN 20-pin           BF0430HJ020SG         4KB         256         Yes         8         SOIC 28-pin           BF0430PJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0430QJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431FJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431FJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431PJ020SG         4KB         256         Yes         0<                                                                                                   | 8F0430HH020SG        | 4KB          | 256   | Yes  | 7   | SSOP 20-pin |

| BF0431SH020SG         4KB         256         Yes         0         SOIC 20-pin           BF0431HH020SG         4KB         256         Yes         0         SSOP 20-pin           BF0431PH020SG         4KB         256         Yes         0         PDIP 20-pin           BF0431PH020SG         4KB         256         Yes         0         QFN 20-pin           BF0431QH020SG         4KB         256         Yes         0         QFN 20-pin           BF0430SJ020SG         4KB         256         Yes         8         SOIC 28-pin           BF0430HJ020SG         4KB         256         Yes         8         SSOP 28-pin           BF0430DJ020SG         4KB         256         Yes         8         PDIP 28-pin           BF0430QJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431DJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431HJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431HJ020SG         4KB         256         Yes         0         PDIP 28-pin           BF0431PJ020SG         4KB         256         Yes <td< td=""><td>8F0430PH020SG</td><td>4KB</td><td>256</td><td>Yes</td><td>7</td><td>PDIP 20-pin</td></td<> | 8F0430PH020SG        | 4KB          | 256   | Yes  | 7   | PDIP 20-pin |

| BF0431HH020SG         4KB         256         Yes         0         SSOP 20-pin           BF0431PH020SG         4KB         256         Yes         0         PDIP 20-pin           BF0431QH020SG         4KB         256         Yes         0         QFN 20-pin           BF0430SJ020SG         4KB         256         Yes         0         QFN 20-pin           BF0430SJ020SG         4KB         256         Yes         8         SOIC 28-pin           BF0430HJ020SG         4KB         256         Yes         8         SOIP 28-pin           BF0430QJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0430QJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0431SJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431HJ020SG         4KB         256         Yes         0         SOIP 28-pin           BF0431HJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0431HJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0431QJ020SG         4KB         256         Yes         7 </td <td>8F0430QH020SG</td> <td>4KB</td> <td>256</td> <td>Yes</td> <td>7</td> <td>QFN 20-pin</td>   | 8F0430QH020SG        | 4KB          | 256   | Yes  | 7   | QFN 20-pin  |

| BF0431PH020SG         4KB         256         Yes         0         PDIP 20-pin           BF0431QH020SG         4KB         256         Yes         0         QFN 20-pin           BF0430SJ020SG         4KB         256         Yes         8         SOIC 28-pin           BF0430HJ020SG         4KB         256         Yes         8         SSOP 28-pin           BF0430PJ020SG         4KB         256         Yes         8         PDIP 28-pin           BF0430QJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0430QJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0431SJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431HJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431HJ020SG         4KB         256         Yes         0         PDIP 28-pin           BF0431Q020SG         4KB         256         Yes         0         QFN 28-pin           BF0431Q020SG         4KB         256         Yes         0         QFN 28-pin           BF0430H020EG         4KB         256         Yes         7 <td>8F0431SH020SG</td> <td>4KB</td> <td>256</td> <td>Yes</td> <td>0</td> <td>SOIC 20-pin</td>         | 8F0431SH020SG        | 4KB          | 256   | Yes  | 0   | SOIC 20-pin |

| BF0431QH020SG       4KB       256       Yes       0       QFN 20-pin         BF0430SJ020SG       4KB       256       Yes       8       SOIC 28-pin         BF0430HJ020SG       4KB       256       Yes       8       SSOP 28-pin         BF0430PJ020SG       4KB       256       Yes       8       PDIP 28-pin         BF0430QJ020SG       4KB       256       Yes       8       QFN 20-pin         BF0430QJ020SG       4KB       256       Yes       8       QFN 28-pin         BF0431SJ020SG       4KB       256       Yes       0       SOIC 28-pin         BF0431HJ020SG       4KB       256       Yes       0       SOIC 28-pin         BF0431HJ020SG       4KB       256       Yes       0       SOIC 28-pin         BF0431PJ020SG       4KB       256       Yes       0       PDIP 28-pin         BF0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         BF0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         BF0430H020EG       4KB       256       Yes       7       SOIC 20-pin         BF0430H020EG       4KB       256       Yes <td< td=""><td>8F0431HH020SG</td><td>4KB</td><td>256</td><td>Yes</td><td>0</td><td>SSOP 20-pin</td></td<>                                                                              | 8F0431HH020SG        | 4KB          | 256   | Yes  | 0   | SSOP 20-pin |

| BF0430SJ020SG         4KB         256         Yes         8         SOIC 28-pin           BF0430HJ020SG         4KB         256         Yes         8         SSOP 28-pin           BF0430PJ020SG         4KB         256         Yes         8         PDIP 28-pin           BF0430QJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0430QJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0431SJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431HJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431HJ020SG         4KB         256         Yes         0         SSOP 28-pin           BF0431PJ020SG         4KB         256         Yes         0         PDIP 28-pin           BF0431QJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0430LQJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0430SH020EG         4KB         256         Yes         7         SOIC 20-pin           BF0430HH020EG         4KB         256         Yes                                                                                                            | 8F0431PH020SG        | 4KB          | 256   | Yes  | 0   | PDIP 20-pin |

| BF0430HJ020SG       4KB       256       Yes       8       SSOP 28-pin         BF0430PJ020SG       4KB       256       Yes       8       PDIP 28-pin         BF0430QJ020SG       4KB       256       Yes       8       QFN 28-pin         BF0431SJ020SG       4KB       256       Yes       0       SOIC 28-pin         BF0431HJ020SG       4KB       256       Yes       0       SSOP 28-pin         BF0431PJ020SG       4KB       256       Yes       0       SSOP 28-pin         BF0431PJ020SG       4KB       256       Yes       0       PDIP 28-pin         BF0431PJ020SG       4KB       256       Yes       0       QFN 28-pin         BF0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         BF0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         BF0430H020EG       4KB       256       Yes       7       SOIC 20-pin         BF0430H020EG       4KB       256       Yes       7       SOIC 20-pin         BF0430HH020EG       4KB       256       Yes       7       SSOP 20-pin                                                                                                                                                                                                                                           | 8F0431QH020SG        | 4KB          | 256   | Yes  | 0   | QFN 20-pin  |

| 3F0430PJ020SG       4KB       256       Yes       8       PDIP 28-pin         3F0430QJ020SG       4KB       256       Yes       8       QFN 28-pin         3F0431SJ020SG       4KB       256       Yes       0       SOIC 28-pin         3F0431HJ020SG       4KB       256       Yes       0       SOIC 28-pin         3F0431HJ020SG       4KB       256       Yes       0       SSOP 28-pin         3F0431PJ020SG       4KB       256       Yes       0       PDIP 28-pin         3F0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         3F0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         3F0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         3F0430H020EG       4KB       256       Yes       7       SOIC 20-pin         3F0430H020EG       4KB       256       Yes       7       SOIC 20-pin         3F0430HH020EG       4KB       256       Yes       7       SSOP 20-pin                                                                                                                                                                                                                                                                                                                         | 8F0430SJ020SG        | 4KB          | 256   | Yes  | 8   | SOIC 28-pin |

| BF0430QJ020SG         4KB         256         Yes         8         QFN 28-pin           BF0431SJ020SG         4KB         256         Yes         0         SOIC 28-pin           BF0431HJ020SG         4KB         256         Yes         0         SSOP 28-pin           BF0431PJ020SG         4KB         256         Yes         0         PDIP 28-pin           BF0431QJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0431QJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0431QJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0430BH020EG         4KB         256         Yes         7         SOIC 20-pin           BF0430HH020EG         4KB         256         Yes         7         SOIC 20-pin                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8F0430HJ020SG        | 4KB          | 256   | Yes  | 8   | SSOP 28-pin |

| 3F0431SJ020SG       4KB       256       Yes       0       SOIC 28-pin         3F0431HJ020SG       4KB       256       Yes       0       SSOP 28-pin         3F0431PJ020SG       4KB       256       Yes       0       PDIP 28-pin         3F0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         3F0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         3F0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         3F0430H020EG       4KB       256       Yes       7       SOIC 20-pin         3F0430HH020EG       4KB       256       Yes       7       SSOP 20-pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8F0430PJ020SG        | 4KB          | 256   | Yes  | 8   | PDIP 28-pin |

| BF0431HJ020SG         4KB         256         Yes         0         SSOP 28-pin           BF0431PJ020SG         4KB         256         Yes         0         PDIP 28-pin           BF0431QJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0431QJ020SG         4KB         256         Yes         0         QFN 28-pin           BF0430SH020EG         4KB         256         Yes         7         SOIC 20-pin           BF0430HH020EG         4KB         256         Yes         7         SSOP 20-pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8F0430QJ020SG        | 4KB          | 256   | Yes  | 8   | QFN 28-pin  |

| BF0431PJ020SG       4KB       256       Yes       0       PDIP 28-pin         BF0431QJ020SG       4KB       256       Yes       0       QFN 28-pin         attended Temperature:       -40°C to 105°C       0       SOIC 20-pin         BF0430SH020EG       4KB       256       Yes       7         BF0430HH020EG       4KB       256       Yes       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8F0431SJ020SG        | 4KB          | 256   | Yes  | 0   | SOIC 28-pin |