# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0130sh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Description**

The Z8 Encore! F0830 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and the pin configurations for each of the package styles. For information about the physical package specifications, see the <u>Packaging</u> chapter on page 199.

# **Available Packages**

Table 3 lists the package styles that are available for each device in the Z8 Encore! F0830 Series product line.

| Part<br>Number | ADC | 20-pin<br>QFN | 20-pin<br>SOIC | 20-pin<br>SSOP | 20-pin<br>PDIP | 28-pin<br>QFN | 28-pin<br>SOIC | 28-pin<br>SSOP | 28-pin<br>PDIP |

|----------------|-----|---------------|----------------|----------------|----------------|---------------|----------------|----------------|----------------|

| Z8F1232        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F1233        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0830        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0831        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0430        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0431        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0230        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0231        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0130        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0131        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

Table 3. Z8 Encore! F0830 Series Package Options

# **Pin Configurations**

Figures 2 and 3 display the pin configurations of all of the packages available in the Z8 Encore! F0830 Series. See <u>Table 4</u> on page 11 for a description of the signals. Analog input alternate functions (ANAx) are not available on the following devices:

- Z8F0831

- Z8F0431

- Z8F0131

- Z8F0231

- Z8F1233

# **Signal Descriptions**

Table 4 describes the Z8 Encore! F0830 Series signals. See the <u>Pin Configurations</u> section on page 7 to determine the signals available for each specific package style.

| Signal<br>Mnemonic                             | I/O       | Description                                                                                                                     |

|------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose                                | I/O Ports | s A–D                                                                                                                           |

| PA[7:0]                                        | I/O       | Port A. These pins are used for general purpose I/O.                                                                            |

| PB[7:0]                                        | I/O       | Port B. These pins are used for general purpose I/O. PB6 and PB7 are available only in those devices without an ADC.            |

| PC[7:0]                                        | I/O       | Port C. These pins are used for general purpose I/O.                                                                            |

| PD[0]                                          | I/O       | Port D. This pin is used for general purpose output only.                                                                       |

| Note: PB6 and PB7<br>placed by AV <sub>I</sub> |           | available in 28-pin packages without ADC. In 28-pin packages with ADC, they are re- $^{\prime}_{\rm SS}$                        |

| Timers                                         |           |                                                                                                                                 |

| T0OUT/T1OUT                                    | 0         | Timer output 0–1. These signals are the output from the timers.                                                                 |

| T0OUT/T1OUT                                    | 0         | Timer complement output 0–1. These signals are output from the timers in PWM DUAL OUTPUT Mode.                                  |

| T0IN/T1IN                                      | I         | Timer Input 0–1. These signals are used as the capture, gating and counte inputs. The T0IN signal is multiplexed T0OUT signals. |

| Comparator                                     |           |                                                                                                                                 |

| CINP/CINN                                      | I         | Comparator inputs. These signals are the positive and negative inputs to the comparator.                                        |

| COUT                                           | 0         | Comparator output. This is the output of the comparator.                                                                        |

| Analog                                         |           |                                                                                                                                 |

| ANA[7:0]                                       | I         | Analog port. These signals are used as inputs to the analog-to-digital converter (ADC).                                         |

| V <sub>REF</sub>                               | I/O       | Analog-to-digital converter reference voltage input.                                                                            |

|                                                |           | <b>Note:</b> When configuring ADC using external $V_{REF}$ , PB5 is used as $V_{REF}$ in 28-pin package.                        |

|                                                |           | nals are available only in the 28-pin packages with ADC. They are replaced by PB6 ages without ADC.                             |

## **Table 4. Signal Descriptions**

## Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! F0830 Series device is in STOP Mode and the external RESET pin is driven low, a system reset occurs. Because of a glitch filter operating on the RESET pin, the low pulse must be greater than the minimum width specified about 12 ns or it is ignored. The EXT bit in the Reset Status (RSTSTAT) Register is set.

## **Debug Pin Driven Low**

Debug reset is initiated when the On-Chip Debugger detects any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received STOP bit is Low)

- Transmit collision (simultaneous OCD and host transmission detected by the OCD)

When the Z8F0830 Series device is operating in STOP Mode, the debug reset will cause a system reset. The On-Chip Debugger block is not reset, but the remainder of the chip's operations go through a normal system reset. The POR bit in the Reset Status (RSTSTAT) Register is set to 1.

## **Reset Register Definitions**

The following sections define the Reset registers.

### **Reset Status Register**

The Reset Status (RSTSTAT) Register, shown in Table 12, is a read-only register that indicates the source of the most recent Reset event, Stop Mode Recovery event or Watchdog Timer time-out event. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer Control Register, which is writeonly.

## HALT Mode

Executing the eZ8 CPU HALT instruction places the device into HALT Mode. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any one of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as digital inputs must be driven to  $V_{DD}$  when pull-up register bit is enabled or to one of power rail ( $V_{DD}$  or GND) when pull-up register bit is disabled.

## **Peripheral Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! F0830 Series devices. Disabling a given peripheral minimizes its power consumption.

## **Power Control Register Definitions**

## **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

| Port                | Pin | Mnemonic  | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-----------|--------------------------------|-----------------------------------------|

| Port C <sup>3</sup> | PC0 | Reserved  |                                | AFS1[0]: 0                              |

|                     |     | ANA4/CINP | ADC or comparator input        | AFS1[0]: 1                              |

| -                   | PC1 | Reserved  |                                | AFS1[1]: 0                              |

|                     |     | ANA5/CINN | ADC or comparator input        | AFS1[1]: 1                              |

|                     | PC2 | Reserved  |                                | AFS1[2]: 0                              |

|                     |     | ANA6      | ANA6 ADC analog input          |                                         |

|                     | PC3 | COUT      | Comparator output              | AFS1[3]: 0                              |

|                     |     | Reserved  |                                | AFS1[3]: 1                              |

|                     | PC4 | Reserved  |                                | AFS1[4]: 0                              |

|                     |     |           |                                | AFS1[4]: 1                              |

|                     | PC5 | Reserved  |                                | AFS1[5]: 0                              |

|                     |     |           |                                | AFS1[5]: 1                              |

|                     | PC6 | Reserved  |                                | AFS1[6]: 0                              |

|                     |     |           |                                | AFS1[6]: 1                              |

|                     | PC7 | Reserved  |                                | AFS1[7]: 0                              |

|                     |     |           |                                | AFS1[7]: 1                              |

| Port D <sup>1</sup> | PD0 | RESET     | Default to be Reset function   | N/A                                     |

#### Table 16. Port Alternate Function Mapping (Continued)

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

# LED Drive Enable Register

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | LEDEN[7:0] |     |     |     |     |     |     |     |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F82H       |     |     |     |     |     |     |     |

| Bit   | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | LED Drive Enable                                                                                                                                                           |

| LEDEN | These bits determine which Port C pins are connected to an internal current sink.<br>0 = Tristate the Port C pin.<br>1= Connect controlled current sink to the Port C pin. |

## LED Drive Level High Register

The LED Drive Level High Register, shown in Table 32, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7            | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|--------------|-----------------------------|---|---|---|---|---|---|--|

| Field   | LEDLVLH[7:0] |                             |   |   |   |   |   |   |  |

| RESET   | 0            | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |  |

| R/W     | R/W          | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address |              | F83H                        |   |   |   |   |   |   |  |

## Bit Description

[7:0] LED Level High Bits

LEDLVLH {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3mA.

01= 7 mA.

10= 13mA.

11= 20mA.

## Table 45. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7        | 6    | 5   | 4   | 3     | 2     | 1     | 0     |  |

|---------|----------|------|-----|-----|-------|-------|-------|-------|--|

| Field   | Reserved |      |     |     | C3ENH | C2ENH | C1ENH | C0ENH |  |

| RESET   | 0        | 0    | 0   | 0   | 0     | 0     | 0     | 0     |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   |  |

| Address |          | FC7H |     |     |       |       |       |       |  |

| Bit          | Description                                                                     |

|--------------|---------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit                                       |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit                                       |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit                                       |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit                                       |

## Table 46. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7        | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|---------|----------|-----|-----|-----|-------|-------|-------|-------|

| Field   | Reserved |     |     |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET   | 0        | 0   | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| Address | FC8H     |     |     |     |       |       |       |       |

| Bit          | Description                                                                     |

|--------------|---------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000. |

| [3]<br>C3ENL | Port C3 Interrupt Request Enable Low Bit                                        |

| [2]<br>C2ENL | Port C2 Interrupt Request Enable Low Bit                                        |

| [1]<br>C1ENL | Port C1 Interrupt Request Enable Low Bit                                        |

| [0]<br>COENL | Port C0 Interrupt Request Enable Low Bit                                        |

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period.

If TPOL bit is set to 0, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL bit is set to 1, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$

## **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to 16-bit PWM match value stored in the timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the timer output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the timer output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The timer output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the timer output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The timer output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal: the timer output complement. The timer output complement is the complement of the timer output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a Low to a High (inactive to active) to ensure a time gap between the deassertion of one PWM output to the assertion of its complement.

| Bit                     | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6]<br>TPOL<br>(cont'd) | <ul> <li>PWM DUAL OUTPUT Mode</li> <li>0 = Timer output is forced Low (0) and timer output complement is forced High (1), when the timer is disabled. When enabled and the PWM count matches, the timer output is forced High (1) and forced Low (0) when enabled and reloaded. When enabled and the PWM count matches, the timer output complement is forced Low (0) and forced High (1) when enabled and reloaded.</li> <li>1 = Timer output is forced High (1) and timer output complement is forced Low (0) when the timer is disabled. When enabled and the PWM count matches, the timer output is forced Low (0) when the timer is disabled. When enabled and the PWM count matches, the timer output is forced Low (0) and forced High (1) when enabled and reloaded. When enabled and the PWM count matches, the timer output complement is forced High (1) and forced Low (0) when the timer is disabled. The PWMD field in the TxCTL0 register determines an optional added delay on the assertion (Low to High) transition of both timer output and timer output complement for deadband generation.</li> </ul> |

|                         | <ul> <li>CAPTURE RESTART Mode</li> <li>0 = Count is captured on the rising edge of the timer input signal.</li> <li>1 = Count is captured on the falling edge of the timer input signal.</li> <li>COMPARATOR COUNTER Mode</li> <li>When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                         | <b>Caution:</b> When the timer output alternate function TxOUT on a GPIO port pin is enabled, TxOUT will change to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Additionally, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit when the timer is enabled and running does not immediately change the polarity TxOUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [5:3]<br>PRES           | Prescale Value<br>The timer input clock is divided by 2 <sup>PRES</sup> , where PRES can be set from 0 to 7. The prescaler is<br>reset each time the timer is disabled. This reset ensures proper clock division each time the<br>timer is restarted.<br>000 = Divide by 1.<br>001 = Divide by 2.<br>010 = Divide by 4.<br>011 = Divide by 8.<br>100 = Divide by 16.<br>101 = Divide by 32.<br>110 = Divide by 64.<br>111 = Divide by 128.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 60 through 62, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. This 24-bit value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate reload value; reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                         | WDTU |      |      |      |      |      |      |      |

| RESET                                                                                         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W                                                                                           | R/W* |

| Address                                                                                       | FF1H |      |      |      |      |      |      |      |

| Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |      |

### Table 60. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

| Bit         | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Field       | WDTH                                                                                          |      |      |      |      |      |      |      |

| RESET       | 0                                                                                             | 0    | 0    | 0    | 0    | 1    | 0    | 0    |

| R/W         | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |

| Address     | FF2H                                                                                          |      |      |      |      |      |      |      |

| Note: *A re | Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte, bits[15:8] of the 24-bit WDT reload value. |

## ADC Data High Byte Register

The ADC Data High Byte Register, listed in Table 64, contains the upper eight bits of the ADC output. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

## Table 64. ADC Data High Byte Register (ADCD\_H)

| Bit     | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------|---|---|---|---|---|---|---|--|

| Field   | ADCDH |   |   |   |   |   |   |   |  |

| RESET   |       | X |   |   |   |   |   |   |  |

| R/W     | R     |   |   |   |   |   |   |   |  |

| Address | F72H  |   |   |   |   |   |   |   |  |

|         |       |   |   |   |   |   |   |   |  |

| Bit   | Description                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------|

| [7:0] | ADC High Byte                                                                                                       |

| ADCDH | 00h–FFh = The last conversion output is held in the data registers until the next ADC conver-<br>sion is completed. |

## ADC Data Low Bits Register

The ADC Data Low Bits Register, shown in Table 65, contains the lower bits of the ADC output. Access to the ADC Data Low Bits Register is read-only. Reading the ADC Data High Byte Register latches lower bits of the ADC in the ADC Data Low Bits Register.

| Bit     | 7   | 6    | 5        | 4 | 3 | 2 | 1 | 0 |

|---------|-----|------|----------|---|---|---|---|---|

| Field   | ADO | CDL  | Reserved |   |   |   |   |   |

| RESET   | )   | K    |          |   | ) | < |   |   |

| R/W     | F   | २    | R        |   |   |   |   |   |

| Address |     | F73H |          |   |   |   |   |   |

| Table 65. | ADC Data L | ow Bits R | Register (A | ADCD_L) |

|-----------|------------|-----------|-------------|---------|

|-----------|------------|-----------|-------------|---------|

| Bit            | Description                                                                                                                                                                                                                                  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]<br>ADCDL | ADC Low Bits<br>00–11b = These bits are the two least-significant bits of the 10-bit ADC output. These bits are<br>undefined after a reset. The low bits are latched into this register whenever the ADC Data High<br>Byte Register is read. |

| [5:0]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                 |

# **Comparator Control Register Definitions**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference. The GPIO pin is always used as positive comparator input.

| Bit             | 7                                                                                                                                                                                                             | 6                                          | 5            | 4           | 3            | 2   | 1      | 0     |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|-------------|--------------|-----|--------|-------|

| Field           | Reserved                                                                                                                                                                                                      | INNSEL                                     |              | REF         | LVL          |     | Rese   | erved |

| RESET           | 0                                                                                                                                                                                                             | 0                                          | 0            | 1           | 0            | 1   | 0      | 0     |

| R/W             | R/W                                                                                                                                                                                                           | R/W                                        | R/W          | R/W         | R/W          | R/W | R/W    | R/W   |

| Address         |                                                                                                                                                                                                               |                                            |              | F9          | 0H           |     |        |       |

| Bit             | Descriptio                                                                                                                                                                                                    | n                                          |              |             |              |     |        |       |

| [7]             | Reserved<br>This bit is re                                                                                                                                                                                    | eserved and                                | must be pro  | ogrammed to | o 0.         |     |        |       |

| [6]<br>INNSEL   | 0 = internal                                                                                                                                                                                                  | ect for Nega<br>reference d<br>reference e | isabled, GP  | •           | •            |     | input. |       |

| [5:2]<br>REFLVL | This referent<br>$0000 = 0.0^{\circ}$<br>$0001 = 0.2^{\circ}$<br>$0010 = 0.4^{\circ}$<br>$0100 = 0.8^{\circ}$<br>$0100 = 1.2^{\circ}$<br>$0111 = 1.4^{\circ}$<br>$1000 = 1.6^{\circ}$<br>$1001 = 1.8^{\circ}$ | V.<br>V.<br>V.<br>V (Default).<br>V.<br>V. | endent of th | e ADC volta | ge reference | 9.  |        |       |

| [1:0]           | Reserved<br>These bits a                                                                                                                                                                                      | are reserved                               | l and must b | e programm  | ned to 00.   |     |        |       |

## Table 68. Comparator Control Register (CMP0)

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

## Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

## Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

# Flash Option Bit Control Register Definitions

This section briefly describes the features of the Trim Bit Address and Data registers.

## **Trim Bit Address Register**

The Trim Bit Address Register, shown in Table 78, contains the target address to access the trim option bits. Trim bit addresses in the range 00h–1Fh map to the information area at addresses 20h–3Fh, as shown in Table 79.

| Bit     | 7   | 6                                     | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|---------------------------------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | TRMADR: Trim Bit Address (00H to 1FH) |     |     |     |     |     |     |  |

| RESET   | 0   | 0                                     | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W                                   | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     |                                       |     | FF  | 6H  |     |     |     |  |

### Table 78. Trim Bit Address Register (TRMADR)

| Table 79. Trim E | Bit Address Map             |

|------------------|-----------------------------|

| Trim Bit Address | Information Area<br>Address |

| 00h              | 20h                         |

| 01h              | 21h                         |

| 02h              | 22h                         |

| 03h              | 23h                         |

| :                | :                           |

| 1Fh              | 3Fh                         |

## Table 79. Trim Bit Address Map

## **Trim Bit Data Register**

The Trim Bit Data Register, shown in Table 80, contains the read or write data to access the trim option bits.

### Table 83. Trim Bit Address Space

| Address | Function                      |

|---------|-------------------------------|

| 00h     | ADC reference voltage         |

| 01h     | ADC and comparator            |

| 02h     | Internal Precision Oscillator |

| 03h     | Oscillator and VBO            |

| 06h     | ClkFltr                       |

### Table 84. Trim Option Bits at 0000H (ADCREF)

| Bit       | 7           | 6             | 5             | 4           | 3           | 2    | 1   | 0 |  |

|-----------|-------------|---------------|---------------|-------------|-------------|------|-----|---|--|

| Field     |             | Al            | DCREF_TRI     | Reserved    |             |      |     |   |  |

| RESET     |             |               | U             |             |             | U    |     |   |  |

| R/W       |             | R/W           |               |             |             |      | R/W |   |  |

| Address   |             |               | Infor         | mation Page | e Memory 00 | )20H |     |   |  |

| Note: U = | Unchanged b | by Reset. R/W | / = Read/Writ | e.          |             |      |     |   |  |

| Bit                  | Description                                                                          |

|----------------------|--------------------------------------------------------------------------------------|

| [7:3]<br>ADCREF_TRIM | ADC Reference Voltage Trim Byte<br>Contains trimming bits for ADC reference voltage. |

| [2:0]                | <b>Reserved</b><br>These bits are reserved and must be programmed to 111.            |

**Note:** The bit values used in Table 84 are set at the factory; no calibration is required.

| Bit       | 7           | 6             | 5             | 4           | 3           | 2    | 1   | 0   |

|-----------|-------------|---------------|---------------|-------------|-------------|------|-----|-----|

| Field     |             |               |               | Rese        | erved       |      |     |     |

| RESET     | U           | U             | U             | U           | U           | U    | U   | U   |

| R/W       | R/W         | R/W           | R/W           | R/W         | R/W         | R/W  | R/W | R/W |

| Address   |             |               | Infor         | mation Page | e Memory 00 | 021H |     |     |

| Note: U = | Unchanged b | by Reset. R/W | / = Read/Writ | te.         |             |      |     |     |

| Bit       | De          | scription     |               |             |             |      |     |     |

### Table 85. Trim Option Bits at 0001H (TADC\_COMP)

| Bit   | Description                                                      |

|-------|------------------------------------------------------------------|

| [7:0] | Reserved                                                         |

|       | Altering this register may result in incorrect device operation. |

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a system reset

## **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 start bit, 8 data bits (least-significant bit first) and 1 stop bit. See Figure 23.

| <br>START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-----------|----|----|----|----|----|----|----|----|------|

| OTAKI     | 00 | ы  | 02 | 05 | D4 | 00 | DU | ы  | 0101 |

## Figure 23. OCD Data Format

## **OCD Autobaud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an autobaud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits low (one Start bit plus 7 data bits), framed between high bits. The autobaud detector measures this period and sets the OCD baud rate generator accordingly.

The autobaud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 94 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency<br>(MHz) | Recommended<br>Maximum Baud Rate<br>(kbps) | Recommended<br>Standard PC Baud Rate<br>(bps) | Minimum Baud Rate<br>(kbps) |

|------------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                               | 2500.0                                     | 1,843,200                                     | 39                          |

| 1.0                                | 125.0                                      | 115,200                                       | 1.95                        |

| 0.032768 (32 KHz)                  | 4.096                                      | 2400                                          | 0.064                       |

| Table 9 | 94. OCD | Baud-Rate | Limits |

|---------|---------|-----------|--------|

|         |         |           |        |

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

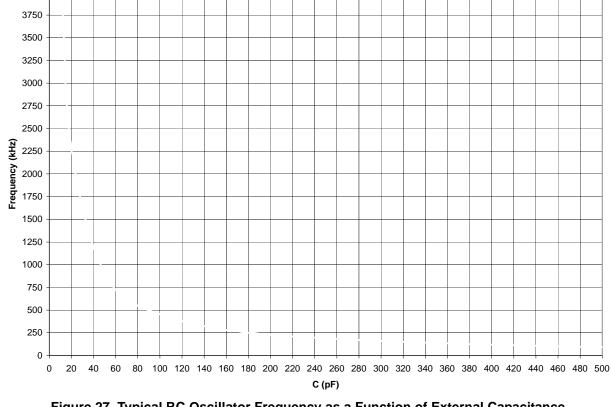

Figure 27. Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$  Resistor

**Caution:** When using the external RC OSCILLATOR Mode, the oscillator can stop oscillating if the power supply drops below 2.7V but before it drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7V.

160

4000

|                 |                                  | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |      |             |       |                         |

|-----------------|----------------------------------|----------------------------------------------------------------|-----|-----|-------------------------------------------------------------------|------|-------------|-------|-------------------------|

| Symbol          | Parameter                        | Min                                                            | Тур | Max | Min                                                               | Тур  | Мах         | Units | Conditions              |

| Z <sub>IN</sub> | Input Impedance                  |                                                                |     |     | 10                                                                |      |             | MΩ    |                         |

| V <sub>IN</sub> | Input Voltage<br>Range           |                                                                |     |     | 0                                                                 |      | 2.0         | V     | Internal refer-<br>ence |

|                 |                                  |                                                                |     |     | 0                                                                 |      | 0.9*VD<br>D |       | External refer-<br>ence |

|                 | Conversion Time                  |                                                                |     |     | 11.9                                                              |      |             | μs    | 20MHz (ADC<br>Clock)    |

|                 | Input Bandwidth                  |                                                                |     |     |                                                                   | 500  |             | KHz   |                         |

|                 | Wake Up Time                     |                                                                |     |     |                                                                   | 0.02 |             | ms    | Internal refer-<br>ence |

|                 |                                  |                                                                |     |     |                                                                   | 10   |             |       | External refer-<br>ence |

|                 | Input Clock Duty                 |                                                                |     |     | 45                                                                | 50   | 55          |       |                         |

|                 | Maximum Input<br>Clock Frequency |                                                                |     |     |                                                                   |      | 20          | MHz   |                         |

## Table 122. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

| Table 123. | Comparator | Electrical | Characteristics |

|------------|------------|------------|-----------------|

|------------|------------|------------|-----------------|

|                   |                                                     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |     |      |       |                                          |

|-------------------|-----------------------------------------------------|----------------------------------------------------------------|-----|-----|-------------------------------------------------------------------|-----|------|-------|------------------------------------------|

| Symbol            | Parameter                                           | Min                                                            | Тур | Max | Min                                                               | Тур | Max  | Units | Conditions                               |

| V <sub>OS</sub>   | Input DC Offset                                     |                                                                |     |     |                                                                   | 5   |      | mV    |                                          |

| V <sub>CREF</sub> | Programmable<br>Internal Reference<br>Voltage Range |                                                                |     |     | 0                                                                 |     | 1.8  | V     | User-program-<br>mable in 200<br>mV step |

| V <sub>CREF</sub> | Programmable<br>internal reference<br>voltage       |                                                                |     |     | 0.92                                                              | 1.0 | 1.08 | V     | Default<br>(CMP0[REFLVL]<br>=5H)         |

| T <sub>PROP</sub> | Propagation delay                                   |                                                                |     |     |                                                                   | 100 |      | ns    |                                          |

| V <sub>HYS</sub>  | Input hysteresis                                    |                                                                |     |     |                                                                   | 8   |      | mV    |                                          |

194

# Low Power Control

For more information about the Power Control Register, see the <u>Power Control Register</u> <u>Definitions</u> section on page 31.

## Hex Address: F80

| Bit     | 7        | 6    | 5   | 4   | 3        | 2        | 1    | 0        |  |  |

|---------|----------|------|-----|-----|----------|----------|------|----------|--|--|

| Field   | Reserved |      |     | VBO | Reserved | Reserved | COMP | Reserved |  |  |

| RESET   | 1        | 0    | 0   | 0   | 1        | 0        | 0    | 0        |  |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W      | R/W      | R/W  | R/W      |  |  |

| Address |          | F80H |     |     |          |          |      |          |  |  |

### Table 151. Power Control Register 0 (PWRCTL0)

## Hex Address: F81

This address range is reserved.

# **LED Controller**

For more information about the LED Drive registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

## Hex Address: F82

| Bit     | 7   | 6          | 5   | 4   | 3    | 2   | 1   | 0   |  |  |  |  |  |

|---------|-----|------------|-----|-----|------|-----|-----|-----|--|--|--|--|--|

| Field   |     | LEDEN[7:0] |     |     |      |     |     |     |  |  |  |  |  |

| RESET   | 0   | 0          | 0   | 0   | 0    | 0   | 0   | 0   |  |  |  |  |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W  | R/W | R/W | R/W |  |  |  |  |  |

| Address |     |            |     | F8  | F82H |     |     |     |  |  |  |  |  |

## Table 152. LED Drive Enable (LEDEN)

## Hex Address: FD7

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |       | FD7H  |       |       |       |       |       |       |  |  |

## Table 176. Port B Output Data Register (PBOUT)

## Hex Address: FD8

### Table 177. Port C GPIO Address Register (PCADDR)

| Bit     | 7    | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------|------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |      | PADDR[7:0] |     |     |     |     |     |     |  |  |

| RESET   |      | 00H        |     |     |     |     |     |     |  |  |

| R/W     | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | FD8H |            |     |     |     |     |     |     |  |  |

## Hex Address: FD9

### Table 178. Port C Control Registers (PCCTL)

| Bit     | 7    | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------|------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |      | PCTL |     |     |     |     |     |     |  |  |

| RESET   |      | 00H  |     |     |     |     |     |     |  |  |

| R/W     | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | FD9H |      |     |     |     |     |     |     |  |  |

## Hex Address: FDA

### Table 179. Port C Input Data Registers (PCIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |  |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |  |  |

| Address |      | FDAH |      |      |      |      |      |      |  |  |