# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0131hh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address (Hex)    | Register Description             | Mnemonic | Reset (Hex) | Page No |

|------------------|----------------------------------|----------|-------------|---------|

| Interrupt Contro | oller (cont'd)                   |          |             |         |

| FCE              | Shared interrupt select          | IRQSS    | 00          | 66      |

| FCF              | Interrupt control                | IRQCTL   | 00          | 67      |

| GPIO Port A      |                                  |          |             |         |

| FD0              | Port A address                   | PAADDR   | 00          | 39      |

| FD1              | Port A control                   | PACTL    | 00          | 41      |

| FD2              | Port A input data                | PAIN     | XX          | 41      |

| FD3              | Port A output data               | PAOUT    | 00          | 41      |

| GPIO Port B      |                                  |          |             |         |

| FD4              | Port B address                   | PBADDR   | 00          | 39      |

| FD5              | Port B control                   | PBCTL    | 00          | 41      |

| FD6              | Port B input data                | PBIN     | XX          | 41      |

| FD7              | Port B output data               | PBOUT    | 00          | 41      |

| GPIO Port C      |                                  |          |             |         |

| FD8              | Port C address                   | PCADDR   | 00          | 39      |

| FD9              | Port C control                   | PCCTL    | 00          | 41      |

| FDA              | Port C input data                | PCIN     | XX          | 41      |

| FDB              | Port C output data               | PCOUT    | 00          | 41      |

| GPIO Port D      |                                  |          |             |         |

| FDC              | Port D address                   | PDADDR   | 00          | 39      |

| FDD              | Port D control                   | PDCTL    | 00          | 41      |

| FDE              | Reserved                         |          | XX          |         |

| FDF              | Port D output data               | PDOUT    | 00          | 41      |

| FE0–FEF          | Reserved                         | _        | XX          |         |

| Watchdog Time    | r (WDT)                          |          |             |         |

| FF0              | Reset status                     | RSTSTAT  | XX          | 95      |

|                  | Watchdog Timer control           | WDTCTL   | XX          | 95      |

| FF1              | Watchdog Timer reload upper byte | WDTU     | FF          | 96      |

| FF2              | Watchdog Timer reload high byte  | WDTH     | FF          | 96      |

| FF3              | Watchdog Timer reload low byte   | WDTL     | FF          | 97      |

| FF4–FF5          | Reserved                         |          | XX          |         |

## Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

57

```

LDX r0, IRQ0

AND r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

### Software Interrupt Assertion

Program code can generate interrupts directly. Writing 1 to the correct bit in the interrupt request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the interrupt request register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

# **Interrupt Control Register Definitions**

The Interrupt Control registers enable individual interrupts, set interrupt priorities and indicate interrupt requests for all of the interrupts other than the Watchdog Timer interrupt, the primary oscillator fail trap and the Watchdog Oscillator fail trap interrupts.

## 73

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer reload in COMPARATOR COUNTER Mode, counting always begins at the reset value 0001H. Generally, in COMPARATOR COUNTER Mode, the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions is calculated with the following equation:

Comparator Output Transitions = Current Count Value – Start Value

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the timer PWM High and Low Byte registers to 0000H. This allows user software to determine if interrupts are generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt were generated by a reload.

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. The user can configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **COMPARE Mode**

In COMPARE Mode, the timer counts up to 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) upon compare.

If the timer reaches FFFFH, the timer resets to 0000H and continues counting.

Observe the following steps for configuring a timer for COMPARE Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

# Watchdog Timer

The Watchdog Timer (WDT) protects from corrupted or unreliable software, power faults and other system-level problems which can place the Z8 Encore! F0830 Series devices into unsuitable operating states. The features of the Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The Watchdog Timer is a retriggerable one-shot timer that resets or interrupts the Z8 Encore! F0830 Series devices when the WDT reaches its terminal count. The WDT uses a dedicated on-chip RC oscillator as its clock source. The WDT operates only in two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the WDT to operate immediately on reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is calculated using the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the 24-bit decimal value provided by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10KHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate<br>WDT Reload Value(with 10KHz Typical WI |                        |  |  |  |  |  |

|------------------|------------------|-------------------------------------------------------|------------------------|--|--|--|--|--|

| (Hex)            | (Decimal)        | Typical                                               | Description            |  |  |  |  |  |

| 000004           | 4                | 400µs                                                 | Minimum time-out delay |  |  |  |  |  |

| 000400           | 1024             | 102ms                                                 | Default time-out delay |  |  |  |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                            | Maximum time-out delay |  |  |  |  |  |

#### Table 58. Watchdog Timer Approximate Time-Out Delays

# **Comparator Control Register Definitions**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference. The GPIO pin is always used as positive comparator input.

| Bit             | 7                                                                                                                                                                                                                                                                          | 6                                                      | 5            | 4           | 3            | 2   | 1    | 0     |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------|-------------|--------------|-----|------|-------|--|--|--|

| Field           | Reserved                                                                                                                                                                                                                                                                   | INNSEL                                                 |              | REF         | LVL          |     | Rese | erved |  |  |  |

| RESET           | 0                                                                                                                                                                                                                                                                          | 0                                                      | 0            | 1           | 0            | 1   | 0    | 0     |  |  |  |

| R/W             | R/W                                                                                                                                                                                                                                                                        | R/W                                                    | R/W          | R/W         | R/W          | R/W | R/W  | R/W   |  |  |  |

| Address         |                                                                                                                                                                                                                                                                            |                                                        |              | F9          | 0H           |     |      |       |  |  |  |

| Bit             | Descriptio                                                                                                                                                                                                                                                                 | n                                                      |              |             |              |     |      |       |  |  |  |

| [7]             | Reserved<br>This bit is re                                                                                                                                                                                                                                                 | eserved and                                            | must be pro  | ogrammed to | o 0.         |     |      |       |  |  |  |

| [6]<br>INNSEL   | Signal Select for Negative Input<br>0 = internal reference disabled, GPIO pin used as negative comparator input.<br>1 = internal reference enabled as negative comparator input.                                                                                           |                                                        |              |             |              |     |      |       |  |  |  |

| [5:2]<br>REFLVL | This referent<br>$0000 = 0.0^{\circ}$<br>$0001 = 0.2^{\circ}$<br>$0010 = 0.4^{\circ}$<br>$0110 = 0.8^{\circ}$<br>$0100 = 0.8^{\circ}$<br>$0101 = 1.0^{\circ}$<br>$0110 = 1.2^{\circ}$<br>$0111 = 1.4^{\circ}$<br>$1000 = 1.6^{\circ}$<br>$1001 = 1.8^{\circ}$<br>1010-1111 | V.<br>V.<br>V.<br>V.<br>V.<br>V (Default).<br>V.<br>V. | endent of th | e ADC volta | ge reference | 9.  |      |       |  |  |  |

| [1:0]           | Reserved<br>These bits a                                                                                                                                                                                                                                                   | are reserved                                           | l and must b | e programm  | ned to 00.   |     |      |       |  |  |  |

### Table 68. Comparator Control Register (CMP0)

113

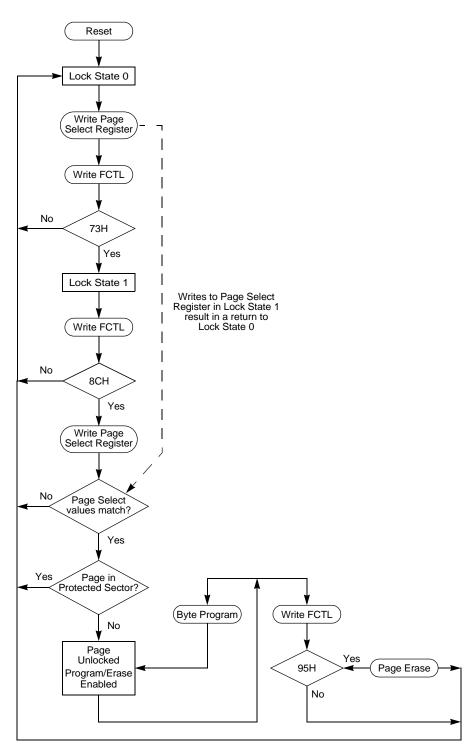

Figure 19. Flash Controller Operation Flow Chart

bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register. Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased. After setting a bit in the Sector Protect Register, the bit cannot be cleared by the user.

# **Byte Programming**

Flash memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either mass erase or page erase. When the Flash Controller is unlocked and mass erase is successfully enabled, all of the program memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and page erase is successfully enabled, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the page erase or mass erase commands.

Byte programming can be accomplished using the On-Chip Debugger's write memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the <u>eZ8 CPU</u> <u>Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>, for the description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control Register, except the mass erase or page erase commands.

**Caution:** The byte at each address within Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs.

| Bit     | 7   | 6                           | 5 | 4         | 3           | 2 | 1 | 0 |  |  |  |

|---------|-----|-----------------------------|---|-----------|-------------|---|---|---|--|--|--|

| Field   |     |                             |   | TRMDR: Tr | im Bit Data |   |   |   |  |  |  |

| RESET   | 0   | 0                           | 0 | 0         | 0           | 0 | 0 | 0 |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |           |             |   |   |   |  |  |  |

| Address |     |                             |   | FF        | 7H          |   |   |   |  |  |  |

#### Table 80. Trim Bit Data Register (TRMDR)

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits. See Tables 81 and 82.

| Bit              | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                          | 5                                                      | 4           | 3          | 2            | 1                                             | 0       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------|-------------|------------|--------------|-----------------------------------------------|---------|--|--|--|--|

| Field            | WDT_RES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | WDT_AO                                     | OSC_S                                                  | EL[1:0]     | VBO_AO     | FRP          | Reserved                                      | FWP     |  |  |  |  |

| RESET            | U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U                                          | U                                                      | U           | U          | U            | U                                             | U       |  |  |  |  |

| R/W              | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                                        | R/W                                                    | R/W         | R/W        | R/W          | R/W                                           | R/W     |  |  |  |  |

| Address          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Program Memory 0000H                       |                                                        |             |            |              |                                               |         |  |  |  |  |

| Note: U =        | Unchanged by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reset. R/W :                               | = Read/Write                                           |             |            |              |                                               |         |  |  |  |  |

| Bit              | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u></u>                                    |                                                        |             |            |              |                                               |         |  |  |  |  |

| [7]<br>WDT_RES   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                            |                                                        |             |            |              |                                               |         |  |  |  |  |

| [6]<br>WDT_AO    | 0 = On ap<br>Timer<br>1 = Watch<br>Watch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cannot be d<br>dog Timer is<br>dog Timer c | system pow<br>isabled.<br>s enabled oi<br>an only be o | n execution | of the WDT | instruction. | y enabled. V<br>Once enabl<br>ault setting fo | ed, the |  |  |  |  |

| [5:4]<br>OSC_SEL | <ul> <li>Watchdog Timer can only be disabled by a reset. This is the default setting for unprogrammed (erased) Flash.</li> <li>OSCILLATOR Mode Selection <ul> <li>00 = On-chip oscillator configured for use with external RC networks (&lt;4MHz).</li> <li>01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0MHz).</li> <li>10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 5.0MHz).</li> <li>11 = Maximum power for use with high frequency crystals (5.0MHz to 20.0MHz). This is the default setting for unprogrammed (erased) Flash.</li> </ul> </li> </ul> |                                            |                                                        |             |            |              |                                               |         |  |  |  |  |

Table 81. Flash Option Bits at Program Memory Address 0000H

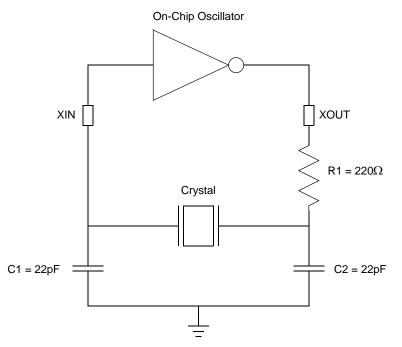

ister, the user code must wait at least 5000 IPO cycles for the crystal to stabilize. After this period, the crystal oscillator may be selected as the system clock.

Figure 25 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20MHz. Recommended 20MHz crystal specifications are provided in Table 100. Resistor R<sub>1</sub> is optional and limits total power dissipation by the crystal. Printed circuit board layout must add no more than 4pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

Figure 25. Recommended 20MHz Crystal Oscillator Configuration

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | Ω     | Maximum  |

| Load Capacitance (CL)               | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

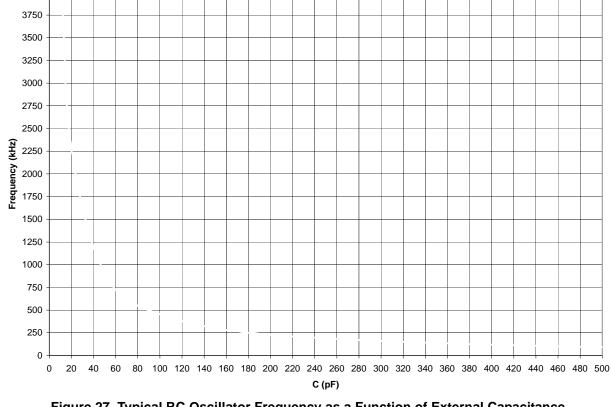

Figure 27. Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$  Resistor

**Caution:** When using the external RC OSCILLATOR Mode, the oscillator can stop oscillating if the power supply drops below 2.7V but before it drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7V.

160

4000

# eZ8 CPU Instruction Set

This chapter describes the following features of the eZ8 CPU instruction set: <u>Assembly Language Programming Introduction</u>: see page 162 <u>Assembly Language Syntax</u>: see page 163 <u>eZ8 CPU Instruction Notation</u>: see page 164 <u>eZ8 CPU Instruction Classes</u>: see page 166 <u>eZ8 CPU Instruction Summary</u>: see page 171

# **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (op codes and operands) to represent the instructions themselves. The op codes identify the instruction while the operands represent memory locations, registers or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement contains labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, these pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is provided in the following example.

| Assembly         |                                                                                           |     | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | Fetch | Instr. |

|------------------|-------------------------------------------------------------------------------------------|-----|-------------|---------------|---|---|-----|-----|---|---|-------|--------|

| Mnemonic         | Symbolic Operation                                                                        | dst | src         | (Hex)         | С | Ζ | S   | ۷   | D | Н |       |        |

| AND dst, src     | $dst \gets dst \; AND \; src$                                                             | r   | r           | 52            | _ | * | *   | 0   | _ | _ | 2     | 3      |

|                  |                                                                                           | r   | lr          | 53            | _ |   |     |     |   |   | 2     | 4      |

|                  |                                                                                           | R   | R           | 54            |   |   |     |     |   |   | 3     | 3      |

|                  |                                                                                           | R   | IR          | 55            | _ |   |     |     |   |   | 3     | 4      |

|                  |                                                                                           | R   | IM          | 56            | _ |   |     |     |   |   | 3     | 3      |

|                  |                                                                                           | IR  | IM          | 57            | _ |   |     |     |   |   | 3     | 4      |

| ANDX dst, src    | $dst \gets dst \; AND \; src$                                                             | ER  | ER          | 58            | _ | * | *   | 0   | _ | _ | 4     | 3      |

|                  |                                                                                           | ER  | IM          | 59            | _ |   |     |     |   |   | 4     | 3      |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |     |             | 2F            | - | _ | _   | _   | _ | _ | 1     | 2      |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r   |             | E2            | _ | * | *   | 0   | _ | _ | 2     | 2      |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r   |             | E2            | _ | * | *   | 0   | _ | _ | 2     | 2      |

| BRK              | Debugger Break                                                                            |     |             | 00            | - | _ | -   | -   | _ | _ | 1     | 1      |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r   |             | E2            | - | * | *   | 0   | - | - | 2     | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R   |             | D5            | Х | * | *   | 0   | - | - | 2     | 2      |

| BTJ p, bit, src, | if src[bit] = p                                                                           |     | r           | F6            | - | _ | -   | -   | _ | _ | 3     | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr          | F7            | _ |   |     |     |   |   | 3     | 4      |

| BTJNZ bit, src,  |                                                                                           |     | r           | F6            | - | _ | -   | -   | - | - | 3     | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr          | F7            | _ |   |     |     |   |   | 3     | 4      |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |     | r           | F6            | _ | - | _   | _   | - | - | 3     | 3      |

| dst              | $PC \gets PC + X$                                                                         |     | Ir          | F7            |   |   |     |     |   |   | 3     | 4      |

| CALL dst         | $SP \leftarrow SP -\!\!\!\!\!-\!\!\!\!\!2$                                                | IRR |             | D4            | _ | _ | -   | -   | _ | - | 2     | 6      |

|                  | @SP ← PC<br>PC ← dst                                                                      | DA  |             | D6            |   |   |     |     |   |   | 3     | 3      |

| CCF              | $C \leftarrow \sim C$                                                                     |     |             | EF            | * | _ | _   | _   | _ |   | 1     | 2      |

## Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F0830 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 115 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | 0       | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     |       |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 125     | mA    |       |

#### **Table 115. Absolute Maximum Ratings**

|                                                  |     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |        | = 2.7 to<br>40°C to - |     |        |                                                                                                                                                                             |

|--------------------------------------------------|-----|----------------------------------------------------------------|-----|--------|-----------------------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                        | Min | Тур                                                            | Max | Min    | Тур                   | Max | Units  | Notes                                                                                                                                                                       |

| Flash Byte Read<br>Time                          |     |                                                                |     | 50     | -                     | _   | ns     |                                                                                                                                                                             |

| Flash Byte Program<br>Time                       |     |                                                                |     | 20     | _                     | _   | μs     |                                                                                                                                                                             |

| Flash Page Erase<br>Time                         |     |                                                                |     | 50     | -                     | _   | ms     |                                                                                                                                                                             |

| Flash Mass Erase<br>Time                         |     |                                                                |     | 50     | -                     | _   | ms     |                                                                                                                                                                             |

| Writes to Single<br>Address Before Next<br>Erase |     |                                                                |     | _      | -                     | 2   |        |                                                                                                                                                                             |

| Flash Row Program<br>Time                        |     |                                                                |     | _      | -                     | 8   | ms     | Cumulative pro-<br>gram time for single<br>row cannot exceed<br>limit before next<br>erase. This parame-<br>ter is only an issue<br>when bypassing the<br>Flash Controller. |

| Data Retention                                   |     |                                                                |     | 10     | _                     | _   | years  | 25°C                                                                                                                                                                        |

| Endurance                                        |     |                                                                |     | 10,000 | -                     | -   | cycles | Program/erase<br>cycles                                                                                                                                                     |

#### Table 119. Flash Memory Electrical Characteristics and Timing

#### Table 120. Watchdog Timer Electrical Characteristics and Timing

|                  |                             | $V_{DD} = 2.7 \text{ to } 3.6 \text{ V}$<br>$V_{DD} = 2.7 \text{ to } 3.6 \text{ V}$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$<br>$V_{DD} = 2.7 - 3.6 \text{ V}$<br>$T_A = -40^{\circ}\text{C to}$<br>$+105^{\circ}\text{C}$ |     |     |     |             |     |       |            |

|------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------|-----|-------|------------|

| Symbol           | Parameter                   | Min                                                                                                                                                                                                                                     | Тур | Max | Min | Min Typ Max |     | Units | Conditions |

|                  | Active power consumption    |                                                                                                                                                                                                                                         |     |     |     | 2           | 3   | μA    |            |

| F <sub>WDT</sub> | WDT oscillator<br>frequency |                                                                                                                                                                                                                                         |     |     | 2.5 | 5           | 7.5 | kHz   |            |

## Hex Addresses: F87–F8F

This address range is reserved.

# Comparator 0

For more information about the Comparator Register, see the <u>Comparator Control Register Definitions</u> section on page 107.

### Hex Address: F90

| Bit     | 7        | 6      | 5               | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|----------|--------|-----------------|-----|-----|-----|-----|-----|--|--|

| Field   | Reserved | INNSEL | REFLVL Reserved |     |     |     |     |     |  |  |

| RESET   | 0        | 0      | 0               | 1   | 0   | 1   | 0   | 0   |  |  |

| R/W     | R/W      | R/W    | R/W             | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |          | F90H   |                 |     |     |     |     |     |  |  |

#### Table 156. Comparator Control Register (CMP0)

#### Hex Addresses: F91–FBF

This address range is reserved.

# **Interrupt Controller**

For more information about the Interrupt Control registers, see the <u>Interrupt Control Reg-</u> <u>ister Definitions</u> section on page 57.

### Hex Address: FC0

| Bit     | 7        | 6    | 5   | 4        | 3        | 2        | 1        | 0    |  |  |

|---------|----------|------|-----|----------|----------|----------|----------|------|--|--|

| Field   | Reserved | T1I  | TOI | Reserved | Reserved | Reserved | Reserved | ADCI |  |  |

| RESET   | 0        | 0    | 0   | 0        | 0        | 0        | 0        | 0    |  |  |

| R/W     | R/W      | R/W  | R/W | R/W      | R/W      | R/W      | R/W      | R/W  |  |  |

| Address |          | FC0H |     |          |          |          |          |      |  |  |

#### Table 157. Interrupt Request 0 Register (IRQ0)

## Hex Addresses: FC9–FCC

This address range is reserved.

### Hex Address: FCD

#### Table 166. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |      |      |      | FC   | DH   |      |      |      |

#### Hex Address: FCE

#### Table 167. Shared Interrupt Select Register (IRQSS)

| Bit     | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |  |

|---------|----------|-------|----------|-----|-----|-----|-----|-----|--|

| Field   | Reserved | PA6CS | Reserved |     |     |     |     |     |  |

| RESET   | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |  |

| Address |          |       |          | FC  | EH  |     |     |     |  |

## Hex Address: FCF

#### Table 168. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6 | 5        | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|------|---|----------|----|----|---|---|---|--|--|--|

| Field   | IRQE |   | Reserved |    |    |   |   |   |  |  |  |

| RESET   | 0    | 0 | 0        | 0  | 0  | 0 | 0 | 0 |  |  |  |

| R/W     | R/W  | R | R        | R  | R  | R | R | R |  |  |  |

| Address |      |   |          | FC | FH |   |   |   |  |  |  |

# **Trim Bit Control**

For more information about the Trim Bit Control registers, see the <u>Flash Option Bit Con-</u> <u>trol Register Definitions</u> section on page 126.

# Hex Address: FF6

| Bit     | 7   | 6                                      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|----------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | TRMADR - Trim Bit Address (00H to 1FH) |     |     |     |     |     |     |  |  |  |

| RESET   | 0   | 0                                      | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W                                    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     |                                        |     | FF  | 6H  |     |     |     |  |  |  |

#### Table 189. Trim Bit Address Register (TRMADR)

## Hex Address: FF7

#### Table 190. Trim Bit Data Register (TRMDR)

| Bit     | 7   | 6                     | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|-----------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | TRMDR - Trim Bit Data |     |     |     |     |     |     |  |  |  |

| RESET   | 0   | 0                     | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W                   | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     |                       |     | FF  | 7H  |     |     |     |  |  |  |

# **Flash Memory Controller**

For more information about the Flash Control registers, see the <u>Flash Control Register</u> <u>Definitions</u> section on page 118.

## Hex Address: FF8

| Bit     | 7 | 6    | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|---|------|---|----|----|---|---|---|--|--|--|

| Field   |   | FCMD |   |    |    |   |   |   |  |  |  |

| RESET   | 0 | 0    | 0 | 0  | 0  | 0 | 0 | 0 |  |  |  |

| R/W     | W | W    | W | W  | W  | W | W | W |  |  |  |

| Address |   |      |   | FF | 8H |   |   |   |  |  |  |

#### Table 191. Flash Control Register (FCTL)

JP 169 LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167 LDX 168 LEA 168 load 168 logical 169 **MULT 167 NOP 168** OR 169 ORX 169 POP 168 **POPX 168** program control 169 **PUSH 168** PUSHX 168 RCF 167, 168 **RET 169** RL 169 **RLC 169** rotate and shift 169 RR 170 **RRC** 170 **SBC 167** SCF 167. 168 **SRA 170 SRL 170 SRP 168 STOP 168 SUB 167 SUBX 167 SWAP 170** TCM 167 **TCMX 167** TM 167 TMX 167 **TRAP 169** watch-dog timer refresh 168 XOR 169 **XORX 169** instructions, eZ8 classes of 166

interrupt control register 67 interrupt controller 53 architecture 53 interrupt assertion types 56 interrupt vectors and priority 56 operation 55 register definitions 57 software interrupt assertion 57 interrupt edge select register 65 interrupt request 0 register 58 interrupt request 1 register 59 interrupt request 2 register 60 interrupt return 169 interrupt vector listing 53 IR 164 Ir 164 **IRET 169** IRQ0 enable high and low bit registers 60 IRQ1 enable high and low bit registers 62 IRQ2 enable high and low bit registers 63 **IRR 164** Irr 164

# J

JP 169 jump, conditional, relative, and relative conditional 169

## L

LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167, 168 LDX 168 LEA 168 load constant 167 load constant to/from program memory 168 load constant with auto-increment addresses 168 load effective address 168 load external data 168