Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | ·                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0131hj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Signal<br>Mnemonic | I/O | Description                                                                                                                                                                                                                                                                   |

|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators        |     |                                                                                                                                                                                                                                                                               |

| X <sub>IN</sub>    | I   | External crystal input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| X <sub>OUT</sub>   | 0   | External crystal output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input        |     |                                                                                                                                                                                                                                                                               |

| CLK <sub>IN</sub>  | Ι   | Clock input signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |

| LED Drivers        |     |                                                                                                                                                                                                                                                                               |

| LED                | 0   | Direct LED drive capability. All Port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |

| On-Chip Debugger   | •   |                                                                                                                                                                                                                                                                               |

| DBG                | I/O | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |

|                    |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                                                                                                                                                               |

| Reset              |     |                                                                                                                                                                                                                                                                               |

| RESET              | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                            |

| Power Supply       |     |                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub>    | Ι   | Digital power supply.                                                                                                                                                                                                                                                         |

| AV <sub>DD</sub>   | I   | Analog power supply.                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>    | I   | Digital ground.                                                                                                                                                                                                                                                               |

| AV <sub>SS</sub>   | I   | Analog ground.                                                                                                                                                                                                                                                                |

|                    |     | gnals are available only in the 28-pin packages with ADC. They are replaced by PB6 kages without ADC.                                                                                                                                                                         |

### Table 4. Signal Descriptions (Continued)

# **Program Memory**

The eZ8 CPU supports 64KB of program memory address space. The Z8 Encore! F0830 Series devices contain 1KB to 12KB of on-chip Flash memory in the program memory address space, depending on the device. Reading from program memory addresses outside the available Flash memory address range returns FFH. Writing to these unimplemented program memory addresses produces no effect. Table 6 shows a program memory map for the Z8 Encore! F0830 Series products.

|                                             | 0 , 1                      |

|---------------------------------------------|----------------------------|

| Program Memory Address (Hex)                | Function                   |

| Z8F0830 and Z8F0831 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-1FFF                                   | Program Memory             |

| Z8F0430 and Z8F0431 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-0FFF                                   | Program Memory             |

| Z8F0130 and Z8F0131 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-03FF                                   | Program Memory             |

| Z8F0230 and Z8F0231 Products                |                            |

| 0000–0001                                   | Flash Option Bits          |

| 0002–0003                                   | Reset Vector               |

| 0004–003D                                   | Interrupt Vectors*         |

| 003E-07FF                                   | Program Memory             |

| Note: *See <u>Table 34</u> on page 54 for a | list of interrupt vectors. |

| Table 6 | . Z8 | Encore! | F0830 | Series | Program | Memory Ma | ips |

|---------|------|---------|-------|--------|---------|-----------|-----|

|---------|------|---------|-------|--------|---------|-----------|-----|

# Port A–D Control Registers

The Port A–D Control registers, shown in Table 20, set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction.

| Bit     | 7   | 6   | 5   | 4          | 3         | 2   | 1   | 0   |

|---------|-----|-----|-----|------------|-----------|-----|-----|-----|

| Field   |     |     |     | PC         | TL        |     |     |     |

| RESET   |     |     |     | 00         | )H        |     |     |     |

| R/W     | R/W | R/W | R/W | R/W        | R/W       | R/W | R/W | R/W |

| Address |     |     | FI  | D1H, FD5H, | FD9H, FDD | Н   |     |     |

| Table 20 | . Port A–D | Control | Registers | (PxCTL) |

|----------|------------|---------|-----------|---------|

|----------|------------|---------|-----------|---------|

| Bit   | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Port Control</b>                                                                                   |

| PCTL  | The Port Control Register provides access to all subregisters that configure the GPIO port operation. |

## Port A–D Data Direction Subregisters

The Port A–D Data Direction Subregister, shown in Table 21, is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register.

| Bit     | 7         | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | DD7       | DD6          | DD5         | DD4           | DD3          | DD2          | DD1          | DD0      |

| RESET   | 1         | 1            | 1           | 1             | 1            | 1            | 1            | 1        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | If 01H ir | n Port A–D A | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Direction                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction Register setting.</li> <li>0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register The output driver is tristated.</li> </ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                       |

Note: x indicates the specific GPIO port pin number (7–0).

# **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 42 and 43, form a priority-encoded enabling service for interrupts in the Interrupt Request 1 Register. Priority is generated by setting the bits in each register.

| ty Description |

|----------------|

| ed Disabled    |

| 1 Low          |

| 2 Nominal      |

| 3 High         |

| 2              |

Table 41. IRQ1 Enable and Priority Encoding

#### Table 42. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address |        |         |        | FC     | 4H            |        |        |        |

| Bit             | Description                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------|

| [7]<br>PA7ENH   | Port A Bit[7] Interrupt Request Enable High Bit                                                          |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit                                            |

| [5:0]           | Port A Bit[x] Interrupt Request Enable High Bit                                                          |

| PA <i>x</i> ENH | See the interrupt port select register for selection of either Port A or Port D as the interrupt source. |

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7    | 6    | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|------|----------|---|---|---|---|---|--|--|

| Field   | IRQE |      | Reserved |   |   |   |   |   |  |  |

| RESET   | 0    | 0    | 0        | 0 | 0 | 0 | 0 |   |  |  |

| R/W     | R/W  | R    | R        | R | R | R | R | R |  |  |

| Address |      | FCFH |          |   |   |   |   |   |  |  |

|         |      |      |          |   |   |   |   |   |  |  |

# Table 49. Interrupt Control Register (IRQCTL)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by executing an Enable Interrupts (EI) or Interrupt Return (IRET) instruction or by a direct register write of 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset, or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                                                                                                            |

reload. For the timer output to make a state change at a ONE-SHOT time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode

- Set the prescale value

- Set the initial output level (High or Low) if using the timer output Alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

One-Shot Mode Time-Out Period (s) =  $\frac{(\text{Reload Value} - \text{Start Value}) \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and for initiating the count:

1. Write to the Timer Control Register to:

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the timer input signal. No interrupt is generated by the first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on Timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the timer low byte register are placed in a holding register. A subsequent read from the timer low byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value when enabled. When the timers are not enabled, a read from the timer low byte register returns the actual value in the counter.

# **Timer Pin Signal Operation**

Timer output is a GPIO port pin alternate function. The timer output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO alternate function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT Mode. For this mode, no timer input is available.

# **ADC Control Register 0**

The ADC Control 0 Register, shown in Table 63, initiates an A/D conversion and provides ADC status information.

| Bit            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                               | 5             | 4          | 3        | 2   | 1                              | 0   |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|----------|-----|--------------------------------|-----|--|--|--|

| Field          | START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reserved                                                                                                                                                                                                                                                        | REFEN         | ADCEN      | Reserved |     | ANAIN[2:0]                     |     |  |  |  |

| RESET          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                               | 0             | 0          | 0        | 0   | 0                              | 0   |  |  |  |

| R/W            | R/W1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                                                                                                                                                                                                                                                             | R/W           | R/W        | R/W      | R/W | R/W                            | R/W |  |  |  |

| Address        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F70h                                                                                                                                                                                                                                                            |               |            |          |     |                                |     |  |  |  |

| Bit            | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                     |               |            |          |     |                                |     |  |  |  |

| [7]<br>START   | 0 = Writing sion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>ADC Start/Busy</li> <li>0 = Writing to 0 has no effect; reading a 0 indicates that the ADC is available to begin a conversion.</li> <li>1 = Writing to 1 starts a conversion; reading a 1 indicates that a conversion is currently in prog-</li> </ul> |               |            |          |     |                                |     |  |  |  |

| [6]            | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Reserved<br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                   |               |            |          |     |                                |     |  |  |  |

| [5]<br>REFEN   | the ADO<br>1 = Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | reference v<br>C.                                                                                                                                                                                                                                               | oltage for th |            | •        |     | e voltage to l<br>rence voltag | -   |  |  |  |

| [4]<br>ADCEN   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>le</b><br>disabled for<br>enabled for                                                                                                                                                                                                                        |               |            |          |     |                                |     |  |  |  |

| [3]            | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | eserved and                                                                                                                                                                                                                                                     | must be pro   | ogrammed t | o 0.     |     |                                |     |  |  |  |

| [2:0]<br>ANAIN | This bit is reserved and must be programmed to 0.<br><b>Analog Input Select</b><br>000 = ANA0 input is selected for analog to digital conversion.<br>001 = ANA1 input is selected for analog to digital conversion.<br>010 = ANA2 input is selected for analog to digital conversion.<br>011 = ANA3 input is selected for analog to digital conversion.<br>100 = ANA4 input is selected for analog to digital conversion.<br>101 = ANA5 input is selected for analog to digital conversion.<br>101 = ANA6 input is selected for analog to digital conversion.<br>110 = ANA6 input is selected for analog to digital conversion.<br>111 = ANA7 input is selected for analog to digital conversion. |                                                                                                                                                                                                                                                                 |               |            |          |     |                                |     |  |  |  |

### Table 63. ADC Control Register 0 (ADCCTL0)

# Comparator

The Z8 Encore! F0830 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or from an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The comparator includes the following features:

- Positive input is connected to a GPIO pin

- Negative input can be connected to either a GPIO pin or a programmable internal reference

- Output can be either an interrupt source or an output to an external pin

# Operation

One of the comparator inputs can be connected to an internal reference that is a user-selectable reference and is user-programmable with 200 mV resolution.

The comparator can be powered down to save supply current. For details, see the <u>Power</u> <u>Control Register 0</u> section on page 31.

**Caution:** As a result of the propagation delay of the comparator, Zilog does not recommend enabling the comparator without first disabling interrupts and waiting for the comparator output to settle. This delay prevents spurious interrupts after comparator enabling.

The following example shows how to safely enable the comparator:

```

di

ld cmp0,r0; load some new configuration

nop

nop ; wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

Figure 18. 12K Flash without NVDS

# **Data Memory Address Space**

The Flash information area, including Zilog Flash option bits, are located in the data memory address space. The Z8 Encore! MCU is configured by these proprietary Flash option bits to prevent the user from writing to the eZ8 CPU data memory address space.

# **Flash Information Area**

The Flash information area is physically separate from program memory and is mapped to the address range FE00H to FE7FH. Not all of these addresses are user-accessible. Factory trim values for the VBO, Internal Precision Oscillator and factory calibration data for the ADC are stored here.

Table 70 describes the Flash information area. This 128-byte information area is accessed by setting the bit 7 of the Flash Page Select Register to 1. When access is enabled, the

| FHSWP  | FWP | Flash Code Protection Description                                                                                                                                                                  |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | Programming and erasing disabled for all Flash program memory. In user code pro-<br>gramming, page erase and mass erase are all disabled. Mass erase is available<br>through the On-Chip Debugger. |

| 0 or 1 | 1   | Programming, page erase and mass erase are enabled for all of the Flash program memory.                                                                                                            |

#### Table 71. Flash Code Protection using the Flash Option Bits

At reset, the Flash Controller is locked to prevent accidental program or erasure of Flash memory. To program or erase Flash memory, first write the target page to the page select register. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The page select register must be rewritten with the same page previously stored there. If the two page select writes do not match, the controller reverts to a Locked state. If the two writes match, the selected page becomes active. See Figure 19 for details.

After unlocking a specific page, you can enable either page program or erase. Writing the value 95H causes a page erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass erase is not allowed in the user code, but is allowed through the debug port.

After unlocking a specific page, the user can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register causes the active page to revert to a Locked state.

#### **Sector Based Flash Protection**

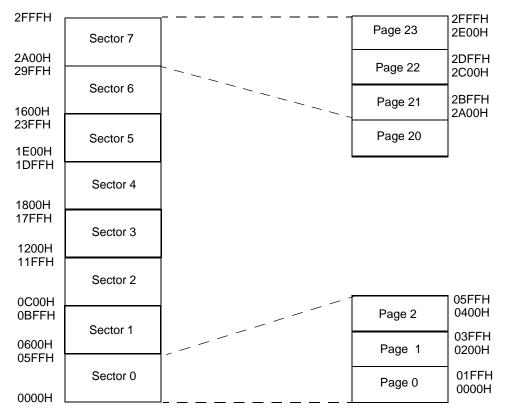

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! devices are divided into maximum number of eight sectors. A sector is oneeighth of the total size of Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal. On Z8 Encore! F0830 Series devices, the sector size is varied according to the Z8 Encore! F0830 Series Flash Memory Configuration shown in Table 69 on page 108 and in Figures 14 through 18, which follow the table

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset and any previously written protection values is lost. User code must write this register in their initialization routine if they want to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

### **Page Erase**

Flash memory can be erased one page (512 bytes) at a time. Page erasing Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the page erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the page erase is complete, the Flash Controller returns to its Locked state.

### **Mass Erase**

Flash memory can also be mass erased using the Flash Controller, but only by using the On-Chip Debugger. Mass erasing Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the mass erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the mass erase is complete, the Flash Controller returns to its Locked state.

## **Flash Controller Bypass**

The Flash Controller can be bypassed; instead, the control signals for Flash memory can be brought out to the GPIO pins. Bypassing the Flash Controller allows faster row programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of Flash memory. Mass Erase and Page Erase operations are also supported, when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to *Third-Party Flash Programming Support for Z8 Encore!*. This document is available for download at <u>www.zilog.com</u>.

# Flash Controller Behavior in Debug Mode

The following behavioral changes can be observed in the Flash Controller when the Flash Controller is accessed using the On-Chip Debugger:

• The Flash write protect option bit is ignored.

# Flash Option Bits

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! F0830 Series operation. The feature configuration data is stored in the Flash program memory and read during reset. The features available for control through the Flash option bits are:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer enabled at reset

- The ability to prevent unwanted read access to user code in program memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in program memory

- Voltage Brown-Out configuration always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- OSCILLATOR Mode selection for high, medium and low power crystal oscillators or external RC oscillator

- Factory trimming information for the Internal Precision Oscillator and VBO voltage

# Operation

This section describes the type and configuration of the programmable Flash option bits.

## **Option Bit Configuration by Reset**

Each time the Flash option bits are programmed or erased, the device must be reset for the change to be effective. During any Reset operation (system reset or Stop Mode Recovery), the Flash option bits are automatically read from Flash program memory and written to the Option Configuration registers, which control Z8 Encore! F0830 Series device operation. Option bit control is established before the device exits reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the register file and are not accessible for read or write access.

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a system reset

# OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 start bit, 8 data bits (least-significant bit first) and 1 stop bit. See Figure 23.

| <br>START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-----------|----|----|----|----|----|----|----|----|------|

| OTAR      | 00 | ы  | 02 | 05 | D4 | 00 | DU | ы  | 0101 |

### Figure 23. OCD Data Format

# **OCD Autobaud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an autobaud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits low (one Start bit plus 7 data bits), framed between high bits. The autobaud detector measures this period and sets the OCD baud rate generator accordingly.

The autobaud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 94 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency<br>(MHz) | Recommended<br>Maximum Baud Rate<br>(kbps) | Recommended<br>Standard PC Baud Rate<br>(bps) | Minimum Baud Rate<br>(kbps) |

|------------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                               | 2500.0                                     | 1,843,200                                     | 39                          |

| 1.0                                | 125.0                                      | 115,200                                       | 1.95                        |

| 0.032768 (32 KHz)                  | 4.096                                      | 2400                                          | 0.064                       |

| Table 9 | 94. OCD | Baud-Rate | Limits |

|---------|---------|-----------|--------|

|         |         |           |        |

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! F0830 Series device ceases functioning and can only be recovered by power-on-reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

Figure 24 displays the oscillator control clock switching flow. See <u>Table 117</u> on page 189 to review the waiting times of various oscillator circuits.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2           | 1 | 0 |  |  |

|---------|-------|-------|-------|-------|-------|-------------|---|---|--|--|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN | SCKSEL      |   |   |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0           | 0 |   |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W R/W R/W |   |   |  |  |

| Address | F86H  |       |       |       |       |             |   |   |  |  |

| Table 99 | . Oscillator | <b>Control Register</b> | (OSCCTL) |

|----------|--------------|-------------------------|----------|

|----------|--------------|-------------------------|----------|

| Bit   | Description                                                       |

|-------|-------------------------------------------------------------------|

| [7]   | Internal Precision Oscillator Enable                              |

| INTEN | 1 = Internal Precision Oscillator is enabled.                     |

|       | 0 = Internal Precision Oscillator is disabled.                    |

| [6]   | Crystal Oscillator Enable                                         |

| XTLEN | This setting overrides the GPIO register control for PA0 and PA1. |

|       | 1 = Crystal oscillator is enabled.                                |

|       | 0 = Crystal oscillator is disabled.                               |

| [5]   | Watchdog Timer Oscillator Enable                                  |

| WDTEN | 1 = Watchdog Timer Oscillator is enabled.                         |

|       | 0 = Watchdog Timer Oscillator is disabled.                        |

| Assembly     |                                                                                                                   |     | ress<br>ode | Op<br>Code(s) | Flags |   |   |   | _ Fetch | Instr. |   |   |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|-------------|---------------|-------|---|---|---|---------|--------|---|---|

| Mnemonic     | Symbolic Operation                                                                                                | dst | src         | (Hex)         | С     | Ζ | S | ۷ | D       | Н      |   |   |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                             | r   |             | 0A–FA         | _     | - | _ | _ | _       | _      | 2 | 3 |

| EI           | IRQCTL[7] ← 1                                                                                                     |     |             | 9F            | _     | _ | _ | _ | -       | _      | 1 | 2 |

| HALT         | HALT Mode                                                                                                         |     |             | 7F            | -     | - | _ | _ | -       | _      | 1 | 2 |

| INC dst      | dst ← dst + 1                                                                                                     | R   |             | 20            | _     | * | * | _ | _       | _      | 2 | 2 |

|              |                                                                                                                   | IR  |             | 21            | _     |   |   |   |         |        | 2 | 3 |

|              |                                                                                                                   | r   |             | 0E-FE         |       |   |   |   |         |        | 1 | 2 |

| INCW dst     | dst ← dst + 1                                                                                                     | RR  |             | A0            | _     | * | * | * | -       | _      | 2 | 5 |

|              |                                                                                                                   | IRR |             | A1            |       |   |   |   |         |        | 2 | 6 |

| IRET         | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |     |             | BF            | *     | * | * | * | *       | *      | 1 | 5 |

| JP dst       | $PC \gets dst$                                                                                                    | DA  |             | 8D            | _     | _ | _ | _ | -       | _      | 3 | 2 |

|              |                                                                                                                   | IRR |             | C4            | _     |   |   |   |         |        | 2 | 3 |

| JP cc, dst   | if cc is true<br>PC ← dst                                                                                         | DA  |             | 0D-FD         | -     | - | - | - | _       | -      | 3 | 2 |

| JR dst       | $PC \gets PC + X$                                                                                                 | DA  |             | 8B            | _     | _ | _ | _ | _       | _      | 2 | 2 |

| JR cc, dst   | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA  |             | 0B–FB         | _     | - | _ | _ | _       | _      | 2 | 2 |

### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

|                                                  | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     |        | = 2.7 to<br>40°C to - |     |        |                                                                                                                                                                             |

|--------------------------------------------------|----------------------------------------------------------------|-----|-----|--------|-----------------------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                        | Min                                                            | Тур | Max | Min    | Тур                   | Max | Units  | Notes                                                                                                                                                                       |

| Flash Byte Read<br>Time                          |                                                                |     |     | 50     | -                     | _   | ns     |                                                                                                                                                                             |

| Flash Byte Program<br>Time                       |                                                                |     |     | 20     | _                     | _   | μs     |                                                                                                                                                                             |

| Flash Page Erase<br>Time                         |                                                                |     |     | 50     | -                     | _   | ms     |                                                                                                                                                                             |

| Flash Mass Erase<br>Time                         |                                                                |     |     | 50     | -                     | _   | ms     |                                                                                                                                                                             |

| Writes to Single<br>Address Before Next<br>Erase |                                                                |     |     | _      | -                     | 2   |        |                                                                                                                                                                             |

| Flash Row Program<br>Time                        |                                                                |     |     | _      | -                     | 8   | ms     | Cumulative pro-<br>gram time for single<br>row cannot exceed<br>limit before next<br>erase. This parame-<br>ter is only an issue<br>when bypassing the<br>Flash Controller. |

| Data Retention                                   |                                                                |     |     | 10     | _                     | _   | years  | 25°C                                                                                                                                                                        |

| Endurance                                        |                                                                |     |     | 10,000 | -                     | -   | cycles | Program/erase<br>cycles                                                                                                                                                     |

#### Table 119. Flash Memory Electrical Characteristics and Timing

#### Table 120. Watchdog Timer Electrical Characteristics and Timing

|                  |                             | $V_{DD} = 2.7 + 3.6V$<br>$V_{DD} = 2.7 \text{ to } 3.6V$<br>$T_{A} = -40^{\circ}\text{C to}$<br>$T_{A} = -40^{\circ}\text{C to}$<br>$+105^{\circ}\text{C}$ |     |     |     |     |     |       |            |

|------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-------|------------|

| Symbol           | Parameter                   | Min                                                                                                                                                        | Тур | Max | Min | Тур | Max | Units | Conditions |

|                  | Active power consumption    |                                                                                                                                                            |     |     |     | 2   | 3   | μA    |            |

| F <sub>WDT</sub> | WDT oscillator<br>frequency |                                                                                                                                                            |     |     | 2.5 | 5   | 7.5 | kHz   |            |

# **On-Chip Debugger Timing**

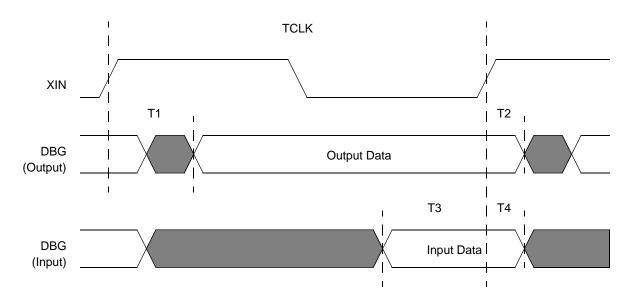

Figure 35 and Table 126 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

| Figure 35. On-Chip Debugger Timing | Figure 35. | <b>On-Chip</b> | Debugger | Timing |

|------------------------------------|------------|----------------|----------|--------|

|------------------------------------|------------|----------------|----------|--------|

|                |                                  | Delay (ns) |         |  |

|----------------|----------------------------------|------------|---------|--|

| Parameter      | Abbreviation                     | Minimum    | Maximum |  |

| DBG            |                                  |            |         |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | _          | 15      |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | _       |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5          | _       |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _       |  |

### Hex Address: F09

#### Table 139. Timer 1 Low Byte Register (T1L)

| Bit     | 7   | 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |  |  |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     |                 |     | Т   | Ľ   |     |     |     |  |  |

| RESET   | 0   | 0 0 0 0 0 0 1   |     |     |     |     |     |     |  |  |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F09H            |     |     |     |     |     |     |  |  |

### Hex Address: F0A

#### Table 140. Timer 1 Reload High Byte Register (T1RH)

| Bit     | 7   | 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |  |  |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | TRH             |     |     |     |     |     |     |  |  |

| RESET   | 1   | 1 1 1 1 1 1 1 1 |     |     |     |     |     |     |  |  |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | FOAH            |     |     |     |     |     |     |  |  |

### Hex Address: F0B

### Table 141. Timer 1 Reload Low Byte Register (T1RL)

| Bit     | 7   | 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |  |  |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     |                 |     | TF  | RL  |     |     |     |  |  |

| RESET   | 1   | 1 1 1 1 1 1 1 1 |     |     |     |     |     |     |  |  |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F0BH            |     |     |     |     |     |     |  |  |

### Hex Address: F0C

#### Table 142. Timer 1 PWM High Byte Register (T1PWMH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     |      |     | PW  | MH  |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | FOCH |     |     |     |     |     |     |  |

### Hex Address: FC1

| Bit     | 7        | 6     | 5     | 4        | 3        | 2        | 1        | 0      |  |

|---------|----------|-------|-------|----------|----------|----------|----------|--------|--|

| Field   | Reserved | T1ENH | T0ENH | Reserved | Reserved | Reserved | Reserved | ADCENH |  |

| RESET   | 0        | 0     | 0     | 0        | 0        | 0        | 0        | 0      |  |

| R/W     | R/W      | R/W   | R/W   | R/W      | R/W      | R/W      | R/W      | R/W    |  |

| Address |          | FC1H  |       |          |          |          |          |        |  |

### Hex Address: FC2

#### Table 159. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 7         6         5         4         3         2         1         0 |              |          |          |          |          |        |  |  |

|---------|----------|-------------------------------------------------------------------------|--------------|----------|----------|----------|----------|--------|--|--|

| Field   | Reserved | T1ENL                                                                   | <b>T0ENL</b> | Reserved | Reserved | Reserved | Reserved | ADCENL |  |  |

| RESET   | 0        | 0                                                                       | 0            | 0        | 0        | 0        | 0        | 0      |  |  |

| R/W     | R        | R/W                                                                     | R/W          | R/W      | R/W      | R        | R        | R/W    |  |  |

| Address |          | FC2H                                                                    |              |          |          |          |          |        |  |  |

### Hex Address: FC3

### Table 160. Interrupt Request 1 Register (IRQ1)

| Bit     | 7    | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|------|-------|------|------|------|------|------|------|--|

| Field   | PA7I | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |

| RESET   | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |

| R/W     | R/W  | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |

| Address |      | FC3H  |      |      |      |      |      |      |  |

### Hex Address: FC4

#### Table 161. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address | FC4H   |         |        |        |               |        |        |        |