Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | ·                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0131ph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| Electrical Characteristics 1                              | 184 |

|-----------------------------------------------------------|-----|

| Absolute Maximum Ratings 1                                | 184 |

| DC Characteristics 1                                      | 185 |

| AC Characteristics 1                                      | 189 |

| On-Chip Peripheral AC and DC Electrical Characteristics 1 | 190 |

| General Purpose I/O Port Input Data Sample Timing 1       | 195 |

| General Purpose I/O Port Output Timing 1                  | 196 |

| On-Chip Debugger Timing 1                                 | 197 |

| Packaging 1                                               | 199 |

| Ordering Information                                      | 200 |

| Part Number Suffix Designations 2                         | 205 |

| Appendix A. Register Tables                               | 208 |

| General Purpose RAM                                       | 208 |

| Timer 0                                                   | 208 |

| Analog-to-Digital Converter                               | 213 |

| Low Power Control                                         | 216 |

| LED Controller                                            | 216 |

| Oscillator Control                                        | 217 |

| Comparator 0                                              | 218 |

| Interrupt Controller                                      | 218 |

| GPIO Port A 2                                             | 222 |

| Watchdog Timer                                            | 226 |

| Trim Bit Control                                          | 228 |

| Flash Memory Controller    2                              | 228 |

| Index                                                     | 231 |

| Customer Support                                          | 239 |

|                                                           |     |

### ix

| Signal<br>Mnemonic | I/O                                                                                                  | Description                                                                                                                                                                                                                                                                   |

|--------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators        |                                                                                                      |                                                                                                                                                                                                                                                                               |

| X <sub>IN</sub>    | I                                                                                                    | External crystal input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| X <sub>OUT</sub>   | 0                                                                                                    | External crystal output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input        |                                                                                                      |                                                                                                                                                                                                                                                                               |

| CLK <sub>IN</sub>  | Clock input signal. This pin may be used to input a TTL-level signal to be used as the system clock. |                                                                                                                                                                                                                                                                               |

| LED Drivers        |                                                                                                      |                                                                                                                                                                                                                                                                               |

| LED                | 0                                                                                                    | Direct LED drive capability. All Port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |

| On-Chip Debugger   | •                                                                                                    |                                                                                                                                                                                                                                                                               |

| DBG                | I/O                                                                                                  | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |

|                    |                                                                                                      | <b>Caution:</b> The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                                                                                                                                                               |

| Reset              |                                                                                                      |                                                                                                                                                                                                                                                                               |

| RESET              | I/O                                                                                                  | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                            |

| Power Supply       |                                                                                                      |                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub>    | Ι                                                                                                    | Digital power supply.                                                                                                                                                                                                                                                         |

| AV <sub>DD</sub>   | I                                                                                                    | Analog power supply.                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>    | I                                                                                                    | Digital ground.                                                                                                                                                                                                                                                               |

| AV <sub>SS</sub>   | I                                                                                                    | Analog ground.                                                                                                                                                                                                                                                                |

|                    |                                                                                                      | gnals are available only in the 28-pin packages with ADC. They are replaced by PB6 kages without ADC.                                                                                                                                                                         |

### Table 4. Signal Descriptions (Continued)

### 17

# **Register Map**

Table 8 provides an address map of the Z8 Encore! F0830 Series register file. Not all devices and package styles in the Z8 Encore! F0830 Series support the ADC or all of the GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)    | Register Description              | Mnemonic      | Reset (Hex) | Page No. |

|------------------|-----------------------------------|---------------|-------------|----------|

| General Purpos   | e RAM                             |               |             |          |

| 000–0FF          | General purpose register file RAM |               | XX          |          |

| 100–EFF          | Reserved                          | _             | XX          |          |

| Timer 0          |                                   |               |             |          |

| F00              | Timer 0 high byte                 | T0H           | 00          | 83       |

| F01              | Timer 0 low byte                  | TOL           | 01          | 83       |

| F02              | Timer 0 reload high byte          | TORH          | FF          | 85       |

| F03              | Timer 0 reload low byte           | TORL          | FF          | 85       |

| F04              | Timer 0 PWM high byte             | <b>T0PWMH</b> | 00          | 86       |

| F05              | Timer 0 PWM low byte              | TOPWML        | 00          | 86       |

| F06              | Timer 0 control 0                 | T0CTL0        | 00          | 87       |

| F07              | Timer 0 control 1                 | T0CTL1        | 00          | 88       |

| Timer 1          |                                   |               |             |          |

| F08              | Timer 1 high byte                 | T1H           | 00          | 83       |

| F09              | Timer 1 low byte                  | T1L           | 01          | 83       |

| F0A              | Timer 1 reload high byte          | T1RH          | FF          | 85       |

| F0B              | Timer 1 reload low byte           | T1RL          | FF          | 85       |

| F0C              | Timer 1 PWM high byte             | T1PWMH        | 00          | 86       |

| F0D              | Timer 1 PWM low byte              | T1PWML        | 00          | 86       |

| F0E              | Timer 1 control 0                 | T1CTL0        | 00          | 87       |

| F0F              | Timer 1 control 1                 | T1CTL1        | 00          | 83       |

| F10–F6F          | Reserved                          | _             | XX          |          |

| Analog-to-Digita | al Converter (ADC)                |               |             |          |

| F70              | ADC control 0                     | ADCCTL0       | 00          | 102      |

| F71              | Reserved                          |               | XX          |          |

| F72              | ADC data high byte                | ADCD_H        | XX          | 103      |

#### Table 8. Register File Address Map

Note: XX = Undefined.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# Reset and Stop Mode Recovery

The reset controller in the Z8 Encore! F0830 Series controls RESET and Stop Mode Recovery operations. In a typical operation, the following events can cause a reset:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash option bit to initiate a reset)

- External RESET pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-Chip Debugger initiated reset (OCDCTL[0] set to 1)

When the device is in STOP Mode, a Stop Mode Recovery event is initiated by either of the following occurrences:

- A Watchdog Timer time-out

- A GPIO port input pin transition on an enabled Stop Mode Recovery source

The VBO circuitry on the device generates a VBO reset when the supply voltage drops below a minimum safe level.

# **Reset Types**

The Z8 Encore! F0830 Series provides different types of Reset operations. Stop Mode Recovery is considered a form of reset. Table 9 lists the types of resets and their operating characteristics. The duration of a system reset is longer if the external crystal oscillator is enabled by the Flash option bits; the result is additional time for oscillator startup.

reload. For the timer output to make a state change at a ONE-SHOT time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode

- Set the prescale value

- Set the initial output level (High or Low) if using the timer output Alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

One-Shot Mode Time-Out Period (s) =  $\frac{(\text{Reload Value} - \text{Start Value}) \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and for initiating the count:

1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the timer output Alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the timer output function) for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

Continuous Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

## **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin: timer input alternate function. The TPOL bit in the Timer Control Register determines whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function

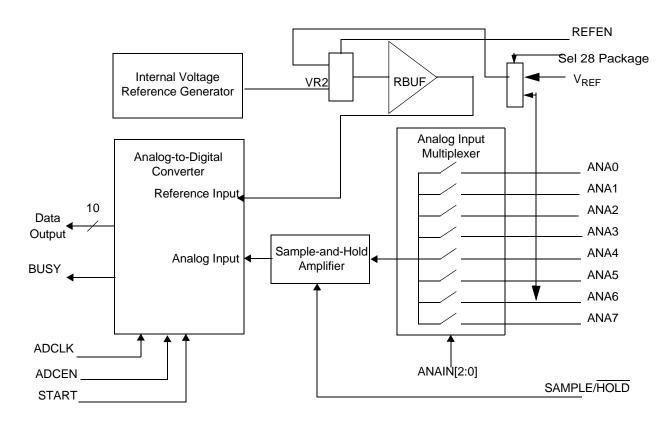

Figure 11. Analog-to-Digital Converter Block Diagram

# Operation

The ADC converts the analog input,  $ANA_X$ , to a 10-bit digital representation. The equation for calculating the digital value is represented by:

ADCOutput =  $1024 \times (ANA_x \div V_{REF})$

Assuming zero gain and offset errors, any voltage outside the ADC input limits of  $AV_{SS}$  and  $V_{REF}$  returns all 0s or 1s, respectively. A new conversion can be initiated by a software to the ADC Control Register's start bit.

Initiating a new conversion, stops any conversion currently in progress and begins a new conversion. To avoid disrupting a conversion already in progress, the START bit can be read to determine ADC operation status (busy or available).

# Sample Settling Time Register

The <u>Sample Settling</u> Time Register, shown in Table 66, is used to program a delay after the <u>SAMPLE/HOLD</u> signal is asserted and before the START signal is asserted; an ADC conversion then begins. The number of clock cycles required for settling will vary from system to system depending on the system clock period used. The system designer should program this register to contain the number of clocks required to meet a  $0.5 \mu s$  minimum settling time.

| Bit     | 7    | 6    | 5     | 4 | 3   | 2  | 1 | 0 |  |

|---------|------|------|-------|---|-----|----|---|---|--|

| Field   |      | Rese | erved |   | SST |    |   |   |  |

| RESET   |      | (    | )     |   | 1   | 1  | 1 | 1 |  |

| R/W     |      | F    | २     |   |     | R/ | W |   |  |

| Address | F74H |      |       |   |     |    |   |   |  |

### Table 66. Sample Settling Time (ADCSST)

| Bit          | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                  |

| [3:0]<br>SST | 0h–Fh = Sample settling time in number of system clock periods to meet 0.5 $\mu$ s minimum. |

# Flash Page Select Register

The Flash Page Select Register shares address space with the Flash Sector Protect Register. Unless the Flash Controller is locked and written with 5EH, any writes to this address will target the Flash Page Select Register.

The register selects one of the eight available Flash memory pages to be programmed or erased. Each Flash page contains 512-bytes of Flash memory. During a page erase operation, all Flash memory containing addresses with the most significant 7-bits within FPS[6:0] are chosen for program/erase operations.

| Bit     | 7       | 6    | 5    | 4   | 3   | 2   | 1   | 0   |  |

|---------|---------|------|------|-----|-----|-----|-----|-----|--|

| Field   | INFO_EN |      | PAGE |     |     |     |     |     |  |

| RESET   | 0       | 0    | 0    | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W     | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W |  |

| Address |         | FF9H |      |     |     |     |     |     |  |

### Table 74. Flash Page Select Register (FPS)

### Bit Description

### [7] Information Area Enable

INFO\_EN 0 = Information area is not selected.

1 = Information area is selected. The information area is mapped into the program memory address space at addresses FE00H through FFFFH.

# [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for page erase and page unlocking. Program memory address[15:9] = PAGE[6:0]. For Z8F04xx and Z8F02xx devices, the upper four bits must always be 0. For Z8F01xx devices, the upper five bits must always be 0.

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>XTLDIS | <ul> <li>State of the Crystal Oscillator at Reset</li> <li>This bit enables only the crystal oscillator. Selecting the crystal oscillator as the system clock must be performed manually.</li> <li>0 = The crystal oscillator is enabled during reset, resulting in longer reset timing.</li> <li>1 = The crystal oscillator is disabled during reset, resulting in shorter reset timing.</li> </ul> |

| [3:0]         | <b>Reserved</b> These bits are reserved and must be programmed to 1111.                                                                                                                                                                                                                                                                                                                              |

# **Trim Bit Address Space**

All available trim bit addresses and their functions are listed in Tables 83 through 90.

130

#### Table 83. Trim Bit Address Space

| Address | Function                      |

|---------|-------------------------------|

| 00h     | ADC reference voltage         |

| 01h     | ADC and comparator            |

| 02h     | Internal Precision Oscillator |

| 03h     | Oscillator and VBO            |

| 06h     | ClkFltr                       |

#### Table 84. Trim Option Bits at 0000H (ADCREF)

| Bit       | 7                                               | 6  | 5         | 4        | 3 | 2   | 1 | 0 |

|-----------|-------------------------------------------------|----|-----------|----------|---|-----|---|---|

| Field     |                                                 | Al | DCREF_TRI | Reserved |   |     |   |   |

| RESET     |                                                 |    | U         |          | U |     |   |   |

| R/W       |                                                 |    | R/W       |          |   | R/W |   |   |

| Address   | Information Page Memory 0020H                   |    |           |          |   |     |   |   |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |    |           |          |   |     |   |   |

| Bit                  | Description                                                                          |

|----------------------|--------------------------------------------------------------------------------------|

| [7:3]<br>ADCREF_TRIM | ADC Reference Voltage Trim Byte<br>Contains trimming bits for ADC reference voltage. |

| [2:0]                | <b>Reserved</b><br>These bits are reserved and must be programmed to 111.            |

**Note:** The bit values used in Table 84 are set at the factory; no calibration is required.

| Bit                                             | 7                             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------|-------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field                                           | Reserved                      |     |     |     |     |     |     |     |  |

| RESET                                           | U                             | U   | U   | U   | U   | U   | U   | U   |  |

| R/W                                             | R/W                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address                                         | Information Page Memory 0021H |     |     |     |     |     |     |     |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |     |     |     |     |     |     |  |

| Bit Description                                 |                               |     |     |     |     |     |     |     |  |

#### Table 85. Trim Option Bits at 0001H (TADC\_COMP)

| Bit   | Description                                                      |

|-------|------------------------------------------------------------------|

| [7:0] | Reserved                                                         |

|       | Altering this register may result in incorrect device operation. |

# Operation

The following section describes the operation of the On-Chip Debugging function.

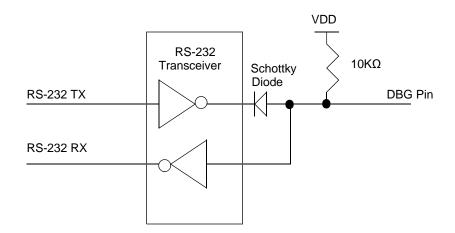

# **OCD** Interface

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, which means that transmission and data retrieval cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface between the Z8 Encore! F0830 Series products and the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figures 21 and 22. The recommended method is the buffered implementation depicted in Figure 22. The DBG pin must always be connected to  $V_{DD}$  through an external pull-up resistor.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

#### Figure 21. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

If the OCD receives a serial break (nine or more continuous bits low), the autobaud detector/generator resets. Reconfigure the autobaud detector/generator by sending 80H.

## **OCD Serial Errors**

The OCD can detect any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received Stop bit is Low)

- Transmit collision (simultaneous transmission by OCD and host detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long serial break back to the host and resets the autobaud detector/generator. A framing error or transmit collision may be caused by the host sending a serial break to the OCD. As a result of the open-drain nature of the interface, returning a serial break back to the host only extends the length of the serial break if the host releases the serial break early.

The host transmits a serial break on the DBG pin when first connecting to the Z8 Encore! F0830 Series devices or when recovering from an error. A serial break from the host resets the autobaud generator/detector, but does not reset the OCD Control Register. A serial break leaves the device in DEBUG Mode, if that is the current mode. The OCD is held in reset until the end of the serial break when the DBG pin returns high. Because of the opendrain nature of the DBG pin, the host can send a serial break to the OCD even if the OCD is transmitting a character.

## **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

188

Figure 32 displays the typical current consumption versus the system clock frequency in NORMAL Mode.

Figure 32.  $I_{CC}$  Versus System Clock Frequency (NORMAL Mode)

### Hex Address: F01

#### Table 131. Timer 0 Low Byte Register (T0L)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     |      |     | Т   | L   |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 1   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F01H |     |     |     |     |     |     |  |

### Hex Address: F02

#### Table 132. Timer 0 Reload High Byte Register (T0RH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     |      |     | TF  | RH  |     |     |     |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F02H |     |     |     |     |     |     |  |

### Hex Address: F03

#### Table 133. Timer 0 Reload Low Byte Register (T0RL)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     |      |     | TF  | RL  |     |     |     |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F03H |     |     |     |     |     |     |  |

#### Hex Address: F04

#### Table 134. Timer 0 PWM High Byte Register (T0PWMH)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | PW  | MH  |     |     |     |

| RESET   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F0  | 4H  |     |     |     |

### Hex Address: F83

#### Table 153. LED Drive Level High Register (LEDLVLH)

| Bit     | 7   | 6    | 5   | 4     | 3       | 2   | 1   | 0   |  |

|---------|-----|------|-----|-------|---------|-----|-----|-----|--|

| Field   |     |      |     | LEDLV | LH[7:0] |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0     | 0       | 0   | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W   | R/W     | R/W | R/W | R/W |  |

| Address |     | F83H |     |       |         |     |     |     |  |

### Hex Address: F84

#### Table 154. LED Drive Level Low Register (LEDLVLL)

| Bit     | 7   | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|---------|-----|-----|-----|

| Field   |     |     |     | LEDLV | LL[7:0] |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Address |     |     |     | F8    | 4H      |     |     |     |

### Hex Address: F85

This address range is reserved.

# **Oscillator Control**

For more information about the Oscillator Control registers, see the <u>Oscillator Control</u> <u>Register Definitions</u> section on page 154.

#### Hex Address: F86

| Table 155. | Oscillator | Control | Register | (OSCCTL) |

|------------|------------|---------|----------|----------|

|------------|------------|---------|----------|----------|

| Bit     | 7     | 6     | 5     | 4     | 3     | 2   | 1      | 0   |  |

|---------|-------|-------|-------|-------|-------|-----|--------|-----|--|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN |     | SCKSEL |     |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0   | 0      | 0   |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W | R/W    | R/W |  |

| Address |       | F86H  |       |       |       |     |        |     |  |

# **Trim Bit Control**

For more information about the Trim Bit Control registers, see the <u>Flash Option Bit Con-</u> <u>trol Register Definitions</u> section on page 126.

## Hex Address: FF6

| Bit     | 7   | 6   | 5      | 4              | 3           | 2         | 1   | 0   |

|---------|-----|-----|--------|----------------|-------------|-----------|-----|-----|

| Field   |     |     | TRMADF | R - Trim Bit A | ddress (00ł | H to 1FH) |     |     |

| RESET   | 0   | 0   | 0      | 0              | 0           | 0         | 0   | 0   |

| R/W     | R/W | R/W | R/W    | R/W            | R/W         | R/W       | R/W | R/W |

| Address |     |     |        | FF             | 6H          |           |     |     |

#### Table 189. Trim Bit Address Register (TRMADR)

### Hex Address: FF7

#### Table 190. Trim Bit Data Register (TRMDR)

| Bit     | 7   | 6    | 5   | 4         | 3            | 2   | 1   | 0   |

|---------|-----|------|-----|-----------|--------------|-----|-----|-----|

| Field   |     |      |     | TRMDR - T | rim Bit Data |     |     |     |

| RESET   | 0   | 0    | 0   | 0         | 0            | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W       | R/W          | R/W | R/W | R/W |

| Address |     | FF7H |     |           |              |     |     |     |

# **Flash Memory Controller**

For more information about the Flash Control registers, see the <u>Flash Control Register</u> <u>Definitions</u> section on page 118.

### Hex Address: FF8

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|---|---|----|----|---|---|---|

| Field   |   |   |   | FC | MD |   |   |   |

| RESET   | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W     | W | W | W | W  | W  | W | W | W |

| Address |   |   |   | FF | 8H |   |   |   |

### Table 191. Flash Control Register (FCTL)

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

232

compare - extended addressing 166 compare mode 89 compare with carry 166 compare with carry - extended addressing 166 complement 169 complement carry flag 167, 168 condition code 164 continuous mode 89 Control Registers 14, 17 counter modes 89 CP 166 CPC 166 **CPCX 166** CPU and peripheral overview 4 CPU control instructions 168 CPX 166 current measurement architecture 98 operation 99 Customer Feedback Form 239 Customer Information 239

# D

DA 164, 166 data memory 16 DC characteristics 185 debugger, on-chip 139 **DEC 166** decimal adjust 166 decrement 166 decrement and jump non-zero 169 decrement word 166 **DECW 166** destination operand 165 device, port availability 33 DI 168 direct address 164 disable interrupts 168 **DJNZ 169** dst 165

# Ε

EI 168 electrical characteristics 184 GPIO input data sample timing 195 watch-dog timer 194 electrical noise 98 enable interrupt 168 ER 164 extended addressing register 164 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 166 eZ8 CPU instruction notation 164 eZ8 CPU instruction set 162 eZ8 CPU instruction summary 171

# F

FCTL register 119, 126, 127, 228 features, Z8 Encore! 1 first opcode map 182 FLAGS 165 flags register 165 flash controller 4 option bit address space 127 option bit configuration - reset 124 program memory address 0000H 127 program memory address 0001H 128 flash memory 108 byte programming 116 code protection 114 configurations 108 control register definitions 118, 126 controller bypass 117 flash control register 119, 126, 127, 228 flash option bits 115 flash status register 120 flow chart 113 frequency high and low byte registers 123 mass erase 117 operation 112 operation timing 114 page erase 117

watchdog timer reload upper byte (WDTU) 96 register file 14 register pair 165 register pointer 165 registers ADC channel 1 102 ADC data high byte 103 ADC data low bit 103, 104, 105 reset and stop mode characteristics 22 and stop mode recovery 21 carry flag 167 sources 23 **RET 169** return 169 RL 169 **RLC 169** rotate and shift instuctions 169 rotate left 169 rotate left through carry 169 rotate right 170 rotate right through carry 170 RP 165 RR 165, 170 rr 165 **RRC** 170

# S

SBC 167 SCF 167, 168 second opcode map after 1FH 183 set carry flag 167, 168 set register pointer 168 shift right arithmatic 170 shift right logical 170 signal descriptions 11 software trap 169 source operand 165 SP 165 SRA 170 src 165 SRL 170 SRP 168 stack pointer 165 **STOP 168** stop mode 30, 168 stop mode recovery sources 26 using a GPIO port pin transition 27, 28 using watch-dog timer time-out 27 **SUB 167** subtract 167 subtract - extended addressing 167 subtract with carry 167 subtract with carry - extended addressing 167 **SUBX 167 SWAP 170** swap nibbles 170 symbols, additional 165

# Т

Table 134. Power Consumption Reference Table 197 **TCM 167 TCMX 167** test complement under mask 167 test complement under mask - extended addressing 167 test under mask 167 test under mask - extended addressing 167 tiing diagram, voltage measurement 100 timer signals 11 timers 68 architecture 68 block diagram 69 capture mode 77, 78, 89, 90 capture/compare mode 81, 89 compare mode 79, 89 continuous mode 70, 89 counter mode 71.72 counter modes 89 gated mode 80, 89 one-shot mode 69, 89 operating mode 69 PWM mode 74, 75, 89, 90 reading the timer count values 82

# **Customer Support**

To share comments, get your technical questions answered or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://zilog.com/</u><u>kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.