Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | <u>.</u>                                                  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-VQFN                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0131qj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

## LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2012 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES or TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES or TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

# **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit CPU, meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 CPU code

- Expanded internal register file allows access up to 4KB

- New instructions improve execution efficiency for code developed using high-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the register file

- Up to 10 MIPS operation

- C Compiler-friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

## **General Purpose Input/Output**

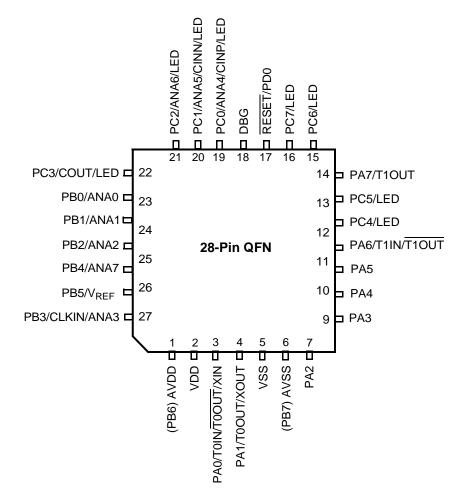

The Z8 Encore! F0830 Series features up to 25 port pins (Ports A–D) for general-purpose input/output (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable.

# **Flash Controller**

The Flash Controller programs and erases the Flash memory. It also supports protection against accidental programming and erasure.

# Nonvolatile Data Storage

The Nonvolatile Data Storage (NVDS) function uses a hybrid hardware/software scheme to implement a byte-programmable data memory and is capable of storing about 100,000 write cycles.

# **Internal Precision Oscillator**

The Internal Precision Oscillator (IPO) function, with an accuracy of  $\pm 4\%$  full voltage/ temperature range, is a trimmable clock source that requires no external components.

# **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies using an external crystal, ceramic resonator or RC network.

# **10-Bit Analog-to-Digital Converter**

The optional Analog-to-Digital Converter (ADC) converts an analog input signal to a 10bit binary number. The ADC accepts inputs from eight different analog input pins.

### Analog Comparator

The analog comparator compares the signal at an input pin with either an internal programmable reference voltage or with a signal at the second input pin. The comparator output is used either to drive a logic output pin or to generate an interrupt.

## Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT Modes.

# **Interrupt Controller**

The Z8 Encore! F0830 Series products support seventeen interrupt sources with sixteen interrupt vectors: up to five internal peripheral interrupts and up to twelve GPIO interrupts. These interrupts have three levels of programmable interrupt priority.

# **Reset Controller**

The Z8 Encore! F0830 Series products are reset using any one of the following: the RESET pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP Mode exit or Voltage Brown-Out (VBO) warning signal. The RESET pin is bidirectional; i.e., it functions as a reset source as well as a reset indicator.

# **On-Chip Debugger**

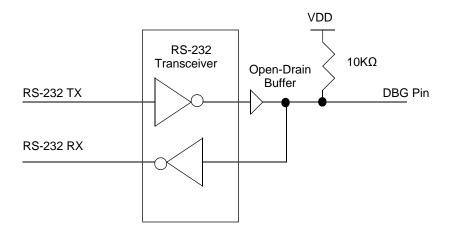

The Z8 Encore! F0830 Series products feature an integrated On-Chip Debugger (OCD). The OCD provides a rich set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. The OCD uses one single-pin interface for communication with an external host.

# **Acronyms and Expansions**

This document references a number of acronyms; each is expanded in Table 2 for the reader's understanding.

| Acronyms | Expansions                       |

|----------|----------------------------------|

| ADC      | Analog-to-Digital Converter      |

| NVDS     | Nonvolatile Data Storage         |

| WDT      | Watchdog Timer                   |

| GPIO     | General-Purpose Input/Output     |

| OCD      | On-Chip Debugger                 |

| POR      | Power-On Reset                   |

| VBO      | Voltage Brown-Out                |

| IPO      | Internal Precision Oscillator    |

| PDIP     | Plastic Dual Inline Package      |

| SOIC     | Small Outline Integrated Circuit |

| SSOP     | Small Shrink Outline Package     |

| QFN      | Quad Flat No Lead                |

| IRQ      | Interrupt request                |

| ISR      | Interrupt service routine        |

| MSB      | Most significant byte            |

| LSB      | Least significant byte           |

| PWM      | Pulse Width Modulation           |

| SAR      | Successive Approximation Regis-  |

|          |                                  |

#### Table 2. Acronyms and Expansions

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

Figure 5. Z8F0830 Series in 28-Pin QFN Package

10

# General Purpose Input/Output

The Z8 Encore! F0830 Series products support a maximum of 25 port pins (Ports A–D) for General Purpose Input/Output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

# **GPIO Port Availability by Device**

Table 15 lists the port pins available with each device and package type.

|                                                   |         | 10-Bit |        |        |        |        |           |

|---------------------------------------------------|---------|--------|--------|--------|--------|--------|-----------|

| Devices                                           | Package | ADC    | Port A | Port B | Port C | Port D | Total I/O |

| Z8F1232, Z8F0830,<br>Z8F0430, Z8F0230,<br>Z8F0130 | 20-pin  | Yes    | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F1233, Z8F0831<br>Z8F0431, Z8F0231<br>Z8F0131   | 20-pin  | No     | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F1232, Z8F0830,<br>Z8F0430, Z8F0230,<br>Z8F0130 | 28-pin  | Yes    | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F1233, Z8F0831<br>Z8F0431, Z8F0231<br>Z8F0131   | 28-pin  | No     | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

#### Table 15. Port Availability by Device and Package Type

# Port A–D Address Registers

The Port A–D Address registers select the GPIO port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO port controls; see Tables 18 and 19.

| <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W | Bit     | 7                           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------------|---------|-----------------------------|---|---|---|---|---|---|---|

| <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W | Field   | PADDR[7:0]                  |   |   |   |   |   |   |   |

|                                        | RESET   | 00H                         |   |   |   |   |   |   |   |

| Address FD0H, FD4H, FD8H, FDCH         | R/W     | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |   |

|                                        | Address | FD0H, FD4H, FD8H, FDCH      |   |   |   |   |   |   |   |

## Table 18. Port A–D GPIO Address Registers (PxADDR)

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The port address selects one of the subregisters accessible through the Port Control Register. |

## Table 19. Port Control Subregister Access

| PADDR[7:0] | Port Control Subregister accessible using the Port A–D Control registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental port reconfiguration. |

| 01H        | Data Direction                                                                 |

| 02H        | Alternate Function                                                             |

| 03H        | Output Control (open-drain)                                                    |

| 04H        | High Drive Enable                                                              |

| 05H        | Stop Mode Recovery Source Enable                                               |

| 06H        | Pull-Up Enable                                                                 |

| 07H        | Alternate Function Set 1                                                       |

| 08H        | Alternate Function Set 2                                                       |

| 09H–FFH    | No function                                                                    |

# Port A–D Output Control Subregisters

The Port A–D Output Control Subregister, shown in Table 23, is accessed through the Port A–D Control Register by writing 03H to the Port A–D Address Register. Setting the bits in the Port A–D Output Control subregisters to 1 configures the specified port pins for opendrain operation. These subregisters affect the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7                                                                                     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Field   | POC7                                                                                  | POC6 | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |

| RESET   | 0                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |      |      |      |      |      |      |      |

#### Table 23. Port A–D Output Control Subregisters (PxOC)

#### Bit Description

[7:0] Port Output Control

POCx These bits function independently of the Alternate function bit and always disable the drains, if set to 1.

0 = The drains are enabled for any OUTPUT Mode (unless overridden by the Alternate function).

1 = The drain of the associated pin is disabled (OPEN-DRAIN mode).

Note: x indicates the specific GPIO port pin number (7–0).

# **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 42 and 43, form a priority-encoded enabling service for interrupts in the Interrupt Request 1 Register. Priority is generated by setting the bits in each register.

| ty Description |

|----------------|

| ed Disabled    |

| 1 Low          |

| 2 Nominal      |

| 3 High         |

| 2              |

Table 41. IRQ1 Enable and Priority Encoding

#### Table 42. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address | FC4H   |         |        |        |               |        |        |        |

| Bit             | Description                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------|

| [7]<br>PA7ENH   | Port A Bit[7] Interrupt Request Enable High Bit                                                          |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit                                            |

| [5:0]           | Port A Bit[x] Interrupt Request Enable High Bit                                                          |

| PA <i>x</i> ENH | See the interrupt port select register for selection of either Port A or Port D as the interrupt source. |

# Sample Time Register

The Sample Time Register, shown in Table 67, is used to program the length of active time for a sample after a conversion has begun by setting the START bit in the ADC Control Register. The number of system clock cycles required for the sample time varies from system to system, depending on the clock period used. The system designer should program this register to contain the number of system clocks required to meet a  $1 \mu s$  minimum sample time.

| Bit     | 7    | 6     | 5   | 4 | 3 | 2 | 1 | 0 |

|---------|------|-------|-----|---|---|---|---|---|

| Field   | Rese | erved |     |   | S | Т |   |   |

| RESET   | (    | )     | 1   | 1 | 1 | 1 | 1 | 1 |

| R/W     | R/   | W     | R/W |   |   |   |   |   |

| Address |      | F75H  |     |   |   |   |   |   |

| Table 67 | Sample Time | e (ADCST) |

|----------|-------------|-----------|

|----------|-------------|-----------|

| Bit         | Description                                                                           |

|-------------|---------------------------------------------------------------------------------------|

| [7:6]       | Reserved<br>These bits are reserved and must be programmed to 00.                     |

| [5:0]<br>ST | 0h–Fh = Sample-hold time in number of system clock periods to meet 1 $\mu$ s minimum. |

# **Comparator Control Register Definitions**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference. The GPIO pin is always used as positive comparator input.

| Bit             | 7                                                                                                                                                                                | 6            | 5            | 4          | 3          | 2   | 1        | 0   |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------------|------------|-----|----------|-----|--|--|--|--|

| Field           | Reserved                                                                                                                                                                         | INNSEL       |              | REF        | LVL        |     | Reserved |     |  |  |  |  |

| RESET           | 0                                                                                                                                                                                | 0            | 0            | 1          | 0          | 1   | 0        | 0   |  |  |  |  |

| R/W             | R/W                                                                                                                                                                              | R/W          | R/W          | R/W        | R/W        | R/W | R/W      | R/W |  |  |  |  |

| Address         | F90H                                                                                                                                                                             |              |              |            |            |     |          |     |  |  |  |  |

| Bit             | Description                                                                                                                                                                      |              |              |            |            |     |          |     |  |  |  |  |

| [7]             | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                             |              |              |            |            |     |          |     |  |  |  |  |

| [6]<br>INNSEL   | Signal Select for Negative Input<br>0 = internal reference disabled, GPIO pin used as negative comparator input.<br>1 = internal reference enabled as negative comparator input. |              |              |            |            |     |          |     |  |  |  |  |

| [5:2]<br>REFLVL |                                                                                                                                                                                  |              |              |            |            |     |          |     |  |  |  |  |

| [1:0]           | Reserved<br>These bits a                                                                                                                                                         | are reserved | l and must b | e programm | ned to 00. |     |          |     |  |  |  |  |

## Table 68. Comparator Control Register (CMP0)

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

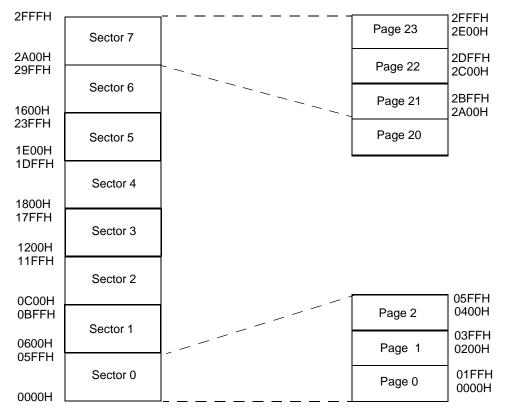

Figure 18. 12K Flash without NVDS

# **Data Memory Address Space**

The Flash information area, including Zilog Flash option bits, are located in the data memory address space. The Z8 Encore! MCU is configured by these proprietary Flash option bits to prevent the user from writing to the eZ8 CPU data memory address space.

# **Flash Information Area**

The Flash information area is physically separate from program memory and is mapped to the address range FE00H to FE7FH. Not all of these addresses are user-accessible. Factory trim values for the VBO, Internal Precision Oscillator and factory calibration data for the ADC are stored here.

Table 70 describes the Flash information area. This 128-byte information area is accessed by setting the bit 7 of the Flash Page Select Register to 1. When access is enabled, the

# Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

# Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

## Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

# Flash Option Bits

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! F0830 Series operation. The feature configuration data is stored in the Flash program memory and read during reset. The features available for control through the Flash option bits are:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer enabled at reset

- The ability to prevent unwanted read access to user code in program memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in program memory

- Voltage Brown-Out configuration always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- OSCILLATOR Mode selection for high, medium and low power crystal oscillators or external RC oscillator

- Factory trimming information for the Internal Precision Oscillator and VBO voltage

# Operation

This section describes the type and configuration of the programmable Flash option bits.

# **Option Bit Configuration by Reset**

Each time the Flash option bits are programmed or erased, the device must be reset for the change to be effective. During any Reset operation (system reset or Stop Mode Recovery), the Flash option bits are automatically read from Flash program memory and written to the Option Configuration registers, which control Z8 Encore! F0830 Series device operation. Option bit control is established before the device exits reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the register file and are not accessible for read or write access.

Figure 22. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

# **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates, unless the device is in STOP Mode

- All enabled on-chip peripherals operate, unless the device is in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

## **Entering DEBUG Mode**

- The device enters DEBUG Mode after the eZ8 CPU executes a Breakpoint (BRK) instruction

- If the DBG pin is held low during the most recent clock cycle of system reset, the device enters DEBUG Mode on exiting system reset

## **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

| Debug Command           | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit |

|-------------------------|-----------------|------------------------------------|----------------------------------------------|

| Read Program Memory CRC | 0EH             | -                                  | -                                            |

| Reserved                | 0FH             | -                                  | -                                            |

| Step Instruction        | 10H             | -                                  | Disabled                                     |

| Stuff Instruction       | 11H             | -                                  | Disabled                                     |

| Execute Instruction     | 12H             | -                                  | Disabled                                     |

| Reserved                | 13H–FFH         | _                                  | _                                            |

#### Table 95. On-Chip Debugger Command Summary (Continued)

In the following bulleted list of OCD commands, data and commands sent from the host to the OCD are identified by DBG  $\leftarrow$  Command/Data. Data sent from the OCD back to the host is identified by DBG Data.

**Read OCD Revision (00H).** The read OCD revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed or changed this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

**Read Runtime Counter (03H).** The runtime counter counts system clock cycles in between breakpoints. The 16-bit runtime counter counts from 0000H and stops at the maximum count of FFFFH. The runtime counter is overwritten during the write memory, read memory, write register, read register, read memory CRC, step instruction, stuff instruction and execute instruction commands.

```

DBG \leftarrow 03H

DBG \rightarrow RuntimeCounter[15:8]

DBG \rightarrow RuntimeCounter[7:0]

```

Write OCD Control Register (04H). The write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash read protect option bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0. To return the device to normal operating mode, the device must be reset.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

| Assembly         |                                                                                           | Address<br>Mode |    | Op<br>Code(s) | Flags  |   |   |   |   |   | Fetch | Instr. |

|------------------|-------------------------------------------------------------------------------------------|-----------------|----|---------------|--------|---|---|---|---|---|-------|--------|

| Mnemonic         | Symbolic Operation                                                                        | dst src (Hex)   |    | С             | CZSVDH |   |   |   | Н |   |       |        |

| AND dst, src     | $dst \gets dst \; AND \; src$                                                             | r               | r  | 52            | _      | * | * | 0 | _ | _ | 2     | 3      |

|                  |                                                                                           | r               | lr | 53            | _      |   |   |   |   |   | 2     | 4      |

|                  |                                                                                           | R               | R  | 54            |        |   |   |   |   |   | 3     | 3      |

|                  |                                                                                           | R               | IR | 55            | _      |   |   |   |   |   | 3     | 4      |

|                  |                                                                                           | R               | IM | 56            | _      |   |   |   |   |   | 3     | 3      |

|                  |                                                                                           | IR              | IM | 57            | _      |   |   |   |   |   | 3     | 4      |

| ANDX dst, src    | $dst \gets dst \; AND \; src$                                                             | ER              | ER | 58            | _      | * | * | 0 | _ | _ | 4     | 3      |

|                  |                                                                                           | ER              | IM | 59            | _      |   |   |   |   |   | 4     | 3      |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |                 |    | 2F            | -      | _ | _ | _ | _ | _ | 1     | 2      |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r               |    | E2            | _      | * | * | 0 | _ | _ | 2     | 2      |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r               |    | E2            | _      | * | * | 0 | _ | _ | 2     | 2      |

| BRK              | Debugger Break                                                                            |                 |    | 00            | -      | _ | - | - | _ | _ | 1     | 1      |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r               |    | E2            | -      | * | * | 0 | - | - | 2     | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R               |    | D5            | Х      | * | * | 0 | - | - | 2     | 2      |

| BTJ p, bit, src, | if src[bit] = p                                                                           |                 | r  | F6            | -      | _ | - | - | _ | _ | 3     | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr | F7            | _      |   |   |   |   |   | 3     | 4      |

| BTJNZ bit, src,  |                                                                                           |                 | r  | F6            | -      | - | - | - | - | - | 3     | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr | F7            | _      |   |   |   |   |   | 3     | 4      |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |                 | r  | F6            | -      | _ | - | - | _ | - | 3     | 3      |

| dst              | $PC \gets PC + X$                                                                         |                 | Ir | F7            |        |   |   |   |   |   | 3     | 4      |

| CALL dst         | $SP \leftarrow SP - 2$                                                                    | IRR             |    | D4            | _      | _ | _ | _ | _ | _ | 2     | 6      |

|                  | @SP ← PC<br>PC ← dst                                                                      | DA              |    | D6            | _      |   |   |   |   |   | 3     | 3      |

| CCF              | $C \leftarrow \sim C$                                                                     |                 |    | EF            | *      | _ | _ | _ | _ |   | 1     | 2      |

# Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Assembly      |                              | Address<br>Mode |     | Op<br>Code(s) | Flags |   |   |   |   |   | _ Fetch | Instr. |

|---------------|------------------------------|-----------------|-----|---------------|-------|---|---|---|---|---|---------|--------|

| Mnemonic      | Symbolic Operation           | dst             | src | (Hex)         | С     | Ζ | S | ۷ | D | Н |         |        |

| CLR dst       | dst ← 00H                    | R               |     | B0            | _     | _ | _ | - | _ | - | 2       | 2      |

|               |                              | IR              |     | B1            | _     |   |   |   |   |   | 2       | 3      |

| COM dst       | dst ← ~dst                   | R               |     | 60            | -     | * | * | 0 | - | - | 2       | 2      |

|               |                              | IR              |     | 61            | _     |   |   |   |   |   | 2       | 3      |

| CP dst, src   | dst - src                    | r               | r   | A2            | *     | * | * | * | - | - | 2       | 3      |

|               |                              | r               | lr  | A3            | _     |   |   |   |   |   | 2       | 4      |

|               |                              | R               | R   | A4            | _     |   |   |   |   |   | 3       | 3      |

|               |                              | R               | IR  | A5            | _     |   |   |   |   |   | 3       | 4      |

|               |                              | R               | IM  | A6            | _     |   |   |   |   |   | 3       | 3      |

|               |                              | IR              | IM  | A7            | _     |   |   |   |   |   | 3       | 4      |

| CPC dst, src  | dst - src - C                | r               | r   | 1F A2         | *     | * | * | * | - | - | 3       | 3      |

|               |                              | r               | lr  | 1F A3         | _     |   |   |   |   |   | 3       | 4      |

|               |                              | R               | R   | 1F A4         | _     |   |   |   |   |   | 4       | 3      |

|               |                              | R               | IR  | 1F A5         | _     |   |   |   |   |   | 4       | 4      |

|               |                              | R               | IM  | 1F A6         | _     |   |   |   |   |   | 4       | 3      |

|               |                              | IR              | IM  | 1F A7         | _     |   |   |   |   |   | 4       | 4      |

| CPCX dst, src | dst - src - C                | ER              | ER  | 1F A8         | *     | * | * | * | _ | _ | 5       | 3      |

|               |                              | ER              | IM  | 1F A9         | _     |   |   |   |   |   | 5       | 3      |

| CPX dst, src  | dst - src                    | ER              | ER  | A8            | *     | * | * | * | - | - | 4       | 3      |

|               |                              | ER              | IM  | A9            | _     |   |   |   |   |   | 4       | 3      |

| DA dst        | dst ← DA(dst)                | R               |     | 40            | *     | * | * | Х | - | - | 2       | 2      |

|               |                              | IR              |     | 41            | _     |   |   |   |   |   | 2       | 3      |

| DEC dst       | $dst \gets dst \text{ - } 1$ | R               |     | 30            | _     | * | * | * | _ | _ | 2       | 2      |

|               |                              | IR              |     | 31            | _     |   |   |   |   |   | 2       | 3      |

| DECW dst      | dst ← dst - 1                | RR              |     | 80            | _     | * | * | * | _ | _ | 2       | 5      |

|               |                              | IRR             |     | 81            | _     |   |   |   |   |   | 2       | 6      |

| DI            | IRQCTL[7] ← 0                |                 |     | 8F            | _     | _ | _ | _ | _ | _ | 1       | 2      |

## Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

|                       |              |       |      | -               | -           |

|-----------------------|--------------|-------|------|-----------------|-------------|

| Part Number           | Flash        | RAM   | NVDS | ADC<br>Channels | Description |

| Extended Temperatur   | re: -40°C to | 105°C |      |                 |             |

| Z8F0230SH020EG        | 2KB          | 256   | Yes  | 7               | SOIC 20-pin |

| Z8F0230HH020EG        | 2KB          | 256   | Yes  | 7               | SSOP 20-pin |

| Z8F0230PH020EG        | 2KB          | 256   | Yes  | 7               | PDIP 20-pin |

| Z8F0230QH020EG        | 2KB          | 256   | Yes  | 7               | QFN 20-pin  |

| Z8F0231SH020EG        | 2KB          | 256   | Yes  | 0               | SOIC 20-pin |

| Z8F0231HH020EG        | 2KB          | 256   | Yes  | 0               | SSOP 20-pin |

| Z8F0231PH020EG        | 2KB          | 256   | Yes  | 0               | PDIP 20-pin |

| Z8F0231QH020EG        | 2KB          | 256   | Yes  | 0               | QFN 20-pin  |

| Z8F0230SJ020EG        | 2KB          | 256   | Yes  | 8               | SOIC 28-pin |

| Z8F0230HJ020EG        | 2KB          | 256   | Yes  | 8               | SSOP 28-pin |

| Z8F0230PJ020EG        | 2KB          | 256   | Yes  | 8               | PDIP 28-pin |

| Z8F0230QJ020EG        | 2KB          | 256   | Yes  | 8               | QFN 28-pin  |

| Z8F0231SJ020EG        | 2KB          | 256   | Yes  | 0               | SOIC 28-pin |

| Z8F0231HJ020EG        | 2KB          | 256   | Yes  | 0               | SSOP 28-pin |

| Z8F0231PJ020EG        | 2KB          | 256   | Yes  | 0               | PDIP 28-pin |

| Z8F0231QJ020EG        | 2KB          | 256   | Yes  | 0               | QFN 28-pin  |

| Z8 Encore! F0830 with | h 1KB Flash  | l     |      |                 |             |

| Standard Temperatur   | e: 0°C to 70 | °C    |      |                 |             |

| Z8F0130SH020SG        | 1KB          | 256   | Yes  | 7               | SOIC 20-pin |

| Z8F0130HH020SG        | 1KB          | 256   | Yes  | 7               | SSOP 20-pin |

| Z8F0130PH020SG        | 1KB          | 256   | Yes  | 7               | PDIP 20-pin |

| Z8F0130QH020SG        | 1KB          | 256   | Yes  | 7               | QFN 20-pin  |

| Z8F0131SH020SG        | 1KB          | 256   | Yes  | 0               | SOIC 20-pin |

| Z8F0131HH020SG        | 1KB          | 256   | Yes  | 0               | SSOP 20-pin |

| Z8F0131PH020SG        | 1KB          | 256   | Yes  | 0               | PDIP 20-pin |

| Z8F0131QH020SG        | 1KB          | 256   | Yes  | 0               | QFN 20-pin  |

| Z8F0130SJ020SG        | 1KB          | 256   | Yes  | 8               | SOIC 28-pin |

| Z8F0130HJ020SG        | 1KB          | 256   | Yes  | 8               | SSOP 28-pin |

| Z8F0130PJ020SG        | 1KB          | 256   | Yes  | 8               | PDIP 28-pin |

| Z8F0130QJ020SG        | 1KB          | 256   | Yes  | 8               | QFN 28-pin  |

| Z8F0131SJ020SG        | 1KB          | 256   | Yes  | 0               | SOIC 28-pin |

| Z8F0131HJ020SG        | 1KB          | 256   | Yes  | 0               | SSOP 28-pin |

|                       |              |       |      |                 |             |

# Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

# Low Power Control

For more information about the Power Control Register, see the <u>Power Control Register</u> <u>Definitions</u> section on page 31.

# Hex Address: F80

| Bit     | 7    | 6        | 5   | 4   | 3        | 2        | 1    | 0        |  |  |  |

|---------|------|----------|-----|-----|----------|----------|------|----------|--|--|--|

| Field   |      | Reserved |     | VBO | Reserved | Reserved | COMP | Reserved |  |  |  |

| RESET   | 1    | 0        | 0   | 0   | 1        | 0        | 0    | 0        |  |  |  |

| R/W     | R/W  | R/W      | R/W | R/W | R/W      | R/W      | R/W  | R/W      |  |  |  |

| Address | F80H |          |     |     |          |          |      |          |  |  |  |

#### Table 151. Power Control Register 0 (PWRCTL0)

## Hex Address: F81

This address range is reserved.

# **LED Controller**

For more information about the LED Drive registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

## Hex Address: F82

| Bit     | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |  |

|---------|------------|------|-----|-----|-----|-----|-----|-----|--|--|--|--|--|

| Field   | LEDEN[7:0] |      |     |     |     |     |     |     |  |  |  |  |  |

| RESET   | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |  |

| R/W     | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |  |

| Address |            | F82H |     |     |     |     |     |     |  |  |  |  |  |

#### Table 152. LED Drive Enable (LEDEN)