Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-VQFN                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0131qj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Part Selection Guide**

Table 1 lists the basic features available for each device within the Z8 Encore! F0830 Series product line. See the <u>Ordering Information</u> chapter on page 200 for details.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS<br>(64B) | ADC |

|----------------|---------------|------------|---------------|-----|

| Z8F1232        | 12            | 256        | No            | Yes |

| Z8F1233        | 12            | 256        | No            | No  |

| Z8F0830        | 8             | 256        | Yes           | Yes |

| Z8F0831        | 8             | 256        | Yes           | No  |

| Z8F0430        | 4             | 256        | Yes           | Yes |

| Z8F0431        | 4             | 256        | Yes           | No  |

| Z8F0230        | 2             | 256        | Yes           | Yes |

| Z8F0231        | 2             | 256        | Yes           | No  |

| Z8F0130        | 1             | 256        | Yes           | Yes |

| Z8F0131        | 1             | 256        | Yes           | No  |

|                |               |            |               |     |

Table 1. Z8 Encore! F0830 Series Family Part Selection Guide

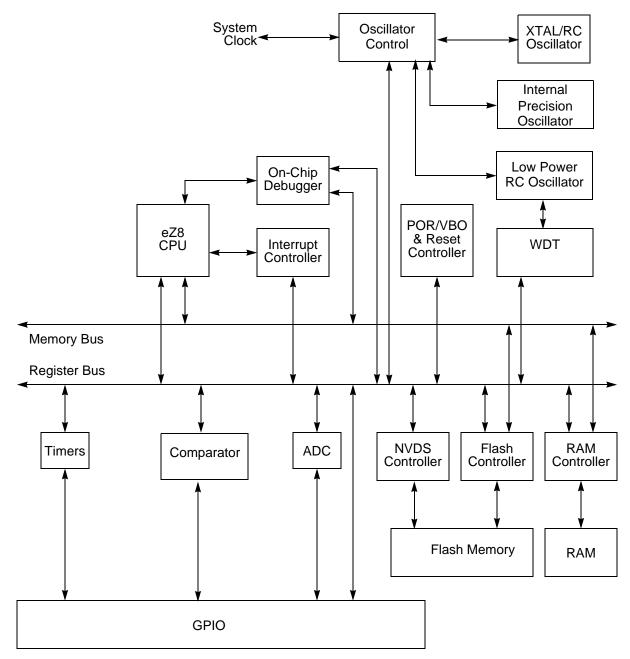

# **Block Diagram**

Figure 1 displays a block diagram of the Z8 Encore! F0830 Series architecture.

Figure 1. Z8 Encore! F0830 Series Block Diagram

29

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                                                                                                                                                                                                                                                                   | 5           | 4            | 3         | 2        | 1 | 0 |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-----------|----------|---|---|--|--|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                           | STOP                                                                                                                                                                                                                                                                                                | WDT         | EXT          |           | Reserved |   |   |  |  |

| RESET       | :                                                                                                                                                                                                                                                                                                                                                                                                                                             | See Table 13                                                                                                                                                                                                                                                                                        | 3           | 0            | 0         | 0        | 0 | 0 |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                                                                                                                                                                                                                                                                   | R           | R            | R         | R        | R | R |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                     |             | FF           | ОH        |          |   |   |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                         |             |              |           |          |   |   |  |  |

| [7]<br>POR  | This bit is s                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>Power-On Reset Indicator</b><br>This bit is set to 1 if a Power-On Reset event occurs and is reset to 0, if a WDT time-out or Stop<br>Mode Recovery occurs. Reading this register also reset this bit to 0.                                                                                      |             |              |           |          |   |   |  |  |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>This bit is set to 1 if a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery is not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |                                                                                                                                                                                                                                                                                                     |             |              |           |          |   |   |  |  |

| [5]<br>WDT  | This bit is s<br>Recovery fr                                                                                                                                                                                                                                                                                                                                                                                                                  | Watchdog Timer Time-Out Indicator<br>This bit is set to 1 if a WDT time-out occurs. A Power-On Reset resets this pin. A Stop Mode<br>Recovery from a change in an input pin also resets this bit. Reading this register resets this bit.<br>This read must occur before clearing the WDT interrupt. |             |              |           |          |   |   |  |  |

| [4]<br>EXT  | If this bit is<br>a Stop Mod                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>External Reset Indicator</b><br>If this bit is set to 1, a reset initiated by the external RESET pin occurred. A Power-On Reset or<br>a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                              |             |              |           |          |   |   |  |  |

| [3:0]       | Reserved<br>These regis                                                                                                                                                                                                                                                                                                                                                                                                                       | sters are res                                                                                                                                                                                                                                                                                       | erved and n | nust be prog | rammed to | 0000.    |   |   |  |  |

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out                 | 0   | 1    | 1   | 0   |

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for Alternate function CLKIN. Write to the Oscillator Control Register (see the <u>Oscillator Control Register Definitions</u> section on page 154) to select the PB3 as the system clock.

| Port                | ort Pin Mnemonic |            | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|---------------------|------------------|------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1</sup> | PA0              | T0IN/T0OUT | Timer 0 input/Timer 0 output complement | N/A                                     |

|                     |                  | Reserved   |                                         |                                         |

|                     | PA1              | TOOUT      | Timer 0 output                          |                                         |

|                     |                  | Reserved   |                                         |                                         |

|                     | PA2              | Reserved   | Reserved                                |                                         |

|                     |                  | Reserved   |                                         |                                         |

|                     | PA3              | Reserved   | Reserved                                |                                         |

|                     |                  | Reserved   |                                         |                                         |

|                     | PA4              | Reserved   | Reserved                                |                                         |

|                     |                  | Reserved   |                                         |                                         |

|                     | PA5              | Reserved   | Reserved                                |                                         |

|                     |                  | Reserved   |                                         |                                         |

|                     | PA6              | T1IN/T1OUT | Timer 1 input/Timer 1 output complement |                                         |

|                     |                  | Reserved   |                                         |                                         |

|                     | PA7              | T1OUT      | Timer 1 output                          |                                         |

|                     |                  | Reserved   |                                         |                                         |

#### Table 16. Port Alternate Function Mapping

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

## Port A–D Pull-up Enable Subregisters

The Port A–D Pull-Up Enable Subregister is accessed through the Port A–D Control Register by writing 06H to the Port A–D Address Register. See Table 26. Setting the bits in the Port A–D Pull-Up Enable subregisters enables a weak internal resistive pull-up on the specified port pins.

| Bit     | 1                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | PPUE7                                                                                 | PPUE6 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |       |  |

#### Table 26. Port A–D Pull-Up Enable Subregisters (PxPUE)

| Bit                                                        | Description                                       |  |  |  |  |

|------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| [7:0]                                                      | Port Pull-Up Enable                               |  |  |  |  |

| PxPUE                                                      | 0 = The weak pull-up on the port pin is disabled. |  |  |  |  |

|                                                            | 1 = The weak pull-up on the port pin is enabled.  |  |  |  |  |

| Note: x indicates the specific GPIO port pin number (7–0). |                                                   |  |  |  |  |

# LED Drive Enable Register

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6    | 5   | 4    | 3      | 2   | 1   | 0   |  |

|---------|-----|------|-----|------|--------|-----|-----|-----|--|

| Field   |     |      |     | LEDE | N[7:0] |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0    | 0      | 0   | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W  | R/W    | R/W | R/W | R/W |  |

| Address |     | F82H |     |      |        |     |     |     |  |

| Bit   | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | LED Drive Enable                                                                                                                                                           |

| LEDEN | These bits determine which Port C pins are connected to an internal current sink.<br>0 = Tristate the Port C pin.<br>1= Connect controlled current sink to the Port C pin. |

# LED Drive Level High Register

The LED Drive Level High Register, shown in Table 32, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7   | 6            | 5   | 4   | 3    | 2   | 1   | 0   |  |  |  |  |

|---------|-----|--------------|-----|-----|------|-----|-----|-----|--|--|--|--|

| Field   |     | LEDLVLH[7:0] |     |     |      |     |     |     |  |  |  |  |

| RESET   | 0   | 0            | 0   | 0   | 0    | 0   | 0   | 0   |  |  |  |  |

| R/W     | R/W | R/W          | R/W | R/W | R/W  | R/W | R/W | R/W |  |  |  |  |

| Address |     |              |     | F8  | F83H |     |     |     |  |  |  |  |

## Bit Description

[7:0] LED Level High Bits

LEDLVLH {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3mA.

01= 7 mA.

10= 13mA.

11= 20mA.

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                              |

|----------|-------------------------------------|-----------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                              |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer chapter)                           |

|          | 003AH                               | Primary oscillator fail trap (not an interrupt)                       |

|          | 003CH                               | Watchdog Oscillator fail trap (not an interrupt)                      |

|          | 0006H                               | Illegal instruction trap (not an interrupt)                           |

|          | 0008H                               | Reserved                                                              |

|          | 000AH                               | Timer 1                                                               |

|          | 000CH                               | Timer 0                                                               |

|          | 000EH                               | Reserved                                                              |

|          | 0010H                               | Reserved                                                              |

|          | 0012H                               | Reserved                                                              |

|          | 0014H                               | Reserved                                                              |

|          | 0016H                               | ADC                                                                   |

|          | 0018H                               | Port A7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A3, selectable rising or falling input edge                      |

|          | 0022H                               | Port A2, selectable rising or falling input edge                      |

|          | 0024H                               | Port A1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                              |

|          | 002AH                               | Reserved                                                              |

|          | 002CH                               | Reserved                                                              |

|          | 002EH                               | Reserved                                                              |

|          | 0030H                               | Port C3, both input edges                                             |

|          | 0032H                               | Port C2, both input edges                                             |

|          | 0034H                               | Port C1, both input edges                                             |

|          | 0036H                               | Port C0, both input edges                                             |

| Lowest   | 0038H                               | Reserved                                                              |

## Table 34. Trap and Interrupt Vectors in Order of Priority

• Writing 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (disable interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the Interrupt Controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction Trap

- Primary oscillator fail trap

- Watchdog Oscillator fail trap

# **Interrupt Vectors and Priority**

The Interrupt Controller supports three levels of interrupt priority. Level 3 is the highest priority, level 2 is the second highest priority and level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 54. Level 3 interrupts are always assigned higher priority than level 2 interrupts and level 2 interrupts are assigned higher priority than level 1 interrupts. Within each interrupt priority level (level 1, level 2 or level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), primary oscillator fail trap, Watchdog Oscillator fail trap and illegal instruction trap always have highest (level 3) priority.

# **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the interrupt request register is cleared. Writing 0 to the corresponding bit in the interrupt request register clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

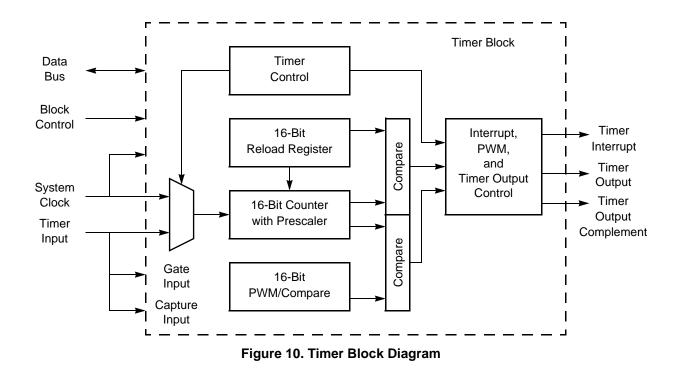

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer resets back to 0000H and continues counting.

# **Timer Operating Modes**

The timers can be configured to operate in the following modes:

## **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

Additionally, if the timer output alternate function is enabled, the timer output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the timer output Alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the timer output function) for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

Continuous Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

# **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin: timer input alternate function. The TPOL bit in the Timer Control Register determines whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period.

If TPOL bit is set to 0, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL bit is set to 1, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$

#### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to 16-bit PWM match value stored in the timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the timer output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the timer output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The timer output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the timer output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The timer output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal: the timer output complement. The timer output complement is the complement of the timer output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a Low to a High (inactive to active) to ensure a time gap between the deassertion of one PWM output to the assertion of its complement.

# **ADC Interrupt**

The ADC can generate an interrupt request when a conversion has been completed. An interrupt request that is pending when the ADC is disabled is not cleared automatically.

# **Reference Buffer**

The reference buffer, RBUF, supplies the reference voltage for the ADC. When enabled, the internal voltage reference generator supplies the ADC. When RBUF is disabled, the ADC must have the reference voltage supplied externally through the  $V_{REF}$  pin in 28-pin package. RBUF is controlled by the REFEN bit in the ADC Control Register.

# **Internal Voltage Reference Generator**

The internal voltage reference generator provides the voltage VR2, for the RBUF. VR2 is 2V.

# **Calibration and Compensation**

A user can perform calibration and store the values into Flash or the user code can perform a manual offset calibration. There is no provision for manual gain calibration.

# **ADC Control Register Definitions**

The ADC Control registers are defined in this section.

# Sample Settling Time Register

The <u>Sample Settling</u> Time Register, shown in Table 66, is used to program a delay after the <u>SAMPLE/HOLD</u> signal is asserted and before the START signal is asserted; an ADC conversion then begins. The number of clock cycles required for settling will vary from system to system depending on the system clock period used. The system designer should program this register to contain the number of clocks required to meet a  $0.5 \mu s$  minimum settling time.

| Bit     | 7 | 6    | 5     | 4 | 3   | 2  | 1 | 0 |  |  |  |

|---------|---|------|-------|---|-----|----|---|---|--|--|--|

| Field   |   | Rese | erved |   | SST |    |   |   |  |  |  |

| RESET   |   | (    | )     |   | 1   | 1  | 1 | 1 |  |  |  |

| R/W     |   | F    | २     |   |     | R/ | W |   |  |  |  |

| Address |   |      |       |   |     |    |   |   |  |  |  |

## Table 66. Sample Settling Time (ADCSST)

| Bit          | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                  |

| [3:0]<br>SST | 0h–Fh = Sample settling time in number of system clock periods to meet 0.5 $\mu$ s minimum. |

# **Comparator Control Register Definitions**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference. The GPIO pin is always used as positive comparator input.

| Bit             | 7                                                                                                                                                                                                                                     | 6                                                                                                                                                                                | 5            | 4           | 3            | 2   | 1    | 0     |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|--------------|-----|------|-------|--|--|--|--|--|

| Field           | Reserved                                                                                                                                                                                                                              | INNSEL                                                                                                                                                                           |              | REF         | LVL          |     | Rese | erved |  |  |  |  |  |

| RESET           | 0                                                                                                                                                                                                                                     | 0                                                                                                                                                                                | 0            | 1           | 0            | 1   | 0 0  |       |  |  |  |  |  |

| R/W             | R/W                                                                                                                                                                                                                                   | R/W                                                                                                                                                                              | R/W          | R/W         | R/W          | R/W | R/W  | R/W   |  |  |  |  |  |

| Address         |                                                                                                                                                                                                                                       | F90H                                                                                                                                                                             |              |             |              |     |      |       |  |  |  |  |  |

| Bit             | Descriptio                                                                                                                                                                                                                            | escription                                                                                                                                                                       |              |             |              |     |      |       |  |  |  |  |  |

| [7]             | Reserved<br>This bit is re                                                                                                                                                                                                            | eserved and                                                                                                                                                                      | must be pro  | ogrammed to | o 0.         |     |      |       |  |  |  |  |  |

| [6]<br>INNSEL   | 0 = internal                                                                                                                                                                                                                          | Signal Select for Negative Input<br>) = internal reference disabled, GPIO pin used as negative comparator input.<br>I = internal reference enabled as negative comparator input. |              |             |              |     |      |       |  |  |  |  |  |

| [5:2]<br>REFLVL | This referent<br>$0000 = 0.0^{\circ}$<br>$0001 = 0.2^{\circ}$<br>$0010 = 0.4^{\circ}$<br>$0110 = 0.8^{\circ}$<br>$0100 = 0.8^{\circ}$<br>$0101 = 1.2^{\circ}$<br>$0111 = 1.4^{\circ}$<br>$1000 = 1.6^{\circ}$<br>$1001 = 1.8^{\circ}$ | V.<br>V.<br>V.<br>V (Default).<br>V.<br>V.                                                                                                                                       | endent of th | e ADC volta | ge reference | 9.  |      |       |  |  |  |  |  |

| [1:0]           | Reserved<br>These bits a                                                                                                                                                                                                              | are reserved                                                                                                                                                                     | l and must b | e programm  | ned to 00.   |     |      |       |  |  |  |  |  |

#### Table 68. Comparator Control Register (CMP0)

**Read OCD Control Register (05H).** The read OCD Control Register command reads the value of the OCDCTL register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

**Write Program Counter (06H).** The write program counter command, writes the data that follows to the eZ8 CPU's program counter (PC). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, the program counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

**Read Program Counter (07H).** The read program counter command, reads the value in the eZ8 CPUs program counter (PC). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The write register command, writes data to the register file. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash read protect option bit is enabled, only writes to the Flash control registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**Read Register (09H).** The read register command, reads data from the register file. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, this command returns FFH for all of the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

**Write Program Memory (0AH).** The write program memory command, writes data to program memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash read protect option bit is enabled, the data is discarded.

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# **Internal Precision Oscillator**

The Internal Precision Oscillator (IPO) is designed for use without external components. The user can either manually trim the oscillator for a nonstandard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency with  $\pm 4\%$  accuracy and 45%~55% duty cycle over the operating temperature and supply voltage of the device. The maximum start-up time of the IPO is 25µs. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8kHz (contains both a FAST and a SLOW mode)

- Trimming possible through Flash option bits, with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

# Operation

The internal oscillator is an RC relaxation oscillator with a minimized sensitivity to power supply variations. By using ratio-tracking thresholds, the effect of power supply voltage is cancelled out. The dominant source of oscillator error is the absolute variance of chip-level fabricated components, such as capacitors. An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed, the oscillator frequency is stable and does not require subsequent calibration. Trimming was performed during manufacturing and is not necessary for the user to repeat unless a frequency other than 5.53 MHz (FAST mode) or 32.8 kHz (SLOW mode) is required.

**Note:** The user can power down the IPO block for minimum system power.

By default, the oscillator is configured through the Flash option bits. However, the user code can override these trim values, as described in *the* <u>Trim Bit Address Space</u> section on page 129.

Select one of two frequencies for the oscillator: 5.53 MHz or 32.8 kHz, using the OSCSEL bits described in the <u>Oscillator Control</u> chapter on page 151.

| Assembly      |                                                                          |     | ress<br>ode | Op<br>Code(s) |       |   | Fla | ags |   |   | Fetch | Instr. |

|---------------|--------------------------------------------------------------------------|-----|-------------|---------------|-------|---|-----|-----|---|---|-------|--------|

| Mnemonic      | Symbolic Operation                                                       | dst | src         | (Hex)         | C Z S |   |     | V D |   | Η |       |        |

| POPX dst      | dst $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 1                           | ER  |             | D8            | -     | _ | _   | -   | _ | - | 3     | 2      |

| PUSH src      | $SP \leftarrow SP - 1$                                                   | R   |             | 70            | -     | - | _   | -   | _ | - | 2     | 2      |

|               | $@SP \leftarrow src$                                                     | IR  |             | 71            | -     |   |     |     |   |   | 2     | 3      |

|               | -                                                                        | IM  |             | IF70          | -     |   |     |     |   |   | 3     | 2      |

| PUSHX src     | $SP \leftarrow SP - 1$<br>@SP ← src                                      | ER  |             | C8            | _     | - | -   | _   | _ | - | 3     | 2      |

| RCF           | C ← 0                                                                    |     |             | CF            | 0     | - | -   | -   | _ | - | 1     | 2      |

| RET           | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |     |             | AF            | -     | - | -   | -   | _ | - | 1     | 4      |

| RL dst        |                                                                          | R   |             | 90            | *     | * | *   | *   | _ | _ | 2     | 2      |

|               | C                                                                        | IR  |             | 91            |       |   |     |     |   |   | 2     | 3      |

| RLC dst       |                                                                          | R   |             | 10            | *     | * | *   | *   | - | _ | 2     | 2      |

|               | C D7 D6 D5 D4 D3 D2 D1 D0 dst                                            | IR  |             | 11            |       |   |     |     |   |   | 2     | 3      |

| RR dst        |                                                                          | R   |             | E0            | *     | * | *   | *   | _ | - | 2     | 2      |

|               | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C                                            | IR  |             | E1            |       |   |     |     |   |   | 2     | 3      |

| RRC dst       |                                                                          | R   |             | C0            | *     | * | *   | *   | _ | - | 2     | 2      |

|               | ► D7D6D5D4D3D2D1D0 ► C                                                   | IR  |             | C1            |       |   |     |     |   |   | 2     | 3      |

| SBC dst, src  | $dst \gets dst - src - C$                                                | r   | r           | 32            | *     | * | *   | *   | 1 | * | 2     | 3      |

|               |                                                                          | r   | lr          | 33            | _     |   |     |     |   |   | 2     | 4      |

|               |                                                                          | R   | R           | 34            |       |   |     |     |   |   | 3     | 3      |

|               | -                                                                        | R   | IR          | 35            |       |   |     |     |   |   | 3     | 4      |

|               | -                                                                        | R   | IM          | 36            | _     |   |     |     |   |   | 3     | 3      |

|               |                                                                          | IR  | IM          | 37            |       |   |     |     |   |   | 3     | 4      |

| SBCX dst, src | $dst \gets dst - src - C$                                                | ER  | ER          | 38            | *     | * | *   | *   | 1 | * | 4     | 3      |

|               | -                                                                        | ER  | IM          | 39            | _     |   |     |     |   |   | 4     | 3      |

| SCF           | C ← 1                                                                    |     |             | DF            | 1     | _ | _   | _   | _ | _ | 1     | 2      |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

177

|   |                         |                          |                              |                                |                            |                               | Lo                         | ower Nil                       | bble (He                      | x)                           |                            |                          |                           |                           |                  |                           |

|---|-------------------------|--------------------------|------------------------------|--------------------------------|----------------------------|-------------------------------|----------------------------|--------------------------------|-------------------------------|------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|------------------|---------------------------|

|   | 0                       | 1                        | 2                            | 3                              | 4                          | 5                             | 6                          | 7                              | 8                             | 9                            | А                          | В                        | С                         | D                         | Е                | F                         |

| 0 | 1.1<br>BRK              | 2.2<br>SRP<br>IM         | 2.3<br>ADD<br>r1,r2          | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1          | 3.3<br><b>ADD</b><br>R1,IM | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1        | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP                |

| 1 | 2.2<br><b>RLC</b><br>R1 | 2.3<br>RLC<br>IR1        | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1        | 3.4<br>ADC<br>IR2,R1          | 3.3<br>ADC<br>R1,IM        | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1        |                            |                          |                           | 00,271                    |                  | See 2nd<br>Op Code<br>Map |

| 2 | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1        | 2.3<br>SUB<br>r1,r2          | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br>SUB<br>IR2,R1          | 3.3<br>SUB<br>R1,IM        | 3.4<br>SUB<br>IR1,IM           | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br>SUBX                  |                            |                          |                           |                           |                  | map                       |

| 3 | 2.2<br>DEC<br>R1        | 2.3<br>DEC<br>IR1        | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br>SBC<br>R2,R1        | 3.4<br>SBC<br>IR2,R1          | 3.3<br>SBC<br>R1,IM        | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1 |                            |                          |                           |                           |                  |                           |

| 4 | 2.2<br>DA<br>R1         | 2.3<br>DA<br>IR1         | 2.3<br>OR<br>r1,r2           | 2.4<br>OR<br>r1,lr2            | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br>OR<br>IR2,R1           | 3.3<br>OR<br>R1,IM         | 3.4<br>OR<br>IR1,IM            | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1  |                            |                          |                           |                           |                  |                           |

| 5 | 2.2<br>POP<br>R1        | 2.3<br><b>POP</b><br>IR1 | 2.3<br>AND<br>r1,r2          | 2.4<br>AND<br>r1,lr2           | 3.3<br>AND<br>R2,R1        | 3.4<br>AND<br>IR2,R1          | 3.3<br>AND<br>R1,IM        | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1        |                            |                          |                           |                           |                  | 1.2<br>WDT                |

| 6 | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1        | 2.3<br>TCM<br>r1,r2          | 2.4<br>TCM<br>r1,lr2           | 3.3<br>TCM<br>R2,R1        | 3.4<br>TCM<br>IR2,R1          | 3.3<br>TCM<br>R1,IM        | 3.4<br>TCM<br>IR1,IM           | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1 |                            |                          |                           |                           |                  | 1.2<br>STOP               |

| 7 | 2.2<br>PUSH<br>R2       | 2.3<br>PUSH<br>IR2       | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1    | 3.3<br><b>TM</b><br>R1,IM  | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1  |                            |                          |                           |                           |                  | 1.2<br>HALT               |

| 8 | 2.5<br>DECW<br>RR1      | 2.6<br>DECW<br>IRR1      | 2.5<br>LDE<br>r1,lrr2        | 2.9<br>LDEI<br>Ir1,Irr2        | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2         | 3.4<br>LDX                 | 3.5<br>LDX<br>IRR2,IR1         | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X       |                            |                          |                           |                           |                  | 1.2<br>DI                 |

| 9 | 2.2<br>RL<br>R1         | 2.3<br>RL<br>IR1         | 2.5<br>LDE<br>r2,lrr1        | 2.9<br>LDEI<br>Ir2,Irr1        | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1         | 3.4<br>LDX                 | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br>LEA<br>r1,r2,X         | 3.5<br>LEA<br>rr1,rr2,X      |                            |                          |                           |                           |                  | 1.2<br>El                 |

| A | 2.5<br>INCW<br>RR1      | 2.6<br>INCW<br>IRR1      | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1    | 3.3<br><b>CP</b><br>R1,IM  | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br>CPX<br>IM,ER1         |                            |                          |                           |                           |                  | 1.4<br>RET                |

| В | 2.2<br><b>CLR</b><br>R1 | 2.3<br><b>CLR</b><br>IR1 | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br>XOR<br>r1,lr2           | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br><b>XOR</b><br>IR2,R1   | 3.3<br><b>XOR</b><br>R1,IM | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1 |                            |                          |                           |                           |                  | 1.5<br>IRET               |

| С | 2.2<br><b>RRC</b><br>R1 | 2.3<br><b>RRC</b><br>IR1 | 2.5<br><b>LDC</b><br>r1,lrr2 | 2.9<br><b>LDCI</b><br>Ir1,Irr2 | 2.3<br><b>JP</b><br>IRR1   | 2.9<br><b>LDC</b><br>Ir1,Irr2 |                            | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                              |                            |                          |                           |                           |                  | 1.2<br>RCF                |

| D | 2.2<br><b>SRA</b><br>R1 | 2.3<br><b>SRA</b><br>IR1 | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>Ir2,Irr1 | 2.6                        | 2.2<br><b>BSWAP</b><br>R1     | 3.3<br>CALL<br>DA          | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                              |                            |                          |                           |                           |                  | 1.2<br>SCF                |

| E | 2.2<br><b>RR</b><br>R1  | 2.3<br><b>RR</b><br>IR1  | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1    | 3.2<br><b>LD</b><br>R1,IM  | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1         |                            |                          |                           |                           |                  | 1.2<br>CCF                |

| F | 2.2<br>SWAP<br>R1       | 2.3<br>SWAP<br>IR1       | 2.6<br>TRAP<br>Vector        | 2.3<br>LD<br>lr1,r2            | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1    | 3.3<br><b>BTJ</b>          | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               | -                            | V                          | V                        | V                         | ▼                         | ▼                |                           |

# Figures 29 and 30 provide information about each of the eZ8 CPU instructions.

Figure 29. First Op Code Map

Upper Nibble (Hex)

|                             | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     |         | = 2.7 to<br>0°C to + |     |        |                                                 |  |

|-----------------------------|----------------------------------------------------------------|-----|-----|---------|----------------------|-----|--------|-------------------------------------------------|--|

| Parameter                   | Min                                                            | Тур | Max | Min     | Тур                  | Max | Units  | Notes                                           |  |

| NVDS Byte Read<br>Time      |                                                                |     |     | 71      | -                    | 258 | μs     | Withsystemclockat<br>20MHz                      |  |

| NVDS Byte Pro-<br>gram Time |                                                                |     |     | 126     | -                    | 136 | μs     | Withsystemclockat<br>20MHz                      |  |

| Data Retention              |                                                                |     |     | 10      | _                    | _   | years  | 25°C                                            |  |

| Endurance                   |                                                                |     |     | 100,000 | -                    | -   | cycles | Cumulative write<br>cycles for entire<br>memory |  |

#### Table 121. Nonvolatile Data Storage

**Note:** For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write can take up to 58 ms to complete.

#### Table 122. Analog-to-Digital Converter Electrical Characteristics and Timing

|                  |                                                 | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     |     | = 2.7 to<br>40°C to |     |       |                |

|------------------|-------------------------------------------------|----------------------------------------------------------------|-----|-----|-----|---------------------|-----|-------|----------------|

| Symbol           | Parameter                                       | Min                                                            | Тур | Max | Min | Тур                 | Мах | Units | Conditions     |

|                  | Resolution                                      |                                                                |     |     | _   | 10                  | _   | bits  |                |

|                  | Differential<br>Nonlinearity (DNL) <sup>1</sup> |                                                                |     |     | -1  | -                   | +4  | LSB   |                |

|                  | Integral<br>Nonlinearity (INL) <sup>1</sup>     |                                                                |     |     | -5  | _                   | +5  | LSB   |                |

|                  | Gain Error                                      |                                                                |     |     |     | 15                  |     | LSB   |                |

|                  | Offset Error                                    |                                                                |     |     | -15 | _                   | 15  | LSB   | PDIP package   |

|                  | -                                               |                                                                |     |     | -9  | -                   | 9   | LSB   | Other packages |

| V <sub>REF</sub> | On chip reference                               |                                                                |     |     | 1.9 | 2.0                 | 2.1 | V     |                |

|                  | Active Power<br>Consumption                     |                                                                |     |     |     | 4                   |     | mA    |                |

|                  | Power Down<br>Current                           |                                                                |     |     |     |                     | 1   | μA    |                |

Note: <sup>1</sup>When the input voltage is lower than 20mV, the conversion error is out of spec.

193

>

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# Hex Addresses: FC9–FCC

This address range is reserved.

## Hex Address: FCD

#### Table 166. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |      |      |      | FC   | DH   |      |      |      |

## Hex Address: FCE

#### Table 167. Shared Interrupt Select Register (IRQSS)

| Bit     | 7        | 6     | 5   | 4   | 3    | 2     | 1   | 0   |  |  |  |

|---------|----------|-------|-----|-----|------|-------|-----|-----|--|--|--|

| Field   | Reserved | PA6CS |     |     | Rese | erved |     |     |  |  |  |

| RESET   | 0        | 0     | 0   | 0   | 0    | 0     | 0   | 0   |  |  |  |

| R/W     | R/W      | R/W   | R/W | R/W | R/W  | R/W   | R/W | R/W |  |  |  |

| Address |          | FCEH  |     |     |      |       |     |     |  |  |  |

# Hex Address: FCF

#### Table 168. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6    | 5 | 4 | 3        | 2 | 1 | 0 |  |  |  |

|---------|------|------|---|---|----------|---|---|---|--|--|--|

| Field   | IRQE |      |   |   | Reserved |   |   |   |  |  |  |

| RESET   | 0    | 0    | 0 | 0 | 0        | 0 | 0 | 0 |  |  |  |

| R/W     | R/W  | R    | R | R | R        | R | R | R |  |  |  |

| Address |      | FCFH |   |   |          |   |   |   |  |  |  |