Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | ·                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0131sj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! <sup>®</sup> F0830 Series Product Specification

#### xvi

| 93 |

|----|

|    |

| 94 |

| 5  |

| 6  |

| 7  |

|    |

|    |

| 07 |

| 8  |

| 9  |

|    |

|    |

|    |

|    |

|    |

|    |

| C  |

| 1  |

| •  |

| •  |

| -  |

| -  |

|    |

|    |

|    |

|    |

|    |

|    |

# **Pin Description**

The Z8 Encore! F0830 Seriesoplucts are available in a very of package styles and pin configurations. This chaptees cribes the signals and the pin configurations for each of the package styles. For information about physical package specifications, see the Packaging chapter on page 199.

# **Available Packages**

Table 3 lists the package styles that are available for each device in the Z8 Encore! F0830 Series product line.

| Part    |     | 20-pin | 20-pin | 20-pin | 20-pin | 28-pin | 28-pin | 28-pin | 28-pin |

|---------|-----|--------|--------|--------|--------|--------|--------|--------|--------|

| Number  | ADC | QFN    | SOIC   | SSOP   | PDIP   | QFN    | SOIC   | SSOP   | PDIP   |

| Z8F1232 | Yes | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F1233 | No  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F0830 | Yes | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F0831 | No  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F0430 | Yes | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F0431 | No  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F0230 | Yes | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F0231 | No  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F0130 | Yes | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

| Z8F0131 | No  | Х      | Х      | Х      | Х      | Х      | Х      | Х      | Х      |

Table 3. Z8 Encore! F0830 Series Package Options

# **Pin Configurations**

Figures 2 and 3 display the pin configurations of all of the packages available in the Z8 Encore! F0830 Series. Seeble 4 on page 11 for a description of the signals. Analog input alternate functions (ANAx) are not available on the following devices:

- Z8F0831

- Z8F0431

- Z8F0131

- Z8F0231

- Z8F1233

# **Address Space**

The eZ8 CPU can access the followthgee distinct address spaces:

- The register file addresses access for the get purpose registers and the eZ8 CPU, peripheral and general purpose I/O port control registers

- The program memory addresses access for the memory locations having executable code and/or data

- The data memory addresses access for **theof**nemory locationsontaining only the data

The following sections describe these that deress spaces. For momentation about the eZ8 CPU and its address space, refer teztified to the eZ8 CPU and its address space, refer teztified to the eZ8 CPU and its address space, refer text to the eZ8 CPU and its address space with the eZ8 CPU and

# **Register File**

The register file address space in the Z8 Encore! MCU is 4KB (4096 bytes). The register file consists of two sections ontrol registers and general-purpose registers. When instructions are executed, registers defined as ce are read and registers defined as *tions* are written. The architecture of the eZ8UCa lows all general purpose registers to function as accumulators, address pointers, index registers, stack areas or scratch pad memory.

The upper 256 bytes of the 4KB register **äbe** dress space are reserved for controlling the eZ8 CPU, on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within **2566** B Control Register section are reserved (unavailable). Reading from a reserved register file address returns an undefined value. Writing to reserved register fibe dresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address in the register file address space. The Z8 Encore! F0830 Series devices contain up **16 E25f** on-chip RAM. Reading from register file addresses outside the available RAM **address** (and not within the Control Register address space), returns an undefined value **in4/tio** these register file addresses has no effect.

#### Port A–D Pull-up Enable Subregisters

The Port A–D Pull-Up Enableoubregister is accessed through Port A–D Control Register by writing06H to the Port A–D Address Register Table 26. Setting the bits in the Port A–D Pull-Up Enable subregers enables a weak intermesistive pull-up on the specified port pins.

| Bit     | 7         | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | PPUE7     | PPUE6                                                                                 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |  |

| RESET   | 0         | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W       | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address | lf 06H ir | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |  |  |

| <b>T</b>     00 |          | <b>D</b> II I I |        | <b>o</b> 1 · <i>i</i> |         |  |

|-----------------|----------|-----------------|--------|-----------------------|---------|--|

| Table 26.       | Port A–D | Pull-Up         | Enable | Subregisters          | (PXPUE) |  |

| Bit          | Description                                                |  |  |  |  |  |

|--------------|------------------------------------------------------------|--|--|--|--|--|

| [7:0]        | Port Pull-Up Enable                                        |  |  |  |  |  |

| <b>PxPUE</b> | 0 = The weak pull-up on the port pin is disabled.          |  |  |  |  |  |

|              | 1 = The weak pull-up on the port pin is enabled.           |  |  |  |  |  |

| Note: x ii   | Note: x indicates the specific GPIO port pin number (7–0). |  |  |  |  |  |

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the timer output Mernate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte regist to set the startingpunt value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, countinglways begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate)daret the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pfruting the timer output function) for the timer output alternate function.

- 6. Write to the Timer Control Register to able the timer and initiate counting.

In CONTINUOUS Mode, the system clock alyzeprovides the timer input. The timer period is calculated in the following equation:

Continuous Mode Time-Out Period (s) Reload Valueu Prescale System Clock Frequency (Hz)

If an initial starting value other than 01H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation determine the first time-out period.

#### COUNTER Mode

In COUNTER Mode, the timer counts input institutions from a GPIO port pin. The timer input is taken from the GPIO ptopin: timer input alternate function. The TPOL bit in the Timer Control Register determents whether the count occurs on the rising edge or the falling edge of the timer input signal. COUNTER Mode, the prescaler is disabled.

Caution: The input frequency of the timer input signmust not exceed one-fourth the system clock frequency.

Upon reaching the reload value in the Timer Reload High and Low Byte registers, the timer generates  $\frac{1}{2}$  matter rupt, the count value in the Ter High and Low Byte registers is reset to 001H and counting resumes. Additionally the timer output alternate function

#### WDT Reset in Normal Operation

If configured to generate a reset when ætimut occurs, the Wahdog Timer forces the device into the System Reset state. The TWS Datus bit in the Watchdog Timer Control Register is set to 1. Sever Reset and Stop Mode Recovery apper on page 21 for more information about system reset operations.

#### WDT Reset in STOP Mode

If configured to generate a reset when a **tone** occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following WDT time-out in STOP Mode. Set <u>Reset and Stop Mode Recov</u> of <u>page 21</u> for more information about Stop Mode Recovery operations.

#### Watchdog Timer Relo ad Unlock Sequence

Writing the unlock sequence to the WatchdTimer (WDTCTL) Control Register address, unlocks the three Watchdog Ti**Rel**oad Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect onbilteein the WDTCTL Register. The locking mechanism prevents spurious writes to the reload registers.

The following sequence is required to unlock the Watchdorg mer Reload Byte registers (WDTU, WDTH and WDTL) for write access:

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reloadpper Byte Register (WDTU).

- 4. Write the Watchdog Timer Reloadigh Byte Register (WDTH).

- 5. Write the Watchdog Timer Redd Low Byte Register (WDTL).

All three Watchdog Timer Reload registersshipe written in the order listed above. There must be no other register writes between of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog TimeloRe registers is loaded into the counter when the Watchdog Timer first enabled and every time a WDT instruction is executed.

### ADC Interrupt

The ADC can generate an interpt request when a conversion has been completed. An interrupt request that is pending when the OAiB disabled is not cleared automatically.

### **Reference Buffer**

The reference buffer, RBUF, supplies the **refere** voltage for the ADC. When enabled, the internal voltage reference generator the ADC. When RBUF is disabled, the ADC must have the reference voltage supplied externally through the pin package. RBUF is controlled by the FEN bit in the ADC Control Register.

### Internal Voltage Reference Generator

The internal voltage reference generator provides the voltage VR2, for the RBUF. VR2 is 2V.

### Calibration and Compensation

A user can perform calibration and store there is provision for manual gain calibration.

# **ADC Control Register Definitions**

The ADC Control registers are defined in this section.

# Z8 Encore! <sup>®</sup> F0830 Series Product Specification

| 1FFFH          |            | <br>Page 15 | 1FFFH<br>1E00H |

|----------------|------------|-------------|----------------|

|                | Sector 7   | Page 14     | 1DFFH<br>1C00H |

| 1C00H<br>18FFH |            | <br>Page 13 | 1BFFH<br>1A00H |

| 100011         | Sector 6   | <br>Page 12 | 19FFH<br>1800H |

| 1800H<br>17FFH |            | <br>Page 11 | 17FFH<br>1600H |

| 1400H          | Sector 5   | <br>Page 10 | 15FFH<br>1400H |

| 13FFH          |            | <br>Page 9  | 13FFH<br>1200H |

|                | Sector 4   | Page 8      | 11FFH          |

| 1C00H<br>0FFFH | Contor 2   | Page 7      | 1C00H<br>0FFFH |

| 0C00H          | Sector 3   | Page 6      | 0E00H<br>0DFFH |

| 0BFFH          | O s star 0 | Page 5      | 0C00H<br>0BFFH |

| 0800H          | Sector 2   | <br>Page 4  | 0A00H<br>09FFH |

| 07FFH          | Sector 1   | Page 3      | 0800H<br>07FFH |

| 0400H          | Sector     | <br>Page 2  | 0600H<br>05FFH |

| 03FFH          | Sector 0   | Page 1      | 0400H<br>03FFH |

| 0000H          |            | <br>Page 0  | 0200H<br>0100H |

|                |            |             | 0000H          |

Figure 17. 8K Flash with NVDS

110

### Flash Control Register

The Flash Controller must be unlocked **usine** Flash Control Register before programming or erasing Flash memory. Writing the sequence BCH, sequentially, to the Flash Control Register unlocks the ash Controller. When the Flash Controller is unlocked, Flash memory can be enabled for mass eraspage erase by writing the appropriate enable command to the FCTL. Page erase applies only to the active page selected in Flash Page Select Register. Mass erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalisequence returns the Flash **Coller** to its Locked state. The write-only Flash Control Register shalles register file address with the read-only Flash Status Register.

| Bit     | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|------|---|---|---|---|---|---|--|--|

| Field   |      | FCMD |   |   |   |   |   |   |  |  |

| RESET   | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W     | W    | W    | W | W | W | W | W | W |  |  |

| Address | FF8H |      |   |   |   |   |   |   |  |  |

Bit Description

[7:0] Flash Command

FCMD 73H = First unlock command.

8CH = Second unlock command.

95H = Page erase command (must be third command in sequence to initiate page erase).

63H = Mass erase command (must be third command in sequence to initiate mass erase).

5EH = Enable Flash Sector Protect Register access.

# Byte Read

To read a byte from the NVDS array, used econust first push the address onto the stack. User code issues CALL instruction to the address of the byte-read routine (00). At the return from the subrouting read byte resides in wing register R0 and the read status byte resides in working register R1. To the fields of this status byte are defined in Table 92. Additionally, the user code shoppop the address byte off the stack.

The read routine uses 16 bytes of stack spa**æddit**ion to the one byte of address pushed by the user code. Sufficient memory **sthb**e available for this stack usage.

Due to the Flash memory aitercture, NVDS reads exhibit nonuniform execution time. A read operation takes between 71 µs 2568 µs (assuming a 20 MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (the seeeding the NVDS array size) return 0xff. Illegal read operations ave a 6 µs execution time.

The status byte returned by the NVDS read routine is zero for a successful read. If the status byte is nonzero, thereascorrupted value in the NVDs ray at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have an error.

| Bit              | 7                                                                                                                                                                                                                          | 6                                                                  | 5           | 4          | 3        | 2  | 1      | 0        |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------|------------|----------|----|--------|----------|--|--|

| Field            |                                                                                                                                                                                                                            | Reserved                                                           |             | DE         | Reserved | FE | IGADDR | Reserved |  |  |

| Default<br>Value | 0                                                                                                                                                                                                                          | 0                                                                  | 0           | 0          | 0        | 0  | 0      | 0        |  |  |

| Bit              | Description                                                                                                                                                                                                                |                                                                    |             |            |          |    |        |          |  |  |

| [7:5]            | Reserved<br>These bits a                                                                                                                                                                                                   | Reserved<br>These bits are reserved and must be programmed to 000. |             |            |          |    |        |          |  |  |

| [4]<br>DE        | Data Error<br>When reading an NVDS address, if an error is found in the latest data corresponding to this NVDS<br>address, this bit is set to 1. NVDS source code steps forward until it finds valid data at this address. |                                                                    |             |            |          |    |        |          |  |  |

| [3]              | Reserved<br>This bit is re                                                                                                                                                                                                 | eserved and                                                        | must be pro | ogrammed t | o 0.     |    |        |          |  |  |

| [2]<br>FE        | Flash Error<br>If a Flash error is detected, this bit is set to 1.                                                                                                                                                         |                                                                    |             |            |          |    |        |          |  |  |

| [1]<br>IGADDR    | Illegal Address<br>When NVDS byte reads from invalid addresses (those exceeding the NVDS array size) occur,<br>this bit is set to 1.                                                                                       |                                                                    |             |            |          |    |        |          |  |  |

| [0]              | Reserved<br>This bit is re                                                                                                                                                                                                 |                                                                    |             |            |          |    |        |          |  |  |

| Table | 92. | Read | Status | Byte |

|-------|-----|------|--------|------|

|-------|-----|------|--------|------|

Caution: It is possible to disable the clock failudetection circuitry as well as all functioning clock sources. In this case, the Z8 Encode 230 Series device ceases functioning and can only be recovered by power-on-reset.

# **Oscillator Control Register Definitions**

The following section provides bit definitions for the Oscillator Control Register.

#### **Oscillator Control Register**

The Oscillator Control Regist (OSCCTL) enables/disables thereious oscillator circuits, enables/disables the failure detection/recovernguitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must becarked before writing. Writing the two step sequence 7H followed by 18H to the Oscillator Control Regier unlocks it. The register is locked at successful completion register write to the OSCCTL.

Figure 24 displays the oscillatoontrol clock switching flow. Se<u>Eable 117</u> on page 189 to review the waiting times of various oscillator circuits.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2      | 1   | 0   |

|---------|-------|-------|-------|-------|-------|--------|-----|-----|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN | SCKSEL |     |     |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0      | 0   | 0   |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W    | R/W | R/W |

| Address | F86H  |       |       |       |       |        |     |     |

| Table 99. | Oscillator | Control | Register | (OSCCTL) |

|-----------|------------|---------|----------|----------|

|-----------|------------|---------|----------|----------|

| Bit          | Description                                                                                                                                                                 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INTEN | Internal Precision Oscillator Enable<br>1 = Internal Precision Oscillator is enabled.<br>0 = Internal Precision Oscillator is disabled.                                     |

| [6]<br>XTLEN | Crystal Oscillator Enable<br>This setting overrides the GPIO register control for PA0 and PA1.<br>1 = Crystal oscillator is enabled.<br>0 = Crystal oscillator is disabled. |

| [5]<br>WDTEN | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer Oscillator is enabled.<br>0 = Watchdog Timer Oscillator is disabled.                                                 |

ister, the user code must waitlest 5000 IPO cycles for the crystal to stabilize. After this period, the crystal oscillator may eselected as the system clock.

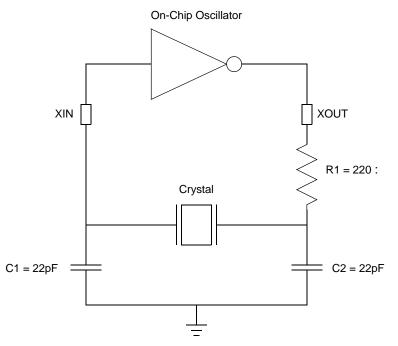

Figure 25 displays a recommended config**o**rator connection with an external fundamental-mode, parallel-resonant crystal opegat 20 MHz. Recommended 20 MHz crystal specifications are provided in Table 100. Resistois Roptional and limits total power dissipation by the crystal. Pterd circuit board layout must add no more than 4pF of stray capacitance to either the Xor  $X_{OUT}$  pins. If oscillation does not occur, reduce the values of capacitors C and C to decrease loading.

Figure 25. Recommended 20MHz Crystal Oscillator Configuration

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | :     | Maximum  |

| Load Capacitance (CL)               | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

# eZ8 CPU Instruction Summary

Table 113 summarizes the eZ8 CPU instruction the table identifies the addressing modes employed by the instruction, the effection the Flags register, the number of CPU clock cycles required for thinstruction fetch and the number of CPU clock cycles required for the instruction execution.

| Assembly      |                           |     | ress Op<br>ode Code(s) |       | Flags |   |   |   |   | _ Fetch | Instr. |        |

|---------------|---------------------------|-----|------------------------|-------|-------|---|---|---|---|---------|--------|--------|

| Mnemonic      | Symbolic Operation        | dst | src                    | (Hex) | С     | Ζ | S | V | D | Н       | Cycles | Cycles |

| ADC dst, src  | $dst \gets dst + src + C$ | r   | r                      | 12    | *     | * | * | * | 0 | *       | 2      | 3      |

|               |                           | r   | lr                     | 13    | _     |   |   |   |   |         | 2      | 4      |

|               |                           | R   | R                      | 14    | _     |   |   |   |   |         | 3      | 3      |

|               |                           | R   | IR                     | 15    | _     |   |   |   |   |         | 3      | 4      |

|               |                           | R   | IM                     | 16    | _     |   |   |   |   |         | 3      | 3      |

|               |                           | IR  | IM                     | 17    | _     |   |   |   |   |         | 3      | 4      |

| ADCX dst, src | $dst \gets dst + src + C$ | ER  | ER                     | 18    | *     | * | * | * | 0 | *       | 4      | 3      |

|               |                           | ER  | IM                     | 19    | _     |   |   |   |   |         | 4      | 3      |

| ADD dst, src  | $dst \gets dst + src$     | r   | r                      | 02    | *     | * | * | * | 0 | *       | 2      | 3      |

|               |                           | r   | lr                     | 03    | _     |   |   |   |   |         | 2      | 4      |

|               |                           | R   | R                      | 04    | _     |   |   |   |   |         | 3      | 3      |

|               |                           | R   | IR                     | 05    | _     |   |   |   |   |         | 3      | 4      |

|               |                           | R   | IM                     | 06    | _     |   |   |   |   |         | 3      | 3      |

|               |                           | IR  | IM                     | 07    | _     |   |   |   |   |         | 3      | 4      |

| ADDX dst, src | $dst \gets dst + src$     | ER  | ER                     | 08    | *     | * | * | * | 0 | *       | 4      | 3      |

|               |                           | ER  | IM                     | 09    |       |   |   |   |   |         | 4      | 3      |

Note: Flags Notation:

\* = Value is a function of the result of the operation.

– = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| Assembly      |                          | Add<br>Mo | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags | Fetch | Instr. |        |        |

|---------------|--------------------------|-----------|-------------|---------------|---|---|-----|-----|-------|--------|--------|--------|

| Mnemonic      | Symbolic Operation       | dst       | src         | (Hex)         | С | Ζ | S   | V   | D     | Н      | Cycles | Cycles |

| LD dst, rc    | $dst \gets src$          | r         | IM          | 0C-FC         | _ | _ | _   | -   | _     | _      | 2      | 2      |

|               |                          | r         | X(r)        | C7            | _ |   |     |     |       |        | 3      | 3      |

|               |                          | X(r)      | r           | D7            | _ |   |     |     |       |        | 3      | 4      |

|               |                          | r         | lr          | E3            | _ |   |     |     |       |        | 2      | 3      |

|               |                          | R         | R           | E4            | _ |   |     |     |       |        | 3      | 2      |

|               |                          | R         | IR          | E5            | _ |   |     |     |       |        | 3      | 4      |

|               |                          | R         | IM          | E6            | _ |   |     |     |       |        | 3      | 2      |

|               |                          | IR        | IM          | E7            | _ |   |     |     |       |        | 3      | 3      |

|               |                          | lr        | r           | F3            | _ |   |     |     |       |        | 2      | 3      |

|               |                          | IR        | R           | F5            | _ |   |     |     |       |        | 3      | 3      |

| LDC dst, src  | dst ← src                | r         | Irr         | C2            | _ | - | _   | -   | _     | _      | 2      | 5      |

|               |                          | lr        | Irr         | C5            | _ |   |     |     |       |        | 2      | 9      |

|               |                          | Irr       | r           | D2            | _ |   |     |     |       |        | 2      | 5      |

| LDCI dst, src | $dst \gets src$          | Ir        | Irr         | C3            | _ | _ | _   | _   | _     | _      | 2      | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr       | lr          | D3            | _ |   |     |     |       |        | 2      | 9      |

| LDE dst, src  | dst ← src                | r         | Irr         | 82            | _ | - | _   | -   | _     | -      | 2      | 5      |

|               |                          | Irr       | r           | 92            | _ |   |     |     |       |        | 2      | 5      |

| LDEI dst, src | dst ← src                | lr        | Irr         | 83            | _ | - | -   | -   | _     | -      | 2      | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr       | lr          | 93            | _ |   |     |     |       |        | 2      | 9      |

| LDWX dst, src | dst ← src                | ER        | ER          | 1FE8          | - | _ | _   | _   | _     | _      | 5      | 4      |

Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Assembly       |                                     | Add<br>Mc | ress<br>ode | Op<br>Code(s) |   |   | Fla | igs |   |   | Fetch  | Instr. |

|----------------|-------------------------------------|-----------|-------------|---------------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic       | Symbolic Operation                  | dst       | src         | (Hex)         | С | Ζ | S   | V   | D | Н | Cycles | Cycles |

| LDX dst, src   | dst ← src                           | r         | ER          | 84            | - | - | _   | -   | - | - | 3      | 2      |

|                |                                     | lr        | ER          | 85            | _ |   |     |     |   |   | 3      | 3      |

|                |                                     | R         | IRR         | 86            | _ |   |     |     |   |   | 3      | 4      |

|                |                                     | IR        | IRR         | 87            |   |   |     |     |   |   | 3      | 5      |

|                |                                     | r         | X(rr)       | 88            | _ |   |     |     |   |   | 3      | 4      |

|                |                                     | X(rr)     | r           | 89            |   |   |     |     |   |   | 3      | 4      |

|                |                                     | ER        | r           | 94            |   |   |     |     |   |   | 3      | 2      |

|                |                                     | ER        | lr          | 95            |   |   |     |     |   |   | 3      | 3      |

|                |                                     | IRR       | R           | 96            |   |   |     |     |   |   | 3      | 4      |

|                |                                     | IRR       | IR          | 97            |   |   |     |     |   |   | 3      | 5      |

|                |                                     | ER        | ER          | E8            |   |   |     |     |   |   | 4      | 2      |

|                |                                     | ER        | IM          | E9            |   |   |     |     |   |   | 4      | 2      |

| LEA dst, X(sro | c) dst   ← src + X                  | r         | X(r)        | 98            | - | - | -   | -   | _ | _ | 3      | 3      |

|                |                                     | rr        | X(rr)       | 99            |   |   |     |     |   |   | 3      | 5      |

| MULT dst       | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR        |             | F4            | _ | - | -   | -   | - | - | 2      | 8      |

| NOP            | No operation                        |           |             | 0F            | _ | _ | _   | -   | _ | - | 1      | 2      |

| OR dst, src    | $dst \gets dst \ OR \ src$          | r         | r           | 42            | _ | * | *   | 0   | _ | - | 2      | 3      |

|                |                                     | r         | lr          | 43            |   |   |     |     |   |   | 2      | 4      |

|                |                                     | R         | R           | 44            |   |   |     |     |   |   | 3      | 3      |

|                |                                     | R         | IR          | 45            |   |   |     |     |   |   | 3      | 4      |

|                |                                     | R         | IM          | 46            |   |   |     |     |   |   | 3      | 3      |

|                |                                     | IR        | IM          | 47            | _ |   |     |     |   |   | 3      | 4      |

| ORX dst, src   | $dst \gets dst \ OR \ src$          | ER        | ER          | 48            | _ | * | *   | 0   | - | _ | 4      | 3      |

|                |                                     | ER        | IM          | 49            | _ |   |     |     |   |   | 4      | 3      |

| POP dst        | dst ← @SP                           | R         |             | 50            | _ | - | -   | -   | - | - | 2      | 2      |

|                | $SP \leftarrow SP + 1$              | IR        |             | 51            | _ |   |     |     |   |   | 2      | 3      |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

Figure 32 displays the typical current con**stition** versus the systemlock frequency in NORMAL Mode.

Figure 32. I  $_{\rm CC}$  Versus System Clock Frequency (NORMAL Mode)

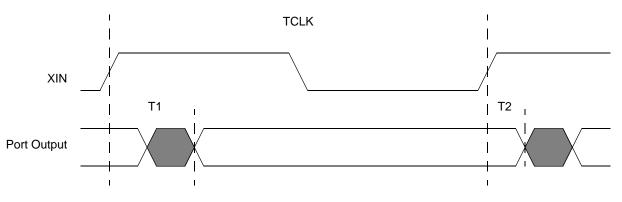

## General Purpose I/O Port Output Timing

Figure 34 and Table 125 provide timing information for the GPIO port pins.

Figure 34. GPIO Port Output Timing

|                |                                     | Dela    | ıy (ns) |  |  |  |  |  |  |

|----------------|-------------------------------------|---------|---------|--|--|--|--|--|--|

| Parameter      | Abbreviation                        | Minimum | Maximum |  |  |  |  |  |  |

| GPIO Port Pins |                                     |         |         |  |  |  |  |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | -       | 15      |  |  |  |  |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2       | _       |  |  |  |  |  |  |

#### Table 125. GPIO Port Output Timing

#### Hex Address: F09

#### Table 139. Timer 1 Low Byte Register (T1L)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|--|--|

| Field   |     | TL   |     |     |     |     |     |     |  |  |  |  |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 1   |  |  |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |  |

| Address |     | F09H |     |     |     |     |     |     |  |  |  |  |  |

#### Hex Address: F0A

#### Table 140. Timer 1 Reload High Byte Register (T1RH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|--|--|

| Field   |     | TRH  |     |     |     |     |     |     |  |  |  |  |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |  |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |  |

| Address |     | FOAH |     |     |     |     |     |     |  |  |  |  |  |

#### Hex Address: F0B

#### Table 141. Timer 1 Reload Low Byte Register (T1RL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   |      | TRL |     |     |     |     |     |     |  |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | FOBH |     |     |     |     |     |     |     |  |

#### Hex Address: F0C

#### Table 142. Timer 1 PWM High Byte Register (T1PWMH)

| Bit     | 7    | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------|------|-----|-----|-----|-----|-----|-----|--|

| Field   |      | PWMH |     |     |     |     |     |     |  |

| RESET   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | FOCH |      |     |     |     |     |     |     |  |

#### Hex Address: FC5

| Table 162. IRQ1 Enable Lo w Bit Register (IRQ1ENL) |  |

|----------------------------------------------------|--|

|                                                    |  |

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|--|--|

| Field   | PA7ENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |  |  |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |

| Address |        | FC5H    |        |        |               |        |        |        |  |  |

#### Hex Address: FC6

#### Table 163. Interrupt Request 2 Register (IRQ2)

| Bit     | 7        | 6   | 5   | 4   | 3    | 2    | 1    | 0    |  |

|---------|----------|-----|-----|-----|------|------|------|------|--|

| Field   | Reserved |     |     |     | PC3I | PC2I | PC1I | PC0I |  |

| RESET   | 0        | 0   | 0   | 0   | 0    | 0    | 0    | 0    |  |

| R/W     | R/W      | R/W | R/W | R/W | R/W  | R/W  | R/W  | R/W  |  |

| Address | FC6H     |     |     |     |      |      |      |      |  |

### Hex Address: FC7

#### Table 164. IRQ2 Enable Hi gh Bit Register (IRQ2ENH)

| Bit     | 7        | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|---------|----------|-----|-----|-----|-------|-------|-------|-------|

| Field   | Reserved |     |     |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET   | 0        | 0   | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| Address | FC7H     |     |     |     |       |       |       |       |

#### Hex Address: FC8

#### Table 165. IRQ2 Enable Lo w Bit Register (IRQ2ENL)

| Bit     | 7        | 6    | 5   | 4   | 3     | 2     | 1     | 0     |  |

|---------|----------|------|-----|-----|-------|-------|-------|-------|--|

| Field   | Reserved |      |     |     | C3ENL | C2ENL | C1ENL | C0ENL |  |

| RESET   | 0        | 0    | 0   | 0   | 0     | 0     | 0     | 0     |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   |  |

| Address |          | FC8H |     |     |       |       |       |       |  |