Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0230ph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

29

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                                                                                                                                                                              | 5   | 4   | 3  | 2    | 1     | 0 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|------|-------|---|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                           | STOP                                                                                                                                                                                                           | WDT | EXT |    | Rese | erved | · |

| RESET       | :                                                                                                                                                                                                                                                                                                                                                                                                                                             | See Table 13                                                                                                                                                                                                   | 3   | 0   | 0  | 0    | 0     | 0 |

| R/W         | R                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                                                                                                                                                                              | R   | R   | R  | R    | R     | R |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                |     | FF  | ОH |      |       |   |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                    | n                                                                                                                                                                                                              |     |     |    |      |       |   |

| [7]<br>POR  | This bit is s                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>Power-On Reset Indicator</b><br>This bit is set to 1 if a Power-On Reset event occurs and is reset to 0, if a WDT time-out or Stop<br>Mode Recovery occurs. Reading this register also reset this bit to 0. |     |     |    |      |       |   |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>This bit is set to 1 if a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery is not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |                                                                                                                                                                                                                |     |     |    |      |       |   |

| [5]<br>WDT  | Watchdog Timer Time-Out Indicator<br>This bit is set to 1 if a WDT time-out occurs. A Power-On Reset resets this pin. A Stop Mode<br>Recovery from a change in an input pin also resets this bit. Reading this register resets this bit.<br>This read must occur before clearing the WDT interrupt.                                                                                                                                           |                                                                                                                                                                                                                |     |     |    |      |       |   |

| [4]<br>EXT  | <b>External Reset Indicator</b><br>If this bit is set to 1, a reset initiated by the external RESET pin occurred. A Power-On Reset or<br>a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                                                                                                                                                                        |                                                                                                                                                                                                                |     |     |    |      |       |   |

| [3:0]       | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000.                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                |     |     |    |      |       |   |

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out                 | 0   | 1    | 1   | 0   |

PA0 and PA6 contain two different Timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the TIMER mode. For more details, see the <u>Timers</u> chapter on page 68.

## **Direct LED Drive**

The Port C pins provide a sinked current output, capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels, 3mA, 7mA, 13mA and 20mA. This mode is enabled through the LED Control registers.

For proper function, the LED anode must be connected to  $V_{\rm DD}$  and the cathode to the GPIO pin.

Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See the <u>Electrical Characteristics</u> chapter on page 184 for the maximum total current for the applicable package.

## Shared Reset Pin

On the 20- and 28-pin devices, the Port D0 pin shares function with a bidirectional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bidirectional input/output open-drain reset with an internal pull-up until the user software reconfigures it as a GPIO PD0. When in GPIO mode, the Port D0 pin functions as output only, and must be configured as an output. PD0 supports the high drive feature, but not the stop-mode recovery feature.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, the pins PA0 and PA1 are connected to the crystal. When the crystal oscillator is enabled, the GPIO settings are overridden and PA0 and PA1 are disabled. See the <u>Oscillator Control Register Definitions</u> section on page 154.

## **5V Tolerance**

In the 20- and 28-pin versions of this device, any pin, which shares functionality with an ADC, crystal or comparator port is not 5V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5V-tolerant and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled, but with excess power consumption on pull-up resistor.

| Port                | Pin | Mnemonic              | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-----------------------|--------------------------------|-----------------------------------------|

| Port B <sup>2</sup> | PB0 | Reserved              |                                | AFS1[0]: 0                              |

|                     |     | ANA0                  | ADC analog input               | AFS1[0]: 1                              |

|                     | PB1 | Reserved              |                                | AFS1[1]: 0                              |

|                     |     | ANA1 ADC analog input |                                | AFS1[1]: 1                              |

|                     | PB2 | Reserved              |                                | AFS1[2]: 0                              |

|                     |     | ANA2                  | ADC analog input               | AFS1[2]: 1                              |

|                     | PB3 | CLKIN                 | External input clock           | AFS1[3]: 0                              |

|                     |     | ANA3                  | ADC analog input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved              |                                | AFS1[4]: 0                              |

|                     |     | ANA7                  | ADC analog input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved              |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub>      | ADC reference voltage          | AFS1[5]: 1                              |

| PB6<br>PB7          | PB6 | Reserved              |                                | AFS1[6]: 0                              |

|                     |     | Reserved              |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved              |                                | AFS1[7]: 0                              |

|                     |     | Reserved              |                                | AFS1[7]: 1                              |

#### Table 16. Port Alternate Function Mapping (Continued)

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

# Port A–D Address Registers

The Port A–D Address registers select the GPIO port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO port controls; see Tables 18 and 19.

| <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W | Bit     | 7                      | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------------|---------|------------------------|------------|-----|-----|-----|-----|-----|-----|

| <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W | Field   |                        | PADDR[7:0] |     |     |     |     |     |     |

|                                        | RESET   |                        | 00H        |     |     |     |     |     |     |

| Address FD0H, FD4H, FD8H, FDCH         | R/W     | R/W                    | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

|                                        | Address | FD0H, FD4H, FD8H, FDCH |            |     |     |     |     |     |     |

## Table 18. Port A–D GPIO Address Registers (PxADDR)

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The port address selects one of the subregisters accessible through the Port Control Register. |

#### Table 19. Port Control Subregister Access

| PADDR[7:0] | Port Control Subregister accessible using the Port A–D Control registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental port reconfiguration. |

| 01H        | Data Direction                                                                 |

| 02H        | Alternate Function                                                             |

| 03H        | Output Control (open-drain)                                                    |

| 04H        | High Drive Enable                                                              |

| 05H        | Stop Mode Recovery Source Enable                                               |

| 06H        | Pull-Up Enable                                                                 |

| 07H        | Alternate Function Set 1                                                       |

| 08H        | Alternate Function Set 2                                                       |

| 09H–FFH    | No function                                                                    |

## Port A–D Alternate Function Subregisters

The Port A–D Alternate Function Subregister is accessed through the Port A–D Control Register by writing 02H to the Port A–D Address Register. See Table 22 on page 42. The Port A–D Alternate Function subregisters enable the alternate function selection on pins. If disabled, the pins function as GPIOs. If enabled, select one of four alternate functions using Alternate Function Set subregisters 1 and 2, as described in the the <u>Port A–D Alternate Function</u> <u>Set 1 Subregisters</u> section on page 47 and the <u>Port A–D Alternate Function</u> <u>Set 2 Subregisters</u> section on page 48. See the <u>GPIO Alternate Functions</u> section on page 34 to determine the alternate functions associated with each port pin.

**Caution:** Do not enable alternate functions for GPIO port pins for which there is no associated Alternate function. Failure to follow this guideline can result in unpredictable operation.

| Bit     | 7                              | 6                                                                                                                                 | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| Field   | AF7                            | AF6                                                                                                                               | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |

| RESET   |                                | 00H (Ports A–C); 01H (Port D)                                                                                                     |     |     |     |     |     |     |

| R/W     |                                | R/W                                                                                                                               |     |     |     |     |     |     |

| Address | If 02H in F                    | If 02H in Port A–D Address Register, then accessible through the Port A–D Control Register                                        |     |     |     |     |     |     |

| Bit     | Description                    | Description                                                                                                                       |     |     |     |     |     |     |

| [7:0]   | Port Alternate Function Enable |                                                                                                                                   |     |     |     |     |     |     |

| AFx     | •                              | D = The port pin is in NORMAL Mode and the DDx bit in the Port A-D Data Direction Subregistor determines the direction of the pin |     |     |     |     |     |     |

Table 22. Port A–D Alternate Function Subregisters (PxAF)

ter determines the direction of the pin. 1 = The alternate function selected through Alternate function set subregisters is enabled. Port

= The alternate function selected through Alternate function set subregisters is enabled. Port pin operation is controlled by the Alternate function.

Note: x indicates the specific GPIO port pin number (7-0).

# LED Drive Enable Register

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|---------|-----|-----|-----|------|--------|-----|-----|-----|

| Field   |     |     |     | LEDE | N[7:0] |     |     |     |

| RESET   | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Address |     |     |     | F8   | 2H     |     |     |     |

| Bit   | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | LED Drive Enable                                                                                                                                                           |

| LEDEN | These bits determine which Port C pins are connected to an internal current sink.<br>0 = Tristate the Port C pin.<br>1= Connect controlled current sink to the Port C pin. |

# LED Drive Level High Register

The LED Drive Level High Register, shown in Table 32, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|--------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | LEDLVLH[7:0] |     |     |     |     |     |     |  |  |  |

| RESET   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     |              |     | F8  | 3H  |     |     |     |  |  |  |

#### Bit Description

[7:0] LED Level High Bits

LEDLVLH {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3mA.

01= 7 mA.

10= 13mA.

11= 20mA.

# Interrupt Controller

The Interrupt Controller on the Z8 Encore!<sup>®</sup> F0830 Series products prioritize the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the Interrupt Controller include:

- Seventeen interrupt sources using sixteen unique interrupt vectors:

- Twelve GPIO port pin interrupt sources

- Five on-chip peripheral interrupt sources (Comparator Output interrupt shares one interrupt vector with PA6)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt m

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the Interrupt Controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU User Manual (UM0128)</u>, which is available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 34 lists the interrupts available in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even program memory address and the least significant byte (LSB) at the odd program memory address.

**Note:** Some port interrupts are not available on the 20-pin and 28-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

113

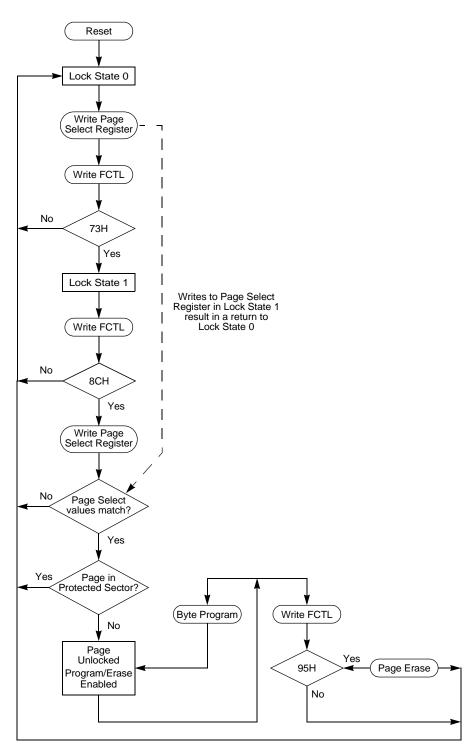

Figure 19. Flash Controller Operation Flow Chart

# **Option Bit Types**

This section describes the two types of Flash option bits offered in the F0830 Series.

## **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits is provided because these locations contain application specific device configurations. The information contained here is lost when page 0 of program memory is erased.

## **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered by the user. Program memory can be erased without endangering these values. It is possible to alter working values of these bits by accessing the trim bit address and data registers, but these working values are lost after a power loss.

There are 32 bytes of trim data. To modify one of these values, the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20–3F only. The remaining information page is not accessible via the Trim Bit Address and Data registers.

During reset, the first 43 system clock cycles perform 43 Flash accesses. The six bits of the counter provide the lower six bits of the Flash memory address. All other address bits are set to 0. The option bit registers use the 6-bit address from the counter as an address and latch the data from the Flash on the positive edge of the IPO clock, allowing for a maximum of 344-bits (43 bytes) of option information to be read from Flash.

Because option information is stored in both the first two bytes of program memory and in the information area of Flash memory, the data must be placed in specific locations to be read correctly. In this case, the first two bytes at addresses 0 and 1 in program memory are read out and the remainder of the bytes are read out of the Flash information area.

## **Byte Read**

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine ( $0 \times 2000$ ). At the return from the subroutine, the read byte resides in working register R0 and the read status byte resides in working register R1. The bit fields of this status byte are defined in Table 92. Additionally, the user code should pop the address byte off the stack.

The read routine uses 16 bytes of stack space in addition to the one byte of address pushed by the user code. Sufficient memory must be available for this stack usage.

Due to the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between  $71 \mu s$  and  $258 \mu s$  (assuming a 20MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return  $0 \times ff$ . Illegal read operations have a  $6 \mu s$  execution time.

The status byte returned by the NVDS read routine is zero for a successful read. If the status byte is nonzero, there is a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have an error.

| Bit              | 7         6         5         4         3         2         1         0                                                                                                                                                        |                                                                           |             |            |      |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------|------------|------|--|--|--|--|--|--|--|

| Field            | Reserved DE Reserved FE IGADDR Reserved                                                                                                                                                                                        |                                                                           |             |            |      |  |  |  |  |  |  |  |

| Default<br>Value | 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                              |                                                                           |             |            |      |  |  |  |  |  |  |  |

| Bit              | Description                                                                                                                                                                                                                    |                                                                           |             |            |      |  |  |  |  |  |  |  |

| [7:5]            | Reserved<br>These bits a                                                                                                                                                                                                       | <b>Reserved</b><br>These bits are reserved and must be programmed to 000. |             |            |      |  |  |  |  |  |  |  |

| [4]<br>DE        | <b>Data Error</b><br>When reading an NVDS address, if an error is found in the latest data corresponding to this NVDS address, this bit is set to 1. NVDS source code steps forward until it finds valid data at this address. |                                                                           |             |            |      |  |  |  |  |  |  |  |

| [3]              | Reserved<br>This bit is re                                                                                                                                                                                                     | eserved and                                                               | must be pro | ogrammed t | o 0. |  |  |  |  |  |  |  |

| [2]<br>FE        | Flash Error<br>If a Flash error is detected, this bit is set to 1.                                                                                                                                                             |                                                                           |             |            |      |  |  |  |  |  |  |  |

| [1]<br>IGADDR    | <b>Illegal Address</b><br>When NVDS byte reads from invalid addresses (those exceeding the NVDS array size) occur, this bit is set to 1.                                                                                       |                                                                           |             |            |      |  |  |  |  |  |  |  |

| [0]              | Reserved<br>This bit is reserved and must be programmed to 0.                                                                                                                                                                  |                                                                           |             |            |      |  |  |  |  |  |  |  |

Table 92. Read Status Byte

| Clock Source                          | Characteristics                                                                                                                                | Required Setup                                                                                                                                                                                                                                                                                      |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal precision<br>RC oscillator   | <ul> <li>32.8 kHz or 5.53MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>                           | <ul> <li>Unlock and write to the Oscillator Con-<br/>trol Register (OSCCTL) to enable and<br/>select oscillator at either 5.53MHz or<br/>32.8 kHz</li> </ul>                                                                                                                                        |

| External crystal/res-<br>onator       | <ul> <li>32 kHz to 20MHz</li> <li>Very high accuracy (dependent on crystal or resonator used)</li> <li>Requires external components</li> </ul> | <ul> <li>Configure Flash option bits for correct<br/>external OSCILLATOR Mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator, wait for it to stabilize<br/>and select as system clock (if the<br/>XTLDIS option bit has been<br/>de-asserted, no waiting is required)</li> </ul> |

| External RC oscilla-<br>tor           | <ul> <li>32 kHz to 4MHz</li> <li>Accuracy dependent on external components</li> </ul>                                                          | <ul> <li>Configure Flash option bits for correct<br/>external OSCILLATOR Mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator and select as system<br/>clock</li> </ul>                                                                                                           |

| External clock drive                  | <ul> <li>0 to 20MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul>                                                                                     |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Low power consumption</li> </ul>                     | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT oscillator is operating.</li> <li>Unlock and write to the Oscillator Con-<br/>trol Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>                                                                                       |

#### Table 98. Oscillator Configuration and Selection

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a nonfunctioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

#### **OSC Control Register Unlocking/Locking**

To write the Oscillator Control Register, unlock it by making two writes to the OSCCTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a Locked state. Any other sequence of Oscillator Control Register writes have no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

# **Internal Precision Oscillator**

The Internal Precision Oscillator (IPO) is designed for use without external components. The user can either manually trim the oscillator for a nonstandard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency with  $\pm 4\%$  accuracy and 45%~55% duty cycle over the operating temperature and supply voltage of the device. The maximum start-up time of the IPO is 25µs. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8kHz (contains both a FAST and a SLOW mode)

- Trimming possible through Flash option bits, with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

## Operation

The internal oscillator is an RC relaxation oscillator with a minimized sensitivity to power supply variations. By using ratio-tracking thresholds, the effect of power supply voltage is cancelled out. The dominant source of oscillator error is the absolute variance of chip-level fabricated components, such as capacitors. An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed, the oscillator frequency is stable and does not require subsequent calibration. Trimming was performed during manufacturing and is not necessary for the user to repeat unless a frequency other than 5.53 MHz (FAST mode) or 32.8 kHz (SLOW mode) is required.

**Note:** The user can power down the IPO block for minimum system power.

By default, the oscillator is configured through the Flash option bits. However, the user code can override these trim values, as described in *the* <u>Trim Bit Address Space</u> section on page 129.

Select one of two frequencies for the oscillator: 5.53 MHz or 32.8 kHz, using the OSCSEL bits described in the <u>Oscillator Control</u> chapter on page 151.

| Assembly         |                                                                                           | Address<br>Mode |     | Op<br>Code(s) | Flags |   |   |   |   | Fetch | Instr. |   |

|------------------|-------------------------------------------------------------------------------------------|-----------------|-----|---------------|-------|---|---|---|---|-------|--------|---|

| Mnemonic         | Symbolic Operation                                                                        | dst             | src | (Hex)         | С     | Ζ | S | ۷ | D | Н     |        |   |

| AND dst, src     | $dst \gets dst \; AND \; src$                                                             | r               | r   | 52            | _     | * | * | 0 | _ | _     | 2      | 3 |

|                  |                                                                                           | r               | lr  | 53            | _     |   |   |   |   |       | 2      | 4 |

|                  |                                                                                           | R               | R   | 54            |       |   |   |   |   |       | 3      | 3 |

|                  |                                                                                           | R               | IR  | 55            | _     |   |   |   |   |       | 3      | 4 |

|                  |                                                                                           | R               | IM  | 56            | _     |   |   |   |   |       | 3      | 3 |

|                  |                                                                                           | IR              | IM  | 57            | _     |   |   |   |   |       | 3      | 4 |

| ANDX dst, src    | $dst \gets dst \; AND \; src$                                                             | ER              | ER  | 58            | _     | * | * | 0 | _ | _     | 4      | 3 |

|                  |                                                                                           | ER              | IM  | 59            | _     |   |   |   |   |       | 4      | 3 |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |                 |     | 2F            | -     | _ | _ | _ | _ | _     | 1      | 2 |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r               |     | E2            | _     | * | * | 0 | _ | _     | 2      | 2 |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r               |     | E2            | _     | * | * | 0 | _ | _     | 2      | 2 |

| BRK              | Debugger Break                                                                            |                 |     | 00            | -     | _ | - | - | _ | _     | 1      | 1 |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r               |     | E2            | -     | * | * | 0 | - | -     | 2      | 2 |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R               |     | D5            | Х     | * | * | 0 | - | -     | 2      | 2 |

| BTJ p, bit, src, | if src[bit] = p                                                                           |                 | r   | F6            | -     | _ | - | - | _ | _     | 3      | 3 |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7            | _     |   |   |   |   |       | 3      | 4 |

| BTJNZ bit, src,  |                                                                                           |                 | r   | F6            | -     | - | - | - | - | -     | 3      | 3 |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7            | _     |   |   |   |   |       | 3      | 4 |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |                 | r   | F6            | _     | - | _ | _ | - | -     | 3      | 3 |

| dst              | $PC \gets PC + X$                                                                         |                 | Ir  | F7            |       |   |   |   |   |       | 3      | 4 |

| CALL dst         | $SP \leftarrow SP -\!\!\!\!\!-\!\!\!\!\!2$                                                | IRR             |     | D4            | _     | _ | - | - | _ | -     | 2      | 6 |

|                  | @SP ← PC<br>PC ← dst                                                                      | DA              |     | D6            |       |   |   |   |   |       | 3      | 3 |

| CCF              | $C \leftarrow \sim C$                                                                     |                 |     | EF            | *     | _ | _ | _ | _ |       | 1      | 2 |

## Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# **On-Chip Debugger Timing**

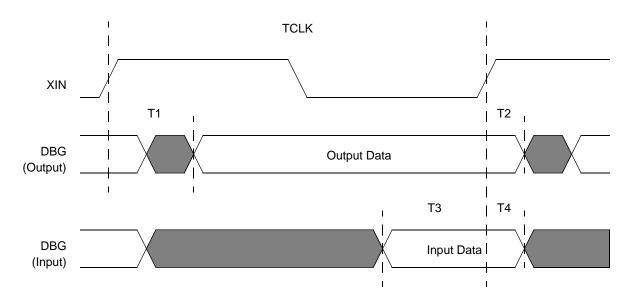

Figure 35 and Table 126 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

| Figure 35. On-Chip Debugger Timing | Figure 35. | <b>On-Chip</b> | Debugger | Timing |

|------------------------------------|------------|----------------|----------|--------|

|------------------------------------|------------|----------------|----------|--------|

|                |                                  | Delay (ns) |         |  |

|----------------|----------------------------------|------------|---------|--|

| Parameter      | Abbreviation                     | Minimum    | Maximum |  |

| DBG            |                                  |            |         |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | _          | 15      |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | _       |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5          | _       |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _       |  |

## Hex Address: F0D

#### Table 143. Timer 1 PWM Low Byte Register (T1PWML)

| Bit     | 7    | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|------|------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   | PWML |      |     |     |     |     |     |     |  |  |  |

| RESET   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |      | FODH |     |     |     |     |     |     |  |  |  |

## Hex Address: F0E

#### Table 144. Timer 1 Control Register 0 (T1CTL0)

| Bit     | 7       | 6    | 5    | 4        | 3    | 2   | 1   | 0      |  |  |

|---------|---------|------|------|----------|------|-----|-----|--------|--|--|

| Field   | TMODEHI | TICO | NFIG | Reserved | PWMD |     |     | INPCAP |  |  |

| RESET   | 0       | 0    | 0    | 0        | 0    | 0   | 0   | 0      |  |  |

| R/W     | R/W     | R/W  | R/W  | R/W      | R/W  | R/W | R/W | R/W    |  |  |

| Address |         | F0EH |      |          |      |     |     |        |  |  |

## Hex Address: F0F

#### Table 145. Timer 1 Control Register 1 (T1CTL1)

| Bit     | 7   | 6    | 5    | 4   | 3   | 2     | 1   | 0   |  |

|---------|-----|------|------|-----|-----|-------|-----|-----|--|

| Field   | TEN | TPOL | PRES |     |     | TMODE |     |     |  |

| RESET   | 0   | 0    | 0    | 0   | 0   | 0     | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W  | R/W | R/W | R/W   | R/W | R/W |  |

| Address |     | FOFH |      |     |     |       |     |     |  |

## Hex Addresses: F10–F6F

This address range is reserved.

## Hex Address: FDB

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | FDBH  |       |       |       |       |       |       |       |

#### Hex Address: FDC

#### Table 181. Port D GPIO Address Register (PDADDR)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PADDR[7:0] |     |     |     |     |     |     |     |

| RESET   | 00H        |     |     |     |     |     |     |     |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FDCH       |     |     |     |     |     |     |     |

## Hex Address: FDD

#### Table 182. Port D Control Registers (PDCTL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PCTL |     |     |     |     |     |     |     |

| RESET   | 00H  |     |     |     |     |     |     |     |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FDDH |     |     |     |     |     |     |     |

#### Hex Address: FDE

This address range is reserved.

# Index

## **Symbols**

@ 165# 165% 165

## **Numerics**

10-bit ADC 4

## Α

absolute maximum ratings 184 AC characteristics 189 ADC 166 block diagram 99 overview 98 ADC Channel Register 1 (ADCCTL) 102 ADC Data High Byte Register (ADCDH) 103 ADC Data Low Bit Register (ADCDL) 103, 104, 105 **ADCX 166** ADD 166 add - extended addressing 166 add with carry 166 add with carry - extended addressing 166 additional symbols 165 address space 14 **ADDX 166** analog block/PWM signal synchronization 100 analog block/PWM signal zynchronization 100 analog signals 11 analog-to-digital converter overview 98 AND 169 **ANDX 169** architecture voltage measurements 98 arithmetic instructions 166 assembly language programming 162 assembly language syntax 163

## В

B 165 b 164 **BCLR 167** binary number suffix 165 BIT 167 bit 164 clear 167 manipulation instructions 167 set 167 set or clear 167 swap 167 test and jump 169 test and jump if non-zero 169 test and jump if zero 169 bit jump and test if non-zero 166 bit swap 169 block diagram 3 block transfer instructions 167 **BRK 169 BSET 167** BSWAP 167. 169 **BTJ** 169 BTJNZ 166, 169 **BTJZ 169**

# С

calibration and compensation, motor control measurements 101 CALL procedure 169 capture mode 89, 90 capture/compare mode 89 cc 164 CCF 168 characteristics, electrical 184 clear 168 CLR 168 COM 169 compare 89

232

compare - extended addressing 166 compare mode 89 compare with carry 166 compare with carry - extended addressing 166 complement 169 complement carry flag 167, 168 condition code 164 continuous mode 89 Control Registers 14, 17 counter modes 89 CP 166 CPC 166 **CPCX 166** CPU and peripheral overview 4 CPU control instructions 168 CPX 166 current measurement architecture 98 operation 99 Customer Feedback Form 239 Customer Information 239

# D

DA 164, 166 data memory 16 DC characteristics 185 debugger, on-chip 139 **DEC 166** decimal adjust 166 decrement 166 decrement and jump non-zero 169 decrement word 166 **DECW 166** destination operand 165 device, port availability 33 DI 168 direct address 164 disable interrupts 168 **DJNZ 169** dst 165

## Ε

EI 168 electrical characteristics 184 GPIO input data sample timing 195 watch-dog timer 194 electrical noise 98 enable interrupt 168 ER 164 extended addressing register 164 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 166 eZ8 CPU instruction notation 164 eZ8 CPU instruction set 162 eZ8 CPU instruction summary 171

# F

FCTL register 119, 126, 127, 228 features, Z8 Encore! 1 first opcode map 182 FLAGS 165 flags register 165 flash controller 4 option bit address space 127 option bit configuration - reset 124 program memory address 0000H 127 program memory address 0001H 128 flash memory 108 byte programming 116 code protection 114 configurations 108 control register definitions 118, 126 controller bypass 117 flash control register 119, 126, 127, 228 flash option bits 115 flash status register 120 flow chart 113 frequency high and low byte registers 123 mass erase 117 operation 112 operation timing 114 page erase 117

page select register 121, 122 FPS register 121, 122 FSTAT register 120

## G

gated mode 89 general-purpose I/O 33 GPIO 4.33 alternate functions 34 architecture 34 control register definitions 39 input data sample timing 195 interrupts 39 port A-C pull-up enable sub-registers 46, 47, 48 port A-H address registers 40 port A-H alternate function sub-registers 42 port A-H control registers 41 port A-H data direction sub-registers 41 port A-H high drive enable sub-registers 44 port A-H input data registers 49 port A-H output control sub-registers 43 port A-H output data registers 50, 51 port A-H stop mode recovery sub-registers 45 port availability by device 33 port input timing 195 port output timing 196

## Η

H 165 HALT 168 halt mode 31, 168 hexadecimal number prefix/suffix 165

##

IM 164 immediate data 164 immediate operand prefix 165 INC 166 increment 166 increment word 167 INCW 167 indexed 165 indirect address prefix 165 indirect register 164 indirect register pair 164 indirect working register 164 indirect working register pair 164 instruction set, ez8 CPU 162 instructions ADC 166 **ADCX 166** ADD 166 **ADDX 166** AND 169 **ANDX 169** arithmetic 166 **BCLR 167** BIT 167 bit manipulation 167 block transfer 167 **BRK 169 BSET 167** BSWAP 167, 169 BTJ 169 BTJNZ 166, 169 **BTJZ 169 CALL 169** CCF 167, 168 CLR 168 COM 169 CP 166 **CPC 166 CPCX 166** CPU control 168 CPX 166 DA 166 **DEC 166 DECW 166** DI 168 **DJNZ 169** EI 168 **HALT 168 INC 166 INCW 167 IRET 169**