# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-VQFN Exposed Pad                                       |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0230qh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

## xvi

| Table 119. | Flash Memory Electrical Characteristics and Timing 192                |

|------------|-----------------------------------------------------------------------|

| Table 120. | Watchdog Timer Electrical Characteristics and Timing 192              |

| Table 121. | Nonvolatile Data Storage                                              |

| Table 122. | Analog-to-Digital Converter Electrical Characteristics and Timing 193 |

| Table 123. | Comparator Electrical Characteristics                                 |

| Table 124. | GPIO Port Input Timing                                                |

| Table 125. | GPIO Port Output Timing 196                                           |

| Table 126. | On-Chip Debugger Timing 197                                           |

| Table 127. | Power Consumption Reference Table                                     |

| Table 128. | Z8 Encore! XP F0830 Series Ordering Matrix                            |

| Table 129. | Package and Pin Count Description 207                                 |

| Table 130. | Timer 0 High Byte Register (T0H) 208                                  |

| Table 131. | Timer 0 Low Byte Register (T0L) 209                                   |

| Table 132. | Timer 0 Reload High Byte Register (T0RH) 209                          |

| Table 133. | Timer 0 Reload Low Byte Register (T0RL)                               |

| Table 134. | Timer 0 PWM High Byte Register (T0PWMH) 209                           |

| Table 135. | Timer 0 PWM Low Byte Register (T0PWML) 210                            |

| Table 136. | Timer 0 Control Register 0 (T0CTL0)                                   |

| Table 137. | Timer 0 Control Register 1 (T0CTL1)                                   |

| Table 138. | Timer 1 High Byte Register (T1H) 210                                  |

| Table 139. | Timer 1 Low Byte Register (T1L) 211                                   |

| Table 140. | Timer 1 Reload High Byte Register (T1RH) 211                          |

| Table 141. | Timer 1 Reload Low Byte Register (T1RL)                               |

| Table 142. | Timer 1 PWM High Byte Register (T1PWMH) 211                           |

| Table 143. | Timer 1 PWM Low Byte Register (T1PWML)                                |

| Table 144. | Timer 1 Control Register 0 (T1CTL0)                                   |

| Table 145. | Timer 1 Control Register 1 (T1CTL1)                                   |

| Table 146. | ADC Control Register 0 (ADCCTL0)                                      |

| Table 147. | ADC Data High Byte Register (ADCD_H) 214                              |

| Table 148. | ADC Data Low Bits Register (ADCD_L) 214                               |

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

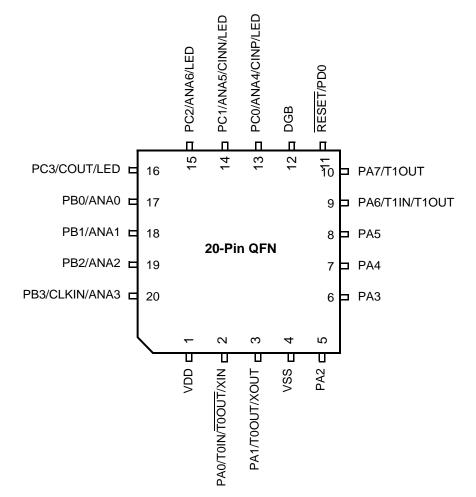

Figure 4. Z8F0830 Series in 20-Pin QFN Package

9

### 13

# **Pin Characteristics**

Table 5 provides detailed characteristics of each pin available on the Z8 Encore! F0830 Series 20- and 28-pin devices. Data in Table 5 are sorted alphabetically by the pin symbol mnemonic.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                      | Active<br>Low or<br>Active<br>High | Tristate<br>Output   | Internal<br>Pull-Up or<br>Pull-Down                  | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance |

|--------------------|-----------|-----------------------------------------|------------------------------------|----------------------|------------------------------------------------------|------------------------------|------------------------------------------------------|-----------------|

| AV <sub>DD</sub>   | N/A       | N/A                                     | N/A                                | N/A                  | N/A                                                  | N/A                          | N/A                                                  | N/A             |

| AV <sub>SS</sub>   | N/A       | N/A                                     | N/A                                | N/A                  | N/A                                                  | N/A                          | N/A                                                  | NA              |

| DBG                | I/O       | I                                       | N/A                                | Yes                  | No                                                   | Yes                          | Yes                                                  | Yes             |

| PA[7:0]            | I/O       | Ι                                       | N/A                                | Yes                  | Programma-<br>ble pull-up                            | Yes                          | Yes,<br>Programma-<br>ble                            | PA[7:2]<br>only |

| PB[7:0]            | I/O       | I                                       | N/A                                | Yes                  | Programma-<br>ble pull-up                            | Yes                          | Yes,<br>Programma-<br>ble                            | PB[7:6]<br>only |

| PC[7:0]            | I/O       | Ι                                       | N/A                                | Yes                  | Programma-<br>ble pull-up                            | Yes                          | Yes,<br>Programma-<br>ble                            | PC[7:3]<br>only |

| RESET/PD0          | I/O       | I/O<br>(defaults<br><u>to</u><br>RESET) | Low (in<br>RESET<br>mode)          | Yes<br>(PD0<br>only) | Programma-<br>ble for PD0;<br>always on<br>for RESET | Yes                          | Programma-<br>ble for PD0;<br>always on<br>for RESET | Yes             |

| V <sub>DD</sub>    | N/A       | N/A                                     | N/A                                | N/A                  |                                                      |                              | N/A                                                  | N/A             |

| V <sub>SS</sub>    | N/A       | N/A                                     | N/A                                | N/A                  |                                                      |                              | N/A                                                  | N/A             |

#### Table 5. Pin Characteristics (20- and 28-pin Devices)

**Note:** PB6 and PB7 are available only in devices without an ADC function.

The eZ8 CPU fetches the reset vector at program memory addresses 0002H and 0003H and loads that value into the program counter. Program execution begins at the reset vector address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 11 lists the Stop Mode Recovery sources and resulting actions. The following sections provide more details about each of the Stop Mode Recovery sources.

| Operating<br>Mode | Stop Mode Recovery Source                                                   | Action                                                               |  |  |

|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| STOP Mode         | Watchdog Timer time-out when configured for Reset                           | Stop Mode Recovery                                                   |  |  |

|                   | Watchdog Timer time-out when configured for interrupt                       | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |  |  |

|                   | Data transition on any GPIO port pin enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |  |  |

|                   | Assertion of external RESET Pin                                             | System reset                                                         |  |  |

|                   | Debug pin driven Low                                                        | System reset                                                         |  |  |

#### Table 11. Stop Mode Recovery Sources and Resulting Action

## Stop Mode Recovery using WDT Time-Out

If the Watchdog Timer times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) Register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! F0830 Series device is configured to respond to interrupts, the eZ8 CPU services the WDT interrupt request following the normal Stop Mode Recovery sequence.

## **Stop Mode Recovery using GPIO Port Pin Transition**

Each of the GPIO port pins may be configured as a Stop Mode Recovery input source. If any GPIO pin is enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery. In the Reset Status (RSTSTAT) Register, the STOP bit is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. These Port Input Data registers record the port transition only if the signal stays on the port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin).

## Port A–D Pull-up Enable Subregisters

The Port A–D Pull-Up Enable Subregister is accessed through the Port A–D Control Register by writing 06H to the Port A–D Address Register. See Table 26. Setting the bits in the Port A–D Pull-Up Enable subregisters enables a weak internal resistive pull-up on the specified port pins.

| Bit     | 1                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | PPUE7                                                                                 | PPUE6 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |       |  |

#### Table 26. Port A–D Pull-Up Enable Subregisters (PxPUE)

| Bit       | Description                                       |

|-----------|---------------------------------------------------|

| [7:0]     | Port Pull-Up Enable                               |

| PxPUE     | 0 = The weak pull-up on the port pin is disabled. |

|           | 1 = The weak pull-up on the port pin is enabled.  |

| Note: x i | ndicates the specific GPIO port pin number (7–0). |

# LED Drive Enable Register

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | LEDEN[7:0] |     |     |     |     |     |     |  |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F82H       |     |     |     |     |     |     |  |

| Bit   | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | LED Drive Enable                                                                                                                                                           |

| LEDEN | These bits determine which Port C pins are connected to an internal current sink.<br>0 = Tristate the Port C pin.<br>1= Connect controlled current sink to the Port C pin. |

# LED Drive Level High Register

The LED Drive Level High Register, shown in Table 32, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7            | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|--------------|------|-----|-----|-----|-----|-----|-----|--|--|

| Field   | LEDLVLH[7:0] |      |     |     |     |     |     |     |  |  |

| RESET   | 0            | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W          | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |              | F83H |     |     |     |     |     |     |  |  |

## Bit Description

[7:0] LED Level High Bits

LEDLVLH {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3mA.

01= 7 mA.

10= 13mA.

11= 20mA.

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7    | 6    | 5 | 4 | 3        | 2 | 1 | 0 |  |

|---------|------|------|---|---|----------|---|---|---|--|

| Field   | IRQE |      |   |   | Reserved |   |   |   |  |

| RESET   | 0    | 0    | 0 | 0 | 0        | 0 | 0 | 0 |  |

| R/W     | R/W  | R    | R | R | R        | R | R | R |  |

| Address |      | FCFH |   |   |          |   |   |   |  |

|         |      |      |   |   |          |   |   |   |  |

## Table 49. Interrupt Control Register (IRQCTL)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by executing an Enable Interrupts (EI) or Interrupt Return (IRET) instruction or by a direct register write of 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset, or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                                                                                                            |

reload. For the timer output to make a state change at a ONE-SHOT time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode

- Set the prescale value

- Set the initial output level (High or Low) if using the timer output Alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

One-Shot Mode Time-Out Period (s) =  $\frac{(\text{Reload Value} - \text{Start Value}) \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and for initiating the count:

1. Write to the Timer Control Register to:

## 73

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer reload in COMPARATOR COUNTER Mode, counting always begins at the reset value 0001H. Generally, in COMPARATOR COUNTER Mode, the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions is calculated with the following equation:

Comparator Output Transitions = Current Count Value – Start Value

## Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 54 and 55, control PWM operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7    | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------|------------|-----|-----|-----|-----|-----|-----|--|

| Field   | PWMH |            |     |     |     |     |     |     |  |

| RESET   | 0    | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |      | F04H, F0CH |     |     |     |     |     |     |  |

## Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

### Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PWML       |     |     |     |     |     |     |     |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F05H, F0DH |     |     |     |     |     |     |     |

#### Bit Description

| [7:0] | Pulse Width Modulator High and Low Bytes                                                     |

|-------|----------------------------------------------------------------------------------------------|

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1).                         |

|       | The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operat-      |

|       | ing in capture or CAPTURE/COMPARE modes.                                                     |

# Watchdog Timer

The Watchdog Timer (WDT) protects from corrupted or unreliable software, power faults and other system-level problems which can place the Z8 Encore! F0830 Series devices into unsuitable operating states. The features of the Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The Watchdog Timer is a retriggerable one-shot timer that resets or interrupts the Z8 Encore! F0830 Series devices when the WDT reaches its terminal count. The WDT uses a dedicated on-chip RC oscillator as its clock source. The WDT operates only in two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the WDT to operate immediately on reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is calculated using the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the 24-bit decimal value provided by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10KHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value |            | ate Time-Out Delay<br>I WDT Oscillator Frequency) |

|------------------|------------------|------------|---------------------------------------------------|

| (Hex)            | (Decimal)        | Typical    | Description                                       |

| 000004           | 4                | 400µs      | Minimum time-out delay                            |

| 000400           | 1024             | 102ms      | Default time-out delay                            |

| FFFFF            | 16,777,215       | 28 minutes | Maximum time-out delay                            |

### Table 58. Watchdog Timer Approximate Time-Out Delays

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| 1FFFH          |           | <br>Page 15 | 1FFFH<br>1E00H |

|----------------|-----------|-------------|----------------|

|                | Sector 7  | Page 14     | 1DFFH<br>1C00H |

| 1C00H<br>18FFH |           | <br>Page 13 | 1BFFH<br>1A00H |

|                | Sector 6  | <br>Page 12 | 19FFH<br>1800H |

| 1800H<br>17FFH |           | <br>Page 11 | 17FFH<br>1600H |

| 1400H          | Sector 5  | <br>Page 10 | 15FFH<br>1400H |

| 13FFH          |           | <br>Page 9  | 13FFH<br>1200H |

|                | Sector 4  | <br>Page 8  | 11FFH          |

| 1C00H<br>0FFFH | Sector 3  | <br>Page 7  | 1C00H<br>0FFFH |

| 0C00H          | Seciol 3  | Page 6      | 0E00H<br>0DFFH |

| 0BFFH          | On star 0 | <br>Page 5  | 0C00H<br>0BFFH |

| 0800H          | Sector 2  | <br>Page 4  | 0A00H<br>09FFH |

| 07FFH          | Sector 1  | Page 3      | 0800H<br>07FFH |

| 0400H          | Sector 1  | <br>Page 2  | 0600H<br>05FFH |

| 03FFH          | Sector 0  | Page 1      | 0400H<br>03FFH |

| 0000H          |           | <br>Page 0  | 0200H<br>0100H |

|                |           |             | 0000H          |

Figure 17. 8K Flash with NVDS

110

## **Page Erase**

Flash memory can be erased one page (512 bytes) at a time. Page erasing Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the page erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the page erase is complete, the Flash Controller returns to its Locked state.

## **Mass Erase**

Flash memory can also be mass erased using the Flash Controller, but only by using the On-Chip Debugger. Mass erasing Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the mass erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the mass erase is complete, the Flash Controller returns to its Locked state.

## **Flash Controller Bypass**

The Flash Controller can be bypassed; instead, the control signals for Flash memory can be brought out to the GPIO pins. Bypassing the Flash Controller allows faster row programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of Flash memory. Mass Erase and Page Erase operations are also supported, when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to *Third-Party Flash Programming Support for Z8 Encore!*. This document is available for download at <u>www.zilog.com</u>.

## Flash Controller Behavior in Debug Mode

The following behavioral changes can be observed in the Flash Controller when the Flash Controller is accessed using the On-Chip Debugger:

• The Flash write protect option bit is ignored.

## **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control Register before programming or erasing Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, Flash memory can be enabled for mass erase or page erase by writing the appropriate enable command to the FCTL. Page erase applies only to the active page selected in Flash Page Select Register. Mass erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its Locked state. The write-only Flash Control Register shares its register file address with the read-only Flash Status Register.

| Bit     | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---|------|---|---|---|---|---|---|--|

| Field   |   | FCMD |   |   |   |   |   |   |  |

| RESET   | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 |  |

| R/W     | W | W    | W | W | W | W | W | W |  |

| Address |   | FF8H |   |   |   |   |   |   |  |

| Table 72. | Flash | Control | Register | (FCTL) |

|-----------|-------|---------|----------|--------|

|-----------|-------|---------|----------|--------|

#### Bit Description

| [7:0] | Flash Command |

|-------|---------------|

|-------|---------------|

- FCMD 73H = First unlock command.

- 8CH = Second unlock command.

- 95H = Page erase command (must be third command in sequence to initiate page erase).

- 63H = Mass erase command (must be third command in sequence to initiate mass erase).

- 5EH = Enable Flash Sector Protect Register access.

## **Flash Status Register**

The Flash Status Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its register file address with the write-only Flash Control Register.

| Bit     | 7    | 6     | 5 | 4 | 3     | 2 | 1 | 0 |

|---------|------|-------|---|---|-------|---|---|---|

| Field   | Rese | erved |   |   | FSTAT |   |   |   |

| RESET   | 0    | 0     | 0 | 0 | 0     | 0 | 0 | 0 |

| R/W     | R    | R     | R | R | R     | R | R | R |

| Address |      | FF8H  |   |   |       |   |   |   |

|         |      |       |   |   |       |   |   |   |

## Table 73. Flash Status Register (FSTAT)

| Bit   | Description                                            |

|-------|--------------------------------------------------------|

| [7:6] | Reserved                                               |

|       | These bits are reserved and must be programmed to 00.  |

| [5:0] | Flash Controller Status                                |

| FSTAT | 000000 = Flash Controller locked.                      |

|       | 000001 = First unlock command received (73H written).  |

|       | 000010 = Second unlock command received (8CH written). |

|       | 000011 = Flash Controller unlocked.                    |

|       | 000100 = Sector protect register selected.             |

|       | 001xxx = Program operation in progress.                |

|       | 010xxx = Page Erase operation in progress.             |

|       | 100xxx = Mass Erase operation in progress.             |

## **Flash Sector Protect Register**

The Flash Sector Protect Register is shared with the Flash Page Select Register. When the Flash Control Register is locked and written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the eight available Flash memory sectors to be protected. The Reset state of each sector protect bit is the zero (unprotected) state. After a sector is protected by setting its corresponding register bit, the register bit cannot be cleared by the user.

To determine the appropriate Flash memory sector address range and sector number for your F0830 Series product, please refer to <u>Table 70</u> on page 112.

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |

| Address |        | FF9H   |        |        |        |        |        |        |  |

| Table 75 | . Flash Sect | or Protect Reg | gister (FPROT) |

|----------|--------------|----------------|----------------|

|----------|--------------|----------------|----------------|

#### Bit Description

#### [7:0] Sector Protection

SPROT*x* For Z8F12xx, Z8F08xx and Z8F04xx devices, all bits are used. For Z8F02xx devices, the upper four bits remain unused. For Z8F01xx devices, the upper six bits remain unused. To determine the appropriate Flash memory sector address range and sector number for your F0830 Series product, please refer to <u>Table 69</u> and to Figures 14 through 18.

Note: x indicates bits in the range 7–0.

# **Option Bit Types**

This section describes the two types of Flash option bits offered in the F0830 Series.

## **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits is provided because these locations contain application specific device configurations. The information contained here is lost when page 0 of program memory is erased.

## **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered by the user. Program memory can be erased without endangering these values. It is possible to alter working values of these bits by accessing the trim bit address and data registers, but these working values are lost after a power loss.

There are 32 bytes of trim data. To modify one of these values, the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20–3F only. The remaining information page is not accessible via the Trim Bit Address and Data registers.

During reset, the first 43 system clock cycles perform 43 Flash accesses. The six bits of the counter provide the lower six bits of the Flash memory address. All other address bits are set to 0. The option bit registers use the 6-bit address from the counter as an address and latch the data from the Flash on the positive edge of the IPO clock, allowing for a maximum of 344-bits (43 bytes) of option information to be read from Flash.

Because option information is stored in both the first two bytes of program memory and in the information area of Flash memory, the data must be placed in specific locations to be read correctly. In this case, the first two bytes at addresses 0 and 1 in program memory are read out and the remainder of the bytes are read out of the Flash information area.

ory size and is approximately equal to the system clock period multiplied by the number of bytes in program memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

**Step Instruction (10H).** The step instruction command, steps one assembly instruction at the current program counter (PC) location. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 10H

```

**Stuff Instruction (11H).** The stuff instruction command, steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0–4 bytes of the instruction are read from program memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a breakpoint. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The execute instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

## **OCD Control Register**

The OCD Control Register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It can also reset the Z8 Encore! F0830 Series device.

A reset and stop function can be achieved by writing 81H to this register. A *reset and go* function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

|                   |                                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = -40°C to<br>+105°C |                  |     |       |                                                             |  |

|-------------------|-------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|-----|-------|-------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                 | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max | Units | Conditions                                                  |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>disabled                              |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>enabled                               |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                                            |                               |     |     | _                                   | 10               | _   | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to gen<br>erate a Reset. |  |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to<br>transition from $V_{SS}$<br>to $V_{POR}$ to ensure<br>valid Reset |                               |     |     | 0.10                                | _                | 100 | ms    |                                                             |  |

## Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

ance only and are not tested in production.

## Hex Address: F09

## Table 139. Timer 1 Low Byte Register (T1L)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TL   |     |     |     |     |     |     |     |

| RESET   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F09H |     |     |     |     |     |     |     |

## Hex Address: F0A

#### Table 140. Timer 1 Reload High Byte Register (T1RH)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TRH  |     |     |     |     |     |     |     |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FOAH |     |     |     |     |     |     |     |

## Hex Address: F0B

## Table 141. Timer 1 Reload Low Byte Register (T1RL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TRL  |     |     |     |     |     |     |     |

| RESET   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F0BH |     |     |     |     |     |     |     |

## Hex Address: F0C

#### Table 142. Timer 1 PWM High Byte Register (T1PWMH)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PWMH |     |     |     |     |     |     |     |

| RESET   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F0CH |     |     |     |     |     |     |     |