Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore Processore38Core Size8-BitSpeed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O23Program Memory Size2KB (2K × 8)FLASHEXEROM SizeRAM Size256 × 8Voltage - Supply (Vcc/Vdd)2.7 v - 3.6VData ConvertersA/D 81/D6Operating Temperature4.0° c ~ 105°C (TA)Mounting TypeSirace MountProkage / Case2.8 vQFNSupplier Device Package-Procesure III1.9 vorwersfLocm/product-detail/zilog/28f0230g/020eg | Details                    |                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------|

| Core Size8-BitSpeed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O23Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size-XAM Size256 x 8Voltage - Supply (Vcc/Vdd)27 v ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case8-VQFN                                                                                        | Product Status             | Active                                                    |

| Speed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O23Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case82-VQFNSupplier Device Package-                                                                                                   | Core Processor             | eZ8                                                       |

| Connectivity-Connectivity-PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O23Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFN                                                                                                 | Core Size                  | 8-Bit                                                     |

| PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O23Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting Type28-VOFNSupplier Device Package-                                                                                                                              | Speed                      | 20MHz                                                     |

| Number of I/O23Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFN                                                                                                                                                                                | Connectivity               | -                                                         |

| Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFNSupplier Device Package-                                                                                                                                                                       | Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case8-VQFNSupplier Device Package-                                                                                                                                                                                                       | Number of I/O              | 23                                                        |

| EEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFNSupplier Device Package-                                                                                                                                                                                                                              | Program Memory Size        | 2KB (2K x 8)                                              |

| RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFNSupplier Device Package-                                                                                                                                                                                                                                          | Program Memory Type        | FLASH                                                     |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFNSupplier Device Package-                                                                                                                                                                                                                                                         | EEPROM Size                | -                                                         |

| Data ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFNSupplier Device Package-                                                                                                                                                                                                                                                                                              | RAM Size                   | 256 x 8                                                   |

| Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFNSupplier Device Package-                                                                                                                                                                                                                                                                                                                      | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Operating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case28-VQFNSupplier Device Package-                                                                                                                                                                                                                                                                                                                                             | Data Converters            | A/D 8x10b                                                 |

| Mounting Type     Surface Mount       Package / Case     28-VQFN       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                       | Oscillator Type            | Internal                                                  |

| Package / Case     28-VQFN       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                             | Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Supplier Device Package -                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mounting Type              | Surface Mount                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Package / Case             | 28-VQFN                                                   |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f0230qj020eg                                                                                                                                                                                                                                                                                                                                                                                     | Supplier Device Package    | •                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0230qj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Electrical Characteristics 1                              | 184 |

|-----------------------------------------------------------|-----|

| Absolute Maximum Ratings 1                                | 184 |

| DC Characteristics 1                                      | 185 |

| AC Characteristics                                        | 189 |

| On-Chip Peripheral AC and DC Electrical Characteristics 1 | 190 |

| General Purpose I/O Port Input Data Sample Timing 1       | 195 |

| General Purpose I/O Port Output Timing 1                  | 196 |

| On-Chip Debugger Timing 1                                 | 197 |

| Packaging 1                                               | 199 |

| Ordering Information                                      | 200 |

| Part Number Suffix Designations 2                         | 205 |

| Appendix A. Register Tables                               | 208 |

| General Purpose RAM                                       | 208 |

| Timer 0                                                   | 208 |

| Analog-to-Digital Converter                               | 213 |

| Low Power Control                                         | 216 |

| LED Controller                                            | 216 |

| Oscillator Control                                        | 217 |

| Comparator 0                                              | 218 |

| Interrupt Controller                                      | 218 |

| GPIO Port A 2                                             | 222 |

| Watchdog Timer                                            | 226 |

| Trim Bit Control                                          | 228 |

| Flash Memory Controller    2                              | 228 |

| Index                                                     | 231 |

| Customer Support                                          | 239 |

|                                                           |     |

# ix

### xi

| Figure 27. | Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$ Resistor |

|------------|-----------------------------------------------------------------------------------------------------|

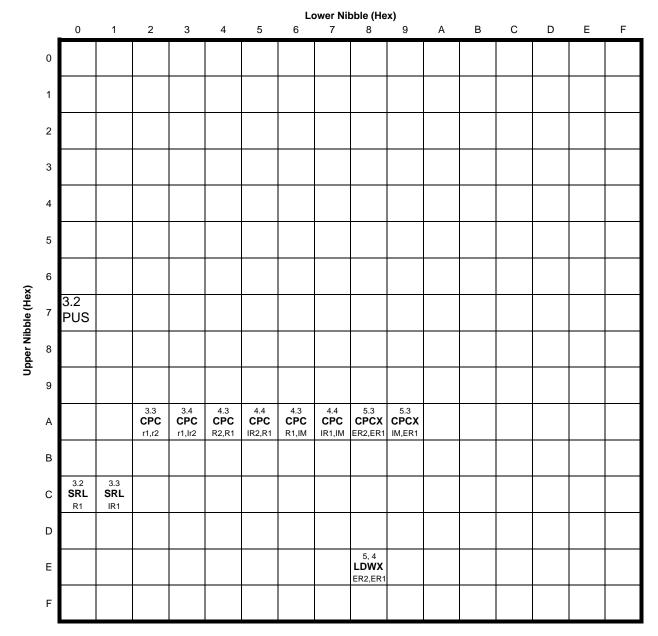

| Figure 28. | Op Code Map Cell Description 180                                                                    |

| Figure 29. | First Op Code Map                                                                                   |

| Figure 30. | Second Op Code Map after 1FH 183                                                                    |

| Figure 31. | $I_{CC}$ Versus System Clock Frequency (HALT Mode) 187                                              |

| Figure 32. | I <sub>CC</sub> Versus System Clock Frequency (NORMAL Mode) 188                                     |

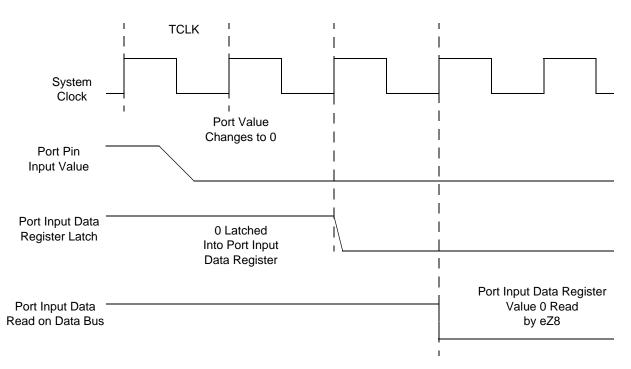

| Figure 33. | Port Input Sample Timing 195                                                                        |

| Figure 34. | GPIO Port Output Timing 196                                                                         |

| Figure 35. | On-Chip Debugger Timing 197                                                                         |

| Figure 36. | Flash Current Diagram                                                                               |

# 17

# **Register Map**

Table 8 provides an address map of the Z8 Encore! F0830 Series register file. Not all devices and package styles in the Z8 Encore! F0830 Series support the ADC or all of the GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)    | Register Description              | Mnemonic      | Reset (Hex) | Page No. |

|------------------|-----------------------------------|---------------|-------------|----------|

| General Purpos   | e RAM                             |               |             |          |

| 000–0FF          | General purpose register file RAM |               | XX          |          |

| 100–EFF          | Reserved                          | _             | XX          |          |

| Timer 0          |                                   |               |             |          |

| F00              | Timer 0 high byte                 | T0H           | 00          | 83       |

| F01              | Timer 0 low byte                  | TOL           | 01          | 83       |

| F02              | Timer 0 reload high byte          | TORH          | FF          | 85       |

| F03              | Timer 0 reload low byte           | TORL          | FF          | 85       |

| F04              | Timer 0 PWM high byte             | <b>T0PWMH</b> | 00          | 86       |

| F05              | Timer 0 PWM low byte              | TOPWML        | 00          | 86       |

| F06              | Timer 0 control 0                 | T0CTL0        | 00          | 87       |

| F07              | Timer 0 control 1                 | T0CTL1        | 00          | 88       |

| Timer 1          |                                   |               |             |          |

| F08              | Timer 1 high byte                 | T1H           | 00          | 83       |

| F09              | Timer 1 low byte                  | T1L           | 01          | 83       |

| F0A              | Timer 1 reload high byte          | T1RH          | FF          | 85       |

| F0B              | Timer 1 reload low byte           | T1RL          | FF          | 85       |

| F0C              | Timer 1 PWM high byte             | T1PWMH        | 00          | 86       |

| F0D              | Timer 1 PWM low byte              | T1PWML        | 00          | 86       |

| F0E              | Timer 1 control 0                 | T1CTL0        | 00          | 87       |

| F0F              | Timer 1 control 1                 | T1CTL1        | 00          | 83       |

| F10–F6F          | Reserved                          | _             | XX          |          |

| Analog-to-Digita | al Converter (ADC)                |               |             |          |

| F70              | ADC control 0                     | ADCCTL0       | 00          | 102      |

| F71              | Reserved                          |               | XX          |          |

| F72              | ADC data high byte                | ADCD_H        | XX          | 103      |

#### Table 8. Register File Address Map

Note: XX = Undefined.

|                                                    | Reset Characteristics and Latency                      |         |                                                    |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------|---------|----------------------------------------------------|--|--|--|--|

| Reset Type                                         | Control Registers                                      | eZ8 CPU | Reset Latency (Delay)                              |  |  |  |  |

| System Reset                                       | Reset (as applicable)                                  | Reset   | About 66 Internal Precision Oscillator<br>Cycles   |  |  |  |  |

| System Reset with Crystal<br>Oscillator Enabled    | Reset (as applicable)                                  | Reset   | About 5000 Internal Precision Oscillator<br>Cycles |  |  |  |  |

| Stop Mode Recovery                                 | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset   | About 66 Internal Precision Oscillator cycles      |  |  |  |  |

| Stop Mode Recovery with crystal oscillator enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset   | About 5000 Internal Precision Oscillator cycles    |  |  |  |  |

#### Table 9. Reset and Stop Mode Recovery Characteristics and Latency

During a system RESET or Stop Mode Recovery, the Z8 Encore! F0830 Series device is held in reset for about 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, the reset period is increased to about 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, the reset delay is measured from the time that the supply voltage first exceeds the POR level (discussed later in this chapter). If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 which is shared with the reset pin. On reset, the Port D0 pin is configured as a bidirectional open-drain reset. This pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer Oscillator continues to run.

On reset, control registers within the register file that have a defined reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general purpose RAM are undefined following the reset. The eZ8 CPU fetches the reset vector at program memory addresses 0002H and 0003H and loads that value into the program counter. Program execution begins at the reset vector address.

Because the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. User software must reconfigure the oscillator control block, to enable and select the correct system clock source.

## Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the Port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high-output current drive operation. The Port A–D High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit     | 7         | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Field   | PHDE7     | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET   | 0         | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W       | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | lf 04H ir | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |

#### Bit Description

[7:0] Port High Drive Enable

PHDEx 0 = The port pin is configured for standard output current drive.

1 = The port pin is configured for high output current drive.

Note: x indicates the specific GPIO port pin number (7–0).

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers. <u>Timer 0–1 High and Low Byte Registers</u>: see page 83

Timer Reload High and Low Byte Registers: see page 85

Timer 0-1 PWM High and Low Byte Registers: see page 86

Timer 0-1 Control Registers: see page 87

# Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers, shown in Tables 50 and 51, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register content when the timer is enabled; however, when the timer is disabled, a read from the TxL reads the TxL Register content directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations; therefore, simultaneous 16-bit writes are not possible. If either the timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low byte) at the next clock edge. The counter continues counting from the new value.

| Bit     | 7   | 6                           | 5 | 4     | 3    | 2 | 1 | 0 |

|---------|-----|-----------------------------|---|-------|------|---|---|---|

| Field   |     |                             |   | Т     | Н    |   |   |   |

| RESET   | 0   | 0                           | 0 | 0     | 0    | 0 | 0 | 0 |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |

| Address |     |                             |   | F00H, | F08H |   |   |   |

Table 50. Timer 0–1 High Byte Register (TxH)

| Table 51 | . Timer 0–1 | Low Byte | Register | (TxL) |

|----------|-------------|----------|----------|-------|

|          |             |          |          |       |

| Bit     | 7   | 6                           | 5 | 4     | 3    | 2 | 1 | 0 |

|---------|-----|-----------------------------|---|-------|------|---|---|---|

| Field   |     | TL                          |   |       |      |   |   |   |

| RESET   | 0   | 0                           | 0 | 0     | 0    | 0 | 0 | 1 |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |

| Address |     |                             |   | F01H, | F09H |   |   |   |

# Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 54 and 55, control PWM operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7   | 6                       | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|-----|-------------------------|---|----|----|---|---|---|

| Field   |     |                         |   | PW | MH |   |   |   |

| RESET   | 0   | 0                       | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |

| Address |     | F04H, F0CH              |   |    |    |   |   |   |

### Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

### Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|------|-----|-----|-----|-----|-----|-----|

| Field   |            | PWML |     |     |     |     |     |     |

| RESET   | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F05H, F0DH |      |     |     |     |     |     |     |

#### Bit Description

| [7:0] | Pulse Width Modulator High and Low Bytes                                                     |

|-------|----------------------------------------------------------------------------------------------|

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1).                         |

|       | The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operat-      |

|       | ing in capture or CAPTURE/COMPARE modes.                                                     |

113

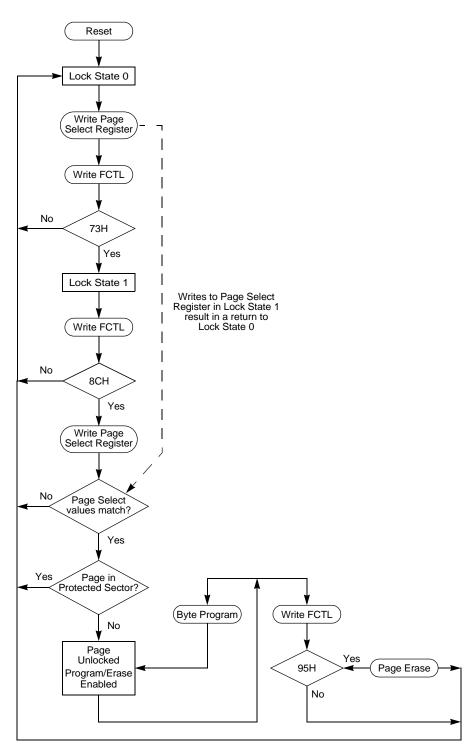

Figure 19. Flash Controller Operation Flow Chart

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>VBO_AO | <ul> <li>Voltage Brown-Out Protection Always On</li> <li>0 = Voltage Brown-Out protection is disabled in STOP Mode to reduce total power consumption.</li> <li>1 = Voltage Brown-Out protection is always enabled, even during STOP Mode. This setting is the default setting for unprogrammed (erased) Flash.</li> </ul>                                                                                      |

| [2]<br>FRP    | <ul> <li>Flash Read Protect</li> <li>0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.</li> <li>1 = User program code is accessible. All On-Chip Debugger commands are enabled. This is the default setting for unprogrammed (erased) Flash.</li> </ul>                                                                                              |

| [1]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                                                                           |

| [0]<br>FWP    | <ul> <li>Flash Write Protect</li> <li>This option bit provides Flash program memory protection.</li> <li>0 = Programming and erasure disabled for all Flash program memory. Programming, page erase and mass erase through user code is disabled. Mass erase is available using the On-Chip Debugger.</li> <li>1 = Programming, page erase and mass erase are enabled for all Flash program memory.</li> </ul> |

# Table 82. Flash Options Bits at Program Memory Address 0001H

| Bit       | 7                                               | 6                    | 5   | 4      | 3        | 2       | 1   | 0   |  |

|-----------|-------------------------------------------------|----------------------|-----|--------|----------|---------|-----|-----|--|

| Field     | VBO_RES                                         | Reserved             |     | XTLDIS | Reserved |         |     |     |  |

| RESET     | U                                               | U                    | U   | U      | U        | U U U U |     |     |  |

| R/W       | R/W                                             | R/W                  | R/W | R/W    | R/W      | R/W     | R/W | R/W |  |

| Address   |                                                 | Program Memory 0001H |     |        |          |         |     |     |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                      |     |        |          |         |     |     |  |

| Bit            | Description                                                                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>VBO_RES | Voltage Brown-Out reset<br>1 = VBO detection causes a system reset. This setting is the default setting for unpro-<br>grammed (erased) Flash. |

| [6:5]          | Reserved<br>These bits are reserved and must be programmed to 11.                                                                             |

128

# Nonvolatile Data Storage

Z8 Encore! F0830 Series devices contain a Nonvolatile Data Storage (NVDS) element of up to 64 bytes (except when in Flash 12KB mode). This type of memory can perform over 100,000 write cycles.

# Operation

NVDS is implemented by special-purpose Zilog software stored in areas of program memory that are not user-accessible. These special-purpose routines use Flash memory to store the data, and incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

**Note:** The products in the Z8 Encore! F0830 Series feature multiple NVDS array sizes. See the <u>Z8 Encore! F0830 Series Family Part Selection Guide</u> section on page 2 for details.

# **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a predefined address outside of program memory that is accessible to the user. Both the NVDS address and data are singlebyte values. In order to not disturb the user code, these routines save the working register set before using it so that 16 bytes of stack space are required to preserve the site. After finishing the call to these routines, the working register set of the user code is recovered.

During both read and write accesses to the NVDS, interrupt service is not disabled. Any interrupts that occur during NVDS execution must not disturb the working register and existing stack contents; otherwise, the array can become corrupted. Zilog recommends the user disable interrupts before executing NVDS operations.

Use of the NVDS requires 16 bytes of available stack space. The contents of the working register set are saved before calling NVDS read or write routines.

For correct NVDS operation, the Flash Frequency registers must be programmed based on the system clock frequency. See *the* <u>Flash Operation Timing Using the Flash Frequency</u><u>Registers</u> *section on page 114*.

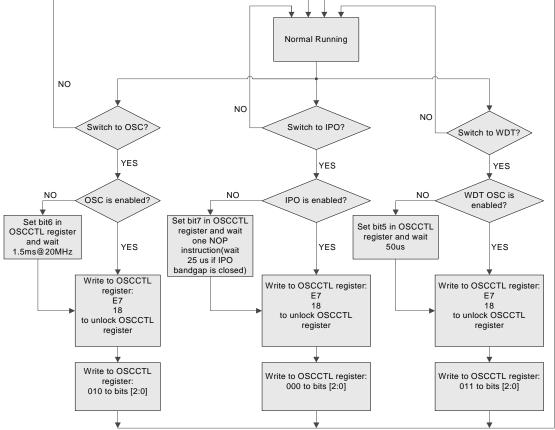

Figure 24. Oscillator Control Clock Switching Flow Chart

# eZ8 CPU Instruction Summary

Table 113 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch and the number of CPU clock cycles required for the instruction.

| Assembly      |                           | Address<br>Mode |     | Op<br>Code(s) | Flags |   |   |   |   |   | Fetch | Instr. |

|---------------|---------------------------|-----------------|-----|---------------|-------|---|---|---|---|---|-------|--------|

| Mnemonic      | Symbolic Operation        | dst             | src | (Hex)         | С     | Ζ | S | ۷ | D | Н |       |        |

| ADC dst, src  | $dst \gets dst + src + C$ | r               | r   | 12            | *     | * | * | * | 0 | * | 2     | 3      |

|               |                           | r               | lr  | 13            | -     |   |   |   |   |   | 2     | 4      |

|               |                           | R               | R   | 14            | -     |   |   |   |   |   | 3     | 3      |

|               |                           | R               | IR  | 15            | -     |   |   |   |   |   | 3     | 4      |

|               |                           | R               | IM  | 16            | -     |   |   |   |   |   | 3     | 3      |

|               |                           | IR              | IM  | 17            | _     |   |   |   |   |   | 3     | 4      |

| ADCX dst, src | $dst \gets dst + src + C$ | ER              | ER  | 18            | *     | * | * | * | 0 | * | 4     | 3      |

|               |                           | ER              | IM  | 19            | _     |   |   |   |   |   | 4     | 3      |

| ADD dst, src  | dst ← dst + src           | r               | r   | 02            | *     | * | * | * | 0 | * | 2     | 3      |

|               |                           | r               | Ir  | 03            | _     |   |   |   |   |   | 2     | 4      |

|               |                           | R               | R   | 04            | _     |   |   |   |   |   | 3     | 3      |

|               |                           | R               | IR  | 05            | _     |   |   |   |   |   | 3     | 4      |

|               |                           | R               | IM  | 06            | _     |   |   |   |   |   | 3     | 3      |

|               |                           | IR              | IM  | 07            | _     |   |   |   |   |   | 3     | 4      |

| ADDX dst, src | $dst \gets dst + src$     | ER              | ER  | 08            | *     | * | * | * | 0 | * | 4     | 3      |

|               |                           | ER              | IM  | 09            | -     |   |   |   |   |   | 4     | 3      |

### Table 113. eZ8 CPU Instruction Summary

Note: Flags Notation:

\* = Value is a function of the result of the operation.

– = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

Figure 30. Second Op Code Map after 1FH

183

### 195

# General Purpose I/O Port Input Data Sample Timing

Figure 33 displays timing of the GPIO port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The port value is available to the eZ8 CPU on the second rising clock edge following the change of the port value.

#### Figure 33. Port Input Sample Timing

#### Table 124. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |         |  |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (not pictured)                            | 5          | -       |  |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (not pictured)                             | 0          | -       |  |  |

| T <sub>SMR</sub>    | GPIO port pin pulse width to ensure Stop Mode Recovery (for GPIO port pins enabled as SMR sources) | 1µs        |         |  |  |

| Part Number          | Flash      | RAM   | NVDS | ADC<br>Channels | Description                                    |

|----------------------|------------|-------|------|-----------------|------------------------------------------------|

| Z8F0131PJ020SG       | 1KB        | 256   | Yes  | 0               | PDIP 28-pin                                    |

| Z8F0131QJ020SG       | 1KB        | 256   | Yes  | 0               | QFN 28-pin                                     |

| Extended Temperature | : −40°C to | 105°C |      |                 |                                                |

| Z8F0130SH020EG       | 1KB        | 256   | Yes  | 7               | SOIC 20-pin                                    |

| Z8F0130HH020EG       | 1KB        | 256   | Yes  | 7               | SSOP 20-pin                                    |

| Z8F0130PH020EG       | 1KB        | 256   | Yes  | 7               | PDIP 20-pin                                    |

| Z8F0130QH020EG       | 1KB        | 256   | Yes  | 7               | QFN 20-pin                                     |

| Z8F0131SH020EG       | 1KB        | 256   | Yes  | 0               | SOIC 20-pin                                    |

| Z8F0131HH020EG       | 1KB        | 256   | Yes  | 0               | SSOP 20-pin                                    |

| Z8F0131PH020EG       | 1KB        | 256   | Yes  | 0               | PDIP 20-pin                                    |

| Z8F0131QH020EG       | 1KB        | 256   | Yes  | 0               | QFN 20-pin                                     |

| Z8F0130SJ020EG       | 1KB        | 256   | Yes  | 8               | SOIC 28-pin                                    |

| Z8F0130HJ020EG       | 1KB        | 256   | Yes  | 8               | SSOP 28-pin                                    |

| Z8F0130PJ020EG       | 1KB        | 256   | Yes  | 8               | PDIP 28-pin                                    |

| Z8F0130QJ020EG       | 1KB        | 256   | Yes  | 8               | QFN 28-pin                                     |

| Z8F0131SJ020EG       | 1KB        | 256   | Yes  | 0               | SOIC 28-pin                                    |

| Z8F0131HJ020EG       | 1KB        | 256   | Yes  | 0               | SSOP 28-pin                                    |

| Z8F0131PJ020EG       | 1KB        | 256   | Yes  | 0               | PDIP 28-pin                                    |

| Z8F0131QJ020EG       | 1KB        | 256   | Yes  | 0               | QFN 28-pin                                     |

| ZUSBSC00100ZACG      |            |       |      |                 | USB Smart Cable Accessory Kit                  |

| ZUSBOPTSC01ZACG      |            |       |      |                 | Opto-Isolated USB Smart Cable<br>Accessory Kit |

#### Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

# **Part Number Suffix Designations**

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0830SH020SG is an 8-bit 20MHz Flash MCU with 8KB Program Memory and equipped with ADC and NVDS in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

207

Table 129 lists the pin count by package.

|         | Pin Count    |    |  |  |  |

|---------|--------------|----|--|--|--|

| Package | 20           | 28 |  |  |  |

| PDIP    | $\checkmark$ |    |  |  |  |

| QFN     | $\checkmark$ |    |  |  |  |

| SOIC    | $\checkmark$ |    |  |  |  |

| SSOP    | $\checkmark$ |    |  |  |  |

### Table 129. Package and Pin Count Description

# Appendix A. Register Tables

For the reader's convenience, this appendix lists all F0830 Series registers numerically by hexadecimal address.

# **General Purpose RAM**

In the F0830 Series, the 000–EFF hexadecimal address range is partitioned for general-purpose random access memory, as follows.

# Hex Addresses: 000–0FF

This address range is reserved for general-purpose register file RAM. For more details, see the <u>Register File</u> section on page 14.

## Hex Addresses: 100-EFF

This address range is reserved.

# Timer 0

For more information about these Timer Control registers, see the <u>Timer Control Register</u> <u>Definitions</u> section on page 83.

## Hex Address: F00

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | TH   |     |     |     |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F00H |     |     |     |     |     |     |  |

### Table 130. Timer 0 High Byte Register (T0H)

# Hex Address: F74

### Table 149. ADC Sample Settling Time (ADCSST)

| Bit     | 7        | 6    | 5 | 4 | 3   | 2  | 1 | 0 |  |  |

|---------|----------|------|---|---|-----|----|---|---|--|--|

| Field   | Reserved |      |   |   | SST |    |   |   |  |  |

| RESET   |          | (    | ) |   | 1   | 1  | 1 | 1 |  |  |

| R/W     |          | F    | २ |   |     | R/ | W |   |  |  |

| Address |          | F74H |   |   |     |    |   |   |  |  |

| Bit          | Description                                                                                   |

|--------------|-----------------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                    |

| [3:0]<br>SST | <b>Sample Settling Time</b><br>0h–Fh = Number of system clock periods to meet 0.5 μs minimum. |

# Hex Address: F75

# Table 150. ADC Sample Time (ADCST)

| Bit     | 7    | 6     | 5  | 4    | 3 | 2 | 1 | 0 |  |

|---------|------|-------|----|------|---|---|---|---|--|

| Field   | Rese | erved | ST |      |   |   |   |   |  |

| RESET   | (    | )     | 1  | 1    | 1 | 1 | 1 | 1 |  |

| R/W     | R/   | W     |    | R/W  |   |   |   |   |  |

| Address |      |       |    | F75H |   |   |   |   |  |

| Bit         | Description                                                                      |

|-------------|----------------------------------------------------------------------------------|

| [7:6]       | <b>Reserved</b><br>This register is reserved and must be programmed to 0.        |

| [5:0]<br>ST | Sample/Hold Time<br>0h–Fh = Number of system clock periods to meet 1 µs minimum. |

# Hex Addresses: F77–F7F

This address range is reserved.

# Hex Address: FDB

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address |       | FDBH  |       |       |       |       |       |       |  |

## Hex Address: FDC

### Table 181. Port D GPIO Address Register (PDADDR)

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|

| Field   |      | PADDR[7:0]                  |   |   |   |   |   |   |  |

| RESET   |      | 00H                         |   |   |   |   |   |   |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FDCH |                             |   |   |   |   |   |   |  |

# Hex Address: FDD

### Table 182. Port D Control Registers (PDCTL)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|

| Field   |     | PCTL                        |   |   |   |   |   |   |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address |     | FDDH                        |   |   |   |   |   |   |  |

## Hex Address: FDE

This address range is reserved.

# Hex Address: FF8

### Table 192. Flash Status Register (FSTAT)

| Bit     | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|---------|------|-------|-------|---|---|---|---|---|

| Field   | Rese | erved | FSTAT |   |   |   |   |   |

| RESET   | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W     | R    | R     | R     | R | R | R | R | R |

| Address |      | FF8H  |       |   |   |   |   |   |

# Hex Address: FF9

The Flash Page Select Register is shared with the Flash Sector Protect Register.

## Table 193. Flash Page Select Register (FPS)

| Bit     | 7       | 6    | 5    | 4   | 3   | 2   | 1   | 0   |

|---------|---------|------|------|-----|-----|-----|-----|-----|

| Field   | INFO_EN |      | PAGE |     |     |     |     |     |

| RESET   | 0       | 0    | 0    | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W     | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W |

| Address |         | FF9H |      |     |     |     |     |     |

## Table 194. Flash Sector Protect Register (FPROT)

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |

| Address |        | FF9H   |        |        |        |        |        |        |  |

# Hex Address: FFA

## Table 195. Flash Frequency High Byte Register (FFREQH)

| Bit     | 7   | 6      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|--------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | FFREQH |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0      | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | FFAH   |     |     |     |     |     |     |  |  |