Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | -                                                         |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 17                                                        |  |

| Program Memory Size        | 2KB (2K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | A/D 7x10b                                                 |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0230sh020eg |  |

# Z8 Encore!® F0830 Series Product Specification

vii

| Calibration and Compensation                                 | 101 |

|--------------------------------------------------------------|-----|

| ADC Control Register Definitions                             | 101 |

| ADC Control Register 0                                       | 102 |

| ADC Data High Byte Register                                  | 103 |

| ADC Data Low Bits Register                                   | 103 |

| Sample Settling Time Register                                | 104 |

| Sample Time Register                                         | 105 |

| Comparator                                                   | 106 |

| Operation                                                    | 106 |

| Comparator Control Register Definitions                      | 107 |

| Flash Memory                                                 | 108 |

| Data Memory Address Space                                    | 111 |

| Flash Information Area                                       | 111 |

| Operation                                                    | 112 |

| Flash Operation Timing Using the Flash Frequency Registers   | 114 |

| Flash Code Protection Against External Access                | 114 |

| Flash Code Protection Against Accidental Program and Erasure | 114 |

| Byte Programming                                             | 116 |

| Page Erase                                                   | 117 |

| Mass Erase                                                   | 117 |

| Flash Controller Bypass                                      | 117 |

| Flash Controller Behavior in Debug Mode                      | 117 |

| NVDS Operational Requirements                                | 118 |

| Flash Control Register Definitions                           | 118 |

| Flash Control Register                                       | 119 |

| Flash Status Register                                        |     |

| Flash Page Select Register                                   | 121 |

| Flash Sector Protect Register                                |     |

| Flash Frequency High and Low Byte Registers                  |     |

| Flash Option Bits                                            | 124 |

| Operation                                                    | 124 |

| Option Bit Configuration by Reset                            | 124 |

| Option Bit Types                                             |     |

| Flash Option Bit Control Register Definitions                |     |

| Trim Bit Address Register                                    |     |

| Trim Bit Data Register                                       |     |

| Flash Option Bit Address Space                               |     |

| Trim Bit Address Space                                       |     |

| Nonvolatile Data Storage                                     | 134 |

PS025113-1212 Table of Contents

# Z8 Encore!® F0830 Series Product Specification

ΧV

| Table 89.  | Trim Option Bits at 0006H (TCLKFLT)                                            |

|------------|--------------------------------------------------------------------------------|

| Table 90.  | ClkFlt Delay Control Definition                                                |

| Table 91.  | Write Status Byte                                                              |

| Table 92.  | Read Status Byte                                                               |

| Table 93.  | NVDS Read Time                                                                 |

| Table 94.  | OCD Baud-Rate Limits                                                           |

| Table 95.  | On-Chip Debugger Command Summary                                               |

| Table 96.  | OCD Control Register (OCDCTL)                                                  |

| Table 97.  | OCD Status Register (OCDSTAT)                                                  |

| Table 98.  | Oscillator Configuration and Selection                                         |

| Table 99.  | Oscillator Control Register (OSCCTL)                                           |

| Table 100. | Recommended Crystal Oscillator Specifications                                  |

| Table 101. | Assembly Language Syntax Example 1 163                                         |

| Table 102. | Assembly Language Syntax Example 2                                             |

| Table 103. | Notational Shorthand                                                           |

| Table 104. | Additional Symbols                                                             |

| Table 105. | Arithmetic Instructions                                                        |

| Table 106. | Bit Manipulation Instructions                                                  |

| Table 107. | Block Transfer Instructions                                                    |

| Table 108. | CPU Control Instructions                                                       |

| Table 109. | Load Instructions                                                              |

| Table 110. | Rotate and Shift Instructions                                                  |

| Table 111. | Logical Instructions                                                           |

| Table 112. | Program Control Instructions                                                   |

| Table 113. | eZ8 CPU Instruction Summary                                                    |

| Table 114. | Op Code Map Abbreviations                                                      |

| Table 115. | Absolute Maximum Ratings                                                       |

| Table 116. | DC Characteristics                                                             |

| Table 117. | AC Characteristics                                                             |

| Table 118. | Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing 190 |

PS025113-1212 List of Tables

### **Reset Sources**

Table 10 lists the possible sources of a system reset.

Table 10. Reset Sources and Resulting Reset Type

| Operating Mode       | Reset Source                                          | Special Conditions                                                  |

|----------------------|-------------------------------------------------------|---------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-Out                      | Reset delay begins after supply voltage exceeds POR level.          |

|                      | Watchdog Timer time-out when configured for reset     | None.                                                               |

|                      | RESET pin assertion                                   | All reset pulses less than four system clocks in width are ignored. |

|                      | On-Chip Debugger initiated reset (OCDCTL[0] set to 1) | System, except the On-Chip Debugger is unaffected by the reset.     |

| STOP Mode            | Power-On Reset/Voltage Brown-Out                      | Reset delay begins after supply voltage exceeds POR level.          |

|                      | RESET pin assertion                                   | All reset pulses less than 12 ns are ignored.                       |

|                      | DBG pin driven Low                                    | None.                                                               |

### **Power-On Reset**

Each device in the Z8 Encore! F0830 Series contains an internal Power-On Reset circuit. The POR circuit monitors the digital supply voltage and holds the device in the Reset state until the digital supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR counter has timed out. If the crystal oscillator is enabled by the option bits, the timeout is longer.

After the Z8 Encore! F0830 Series device exits the Power-On Reset state, the eZ8 CPU fetches the reset vector. Following the Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1.

Figure 6 displays the Power-On Reset operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the POR threshold voltage  $(V_{POR})$ .

PS025113-1212 Reset Sources

**Table 16. Port Alternate Function Mapping (Continued)**

| Port                | Pin | Mnemonic         | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------|--------------------------------|-----------------------------------------|

| Port B <sup>2</sup> | PB0 | Reserved         |                                | AFS1[0]: 0                              |

|                     |     | ANA0             | ADC analog input               | AFS1[0]: 1                              |

|                     | PB1 | Reserved         |                                | AFS1[1]: 0                              |

|                     |     | ANA1             | ADC analog input               | AFS1[1]: 1                              |

|                     | PB2 | Reserved         |                                | AFS1[2]: 0                              |

|                     |     | ANA2             | ADC analog input               | AFS1[2]: 1                              |

|                     | PB3 | CLKIN            | External input clock           | AFS1[3]: 0                              |

|                     |     | ANA3             | ADC analog input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved         |                                | AFS1[4]: 0                              |

|                     |     | ANA7             | ADC analog input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved         |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> | ADC reference voltage          | AFS1[5]: 1                              |

|                     | PB6 | Reserved         |                                | AFS1[6]: 0                              |

|                     |     | Reserved         |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved         |                                | AFS1[7]: 0                              |

|                     |     | Reserved         |                                | AFS1[7]: 1                              |

#### Notes:

- 1. Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate functions (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the <a href="Port A-D Alternate Function Subregisters">Port A and Port D (PD0)</a>. Enabling alternate function selections (as described in the

- 2. Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <a href="Port A-D Alternate Function Subregisters">Port A-D Alternate Function Subregisters</a> section on page 42) must also be enabled.

- 3. Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <a href="Port A-D Alternate Function Subregisters">Port A-D Alternate Function Subregisters</a> section on page 42) must also be enabled.

### Port A-D Pull-up Enable Subregisters

The Port A–D Pull-Up Enable Subregister is accessed through the Port A–D Control Register by writing 06H to the Port A–D Address Register. See Table 26. Setting the bits in the Port A–D Pull-Up Enable subregisters enables a weak internal resistive pull-up on the specified port pins.

Table 26. Port A-D Pull-Up Enable Subregisters (PxPUE)

| Bit     | 7         | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Field   | PPUE7     | PPUE6                                                                                 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |

| RESET   | 0         | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W       | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | If 06H ir | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |

| Bit        | Description                                       |

|------------|---------------------------------------------------|

| [7:0]      | Port Pull-Up Enable                               |

| PxPUE      | 0 = The weak pull-up on the port pin is disabled. |

|            | 1 = The weak pull-up on the port pin is enabled.  |

| Note: x in | dicates the specific GPIO port pin number (7–0).  |

### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

Table 37. Interrupt Request 2 Register (IRQ2)

| Bit     | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|---------|------|------|-------|-----|------|------|------|------|

| Field   |      | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0    | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| Address | FC6H |      |       |     |      |      |      |      |

| Bit   | Description                                                            |  |

|-------|------------------------------------------------------------------------|--|

| [7:4] | Reserved                                                               |  |

|       | These registers are reserved and must be programmed to 0000.           |  |

| [3]   | Port C Pin x Interrupt Request                                         |  |

| PCxI  | 0 = No interrupt request is pending for GPIO Port C pin x.             |  |

|       | 1 = An interrupt request from GPIO Port C pin $x$ is awaiting service. |  |

| Note: | x indicates the specific GPIO port pin number (3–0).                   |  |

## IRQ0 Enable High and Low Bit Registers

Table 38 lists the priority control values for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling service for interrupts in the Interrupt Request 0 Register. Priority is generated by setting the bits in each register.

Table 38. IRQ0 Enable and Priority Encoding

| IRQ0ENH[x]                                                   | IRQ0ENL[x] | Priority | Description |  |  |

|--------------------------------------------------------------|------------|----------|-------------|--|--|

| 0                                                            | 0          | Disabled | Disabled    |  |  |

| 0                                                            | 1          | Level 1  | Low         |  |  |

| 1                                                            | 0          | Level 2  | Nominal     |  |  |

| 1                                                            | 1          | Level 3  | High        |  |  |

| Note: <i>x</i> indicates the register bits in the range 7–0. |            |          |             |  |  |

Observe the following steps for configuring a timer for PWM DUAL OUTPUT Mode and for initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM deadband delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM High and Low Byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the timer output and timer output complement alternate functions. The timer output complement function is shared with the timer input function for both timers. Setting the timer mode to DUAL PWM will automatically switch the function from timer-in to timer-out complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$$PWM \ Period \ (s) \ = \ \frac{Reload \ Value \times Prescale}{System \ Clock \ Frequency \ (Hz)}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output high time to the total period is represented by:

PS025113-1212 Operation

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the timer PWM High and Low Byte registers to 0000H. This allows user software to determine if interrupts are generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt were generated by a reload.

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. The user can configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{\text{(Capture Value - Start Value)} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$$

#### **COMPARE Mode**

In COMPARE Mode, the timer counts up to 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) upon compare.

If the timer reaches FFFFH, the timer resets to 0000H and continues counting.

Observe the following steps for configuring a timer for COMPARE Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

PS025113-1212 Operation

# Watchdog Timer

The Watchdog Timer (WDT) protects from corrupted or unreliable software, power faults and other system-level problems which can place the Z8 Encore! F0830 Series devices into unsuitable operating states. The features of the Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# **Operation**

The Watchdog Timer is a retriggerable one-shot timer that resets or interrupts the Z8 Encore! F0830 Series devices when the WDT reaches its terminal count. The WDT uses a dedicated on-chip RC oscillator as its clock source. The WDT operates only in two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the WDT to operate immediately on reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is calculated using the following equation:

WDT Time-out Period (ms) =

$$\frac{\text{WDT Reload Value}}{10}$$

where the WDT reload value is the 24-bit decimal value provided by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10KHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

Table 58. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value _ | Approximate Time-Out Delay (with 10KHz Typical WDT Oscillator Frequen |                        |  |

|------------------|--------------------|-----------------------------------------------------------------------|------------------------|--|

| (Hex)            | (Decimal)          | Typical                                                               | Description            |  |

| 000004           | 4                  | 400µs                                                                 | Minimum time-out delay |  |

| 000400           | 1024               | 102ms                                                                 | Default time-out delay |  |

| FFFFF            | 16,777,215         | 28 minutes                                                            | Maximum time-out delay |  |

PS025113-1212 Watchdog Timer

# Flash Memory

The products in the Z8 Encore! F0830 Series features either 1KB (1024 bytes with NVDS), 2KB (2048 bytes with NVDS), 4KB (4096 bytes with NVDS), 8KB (8192 bytes with NVDS) or 12KB (12288 bytes with no NVDS) of nonvolatile Flash memory with read/write/erase capability. Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

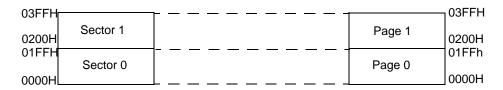

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F0830 Series, each sector maps to one page (for 1 KB, 2 KB and 4 KB devices), two pages (8 KB device) or three pages (12 KB device).

The first two bytes of Flash program memory is used as Flash option bits. For more information, see *the* Flash Option Bits chapter on page 124.

Table 69 lists the Flash memory configuration for each device in the Z8 Encore! F0830 Series. Figures 14 through 18 display the memory arrangements for each Flash memory size.

| Table 69. Z8 Encore! F0830 | Series Flash Memory | Configuration |

|----------------------------|---------------------|---------------|

|----------------------------|---------------------|---------------|

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F123x     | 12 (12,288)              | 24          | 0000H-2FFFH                    | 1536                         |

| Z8F083x     | 8 (8196)                 | 16          | 0000H-1FFFH                    | 1024                         |

| Z8F043x     | 4 (4096)                 | 8           | 0000H-0FFFH                    | 512                          |

| Z8F023x     | 2 (2048)                 | 4           | 0000H-07FFH                    | 512                          |

| Z8F013x     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

Figure 14. 1K Flash with NVDS

PS025113-1212 Flash Memory

Table 83. Trim Bit Address Space

| Function                      |

|-------------------------------|

| ADC reference voltage         |

| ADC and comparator            |

| Internal Precision Oscillator |

| Oscillator and VBO            |

| ClkFltr                       |

|                               |

Table 84. Trim Option Bits at 0000H (ADCREF)

| Bit                                             | 7                             | 6  | 5       | 4        | 3 | 2 1 0 |  |  |  |  |

|-------------------------------------------------|-------------------------------|----|---------|----------|---|-------|--|--|--|--|

| Field                                           |                               | Al | CREF_TR | Reserved |   |       |  |  |  |  |

| RESET                                           |                               |    | U       | U        |   |       |  |  |  |  |

| R/W                                             |                               |    | R/W     |          |   | R/W   |  |  |  |  |

| Address                                         | Information Page Memory 0020H |    |         |          |   |       |  |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |    |         |          |   |       |  |  |  |  |

| Bit         | Description                                            |

|-------------|--------------------------------------------------------|

| [7:3]       | ADC Reference Voltage Trim Byte                        |

| ADCREF_TRIM | Contains trimming bits for ADC reference voltage.      |

| [2:0]       | Reserved                                               |

|             | These bits are reserved and must be programmed to 111. |

**Note:** The bit values used in Table 84 are set at the factory; no calibration is required.

### Table 85. Trim Option Bits at 0001H (TADC\_COMP)

| Bit       | 7                                               | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------|-------------------------------------------------|-----------------|---|---|---|---|---|---|--|--|--|

| Field     | Reserved                                        |                 |   |   |   |   |   |   |  |  |  |

| RESET     | U                                               | U U U U U U U U |   |   |   |   |   |   |  |  |  |

| R/W       | R/W R/W R/W R/W R/W R/W R/W                     |                 |   |   |   |   |   |   |  |  |  |

| Address   | Information Page Memory 0021H                   |                 |   |   |   |   |   |   |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                 |   |   |   |   |   |   |  |  |  |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | Reserved Altering this register may result in incorrect device operation. |

138

Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

2. Use as few unique addresses as possible to optimize the impact of refreshing.

PS025113-1212 NVDS Code Interface

- Watchdog Timer reset

- Asserting the  $\overline{RESET}$  pin Low to initiate a reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a system reset

### **OCD Data Format**

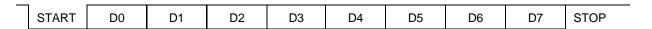

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 start bit, 8 data bits (least-significant bit first) and 1 stop bit. See Figure 23.

Figure 23. OCD Data Format

### OCD Autobaud Detector/Generator

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an autobaud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits low (one Start bit plus 7 data bits), framed between high bits. The autobaud detector measures this period and sets the OCD baud rate generator accordingly.

The autobaud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 94 lists minimum and recommended maximum baud rates for sample crystal frequencies.

Table 94. OCD Baud-Rate Limits

| System Clock<br>Frequency<br>(MHz) | Recommended<br>Maximum Baud Rate<br>(kbps) | Recommended<br>Standard PC Baud Rate<br>(bps) | Minimum Baud Rate<br>(kbps) |

|------------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                               | 2500.0                                     | 1,843,200                                     | 39                          |

| 1.0                                | 125.0                                      | 115,200                                       | 1.95                        |

| 0.032768 (32 KHz)                  | 4.096                                      | 2400                                          | 0.064                       |

PS025113-1212 Operation

Table 113. eZ8 CPU Instruction Summary (Continued)

| Assembly       |                                     |       | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|----------------|-------------------------------------|-------|-------------|---------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic       | Symbolic Operation                  | dst   | src         | (Hex)         | С | Z | S   | ٧   | D | Н |         |        |

| LDX dst, src   | dst ← src                           | r     | ER          | 84            | _ | _ | _   | _   | _ | _ | 3       | 2      |

|                |                                     | lr    | ER          | 85            | = |   |     |     |   |   | 3       | 3      |

|                |                                     | R     | IRR         | 86            | = |   |     |     |   |   | 3       | 4      |

|                |                                     | IR    | IRR         | 87            | _ |   |     |     |   |   | 3       | 5      |

|                |                                     | r     | X(rr)       | 88            | _ |   |     |     |   |   | 3       | 4      |

|                |                                     | X(rr) | r           | 89            | _ |   |     |     |   |   | 3       | 4      |

|                |                                     | ER    | r           | 94            | _ |   |     |     |   |   | 3       | 2      |

|                |                                     | ER    | lr          | 95            | _ |   |     |     |   |   | 3       | 3      |

|                |                                     | IRR   | R           | 96            | _ |   |     |     |   |   | 3       | 4      |

|                |                                     | IRR   | IR          | 97            | _ |   |     |     |   |   | 3       | 5      |

|                |                                     | ER    | ER          | E8            | _ |   |     |     |   |   | 4       | 2      |

|                |                                     | ER    | IM          | E9            | _ |   |     |     |   |   | 4       | 2      |

| LEA dst, X(src | ) dst ← src + X                     | r     | X(r)        | 98            | _ | _ | _   | _   | _ | _ | 3       | 3      |

|                |                                     | rr    | X(rr)       | 99            | _ |   |     |     |   |   | 3       | 5      |

| MULT dst       | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR    |             | F4            | - | - | -   | -   | - | - | 2       | 8      |

| NOP            | No operation                        |       |             | 0F            | _ | _ | _   | _   | _ | _ | 1       | 2      |

| OR dst, src    | dst ← dst OR src                    | r     | r           | 42            | _ | * | *   | 0   | _ | _ | 2       | 3      |

|                |                                     | r     | lr          | 43            | _ |   |     |     |   |   | 2       | 4      |

|                |                                     | R     | R           | 44            | _ |   |     |     |   |   | 3       | 3      |

|                |                                     | R     | IR          | 45            | _ |   |     |     |   |   | 3       | 4      |

|                |                                     | R     | IM          | 46            | _ |   |     |     |   |   | 3       | 3      |

|                |                                     | IR    | IM          | 47            | _ |   |     |     |   |   | 3       | 4      |

| ORX dst, src   | dst ← dst OR src                    | ER    | ER          | 48            | _ | * | *   | 0   | _ | - | 4       | 3      |

|                |                                     | ER    | IM          | 49            | = |   |     |     |   |   | 4       | 3      |

| POP dst        | dst ← @SP                           | R     |             | 50            | _ | _ | _   | _   | _ | _ | 2       | 2      |

|                | SP ← SP + 1                         | IR    |             | 51            | _ |   |     |     |   |   | 2       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

**Table 116. DC Characteristics (Continued)**

|                   |                              | $T_A = 0$ | °C to - | to +70°C $T_A = -40$ °C to +105°C |     |                  |      |       |                                |

|-------------------|------------------------------|-----------|---------|-----------------------------------|-----|------------------|------|-------|--------------------------------|

| Symbol            | Parameter                    | Min       | Тур     | Max                               | Min | Тур              | Max  | Units | Conditions                     |

| I <sub>LED</sub>  | Controlled                   |           |         |                                   | 1.5 | 3                | 4.5  | mA    | See GPIO section on            |

|                   | Current Drive                |           |         |                                   | 2.8 | 7                | 10.5 | mA    | LED description                |

|                   |                              |           |         |                                   | 7.8 | 13               | 19.5 | mΑ    | -                              |

|                   |                              |           |         |                                   | 12  | 20               | 30   | mA    | -                              |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance |           |         |                                   | -   | 8.0 <sup>2</sup> | _    | pF    | TBD                            |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance       |           |         |                                   | -   | 8.0 <sup>2</sup> | -    | pF    | TBD                            |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance      |           |         |                                   | -   | 9.5 <sup>2</sup> | _    | pF    | TBD                            |

| I <sub>PU</sub>   | Weak Pull-up<br>Current      |           |         |                                   | 50  | 120              | 220  | μΑ    | V <sub>DD</sub> = 2.7 - 3.6V   |

| ICCH <sup>3</sup> | Supply Current in HALT Mode  |           |         |                                   |     | TBD              |      | mA    | TBD                            |

| ICCS              | Supply Current in STOP Mode  |           |         | 2                                 |     |                  | 8    | μΑ    | Without Watchdog Timer running |

### Notes:

- 1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

- 2. These values are provided for design guidance only and are not tested in production.

- 3. See Figure 31 for HALT Mode current.

PS025113-1212 DC Characteristics

**Table 117. AC Characteristics (Continued)**

|                      |                                                  |     | 7 to 3.6V<br>to +70°C | T <sub>A</sub> = - | .7 to 3.6V<br>-40°C to<br>05°C |       |                           |  |

|----------------------|--------------------------------------------------|-----|-----------------------|--------------------|--------------------------------|-------|---------------------------|--|

| Symbol               | Parameter                                        | Min | Max                   | Min                | Max                            | Units | Conditions                |  |

| T <sub>XINR</sub>    | System Clock Rise<br>Time                        |     |                       | -                  | 3                              | ns    | T <sub>CLK</sub> = 50 ns  |  |

| T <sub>XINF</sub>    | System Clock Fall Time                           |     |                       | -                  | 3                              | ns    | T <sub>CLK</sub> = 50 ns  |  |

| T <sub>XTALSET</sub> | Crystal Oscillator<br>Setup Time                 |     |                       | -                  | 30,000                         | cycle | Crystal oscillator cycles |  |

| T <sub>IPOSET</sub>  | Internal Precision<br>Oscillator Startup<br>Time |     |                       | -                  | 25                             | μs    | Startup time after enable |  |

| T <sub>WDTSET</sub>  | WDT Startup Time                                 |     |                       | _                  | 50                             | μs    | Startup time after reset  |  |

# On-Chip Peripheral AC and DC Electrical Characteristics

Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                  |                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | $T_A = -40$ °C to<br>+105°C |                  |      |       |                                                                                                          |  |

|------------------|---------------------------------------------------------------------------|-------------------------------|-----|-----|-----------------------------|------------------|------|-------|----------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                                                 | Min                           | Тур | Max | Min                         | Typ <sup>1</sup> | Max  | Units | Conditions                                                                                               |  |

| V <sub>POR</sub> | Power-On Reset<br>Voltage Threshold                                       |                               |     |     | 2.20                        | 2.45             | 2.70 | V     | V <sub>DD</sub> = V <sub>POR</sub><br>(default VBO trim)                                                 |  |

| V <sub>VBO</sub> | Voltage Brown-Out<br>Reset Voltage<br>Threshold                           |                               |     |     | 2.15                        | 2.40             | 2.65 | V     | V <sub>DD</sub> = V <sub>VBO</sub><br>(default VBO trim)                                                 |  |

|                  | V <sub>POR</sub> to V <sub>VBO</sub><br>hysteresis                        |                               |     |     |                             | 50               | 75   | mV    |                                                                                                          |  |

|                  | Starting V <sub>DD</sub><br>voltage to ensure<br>valid Power-On<br>Reset. |                               |     |     | -                           | V <sub>SS</sub>  | _    | V     |                                                                                                          |  |

| T <sub>ANA</sub> | Power-On Reset<br>Analog Delay                                            |                               |     |     | -                           | 50               | -    | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub><br>Digital Reset delay<br>follows T <sub>ANA</sub> |  |

Note: <sup>1</sup>Data in the typical column is from characterization at 3.3 V and 0°C. These values are provided for design guidance only and are not tested in production.

### **Low Power Control**

For more information about the Power Control Register, see the <u>Power Control Register</u> <u>Definitions</u> section on page 31.

**Hex Address: F80**

Table 151. Power Control Register 0 (PWRCTL0)

| Bit     | 7        | 6    | 5   | 4   | 3        | 2        | 1    | 0        |  |  |

|---------|----------|------|-----|-----|----------|----------|------|----------|--|--|

| Field   | Reserved |      |     | VBO | Reserved | Reserved | COMP | Reserved |  |  |

| RESET   | 1        | 0    | 0   | 0   | 1        | 0        | 0    | 0        |  |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W      | R/W      | R/W  | R/W      |  |  |

| Address |          | F80H |     |     |          |          |      |          |  |  |

Hex Address: F81

This address range is reserved.

# **LED Controller**

For more information about the LED Drive registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

**Hex Address: F82**

**Table 152. LED Drive Enable (LEDEN)**

| Bit     | 7   | 6    | 5   | 4    | 3      | 2   | 1   | 0   |  |

|---------|-----|------|-----|------|--------|-----|-----|-----|--|

| Field   |     |      |     | LEDE | N[7:0] |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0    | 0      | 0   | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W  | R/W    | R/W | R/W | R/W |  |

| Address |     | F82H |     |      |        |     |     |     |  |

PS025113-1212 Low Power Control

**Hex Address: FC5**

Table 162. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| Field   | PA7ENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0      | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | FC5H   |         |        |        |        |        |        |        |

**Hex Address: FC6**

Table 163. Interrupt Request 2 Register (IRQ2)

| Bit     | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|---------|-----|------|-------|-----|------|------|------|------|

| Field   |     | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| Address |     | FC6H |       |     |      |      |      |      |

**Hex Address: FC7**

Table 164. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |  |

|---------|-----|------|-------|-----|-------|-------|-------|-------|--|--|

| Field   |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |  |  |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |     | FC7H |       |     |       |       |       |       |  |  |

**Hex Address: FC8**

Table 165. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |

|---------|-----|------|-------|-----|-------|-------|-------|-------|--|

| Field   |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |  |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |

| Address |     | FC8H |       |     |       |       |       |       |  |

PS025113-1212 Interrupt Controller

### **Trim Bit Control**

For more information about the Trim Bit Control registers, see the <u>Flash Option Bit Control Register Definitions</u> section on page 126.

**Hex Address: FF6**

Table 189. Trim Bit Address Register (TRMADR)

| Bit     | 7   | 6    | 5      | 4              | 3           | 2         | 1   | 0   |

|---------|-----|------|--------|----------------|-------------|-----------|-----|-----|

| Field   |     |      | TRMADE | R - Trim Bit A | ddress (00H | H to 1FH) |     |     |

| RESET   | 0   | 0    | 0      | 0              | 0           | 0         | 0   | 0   |

| R/W     | R/W | R/W  | R/W    | R/W            | R/W         | R/W       | R/W | R/W |

| Address |     | FF6H |        |                |             |           |     |     |

**Hex Address: FF7**

Table 190. Trim Bit Data Register (TRMDR)

| Bit     | 7   | 6    | 5   | 4         | 3            | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----------|--------------|-----|-----|-----|--|

| Field   |     |      |     | TRMDR - T | rim Bit Data |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0         | 0            | 0   | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W       | R/W          | R/W | R/W | R/W |  |

| Address |     | FF7H |     |           |              |     |     |     |  |

# **Flash Memory Controller**

For more information about the Flash Control registers, see the <u>Flash Control Register</u> <u>Definitions</u> section on page 118.

**Hex Address: FF8**

Table 191. Flash Control Register (FCTL)

| Bit     | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|------|---|---|----|----|---|---|---|

| Field   |      |   |   | FC | MD |   |   |   |

| RESET   | 0    | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W     | W    | W | W | W  | W  | W | W | W |

| Address | FF8H |   |   |    |    |   |   |   |

PS025113-1212 Trim Bit Control

**Hex Address: FF8**

Table 192. Flash Status Register (FSTAT)

| Bit     | 7    | 6     | 5 | 4     | 3 | 2 | 1 | 0 |  |  |

|---------|------|-------|---|-------|---|---|---|---|--|--|

| Field   | Rese | erved |   | FSTAT |   |   |   |   |  |  |

| RESET   | 0    | 0     | 0 | 0     | 0 | 0 | 0 | 0 |  |  |

| R/W     | R    | R     | R | R     | R | R | R | R |  |  |

| Address |      | FF8H  |   |       |   |   |   |   |  |  |

**Hex Address: FF9**

The Flash Page Select Register is shared with the Flash Sector Protect Register.

Table 193. Flash Page Select Register (FPS)

| Bit     | 7       | 6    | 5   | 4   | 3    | 2   | 1   | 0   |

|---------|---------|------|-----|-----|------|-----|-----|-----|

| Field   | INFO_EN |      |     |     | PAGE |     |     |     |

| RESET   | 0       | 0    | 0   | 0   | 0    | 0   | 0   | 0   |

| R/W     | R/W     | R/W  | R/W | R/W | R/W  | R/W | R/W | R/W |

| Address |         | FF9H |     |     |      |     |     |     |

**Table 194. Flash Sector Protect Register (FPROT)**

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |  |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address |        | FF9H   |        |        |        |        |        |        |  |  |

**Hex Address: FFA**

Table 195. Flash Frequency High Byte Register (FFREQH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------|-----|-----|-----|-----|-----|-----|

| Field   |     |      |     | FFR | EQH |     |     |     |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | FFAH |     |     |     |     |     |     |