Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0230sj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| Electrical Characteristics 1                              | 184 |

|-----------------------------------------------------------|-----|

| Absolute Maximum Ratings 1                                | 184 |

| DC Characteristics 1                                      | 185 |

| AC Characteristics 1                                      | 189 |

| On-Chip Peripheral AC and DC Electrical Characteristics 1 | 190 |

| General Purpose I/O Port Input Data Sample Timing 1       | 195 |

| General Purpose I/O Port Output Timing 1                  | 196 |

| On-Chip Debugger Timing 1                                 | 197 |

| Packaging 1                                               | 199 |

| Ordering Information                                      | 200 |

| Part Number Suffix Designations 2                         | 205 |

| Appendix A. Register Tables                               | 208 |

| General Purpose RAM                                       | 208 |

| Timer 0                                                   | 208 |

| Analog-to-Digital Converter                               | 213 |

| Low Power Control                                         | 216 |

| LED Controller                                            | 216 |

| Oscillator Control                                        | 217 |

| Comparator 0                                              | 218 |

| Interrupt Controller                                      | 218 |

| GPIO Port A 2                                             | 222 |

| Watchdog Timer                                            | 226 |

| Trim Bit Control                                          | 228 |

| Flash Memory Controller    2                              | 228 |

| Index                                                     | 231 |

| Customer Support                                          | 239 |

|                                                           |     |

## ix

# **Signal Descriptions**

Table 4 describes the Z8 Encore! F0830 Series signals. See the <u>Pin Configurations</u> section on page 7 to determine the signals available for each specific package style.

| Signal<br>Mnemonic                             | I/O       | Description                                                                                                                     |

|------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose                                | I/O Ports | s A–D                                                                                                                           |

| PA[7:0]                                        | I/O       | Port A. These pins are used for general purpose I/O.                                                                            |

| PB[7:0]                                        | I/O       | Port B. These pins are used for general purpose I/O. PB6 and PB7 are available only in those devices without an ADC.            |

| PC[7:0]                                        | I/O       | Port C. These pins are used for general purpose I/O.                                                                            |

| PD[0]                                          | I/O       | Port D. This pin is used for general purpose output only.                                                                       |

| Note: PB6 and PB7<br>placed by AV <sub>I</sub> |           | available in 28-pin packages without ADC. In 28-pin packages with ADC, they are re- $^{\prime}_{\rm SS}$                        |

| Timers                                         |           |                                                                                                                                 |

| T0OUT/T1OUT                                    | 0         | Timer output 0–1. These signals are the output from the timers.                                                                 |

| T0OUT/T1OUT                                    | 0         | Timer complement output 0–1. These signals are output from the timers in PWM DUAL OUTPUT Mode.                                  |

| T0IN/T1IN                                      | I         | Timer Input 0–1. These signals are used as the capture, gating and counte inputs. The T0IN signal is multiplexed T0OUT signals. |

| Comparator                                     |           |                                                                                                                                 |

| CINP/CINN                                      | I         | Comparator inputs. These signals are the positive and negative inputs to the comparator.                                        |

| COUT                                           | 0         | Comparator output. This is the output of the comparator.                                                                        |

| Analog                                         |           |                                                                                                                                 |

| ANA[7:0]                                       | I         | Analog port. These signals are used as inputs to the analog-to-digital converter (ADC).                                         |

| V <sub>REF</sub>                               | I/O       | Analog-to-digital converter reference voltage input.                                                                            |

|                                                |           | <b>Note:</b> When configuring ADC using external $V_{REF}$ , PB5 is used as $V_{REF}$ in 28-pin package.                        |

|                                                |           | nals are available only in the 28-pin packages with ADC. They are replaced by PB6 ages without ADC.                             |

## Table 4. Signal Descriptions

| Signal<br>Mnemonic | I/O | Description                                                                                                                                                                                                                                                                   |

|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillators        |     |                                                                                                                                                                                                                                                                               |

| X <sub>IN</sub>    | I   | External crystal input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| X <sub>OUT</sub>   | 0   | External crystal output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |

| Clock Input        |     |                                                                                                                                                                                                                                                                               |

| CLK <sub>IN</sub>  | Ι   | Clock input signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |

| LED Drivers        |     |                                                                                                                                                                                                                                                                               |

| LED                | 0   | Direct LED drive capability. All Port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |

| On-Chip Debugger   | •   |                                                                                                                                                                                                                                                                               |

| DBG                | I/O | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |

|                    |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull-up resistor to ensure proper operation.                                                                                                                                                               |

| Reset              |     |                                                                                                                                                                                                                                                                               |

| RESET              | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                            |

| Power Supply       |     |                                                                                                                                                                                                                                                                               |

| V <sub>DD</sub>    | Ι   | Digital power supply.                                                                                                                                                                                                                                                         |

| AV <sub>DD</sub>   | I   | Analog power supply.                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>    | I   | Digital ground.                                                                                                                                                                                                                                                               |

| AV <sub>SS</sub>   | I   | Analog ground.                                                                                                                                                                                                                                                                |

|                    |     | gnals are available only in the 28-pin packages with ADC. They are replaced by PB6 kages without ADC.                                                                                                                                                                         |

## Table 4. Signal Descriptions (Continued)

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# Reset and Stop Mode Recovery

The reset controller in the Z8 Encore! F0830 Series controls RESET and Stop Mode Recovery operations. In a typical operation, the following events can cause a reset:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash option bit to initiate a reset)

- External RESET pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-Chip Debugger initiated reset (OCDCTL[0] set to 1)

When the device is in STOP Mode, a Stop Mode Recovery event is initiated by either of the following occurrences:

- A Watchdog Timer time-out

- A GPIO port input pin transition on an enabled Stop Mode Recovery source

The VBO circuitry on the device generates a VBO reset when the supply voltage drops below a minimum safe level.

# **Reset Types**

The Z8 Encore! F0830 Series provides different types of Reset operations. Stop Mode Recovery is considered a form of reset. Table 9 lists the types of resets and their operating characteristics. The duration of a system reset is longer if the external crystal oscillator is enabled by the Flash option bits; the result is additional time for oscillator startup.

## 32

**Note:** This register is only reset during a Power-On Reset sequence. Other system reset events do not affect it.

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                | 6             | 5           | 4            | 3          | 2        | 1    | 0        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|--------------|------------|----------|------|----------|

| Field       |                                                                                                                                                                                                                                                                                                                                                                  | Reserved      |             | VBO          | Reserved   | Reserved | COMP | Reserved |

| RESET       | 1                                                                                                                                                                                                                                                                                                                                                                | 0             | 0           | 0            | 1          | 0        | 0    | 0        |

| R/W         | R/W                                                                                                                                                                                                                                                                                                                                                              | R/W           | R/W         | R/W          | R/W        | R/W      | R/W  | R/W      |

| Address     |                                                                                                                                                                                                                                                                                                                                                                  | ·             |             | F8           | 80H        |          |      |          |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                       | n             |             |              |            |          |      |          |

| [7:5]       | Reserved<br>These regis                                                                                                                                                                                                                                                                                                                                          | sters are res | erved and n | nust be proo | grammed to | 000.     |      |          |

| [4]<br>VBO  | Voltage Brown-Out detector disable<br>This bit takes only effect when the VBO_AO Flash option bit is disabled. In STOP Mode, VBO<br>is always disabled when the VBO_AO Flash option bit is disabled. To learn more about the<br>VBO_AO Flash option bit function, see the <u>Flash Option Bits</u> chapter on page 124.<br>0 = VBO enabled.<br>1 = VBO disabled. |               |             |              |            |          |      | bout the |

| [3]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                             |               |             |              |            |          |      |          |

| [2]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                             |               |             |              |            |          |      |          |

| [1]<br>COMP | Comparator Disable<br>0 = Comparator is enabled.<br>1 = Comparator is disabled.                                                                                                                                                                                                                                                                                  |               |             |              |            |          |      |          |

| [0]         | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                       | eserved and   | must be pr  | ogrammed t   | to 0.      |          |      |          |

### Table 14. Power Control Register 0 (PWRCTL0)

>

# LED Drive Enable Register

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|---------|-----|-----|-----|------|--------|-----|-----|-----|

| Field   |     |     |     | LEDE | N[7:0] |     |     |     |

| RESET   | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Address |     |     |     | F8   | 2H     |     |     |     |

| Bit   | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | LED Drive Enable                                                                                                                                                           |

| LEDEN | These bits determine which Port C pins are connected to an internal current sink.<br>0 = Tristate the Port C pin.<br>1= Connect controlled current sink to the Port C pin. |

# LED Drive Level High Register

The LED Drive Level High Register, shown in Table 32, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7   | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|---------|-----|-----|-----|

| Field   |     |     |     | LEDLV | LH[7:0] |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Address |     |     |     | F8    | 3H      |     |     |     |

## Bit Description

[7:0] LED Level High Bits

LEDLVLH {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3mA.

01= 7 mA.

10= 13mA.

11= 20mA.

# **Shared Interrupt Select Register**

The shared interrupt select (IRQSS) register determines the source of the PADxS interrupts. See Table 48. The shared interrupt select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit     | 7        | 6     | 5   | 4   | 3    | 2     | 1   | 0   |

|---------|----------|-------|-----|-----|------|-------|-----|-----|

| Field   | Reserved | PA6CS |     |     | Rese | erved |     |     |

| RESET   | 0        | 0     | 0   | 0   | 0    | 0     | 0   | 0   |

| R/W     | R/W      | R/W   | R/W | R/W | R/W  | R/W   | R/W | R/W |

| Address |          |       |     | FC  | EH   |       |     |     |

### Table 48. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                                         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]          | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt caused by PA6CS interrupt request.</li> <li>1 = The comparator is used for the interrupt caused by PA6CS interrupt request.</li> </ul> |

| [5:0]        | <b>Reserved</b><br>These registers are reserved and must be programmed to 000000.                                                                                                                                   |

is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for COUNTER Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COUNTER Mode

- Select either the rising edge or falling edge of the timer input signal for the count. This selection also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer reload in COUNTER Mode, counting always begins at the reset value 0001H. In COUNTER Mode, the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of timer input transitions is calculated with the following equation:

Counter Mode Timer Input Transitions = Current Count Value – Start Value

### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER Mode, the timer counts the input transitions from the analog comparator output. The TPOL bit in the Timer Control Register determines whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPARATOR COUNTER Mode, the prescaler is disabled.

# **Comparator Control Register Definitions**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference. The GPIO pin is always used as positive comparator input.

| Bit             | 7                                                                                                                                                                                       | 6                     | 5            | 4          | 3          | 2        | 1 | 0 |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|------------|------------|----------|---|---|--|--|--|

| Field           | Reserved                                                                                                                                                                                | INNSEL                |              | REF        | Rese       | Reserved |   |   |  |  |  |

| RESET           | 0                                                                                                                                                                                       | 0                     | 0            | 1          | 0          | 1 0      |   |   |  |  |  |

| R/W             | R/W                                                                                                                                                                                     | R/W R/W R/W R/W R/W R |              |            |            |          |   |   |  |  |  |

| Address         |                                                                                                                                                                                         |                       |              | F9         | 0H         |          |   |   |  |  |  |

| Bit             | Descriptio                                                                                                                                                                              | n                     |              |            |            |          |   |   |  |  |  |

| [7]             | Reserved<br>This bit is re                                                                                                                                                              | •                     |              |            |            |          |   |   |  |  |  |

| [6]<br>INNSEL   | <b>Signal Select for Negative Input</b><br>0 = internal reference disabled, GPIO pin used as negative comparator input.<br>1 = internal reference enabled as negative comparator input. |                       |              |            |            |          |   |   |  |  |  |

| [5:2]<br>REFLVL |                                                                                                                                                                                         |                       |              |            |            |          |   |   |  |  |  |

| [1:0]           | Reserved<br>These bits a                                                                                                                                                                | are reserved          | l and must b | e programm | ned to 00. |          |   |   |  |  |  |

## Table 68. Comparator Control Register (CMP0)

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| 1FFFH          |           | <br>Page 15 | 1FFFH<br>1E00H |

|----------------|-----------|-------------|----------------|

|                | Sector 7  | Page 14     | 1DFFH<br>1C00H |

| 1C00H<br>18FFH |           | <br>Page 13 | 1BFFH<br>1A00H |

|                | Sector 6  | <br>Page 12 | 19FFH<br>1800H |

| 1800H<br>17FFH |           | <br>Page 11 | 17FFH<br>1600H |

| 1400H          | Sector 5  | <br>Page 10 | 15FFH<br>1400H |

| 13FFH          |           | <br>Page 9  | 13FFH<br>1200H |

|                | Sector 4  | <br>Page 8  | 11FFH          |

| 1C00H<br>0FFFH | Sector 3  | <br>Page 7  | 1C00H<br>0FFFH |

| 0C00H          | Seciol 3  | Page 6      | 0E00H<br>0DFFH |

| 0BFFH          | On star 0 | <br>Page 5  | 0C00H<br>0BFFH |

| 0800H          | Sector 2  | <br>Page 4  | 0A00H<br>09FFH |

| 07FFH          | Sector 1  | Page 3      | 0800H<br>07FFH |

| 0400H          | Sector    | <br>Page 2  | 0600H<br>05FFH |

| 03FFH          | Sector 0  | Page 1      | 0400H<br>03FFH |

| 0000H          |           | <br>Page 0  | 0200H<br>0100H |

|                |           |             | 0000H          |

Figure 17. 8K Flash with NVDS

110

# Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

# Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

## Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

- The Flash Sector Protect Register is ignored for programming and Erase operations.

- Programming operations are not limited to the page selected in the page select register.

- Bits in the Flash Sector Protect Register can be written to one or zero.

- The second write of the page select register to unlock the Flash Controller is not necessary.

- The page select register can be written when the Flash Controller is unlocked.

- The mass erase command is enabled through the Flash Control Register

**Caution:** For security reasons, Flash Controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the Flash Controller must go through the unlock sequence again to select another page.

# **NVDS Operational Requirements**

The device uses a 12KB Flash memory space, despite the maximum specified Flash size of 8KB (with the exception of 12KB mode with non-NVDS). User code accesses the lower 8KB of Flash, leaving the upper 4KB for proprietary (for Zilog-only) memory. The NVDS is implemented by using this proprietary memory space for special-purpose routines and for the data required by these routines, which are factory-programmed and cannot be altered by the user. The NVDS operation is described in detail in *the* <u>Nonvolatile</u> <u>Data Storage</u> *chapter on page 134*.

The NVDS routines are triggered by a user code: CALL into proprietary memory. Code executing from this proprietary memory must be able to read and write other locations within proprietary memory. User code must not be able to read or write proprietary memory.

# **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 119

Flash Status Register: see page 120

Flash Page Select Register: see page 121

Flash Sector Protect Register: see page 122

Flash Frequency High and Low Byte Registers: see page 123

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>XTLDIS | <ul> <li>State of the Crystal Oscillator at Reset</li> <li>This bit enables only the crystal oscillator. Selecting the crystal oscillator as the system clock must be performed manually.</li> <li>0 = The crystal oscillator is enabled during reset, resulting in longer reset timing.</li> <li>1 = The crystal oscillator is disabled during reset, resulting in shorter reset timing.</li> </ul> |

| [3:0]         | <b>Reserved</b> These bits are reserved and must be programmed to 1111.                                                                                                                                                                                                                                                                                                                              |

# **Trim Bit Address Space**

All available trim bit addresses and their functions are listed in Tables 83 through 90.

130

### Table 83. Trim Bit Address Space

| Address | Function                      |

|---------|-------------------------------|

| 00h     | ADC reference voltage         |

| 01h     | ADC and comparator            |

| 02h     | Internal Precision Oscillator |

| 03h     | Oscillator and VBO            |

| 06h     | ClkFltr                       |

### Table 84. Trim Option Bits at 0000H (ADCREF)

| Bit       | 7                                               | 6                             | 5         | 4        | 3 | 2 | 0 |  |  |  |

|-----------|-------------------------------------------------|-------------------------------|-----------|----------|---|---|---|--|--|--|

| Field     |                                                 | Al                            | DCREF_TRI | Reserved |   |   |   |  |  |  |

| RESET     |                                                 |                               | U         | U        |   |   |   |  |  |  |

| R/W       |                                                 |                               | R/W       | R/W      |   |   |   |  |  |  |

| Address   |                                                 | Information Page Memory 0020H |           |          |   |   |   |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                               |           |          |   |   |   |  |  |  |

| Bit                  | Description                                                                          |

|----------------------|--------------------------------------------------------------------------------------|

| [7:3]<br>ADCREF_TRIM | ADC Reference Voltage Trim Byte<br>Contains trimming bits for ADC reference voltage. |

| [2:0]                | <b>Reserved</b><br>These bits are reserved and must be programmed to 111.            |

**Note:** The bit values used in Table 84 are set at the factory; no calibration is required.

| Bit                                             | 7        | 6         | 5     | 4           | 3           | 2    | 1   | 0   |  |  |  |

|-------------------------------------------------|----------|-----------|-------|-------------|-------------|------|-----|-----|--|--|--|

| Field                                           | Reserved |           |       |             |             |      |     |     |  |  |  |

| RESET                                           | U        | U         | U     | U           | U           | U    | U   | U   |  |  |  |

| R/W                                             | R/W      | R/W       | R/W   | R/W         | R/W         | R/W  | R/W | R/W |  |  |  |

| Address                                         |          |           | Infor | mation Page | e Memory 00 | 021H |     |     |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |          |           |       |             |             |      |     |     |  |  |  |

| Bit                                             | De       | scription |       |             |             |      |     |     |  |  |  |

### Table 85. Trim Option Bits at 0001H (TADC\_COMP)

| Bit   | Description                                                      |

|-------|------------------------------------------------------------------|

| [7:0] | Reserved                                                         |

|       | Altering this register may result in incorrect device operation. |

# **On-Chip Debugger**

The Z8 Encore! devices contain an integrated On-Chip Debugger (OCD) that provides the following advanced debugging features:

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

# Architecture

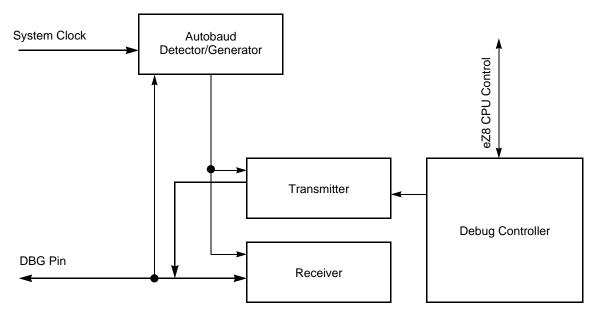

The On-Chip Debugger consists of four primary functional blocks: transmitter, receiver, autobaud detector/generator and debug controller. Figure 20 displays the architecture of the On-Chip Debugger.

Figure 20. On-Chip Debugger Block Diagram

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer Oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The Internal Precision Oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

# **Clock Failure Detection and Recovery**

## **Primary Oscillator Failure**

The Z8F04xA family devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer Oscillator to drive the system clock. The Watchdog Timer Oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer reset function outlined in the Watchdog Timer chapter of this document.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 KHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

## Watchdog Timer Failure

In the event of failure of a Watchdog Timer Oscillator, a similar nonmaskable interruptlike event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer Oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer Oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure is detected. A very slow system clock results in very slow detection times.

| Notation | Description           | Operand | Range                                                                                                                        |

|----------|-----------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| R        | Register              | Reg     | Reg. represents a number in the range of 00H to FFH                                                                          |

| RA       | Relative Address      | Х       | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction |

| rr       | Working Register Pair | RRp     | p = 0, 2, 4, 6, 8, 10, 12 or 14                                                                                              |

| RR       | Register Pair         | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                    |

| Vector   | Vector Address        | Vector  | Vector represents a number in the range of 00H to FFH                                                                        |

| Х        | Indexed               | #Index  | The register or register pair to be indexed is off-<br>set by the signed Index value (#Index) in a +127<br>to<br>-128 range. |

### Table 103. Notational Shorthand (Continued)

Table 104 contains additional symbols that are used throughout the instruction summary and instruction set description sections.

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

### Table 104. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.  $dst \leftarrow dst + src$

| Assembly         |                                                                                           | Address<br>Mode |     | Op<br>Code(s) | Flags |   |   |   |   |   | Fetch | Instr. |

|------------------|-------------------------------------------------------------------------------------------|-----------------|-----|---------------|-------|---|---|---|---|---|-------|--------|

| Mnemonic         | Symbolic Operation                                                                        | dst             | src | • •           |       | Ζ | S | ۷ | D | Н |       |        |

| AND dst, src     | $dst \gets dst \; AND \; src$                                                             | r               | r   | 52            | _     | * | * | 0 | _ | _ | 2     | 3      |

|                  |                                                                                           | r               | lr  | 53            | _     |   |   |   |   |   | 2     | 4      |

|                  |                                                                                           | R               | R   | 54            |       |   |   |   |   |   | 3     | 3      |

|                  |                                                                                           | R               | IR  | 55            | _     |   |   |   |   |   | 3     | 4      |

|                  |                                                                                           | R               | IM  | 56            | _     |   |   |   |   |   | 3     | 3      |

|                  |                                                                                           | IR              | IM  | 57            | _     |   |   |   |   |   | 3     | 4      |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER              | ER  | 58            | _     | * | * | 0 | _ | _ | 4     | 3      |

|                  |                                                                                           | ER              | IM  | 59            | _     |   |   |   |   |   | 4     | 3      |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |                 |     | 2F            | -     | _ | _ | _ | _ | _ | 1     | 2      |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r               |     | E2            | _     | * | * | 0 | _ | _ | 2     | 2      |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r               |     | E2            | _     | * | * | 0 | _ | _ | 2     | 2      |

| BRK              | Debugger Break                                                                            |                 |     | 00            | -     | _ | - | - | _ | _ | 1     | 1      |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r               |     | E2            | -     | * | * | 0 | - | - | 2     | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R               |     | D5            | Х     | * | * | 0 | - | - | 2     | 2      |

| BTJ p, bit, src, | if src[bit] = p                                                                           |                 | r   | F6            | -     | _ | - | - | _ | _ | 3     | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7            | _     |   |   |   |   |   | 3     | 4      |

| BTJNZ bit, src,  |                                                                                           |                 | r   | F6            | -     | - | - | - | - | - | 3     | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7            | _     |   |   |   |   |   | 3     | 4      |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |                 | r   | F6            | _     | - | _ | _ | - | - | 3     | 3      |

| dst              | $PC \gets PC + X$                                                                         |                 | Ir  | F7            |       |   |   |   |   |   | 3     | 4      |

| CALL dst         | $SP \leftarrow SP -\!\!\!\!\!-\!\!\!\!\!2$                                                | IRR             |     | D4            | _     | _ | - | - | _ | - | 2     | 6      |

|                  | @SP ← PC<br>PC ← dst                                                                      | DA              |     | D6            |       |   |   |   |   |   | 3     | 3      |

| CCF              | $C \leftarrow \sim C$                                                                     |                 |     | EF            | *     | _ | _ | _ | _ |   | 1     | 2      |

## Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

|                             | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     |         | = 2.7 to<br>0°C to + |     |        |                                                 |  |

|-----------------------------|----------------------------------------------------------------|-----|-----|---------|----------------------|-----|--------|-------------------------------------------------|--|

| Parameter                   | Min                                                            | Тур | Max | Min     | Тур                  | Max | Units  | Notes                                           |  |

| NVDS Byte Read<br>Time      |                                                                |     |     | 71      | -                    | 258 | μs     | Withsystemclockat<br>20MHz                      |  |

| NVDS Byte Pro-<br>gram Time |                                                                |     |     | 126     | -                    | 136 | μs     | Withsystemclockat<br>20MHz                      |  |

| Data Retention              |                                                                |     |     | 10      | _                    | _   | years  | 25°C                                            |  |

| Endurance                   |                                                                |     |     | 100,000 | -                    | -   | cycles | Cumulative write<br>cycles for entire<br>memory |  |

### Table 121. Nonvolatile Data Storage

**Note:** For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write can take up to 58 ms to complete.

### Table 122. Analog-to-Digital Converter Electrical Characteristics and Timing

|                  |                                                 | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |     |     |       |                |  |

|------------------|-------------------------------------------------|----------------------------------------------------------------|-----|-----|-------------------------------------------------------------------|-----|-----|-------|----------------|--|

| Symbol           | Parameter                                       | Min                                                            | Тур | Max | Min                                                               | Тур | Мах | Units | Conditions     |  |

|                  | Resolution                                      |                                                                |     |     | _                                                                 | 10  | _   | bits  |                |  |

|                  | Differential<br>Nonlinearity (DNL) <sup>1</sup> |                                                                |     |     | -1                                                                | -   | +4  | LSB   |                |  |

|                  | Integral<br>Nonlinearity (INL) <sup>1</sup>     |                                                                |     |     | -5                                                                | _   | +5  | LSB   |                |  |

|                  | Gain Error                                      |                                                                |     |     |                                                                   | 15  |     | LSB   |                |  |

|                  | Offset Error                                    |                                                                |     |     | -15                                                               | -   | 15  | LSB   | PDIP package   |  |

|                  | -                                               |                                                                |     |     | -9                                                                | _   | 9   | LSB   | Other packages |  |

| V <sub>REF</sub> | On chip reference                               |                                                                |     |     | 1.9                                                               | 2.0 | 2.1 | V     |                |  |

|                  | Active Power<br>Consumption                     |                                                                |     |     |                                                                   | 4   |     | mA    |                |  |

|                  | Power Down<br>Current                           |                                                                |     |     |                                                                   |     | 1   | μA    |                |  |

Note: <sup>1</sup>When the input voltage is lower than 20mV, the conversion error is out of spec.

193

>

## Hex Address: FFB

## Table 196. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|--------|---|---|---|---|---|---|---|--|--|--|

| Field   | FFREQL |   |   |   |   |   |   |   |  |  |  |

| RESET   | 0      |   |   |   |   |   |   |   |  |  |  |

| R/W     | R/W    |   |   |   |   |   |   |   |  |  |  |

| Address | FFBH   |   |   |   |   |   |   |   |  |  |  |