Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | •                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0231ph020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

### xi

| Figure 27. | Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$ Resistor |

|------------|-----------------------------------------------------------------------------------------------------|

| Figure 28. | Op Code Map Cell Description 180                                                                    |

| Figure 29. | First Op Code Map                                                                                   |

| Figure 30. | Second Op Code Map after 1FH 183                                                                    |

| Figure 31. | $I_{CC}$ Versus System Clock Frequency (HALT Mode) 187                                              |

| Figure 32. | I <sub>CC</sub> Versus System Clock Frequency (NORMAL Mode) 188                                     |

| Figure 33. | Port Input Sample Timing 195                                                                        |

| Figure 34. | GPIO Port Output Timing 196                                                                         |

| Figure 35. | On-Chip Debugger Timing 197                                                                         |

| Figure 36. | Flash Current Diagram                                                                               |

29

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                                                                                                                                                                                                                                                                          | 5           | 4            | 3         | 2        | 1 | 0 |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-----------|----------|---|---|--|--|--|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                           | STOP                                                                                                                                                                                                                                                                                                       | WDT         | EXT          |           | Reserved |   |   |  |  |  |

| RESET       | :                                                                                                                                                                                                                                                                                                                                                                                                                                             | See Table 13                                                                                                                                                                                                                                                                                               | 3           | 0            | 0         | 0        | 0 | 0 |  |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                                                                                                                                                                                                                                                                          | R           | R            | R         | R        | R | R |  |  |  |

| Address     | FF0H                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |             |              |           |          |   |   |  |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                |             |              |           |          |   |   |  |  |  |

| [7]<br>POR  | This bit is s                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>Power-On Reset Indicator</b><br>This bit is set to 1 if a Power-On Reset event occurs and is reset to 0, if a WDT time-out or Stop<br>Mode Recovery occurs. Reading this register also reset this bit to 0.                                                                                             |             |              |           |          |   |   |  |  |  |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>This bit is set to 1 if a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery is not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |                                                                                                                                                                                                                                                                                                            |             |              |           |          |   |   |  |  |  |

| [5]<br>WDT  | This bit is s<br>Recovery fr                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>Watchdog Timer Time-Out Indicator</b><br>This bit is set to 1 if a WDT time-out occurs. A Power-On Reset resets this pin. A Stop Mode<br>Recovery from a change in an input pin also resets this bit. Reading this register resets this bit.<br>This read must occur before clearing the WDT interrupt. |             |              |           |          |   |   |  |  |  |

| [4]<br>EXT  | <b>External Reset Indicator</b><br>If this bit is set to 1, a reset initiated by the external RESET pin occurred. A Power-On Reset or<br>a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                            |             |              |           |          |   |   |  |  |  |

| [3:0]       | Reserved<br>These regis                                                                                                                                                                                                                                                                                                                                                                                                                       | sters are res                                                                                                                                                                                                                                                                                              | erved and n | nust be prog | rammed to | 0000.    |   |   |  |  |  |

### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out                 | 0   | 1    | 1   | 0   |

### Port A–D Alternate Function Set 1 Subregisters

The Port A–D Alternate Function Set 1 Subregister, shown in Table 27, is accessed through the Port A–D Control Register by writing 07H to the Port A–D Address Register. The Alternate Function Set 1 subregisters select the alternate function available at a port pin. Alternate functions selected by setting or clearing bits in this register are defined in the <u>GPIO Alternate Functions</u> section on page 34.

Note:Alternate function selection on the port pins must also be enabled, as described in the PortA-D Alternate Function Subregisters section on page 42.

| Bit     | 7                                                                                     | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | PAFS17                                                                                | PAFS16 | PAFS15 | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |  |  |

| RESET   | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address | If 07H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |        |  |  |

| Dit     |                                                                                       |        |        |        |        |        |        |        |  |  |

#### Table 27. Port A–D Alternate Function Set 1 Subregisters (PxAFS1)

#### Bit Description

#### [7:0] Port Alternate Function Set 1

PAFS1x 0 = Port Alternate function selected as defined in Table 16 in GPIO Alternate Functions section.

> 1 = Port Alternate function selected as defined in Table 16 in GPIO Alternate Functions section.

Note: x indicates the specific GPIO port pin number (7–0).

# LED Drive Enable Register

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6    | 5   | 4    | 3      | 2   | 1   | 0   |  |  |

|---------|-----|------|-----|------|--------|-----|-----|-----|--|--|

| Field   |     |      |     | LEDE | N[7:0] |     |     |     |  |  |

| RESET   | 0   | 0    | 0   | 0    | 0      | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W  | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |

| Address |     | F82H |     |      |        |     |     |     |  |  |

| Bit   | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | LED Drive Enable                                                                                                                                                           |

| LEDEN | These bits determine which Port C pins are connected to an internal current sink.<br>0 = Tristate the Port C pin.<br>1= Connect controlled current sink to the Port C pin. |

# LED Drive Level High Register

The LED Drive Level High Register, shown in Table 32, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|--------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | LEDLVLH[7:0] |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     |              |     | F8  | 3H  |     |     |     |  |  |

### Bit Description

[7:0] LED Level High Bits

LEDLVLH {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3mA.

01= 7 mA.

10= 13mA.

11= 20mA.

### 96

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 60 through 62, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. This 24-bit value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate reload value; reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

| Bit         | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-------------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Field       | WDTU                                                                                          |      |      |      |      |      |      |      |  |  |

| RESET       | 0                                                                                             | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| R/W         | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| Address     | ress FF1H                                                                                     |      |      |      |      |      |      |      |  |  |

| Note: *A re | Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |  |  |

#### Table 60. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

| Bit         | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Field       | WDTH                                                                                          |      |      |      |      |      |      |      |

| RESET       | 0                                                                                             | 0    | 0    | 0    | 0    | 1    | 0    | 0    |

| R/W         | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |

| Address     | FF2H                                                                                          |      |      |      |      |      |      |      |

| Note: *A re | Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte, bits[15:8] of the 24-bit WDT reload value. |

## Sample Settling Time Register

The <u>Sample Settling</u> Time Register, shown in Table 66, is used to program a delay after the <u>SAMPLE/HOLD</u> signal is asserted and before the START signal is asserted; an ADC conversion then begins. The number of clock cycles required for settling will vary from system to system depending on the system clock period used. The system designer should program this register to contain the number of clocks required to meet a  $0.5 \mu s$  minimum settling time.

| Bit     | 7    | 6    | 5     | 4 | 3   | 2  | 1 | 0 |  |

|---------|------|------|-------|---|-----|----|---|---|--|

| Field   |      | Rese | erved |   | SST |    |   |   |  |

| RESET   |      | (    | )     |   | 1   | 1  | 1 | 1 |  |

| R/W     |      | F    | २     |   |     | R/ | W |   |  |

| Address | F74H |      |       |   |     |    |   |   |  |

### Table 66. Sample Settling Time (ADCSST)

| Bit          | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                  |

| [3:0]<br>SST | 0h–Fh = Sample settling time in number of system clock periods to meet 0.5 $\mu$ s minimum. |

# Flash Page Select Register

The Flash Page Select Register shares address space with the Flash Sector Protect Register. Unless the Flash Controller is locked and written with 5EH, any writes to this address will target the Flash Page Select Register.

The register selects one of the eight available Flash memory pages to be programmed or erased. Each Flash page contains 512-bytes of Flash memory. During a page erase operation, all Flash memory containing addresses with the most significant 7-bits within FPS[6:0] are chosen for program/erase operations.

| Bit     | 7       | 6   | 5    | 4   | 3   | 2   | 1   | 0   |

|---------|---------|-----|------|-----|-----|-----|-----|-----|

| Field   | INFO_EN |     | PAGE |     |     |     |     |     |

| RESET   | 0       | 0   | 0    | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W |

| Address | FF9H    |     |      |     |     |     |     |     |

### Table 74. Flash Page Select Register (FPS)

### Bit Description

### [7] Information Area Enable

INFO\_EN 0 = Information area is not selected.

1 = Information area is selected. The information area is mapped into the program memory address space at addresses FE00H through FFFFH.

# [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for page erase and page unlocking. Program memory address[15:9] = PAGE[6:0]. For Z8F04xx and Z8F02xx devices, the upper four bits must always be 0. For Z8F01xx devices, the upper five bits must always be 0.

| Description (Continued)                             |

|-----------------------------------------------------|

| Filter Select                                       |

| 2-bit selection for the clock filter mode.          |

| 00 = No filter.                                     |

| 01 = Filter low level noise on high level signal.   |

| 10 = Filter high level noise on low level signal.   |

| 11 = Filter both.                                   |

| dicates bit values 3–1; y indicates bit values 1–0. |

|                                                     |

**Note:** The bit values used in Table 89 are set at factory and no calibration is required.

| DlyCtl3, DlyCtl2,<br>DlyCtl1      | Low Noise Pulse<br>on High Signal (ns) | High Noise Pulse<br>on Low Signal (ns) |  |  |  |  |

|-----------------------------------|----------------------------------------|----------------------------------------|--|--|--|--|

| 000                               | 5                                      | 5                                      |  |  |  |  |

| 001                               | 7                                      | 7                                      |  |  |  |  |

| 010                               | 9                                      | 9                                      |  |  |  |  |

| 011                               | 11                                     | 11                                     |  |  |  |  |

| 100                               | 13                                     | 13                                     |  |  |  |  |

| 101                               | 17                                     | 17                                     |  |  |  |  |

| 110                               | 20                                     | 20                                     |  |  |  |  |

| 111                               | 25                                     | 25                                     |  |  |  |  |

| Note: The variation is about 30%. |                                        |                                        |  |  |  |  |

#### Table 90. ClkFlt Delay Control Definition

## **Byte Read**

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine ( $0 \times 2000$ ). At the return from the subroutine, the read byte resides in working register R0 and the read status byte resides in working register R1. The bit fields of this status byte are defined in Table 92. Additionally, the user code should pop the address byte off the stack.

The read routine uses 16 bytes of stack space in addition to the one byte of address pushed by the user code. Sufficient memory must be available for this stack usage.

Due to the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between  $71 \mu s$  and  $258 \mu s$  (assuming a 20MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return  $0 \times ff$ . Illegal read operations have a  $6 \mu s$  execution time.

The status byte returned by the NVDS read routine is zero for a successful read. If the status byte is nonzero, there is a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have an error.

| Bit              | 7                                                                                                                                                                                                                              | 6                                                                         | 5 | 4  | 3        | 2  | 1      | 0        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---|----|----------|----|--------|----------|

| Field            |                                                                                                                                                                                                                                | Reserved                                                                  |   | DE | Reserved | FE | IGADDR | Reserved |

| Default<br>Value | 0                                                                                                                                                                                                                              | 0                                                                         | 0 | 0  | 0        | 0  | 0      | 0        |

| Bit              | Description                                                                                                                                                                                                                    |                                                                           |   |    |          |    |        |          |

| [7:5]            | Reserved<br>These bits a                                                                                                                                                                                                       | <b>Reserved</b><br>These bits are reserved and must be programmed to 000. |   |    |          |    |        |          |

| [4]<br>DE        | <b>Data Error</b><br>When reading an NVDS address, if an error is found in the latest data corresponding to this NVDS address, this bit is set to 1. NVDS source code steps forward until it finds valid data at this address. |                                                                           |   |    |          |    |        |          |

| [3]              | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                           |                                                                           |   |    |          |    |        |          |

| [2]<br>FE        | Flash Error<br>If a Flash error is detected, this bit is set to 1.                                                                                                                                                             |                                                                           |   |    |          |    |        |          |

| [1]<br>IGADDR    | <b>Illegal Address</b><br>When NVDS byte reads from invalid addresses (those exceeding the NVDS array size) occur, this bit is set to 1.                                                                                       |                                                                           |   |    |          |    |        |          |

| [0]              | Reserved<br>This bit is reserved and must be programmed to 0.                                                                                                                                                                  |                                                                           |   |    |          |    |        |          |

Table 92. Read Status Byte

# Operation

The following section describes the operation of the On-Chip Debugging function.

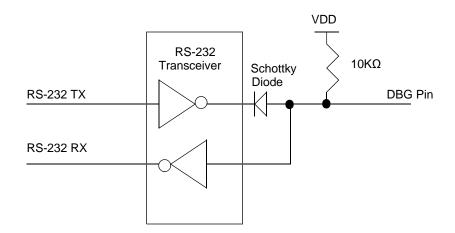

## **OCD** Interface

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, which means that transmission and data retrieval cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface between the Z8 Encore! F0830 Series products and the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figures 21 and 22. The recommended method is the buffered implementation depicted in Figure 22. The DBG pin must always be connected to  $V_{DD}$  through an external pull-up resistor.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

#### Figure 21. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

If the OCD receives a serial break (nine or more continuous bits low), the autobaud detector/generator resets. Reconfigure the autobaud detector/generator by sending 80H.

## **OCD Serial Errors**

The OCD can detect any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received Stop bit is Low)

- Transmit collision (simultaneous transmission by OCD and host detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long serial break back to the host and resets the autobaud detector/generator. A framing error or transmit collision may be caused by the host sending a serial break to the OCD. As a result of the open-drain nature of the interface, returning a serial break back to the host only extends the length of the serial break if the host releases the serial break early.

The host transmits a serial break on the DBG pin when first connecting to the Z8 Encore! F0830 Series devices or when recovering from an error. A serial break from the host resets the autobaud generator/detector, but does not reset the OCD Control Register. A serial break leaves the device in DEBUG Mode, if that is the current mode. The OCD is held in reset until the end of the serial break when the DBG pin returns high. Because of the opendrain nature of the DBG pin, the host can send a serial break to the OCD even if the OCD is transmitting a character.

## **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

| Clock Source                          | Characteristics                                                                                                                                | Required Setup                                                                                                                                                                                                                                                                                      |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal precision<br>RC oscillator   | <ul> <li>32.8 kHz or 5.53MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>                           | <ul> <li>Unlock and write to the Oscillator Con-<br/>trol Register (OSCCTL) to enable and<br/>select oscillator at either 5.53MHz or<br/>32.8 kHz</li> </ul>                                                                                                                                        |

| External crystal/res-<br>onator       | <ul> <li>32 kHz to 20MHz</li> <li>Very high accuracy (dependent on crystal or resonator used)</li> <li>Requires external components</li> </ul> | <ul> <li>Configure Flash option bits for correct<br/>external OSCILLATOR Mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator, wait for it to stabilize<br/>and select as system clock (if the<br/>XTLDIS option bit has been<br/>de-asserted, no waiting is required)</li> </ul> |

| External RC oscilla-<br>tor           | <ul> <li>32 kHz to 4MHz</li> <li>Accuracy dependent on external components</li> </ul>                                                          | <ul> <li>Configure Flash option bits for correct<br/>external OSCILLATOR Mode</li> <li>Unlock and write OSCCTL to enable<br/>crystal oscillator and select as system<br/>clock</li> </ul>                                                                                                           |

| External clock drive                  | <ul> <li>0 to 20MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul>                                                                                     |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Low power consumption</li> </ul>                     | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT oscillator is operating.</li> <li>Unlock and write to the Oscillator Con-<br/>trol Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>                                                                                       |

### Table 98. Oscillator Configuration and Selection

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a nonfunctioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

### **OSC Control Register Unlocking/Locking**

To write the Oscillator Control Register, unlock it by making two writes to the OSCCTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a Locked state. Any other sequence of Oscillator Control Register writes have no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer Oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The Internal Precision Oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## **Clock Failure Detection and Recovery**

### **Primary Oscillator Failure**

The Z8F04xA family devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer Oscillator to drive the system clock. The Watchdog Timer Oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer reset function outlined in the Watchdog Timer chapter of this document.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 KHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

### Watchdog Timer Failure

In the event of failure of a Watchdog Timer Oscillator, a similar nonmaskable interruptlike event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer Oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer Oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure is detected. A very slow system clock results in very slow detection times.

|                      |                                                  |     |                        |                                                                      | •      |       |                           |  |

|----------------------|--------------------------------------------------|-----|------------------------|----------------------------------------------------------------------|--------|-------|---------------------------|--|

|                      | Parameter                                        |     | .7 to 3.6V<br>to +70°C | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to<br>+105°C |        |       |                           |  |

| Symbol               |                                                  | Min | Max                    | Min                                                                  | Max    | Units | Conditions                |  |

| T <sub>XINR</sub>    | System Clock Rise<br>Time                        |     |                        | -                                                                    | 3      | ns    | T <sub>CLK</sub> = 50 ns  |  |

| T <sub>XINF</sub>    | System Clock Fall<br>Time                        |     |                        | -                                                                    | 3      | ns    | T <sub>CLK</sub> = 50 ns  |  |

| T <sub>XTALSET</sub> | Crystal Oscillator<br>Setup Time                 |     |                        | _                                                                    | 30,000 | cycle | Crystal oscillator cycles |  |

| T <sub>IPOSET</sub>  | Internal Precision<br>Oscillator Startup<br>Time |     |                        | _                                                                    | 25     | μs    | Startup time after enable |  |

| T <sub>WDTSET</sub>  | WDT Startup Time                                 |     |                        | _                                                                    | 50     | μs    | Startup time after reset  |  |

#### Table 117. AC Characteristics (Continued)

# **On-Chip Peripheral AC and DC Electrical Characteristics**

|                  | Parameter                                                                 | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = -40°C to<br>+105°C |                  |      |       |                                                                                                          |  |

|------------------|---------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|------|-------|----------------------------------------------------------------------------------------------------------|--|

| Symbol           |                                                                           | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max  | Units | Conditions                                                                                               |  |

| V <sub>POR</sub> | Power-On Reset<br>Voltage Threshold                                       |                               |     |     | 2.20                                | 2.45             | 2.70 | V     | V <sub>DD</sub> = V <sub>POR</sub><br>(default VBO trim)                                                 |  |

| V <sub>VBO</sub> | Voltage Brown-Out<br>Reset Voltage<br>Threshold                           |                               |     |     | 2.15                                | 2.40             | 2.65 | V     | V <sub>DD</sub> = V <sub>VBO</sub><br>(default VBO trim)                                                 |  |

|                  | V <sub>POR</sub> to V <sub>VBO</sub><br>hysteresis                        |                               |     |     |                                     | 50               | 75   | mV    |                                                                                                          |  |

|                  | Starting V <sub>DD</sub><br>voltage to ensure<br>valid Power-On<br>Reset. |                               |     |     | _                                   | V <sub>SS</sub>  | _    | V     |                                                                                                          |  |

| T <sub>ANA</sub> | Power-On Reset<br>Analog Delay                                            |                               |     |     | _                                   | 50               | _    | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub><br>Digital Reset delay<br>follows T <sub>ANA</sub> |  |

Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

Note: <sup>1</sup>Data in the typical column is from characterization at 3.3V and 0°C. These values are provided for design guidance only and are not tested in production.

|                       |              |       |      | -               | -           |

|-----------------------|--------------|-------|------|-----------------|-------------|

| Part Number           | Flash        | RAM   | NVDS | ADC<br>Channels | Description |

| Extended Temperatur   | re: -40°C to | 105°C |      |                 |             |

| Z8F0230SH020EG        | 2KB          | 256   | Yes  | 7               | SOIC 20-pin |

| Z8F0230HH020EG        | 2KB          | 256   | Yes  | 7               | SSOP 20-pin |

| Z8F0230PH020EG        | 2KB          | 256   | Yes  | 7               | PDIP 20-pin |

| Z8F0230QH020EG        | 2KB          | 256   | Yes  | 7               | QFN 20-pin  |

| Z8F0231SH020EG        | 2KB          | 256   | Yes  | 0               | SOIC 20-pin |

| Z8F0231HH020EG        | 2KB          | 256   | Yes  | 0               | SSOP 20-pin |

| Z8F0231PH020EG        | 2KB          | 256   | Yes  | 0               | PDIP 20-pin |

| Z8F0231QH020EG        | 2KB          | 256   | Yes  | 0               | QFN 20-pin  |

| Z8F0230SJ020EG        | 2KB          | 256   | Yes  | 8               | SOIC 28-pin |

| Z8F0230HJ020EG        | 2KB          | 256   | Yes  | 8               | SSOP 28-pin |

| Z8F0230PJ020EG        | 2KB          | 256   | Yes  | 8               | PDIP 28-pin |

| Z8F0230QJ020EG        | 2KB          | 256   | Yes  | 8               | QFN 28-pin  |

| Z8F0231SJ020EG        | 2KB          | 256   | Yes  | 0               | SOIC 28-pin |

| Z8F0231HJ020EG        | 2KB          | 256   | Yes  | 0               | SSOP 28-pin |

| Z8F0231PJ020EG        | 2KB          | 256   | Yes  | 0               | PDIP 28-pin |

| Z8F0231QJ020EG        | 2KB          | 256   | Yes  | 0               | QFN 28-pin  |

| Z8 Encore! F0830 with | h 1KB Flash  |       |      |                 |             |

| Standard Temperatur   | e: 0°C to 70 | °C    |      |                 |             |

| Z8F0130SH020SG        | 1KB          | 256   | Yes  | 7               | SOIC 20-pin |

| Z8F0130HH020SG        | 1KB          | 256   | Yes  | 7               | SSOP 20-pin |

| Z8F0130PH020SG        | 1KB          | 256   | Yes  | 7               | PDIP 20-pin |

| Z8F0130QH020SG        | 1KB          | 256   | Yes  | 7               | QFN 20-pin  |

| Z8F0131SH020SG        | 1KB          | 256   | Yes  | 0               | SOIC 20-pin |

| Z8F0131HH020SG        | 1KB          | 256   | Yes  | 0               | SSOP 20-pin |

| Z8F0131PH020SG        | 1KB          | 256   | Yes  | 0               | PDIP 20-pin |

| Z8F0131QH020SG        | 1KB          | 256   | Yes  | 0               | QFN 20-pin  |

| Z8F0130SJ020SG        | 1KB          | 256   | Yes  | 8               | SOIC 28-pin |

| Z8F0130HJ020SG        | 1KB          | 256   | Yes  | 8               | SSOP 28-pin |

| Z8F0130PJ020SG        | 1KB          | 256   | Yes  | 8               | PDIP 28-pin |

| Z8F0130QJ020SG        | 1KB          | 256   | Yes  | 8               | QFN 28-pin  |

| Z8F0131SJ020SG        | 1KB          | 256   | Yes  | 0               | SOIC 28-pin |

| Z8F0131HJ020SG        | 1KB          | 256   | Yes  | 0               | SSOP 28-pin |

|                       |              |       |      |                 |             |

## Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

## Hex Address: FC1

| Bit     | 7        | 6     | 5     | 4        | 3        | 2        | 1        | 0      |  |

|---------|----------|-------|-------|----------|----------|----------|----------|--------|--|

| Field   | Reserved | T1ENH | T0ENH | Reserved | Reserved | Reserved | Reserved | ADCENH |  |

| RESET   | 0        | 0     | 0     | 0        | 0        | 0        | 0        | 0      |  |

| R/W     | R/W      | R/W   | R/W   | R/W      | R/W      | R/W      | R/W      | R/W    |  |

| Address |          | FC1H  |       |          |          |          |          |        |  |

### Hex Address: FC2

### Table 159. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5            | 4        | 3        | 2        | 1        | 0      |  |  |

|---------|----------|-------|--------------|----------|----------|----------|----------|--------|--|--|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | Reserved | Reserved | Reserved | Reserved | ADCENL |  |  |

| RESET   | 0        | 0     | 0            | 0        | 0        | 0        | 0        | 0      |  |  |

| R/W     | R        | R/W   | R/W          | R/W      | R/W      | R        | R        | R/W    |  |  |

| Address |          | FC2H  |              |          |          |          |          |        |  |  |

## Hex Address: FC3

### Table 160. Interrupt Request 1 Register (IRQ1)

| Bit     | 7    | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|-------|------|------|------|------|------|------|--|--|

| Field   | PA7I | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |  |

| RESET   | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| R/W     | R/W  | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| Address |      | FC3H  |      |      |      |      |      |      |  |  |

### Hex Address: FC4

### Table 161. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address |        |         |        | FC     | 4H            |        |        |        |

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

## Hex Addresses: FC9–FCC

This address range is reserved.

### Hex Address: FCD

### Table 166. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |  |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| Address |      | FCDH |      |      |      |      |      |      |  |  |

### Hex Address: FCE

### Table 167. Shared Interrupt Select Register (IRQSS)

| Bit     | 7        | 6     | 5   | 4        | 3   | 2   | 1   | 0   |  |

|---------|----------|-------|-----|----------|-----|-----|-----|-----|--|

| Field   | Reserved | PA6CS |     | Reserved |     |     |     |     |  |

| RESET   | 0        | 0     | 0   | 0        | 0   | 0   | 0   | 0   |  |

| R/W     | R/W      | R/W   | R/W | R/W      | R/W | R/W | R/W | R/W |  |

| Address |          | FCEH  |     |          |     |     |     |     |  |

## Hex Address: FCF

### Table 168. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6 | 5        | 4  | 3  | 2 | 1 | 0 |  |

|---------|------|---|----------|----|----|---|---|---|--|

| Field   | IRQE |   | Reserved |    |    |   |   |   |  |

| RESET   | 0    | 0 | 0        | 0  | 0  | 0 | 0 | 0 |  |

| R/W     | R/W  | R | R        | R  | R  | R | R | R |  |

| Address |      |   |          | FC | FH |   |   |   |  |

## Hex Address: FDB

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | FDBH  |       |       |       |       |       |       |       |

### Hex Address: FDC

### Table 181. Port D GPIO Address Register (PDADDR)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PADDR[7:0] |     |     |     |     |     |     |     |

| RESET   | 00H        |     |     |     |     |     |     |     |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FDCH       |     |     |     |     |     |     |     |

## Hex Address: FDD

### Table 182. Port D Control Registers (PDCTL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PCTL |     |     |     |     |     |     |     |

| RESET   | 00H  |     |     |     |     |     |     |     |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FDDH |     |     |     |     |     |     |     |

### Hex Address: FDE

This address range is reserved.

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

232

compare - extended addressing 166 compare mode 89 compare with carry 166 compare with carry - extended addressing 166 complement 169 complement carry flag 167, 168 condition code 164 continuous mode 89 Control Registers 14, 17 counter modes 89 CP 166 CPC 166 **CPCX 166** CPU and peripheral overview 4 CPU control instructions 168 CPX 166 current measurement architecture 98 operation 99 Customer Feedback Form 239 **Customer Information 239**

# D

DA 164, 166 data memory 16 DC characteristics 185 debugger, on-chip 139 **DEC 166** decimal adjust 166 decrement 166 decrement and jump non-zero 169 decrement word 166 **DECW 166** destination operand 165 device, port availability 33 DI 168 direct address 164 disable interrupts 168 **DJNZ 169** dst 165

## Ε

EI 168 electrical characteristics 184 GPIO input data sample timing 195 watch-dog timer 194 electrical noise 98 enable interrupt 168 ER 164 extended addressing register 164 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 166 eZ8 CPU instruction notation 164 eZ8 CPU instruction set 162 eZ8 CPU instruction summary 171

# F

FCTL register 119, 126, 127, 228 features, Z8 Encore! 1 first opcode map 182 FLAGS 165 flags register 165 flash controller 4 option bit address space 127 option bit configuration - reset 124 program memory address 0000H 127 program memory address 0001H 128 flash memory 108 byte programming 116 code protection 114 configurations 108 control register definitions 118, 126 controller bypass 117 flash control register 119, 126, 127, 228 flash option bits 115 flash status register 120 flow chart 113 frequency high and low byte registers 123 mass erase 117 operation 112 operation timing 114 page erase 117

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

JP 169 LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167 LDX 168 LEA 168 load 168 logical 169 **MULT 167 NOP 168** OR 169 ORX 169 POP 168 **POPX 168** program control 169 **PUSH 168** PUSHX 168 RCF 167, 168 **RET 169** RL 169 **RLC 169** rotate and shift 169 RR 170 **RRC** 170 **SBC 167** SCF 167. 168 **SRA 170** SRL 170 **SRP** 168 **STOP 168 SUB 167 SUBX 167 SWAP 170** TCM 167 **TCMX 167** TM 167 TMX 167 **TRAP 169** watch-dog timer refresh 168 XOR 169 **XORX 169** instructions, eZ8 classes of 166

interrupt control register 67 interrupt controller 53 architecture 53 interrupt assertion types 56 interrupt vectors and priority 56 operation 55 register definitions 57 software interrupt assertion 57 interrupt edge select register 65 interrupt request 0 register 58 interrupt request 1 register 59 interrupt request 2 register 60 interrupt return 169 interrupt vector listing 53 IR 164 Ir 164 **IRET 169** IRQ0 enable high and low bit registers 60 IRQ1 enable high and low bit registers 62 IRQ2 enable high and low bit registers 63 **IRR 164** Irr 164

## J

JP 169 jump, conditional, relative, and relative conditional 169

## L

LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167, 168 LDX 168 LEA 168 load constant 167 load constant to/from program memory 168 load constant with auto-increment addresses 168 load effective address 168 load external data 168