Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0231sj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| Table 89.  | Trim Option Bits at 0006H (TCLKFLT) 132                                             |

|------------|-------------------------------------------------------------------------------------|

| Table 90.  | ClkFlt Delay Control Definition                                                     |

| Table 91.  | Write Status Byte 135                                                               |

| Table 92.  | Read Status Byte                                                                    |

| Table 93.  | NVDS Read Time                                                                      |

| Table 94.  | OCD Baud-Rate Limits                                                                |

| Table 95.  | On-Chip Debugger Command Summary 144                                                |

| Table 96.  | OCD Control Register (OCDCTL) 149                                                   |

| Table 97.  | OCD Status Register (OCDSTAT) 150                                                   |

| Table 98.  | Oscillator Configuration and Selection                                              |

| Table 99.  | Oscillator Control Register (OSCCTL) 154                                            |

| Table 100. | Recommended Crystal Oscillator Specifications 158                                   |

| Table 101. | Assembly Language Syntax Example 1                                                  |

| Table 102. | Assembly Language Syntax Example 2 164                                              |

| Table 103. | Notational Shorthand                                                                |

| Table 104. | Additional Symbols 165                                                              |

| Table 105. | Arithmetic Instructions                                                             |

| Table 106. | Bit Manipulation Instructions                                                       |

| Table 107. | Block Transfer Instructions                                                         |

| Table 108. | CPU Control Instructions                                                            |

| Table 109. | Load Instructions                                                                   |

| Table 110. | Rotate and Shift Instructions                                                       |

| Table 111. | Logical Instructions                                                                |

| Table 112. | Program Control Instructions                                                        |

| Table 113. | eZ8 CPU Instruction Summary 171                                                     |

| Table 114. | Op Code Map Abbreviations                                                           |

| Table 115. | Absolute Maximum Ratings                                                            |

| Table 116. | DC Characteristics                                                                  |

| Table 117. | AC Characteristics                                                                  |

| Table 118. | Power-On Reset and Voltage Brown-Out Electrical Characteristics and Tim-<br>ing 190 |

# **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit CPU, meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 CPU code

- Expanded internal register file allows access up to 4KB

- New instructions improve execution efficiency for code developed using high-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the register file

- Up to 10 MIPS operation

- C Compiler-friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

#### **General Purpose Input/Output**

The Z8 Encore! F0830 Series features up to 25 port pins (Ports A–D) for general-purpose input/output (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable.

### **Flash Controller**

The Flash Controller programs and erases the Flash memory. It also supports protection against accidental programming and erasure.

|                  | _                          |          | -           |          |

|------------------|----------------------------|----------|-------------|----------|

| Address (Hex)    | Register Description       | Mnemonic | Reset (Hex) | Page No. |

| Analog-to-Digita | al Converter (ADC, cont'd) |          |             |          |

| F73              | ADC data low bits          | ADCD_L   | XX          | 103      |

| F74              | ADC sample settling time   | ADCSST   | 0F          | 104      |

| F75              | ADC sample time            | ADCST    | 3F          | 105      |

| F76              | Reserved                   | —        | XX          |          |

| F77–F7F          | Reserved                   | —        | XX          |          |

| Low Power Con    | trol                       |          |             |          |

| F80              | Power control 0            | PWRCTL0  | 88          | 32       |

| F81              | Reserved                   | _        | XX          |          |

| LED Controller   |                            |          |             |          |

| F82              | LED drive enable           | LEDEN    | 00          | 51       |

| F83              | LED drive level high       | LEDLVLH  | 00          | 51       |

| F84              | LED drive level low        | LEDLVLL  | 00          | 52       |

| F85              | Reserved                   | _        | XX          |          |

| Oscillator Contr | ol                         |          |             |          |

| F86              | Oscillator control         | OSCCTL   | A0          | 154      |

| F87–F8F          | Reserved                   | —        | XX          |          |

| Comparator 0     |                            |          |             |          |

| F90              | Comparator 0 control       | CMP0     | 14          | 107      |

| F91–FBF          | Reserved                   | _        | XX          |          |

| Interrupt Contro | bller                      |          |             |          |

| FC0              | Interrupt request 0        | IRQ0     | 00          | 58       |

| FC1              | IRQ0 enable high bit       | IRQ0ENH  | 00          | 61       |

| FC2              | IRQ0 enable low Bit        | IRQ0ENL  | 00          | 61       |

| FC3              | Interrupt request 1        | IRQ1     | 00          | 59       |

| FC4              | IRQ1 enable high bit       | IRQ1ENH  | 00          | 62       |

| FC5              | IRQ1 enable low bit        | IRQ1ENL  | 00          | 63       |

| FC6              | Interrupt request 2        | IRQ2     | 00          | 60       |

| FC7              | IRQ2 enable high bit       | IRQ2ENH  | 00          | 64       |

| FC8              | IRQ2 enable low bit        | IRQ2ENL  | 00          | 64       |

| FC9–FCC          | Reserved                   | —        | XX          |          |

| FCD              | Interrupt edge select      | IRQES    | 00          | 66       |

### Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

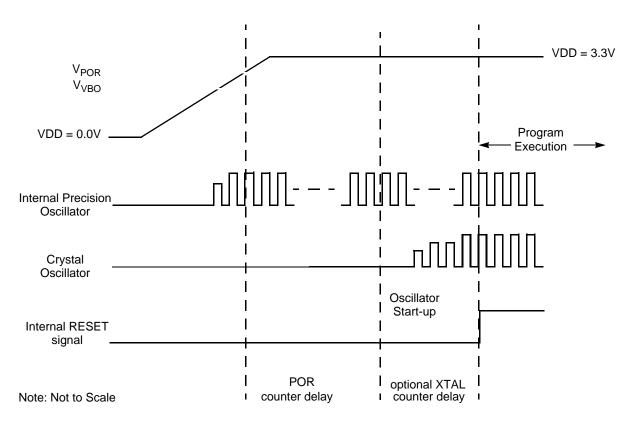

Figure 6. Power-On Reset Operation

### **Voltage Brown-Out Reset**

The devices in the Z8 Encore! F0830 Series provide low Voltage Brown-Out (VBO) protection. The VBO circuit forces the device to the Reset state, when the supply voltage drops below the VBO threshold voltage (unsafe level). While the supply voltage remains below the Power-On Reset threshold voltage ( $V_{POR}$ ), the VBO circuit holds the device in reset.

After the supply voltage exceeds the Power-On Reset threshold voltage, the device progresses through a full system reset sequence, as described in the POR section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 7 displays the Voltage Brown-Out operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

#### 32

**Note:** This register is only reset during a Power-On Reset sequence. Other system reset events do not affect it.

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                | 6                                                                               | 5          | 4          | 3        | 2        | 1        | 0        |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------|------------|----------|----------|----------|----------|--|

| Field       |                                                                                                                                                                                                                                                                                                                                                                  | Reserved                                                                        |            | VBO        | Reserved | Reserved | COMP     | Reserved |  |

| RESET       | 1                                                                                                                                                                                                                                                                                                                                                                | 0                                                                               | 0          | 0          | 1        | 0        | 0        | 0        |  |

| R/W         | R/W                                                                                                                                                                                                                                                                                                                                                              | R/W R/W R/W R/W R/W R/W R/W R/W                                                 |            |            |          |          |          |          |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                  | ·                                                                               |            | F8         | 80H      |          |          |          |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                       | Description                                                                     |            |            |          |          |          |          |  |

| [7:5]       | Reserved<br>These registers are reserved and must be programmed to 000.                                                                                                                                                                                                                                                                                          |                                                                                 |            |            |          |          |          |          |  |

| [4]<br>VBO  | Voltage Brown-Out detector disable<br>This bit takes only effect when the VBO_AO Flash option bit is disabled. In STOP Mode, VBO<br>is always disabled when the VBO_AO Flash option bit is disabled. To learn more about the<br>VBO_AO Flash option bit function, see the <u>Flash Option Bits</u> chapter on page 124.<br>0 = VBO enabled.<br>1 = VBO disabled. |                                                                                 |            |            |          |          | bout the |          |  |

| [3]         | <b>Reserved</b><br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                             |                                                                                 |            |            |          |          |          |          |  |

| [2]         | Reserved<br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                    |                                                                                 |            |            |          |          |          |          |  |

| [1]<br>COMP | 0 = Compa                                                                                                                                                                                                                                                                                                                                                        | Comparator Disable<br>0 = Comparator is enabled.<br>1 = Comparator is disabled. |            |            |          |          |          |          |  |

| [0]         | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                       | eserved and                                                                     | must be pr | ogrammed t | to 0.    |          |          |          |  |

#### Table 14. Power Control Register 0 (PWRCTL0)

>

### Port A–D Control Registers

The Port A–D Control registers, shown in Table 20, set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction.

| Bit     | 7                      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PCTL                   |     |     |     |     |     |     |     |

| RESET   | 00H                    |     |     |     |     |     |     |     |

| R/W     | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FD1H, FD5H, FD9H, FDDH |     |     |     |     |     |     |     |

| Table 20 | . Port A-D | Control | Registers | (PxCTL) |

|----------|------------|---------|-----------|---------|

|----------|------------|---------|-----------|---------|

| Bit   | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Port Control</b>                                                                                   |

| PCTL  | The Port Control Register provides access to all subregisters that configure the GPIO port operation. |

### Port A–D Data Direction Subregisters

The Port A–D Data Direction Subregister, shown in Table 21, is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register.

| Bit     | 7                                                                                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | DD7                                                                                   | DD6 | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET   | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |     |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Direction                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction Register setting.</li> <li>0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register The output driver is tristated.</li> </ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                       |

Note: x indicates the specific GPIO port pin number (7–0).

• Writing 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (disable interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the Interrupt Controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction Trap

- Primary oscillator fail trap

- Watchdog Oscillator fail trap

### **Interrupt Vectors and Priority**

The Interrupt Controller supports three levels of interrupt priority. Level 3 is the highest priority, level 2 is the second highest priority and level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 54. Level 3 interrupts are always assigned higher priority than level 2 interrupts and level 2 interrupts are assigned higher priority than level 1 interrupts. Within each interrupt priority level (level 1, level 2 or level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), primary oscillator fail trap, Watchdog Oscillator fail trap and illegal instruction trap always have highest (level 3) priority.

### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the interrupt request register is cleared. Writing 0 to the corresponding bit in the interrupt request register clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines whether the capture occurs on a rising edge or a falling edge of the timer input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt has been caused by an input capture event.

If no capture event occurs, the timer counts up to 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

# Comparator

The Z8 Encore! F0830 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or from an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The comparator includes the following features:

- Positive input is connected to a GPIO pin

- Negative input can be connected to either a GPIO pin or a programmable internal reference

- Output can be either an interrupt source or an output to an external pin

# Operation

One of the comparator inputs can be connected to an internal reference that is a user-selectable reference and is user-programmable with 200mV resolution.

The comparator can be powered down to save supply current. For details, see the <u>Power</u> <u>Control Register 0</u> section on page 31.

**Caution:** As a result of the propagation delay of the comparator, Zilog does not recommend enabling the comparator without first disabling interrupts and waiting for the comparator output to settle. This delay prevents spurious interrupts after comparator enabling.

The following example shows how to safely enable the comparator:

```

di

ld cmp0,r0; load some new configuration

nop

nop ; wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| 1FFFH          |           | <br>Page 15 | 1FFFH<br>1E00H |

|----------------|-----------|-------------|----------------|

|                | Sector 7  | Page 14     | 1DFFH<br>1C00H |

| 1C00H<br>18FFH |           | <br>Page 13 | 1BFFH<br>1A00H |

|                | Sector 6  | <br>Page 12 | 19FFH<br>1800H |

| 1800H<br>17FFH |           | <br>Page 11 | 17FFH<br>1600H |

| 1400H          | Sector 5  | <br>Page 10 | 15FFH<br>1400H |

| 13FFH          |           | <br>Page 9  | 13FFH<br>1200H |

|                | Sector 4  | <br>Page 8  | 11FFH          |

| 1C00H<br>0FFFH | Sector 3  | <br>Page 7  | 1C00H<br>0FFFH |

| 0C00H          | Seciol 3  | Page 6      | 0E00H<br>0DFFH |

| 0BFFH          | On star 0 | <br>Page 5  | 0C00H<br>0BFFH |

| 0800H          | Sector 2  | <br>Page 4  | 0A00H<br>09FFH |

| 07FFH          | Sector 1  | Page 3      | 0800H<br>07FFH |

| 0400H          | Sector    | <br>Page 2  | 0600H<br>05FFH |

| 03FFH          | Sector 0  | Page 1      | 0400H<br>03FFH |

| 0000H          |           | <br>Page 0  | 0200H<br>0100H |

|                |           |             | 0000H          |

Figure 17. 8K Flash with NVDS

110

### **Flash Status Register**

The Flash Status Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its register file address with the write-only Flash Control Register.

| Bit     | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|---------|------|-------|-------|---|---|---|---|---|

| Field   | Rese | erved | FSTAT |   |   |   |   |   |

| RESET   | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W     | R    | R     | R     | R | R | R | R | R |

| Address |      | FF8H  |       |   |   |   |   |   |

|         |      |       |       |   |   |   |   |   |

#### Table 73. Flash Status Register (FSTAT)

| Bit   | Description                                            |

|-------|--------------------------------------------------------|

| [7:6] | Reserved                                               |

|       | These bits are reserved and must be programmed to 00.  |

| [5:0] | Flash Controller Status                                |

| FSTAT | 000000 = Flash Controller locked.                      |

|       | 000001 = First unlock command received (73H written).  |

|       | 000010 = Second unlock command received (8CH written). |

|       | 000011 = Flash Controller unlocked.                    |

|       | 000100 = Sector protect register selected.             |

|       | 001xxx = Program operation in progress.                |

|       | 010xxx = Page Erase operation in progress.             |

|       | 100xxx = Mass Erase operation in progress.             |

# Flash Option Bit Control Register Definitions

This section briefly describes the features of the Trim Bit Address and Data registers.

### **Trim Bit Address Register**

The Trim Bit Address Register, shown in Table 78, contains the target address to access the trim option bits. Trim bit addresses in the range 00h–1Fh map to the information area at addresses 20h–3Fh, as shown in Table 79.

| Bit     | 7                                     | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------------------------------------|------|-----|-----|-----|-----|-----|-----|

| Field   | TRMADR: Trim Bit Address (00H to 1FH) |      |     |     |     |     |     |     |

| RESET   | 0                                     | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W                                   | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |                                       | FF6H |     |     |     |     |     |     |

#### Table 78. Trim Bit Address Register (TRMADR)

| Table 79. Trim Bit Address Map |                             |  |  |  |  |  |  |

|--------------------------------|-----------------------------|--|--|--|--|--|--|

| Trim Bit Address               | Information Area<br>Address |  |  |  |  |  |  |

| 00h                            | 20h                         |  |  |  |  |  |  |

| 01h                            | 21h                         |  |  |  |  |  |  |

| 02h                            | 22h                         |  |  |  |  |  |  |

| 03h                            | 23h                         |  |  |  |  |  |  |

| :                              | :                           |  |  |  |  |  |  |

| 1Fh                            | 3Fh                         |  |  |  |  |  |  |

#### Table 79. Trim Bit Address Map

### **Trim Bit Data Register**

The Trim Bit Data Register, shown in Table 80, contains the read or write data to access the trim option bits.

| Bit     | 7   | 6                    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|----------------------|-----|-----|-----|-----|-----|-----|

| Field   |     | TRMDR: Trim Bit Data |     |     |     |     |     |     |

| RESET   | 0   | 0                    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W                  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | FF7H                 |     |     |     |     |     |     |

#### Table 80. Trim Bit Data Register (TRMDR)

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits. See Tables 81 and 82.

| Bit                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                   | 5            | 4          | 3          | 2   | 1        | 0   |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|------------|------------|-----|----------|-----|

| Field                           | WDT_RES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | WDT_AO              | OSC_S        | SEL[1:0]   | VBO_AO     | FRP | Reserved | FWP |

| RESET                           | U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U                   | U            | U          | U          | U   | U        | U   |

| R/W                             | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W R/W R/W R/W R/W |              |            |            |     |          |     |

| Address                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | Р            | rogram Mer | nory 0000H |     |          |     |

| Note: U =                       | Unchanged by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reset. R/W :        | = Read/Write | •          |            |     |          |     |

| Bit                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |              |            |            |     |          |     |

| [7]<br>WDT_RES<br>[6]<br>WDT_AO | <ul> <li>enabled for the eZ8 CPU to acknowledge the interrupt request.</li> <li>1 = Watchdog Timer time-out causes a system reset. This is the default setting for unprogrammed (erased) Flash.</li> <li>Watchdog Timer Always On</li> <li>0 = On application of system power, Watchdog Timer is automatically enabled. Watchdog Timer cannot be disabled.</li> <li>1 = Watchdog Timer is enabled on execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a reset. This is the default setting for unpro-</li> </ul> |                     |              |            |            |     |          |     |

| [5:4]<br>OSC_SEL                | <ul> <li>grammed (erased) Flash.</li> <li>OSCILLATOR Mode Selection</li> <li>00 = On-chip oscillator configured for use with external RC networks (&lt;4MHz).</li> <li>01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0MHz).</li> <li>10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 5.0MHz).</li> <li>11 = Maximum power for use with high frequency crystals (5.0MHz to 20.0MHz). This is the default setting for unprogrammed (erased) Flash.</li> </ul>                           |                     |              |            |            |     |          |     |

Table 81. Flash Option Bits at Program Memory Address 0000H

# **Power Failure Protection**

NVDS routines employ error-checking mechanisms to ensure that any power failure will only endanger the most recently written byte. Bytes previously written to the array are not perturbed. For this protection to function, the VBO must be enabled (see the <u>Low-Power</u> <u>Modes</u> chapter on page 30) and configured for a threshold voltage of 2.4V or greater (see *the* <u>Trim Bit Address Space</u> *section on page 129*).

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

### **Optimizing NVDS Memory Usage for Execution Speed**

As indicated in Table 93, the NVDS read time varies drastically; this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N as well as the number of writes since the most recent page erase. Neglecting the effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb to consider is that every write since the most recent page erase causes read times of unwritten addresses to increase by  $0.8\mu s$  up to a maximum of  $258\mu s$ .

| Operation     | Minimum<br>Latency (μs) | Maximum<br>Latency (µs) |

|---------------|-------------------------|-------------------------|

| Read          | 71                      | 258                     |

| Write         | 126                     | 136                     |

| Illegal Read  | 6                       | 6                       |

| Illegal Write | 7                       | 7                       |

| Table | 93. | NVDS | Read | Time |

|-------|-----|------|------|------|

|       |     |      |      |      |

• **Note:** For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write takes up to 58 ms to complete.

If NVDS read performance is critical to your software architecture, you can optimize your code for speed by using either of the two methods listed below.

1. Periodically refresh all addresses that are used; this is the more useful method. The optimal use of NVDS, in terms of speed, is to rotate the writes evenly among all addresses planned for use, thereby bringing all reads closer to the minimum read time.

Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

2. Use as few unique addresses as possible to optimize the impact of refreshing.

# **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Table 97. OCD Status Register (OCDSTAT) | Table 97. | OCD | Status | Register | (OCDSTAT) |

|-----------------------------------------|-----------|-----|--------|----------|-----------|

|-----------------------------------------|-----------|-----|--------|----------|-----------|

| Bit             | 7   | 6    | 5      | 4 | 3 | 2        | 1 | 0 |

|-----------------|-----|------|--------|---|---|----------|---|---|

| Field           | DBG | HALT | FRPENB |   |   | Reserved |   |   |

| RESET           | 0   | 0    | 0      | 0 | 0 | 0        | 0 | 0 |

| R/W             | R   | R    | R      | R | R | R        | R | R |

| Bit Description |     |      |        |   |   |          |   |   |

| Description                                                      |

|------------------------------------------------------------------|

| Debug Status<br>0 = NORMAL Mode.                                 |

| 1 = DEBUG Mode.                                                  |

| HALT Mode                                                        |

| 0 = Not in HALT Mode.                                            |

| 1 = In HALT Mode.                                                |

| Flash Read Protect Option Bit Enable                             |

| 0 = FRP bit enabled, that allows disabling of many OCD commands. |

| 1 = FRP bit has no effect.                                       |

| Reserved                                                         |

| These bits are reserved and must be programmed to 00000.         |

|                                                                  |

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer Oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The Internal Precision Oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

### **Clock Failure Detection and Recovery**

#### **Primary Oscillator Failure**

The Z8F04xA family devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer Oscillator to drive the system clock. The Watchdog Timer Oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer reset function outlined in the Watchdog Timer chapter of this document.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 KHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

#### Watchdog Timer Failure

In the event of failure of a Watchdog Timer Oscillator, a similar nonmaskable interruptlike event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer Oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer Oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure is detected. A very slow system clock results in very slow detection times.

#### 195

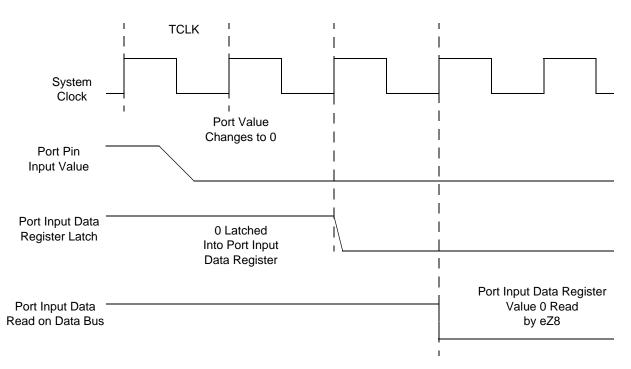

### General Purpose I/O Port Input Data Sample Timing

Figure 33 displays timing of the GPIO port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The port value is available to the eZ8 CPU on the second rising clock edge following the change of the port value.

#### Figure 33. Port Input Sample Timing

#### Table 124. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |         |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (not pictured)                            | 5          | -       |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (not pictured)                             | 0          | -       |  |

| T <sub>SMR</sub>    | GPIO port pin pulse width to ensure Stop Mode Recovery (for GPIO port pins enabled as SMR sources) | 1µs        |         |  |

# **Analog-to-Digital Converter**

For more information about these ADC registers, see the <u>ADC Control Register Defini-</u> tions section on page 101.

### Hex Address: F70

| Bit     | 7     | 6        | 5     | 4     | 3        | 2   | 1          | 0   |

|---------|-------|----------|-------|-------|----------|-----|------------|-----|

| Field   | START | Reserved | REFEN | ADCEN | Reserved |     | ANAIN[2:0] |     |

| RESET   | 0     | 0        | 0     | 0     | 0        | 0   | 0          | 0   |

| R/W     | R/W1  | R/W      | R/W   | R/W   | R/W      | R/W | R/W        | R/W |

| Address | F70h  |          |       |       |          |     |            |     |

#### Table 146. ADC Control Register 0 (ADCCTL0)

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>START   | <ul> <li>ADC Start/Busy</li> <li>0 = Writing to 0 has no effect; reading a 0 indicates that the ADC is available to begin a conversion.</li> <li>1 = Writing to 1 starts a conversion; reading a 1 indicates that a conversion is currently in progress.</li> </ul>                                                                                                                                                                                                                                                                                                                               |

| [6]            | This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [5]<br>REFEN   | <ul> <li>Reference Enable</li> <li>0 = Internal reference voltage is disabled allowing an external reference voltage to be used by the ADC.</li> <li>1 = Internal reference voltage for the ADC is enabled. The internal reference voltage can be measured on the V<sub>REF</sub> pin.</li> </ul>                                                                                                                                                                                                                                                                                                 |

| [4]<br>ADCEN   | ADC Enable<br>0 = ADC is disabled for low power operation.<br>1 = ADC is enabled for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [3]            | This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [2:0]<br>ANAIN | Analog Input Select000 = ANA0 input is selected for analog to digital conversion.001 = ANA1 input is selected for analog to digital conversion.010 = ANA2 input is selected for analog to digital conversion.011 = ANA3 input is selected for analog to digital conversion.100 = ANA4 input is selected for analog to digital conversion.101 = ANA5 input is selected for analog to digital conversion.101 = ANA5 input is selected for analog to digital conversion.111 = ANA6 input is selected for analog to digital conversion.111 = ANA7 input is selected for analog to digital conversion. |

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

read program memory CRC (0EH) 147 read register (09H) 146 read runtime counter (03H) 145 step instruction (10H) 148 stuff instruction (11H) 148 write data memory (0CH) 147 write OCD control register (04H) 145 write program counter (06H) 146 write program memory (0AH) 146 write register (08H) 146 on-chip debugger (OCD) 139 on-chip debugger signals 12 on-chip oscillator 157 one-shot mode 89 opcode map abbreviations 181 cell description 180 first 182 second after 1FH 183 operation 100 current measurement 99 voltage measurement timing diagram 100 Operational Description 21, 30, 33, 53, 68, 92, 98, 106, 108, 124, 134, 139, 151, 157, 161 OR 169 ordering information 200 ORX 169 oscillator signals 12

### Ρ

p 164

Packaging 199

part selection guide 2

PC 165

peripheral AC and DC electrical characteristics 190

pin characteristics 13

Pin Descriptions 7

polarity 164

POP 168

pop using extended addressing 168

POPX 168

port availability, device 33

port input timing (GPIO) 195

port output timing, GPIO 196 power supply signals 12 power-on reset (POR) 23 program control instructions 169 program memory 15 PUSH 168 push using extended addressing 168 PUSHX 168 PWM mode 89, 90 PxADDR register 40, 222, 223, 224, 225 PxCTL register 41, 222, 223, 224, 225

# R

R 165 r 164 RA register address 165 RCF 167, 168 register 165 flash control (FCTL) 119, 126, 127, 228 flash high and low byte (FFREQH and FRE-EQL) 123 flash page select (FPS) 121, 122 flash status (FSTAT) 120 GPIO port A-H address (PxADDR) 40, 222, 223, 224, 225 GPIO port A-H alternate function sub-registers 42 GPIO port A-H control address (PxCTL) 41, 222, 223, 224, 225 GPIO port A-H data direction sub-registers 41 OCD control 148 OCD status 150 watch-dog timer control (WDTCTL) 95, 107, 154, 217, 218, 226 watchdog timer control (WDTCTL) 29 watch-dog timer reload high byte (WDTH) 227 watchdog timer reload high byte (WDTH) 96 watch-dog timer reload low byte (WDTL) 227 watchdog timer reload low byte (WDTL) 97 watch-dog timer reload upper byte (WDTU) 227

236