Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K × 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0430ph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                              |

|----------|-------------------------------------|-----------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                              |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer chapter)                           |

|          | 003AH                               | Primary oscillator fail trap (not an interrupt)                       |

|          | 003CH                               | Watchdog Oscillator fail trap (not an interrupt)                      |

|          | 0006H                               | Illegal instruction trap (not an interrupt)                           |

|          | 0008H                               | Reserved                                                              |

|          | 000AH                               | Timer 1                                                               |

|          | 000CH                               | Timer 0                                                               |

|          | 000EH                               | Reserved                                                              |

|          | 0010H                               | Reserved                                                              |

|          | 0012H                               | Reserved                                                              |

|          | 0014H                               | Reserved                                                              |

|          | 0016H                               | ADC                                                                   |

|          | 0018H                               | Port A7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A3, selectable rising or falling input edge                      |

|          | 0022H                               | Port A2, selectable rising or falling input edge                      |

|          | 0024H                               | Port A1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                              |

|          | 002AH                               | Reserved                                                              |

|          | 002CH                               | Reserved                                                              |

|          | 002EH                               | Reserved                                                              |

|          | 0030H                               | Port C3, both input edges                                             |

|          | 0032H                               | Port C2, both input edges                                             |

|          | 0034H                               | Port C1, both input edges                                             |

|          | 0036H                               | Port C0, both input edges                                             |

| _owest   | 0038H                               | Reserved                                                              |

#### Table 34. Trap and Interrupt Vectors in Order of Priority

#### Port A D High Drive Enable Subregisters

The Port A D High Drive Enable Subregisters in Table 24, is accessed through the Port A D Control Register by writing to the Port A D Address Register. Setting the bits in the Port A D High Drivable subregisters to ignores the specified port pins for high-output current drive operation. The Port A D High Drive Enable Subregister affects the pins directly and, alt antes at functions are also affected.

|          |        |        |       |         |              | /- · · > |

|----------|--------|--------|-------|---------|--------------|----------|

| Table 21 | Dort A | D Hiah | Driva | Fnahlo  | Subregisters | (DVHDF)  |

|          | IUILA  | DINGI  | DIIVE | LIIUDIC | JUDIEQISIEIS |          |

|          |        |        |       |         |              |          |

| Bit     | 7                                                                                 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-----------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | PHDE7                                                                             | PHDE6 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDEO |  |  |

| RESET   | 0                                                                                 | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W                                                                               | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address | s If O4H in Port A D Address Register, accides through the PoAtD Control Register |       |       |       |       |       |       |       |  |  |

|         |                                                                                   |       |       |       |       |       |       |       |  |  |

| Bit     | Description                                                                       |       |       |       |       |       |       |       |  |  |

[7:0] Port High Drive Enable

PHDEx 0 = The port pin is configured **\$b** and ard output current drive.

1 = The port pin is configurfood high output current drive.

Note: x indicates the specific GPIO port pin number (7 0).

Port A D Stop Mode RecoverySource Enable Subregisters

The Port A D Stop Mode Recovery Sound the Bound the Port A D Address accessed through the Port And Register by writing to the Port A D Address Register. Setting the bits in the Port AND Stop Recovery Source Enable subregisters to 1 configures the specified port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a port pind as able top Mode Recovery source initiates a Stop Mode Recovery event.

Table 25. Port A D Stop Mode Recovery Source Enable Subregisters (PxSMRE)

| Bit     | 7                                                                               | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|---------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | PSMRE7                                                                          | PSMRE6 | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMREO |  |  |

| RESET   | 0                                                                               | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W                                                                             | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address | If 05H in Port A D Address Register, accides through the PoAtD Control Register |        |        |        |        |        |        |        |  |  |

Bit Description

[7:0] Port Stop Mode Recovery Source Enable

PSMREx O = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7 0).

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the codiing Extay hple 2 to clear bits in the Interrupt Request O Register:

Example 2. A good coding style thotavlost interrupt requests:

ANDX IRQ0, MASK

#### Software Interrupt Assertion

Program code can generate interrupts Wainition by 1 to the correct bit in the interrupt request register triggers an interrupt (absolution the grupt is enabled). When the interrupt request is acknowledged by the elige CCPU in the interrupt request register is automatically cleared to O.

Caution: Zilog recommends not using a coding geglerable software interrupts by setting bits in the Interrupt Request registers. All in give terrupts received between execution of the first LDX command and the final LDX and are lost. See Example 3, which follows.

Example 3. A poor coding style that sault rie lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interru Request registers:

Example 4. A good coding style thotdsvlost interrupt requests:

ORX IRQ0, MASK

# Interrupt Control Register Definitions

The Interrupt Control registers enable under the interrupts, set interrupt priorities and indicate interrupt requests of the interrupts other than the Watchdog Timer interrupt, the primary oscillatort faip and the Watchdog lass fail trap interrupts.

| Assembly        |                                                                                         | Addr<br>Mc |     | Op<br>Code(s) |   |   | F | laç | gs |   |   | _ Fetch | Instr. |

|-----------------|-----------------------------------------------------------------------------------------|------------|-----|---------------|---|---|---|-----|----|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                                                      | dst        | src | (Hex)         | С | Ζ | S | 5   | V  | D | Н |         | Cycles |

| AND dst, src    | ds∉ dst AND src                                                                         | r          | r   | 52            |   |   | * | ;   | *  | 0 |   | 2       | 3      |

|                 |                                                                                         | r          | lr  | 53            | _ |   |   |     |    |   |   | 2       | 4      |

|                 |                                                                                         | R          | R   | 54            | _ |   |   |     |    |   |   | 3       | 3      |

|                 |                                                                                         | R          | IR  | 55            | _ |   |   |     |    |   |   | 3       | 4      |

|                 |                                                                                         | R          | IM  | 56            | _ |   |   |     |    |   |   | 3       | 3      |

|                 |                                                                                         | IR         | IM  | 57            | _ |   |   |     |    |   |   | 3       | 4      |

| ANDX dst, src   | : dsŧ– dst AND src                                                                      | ER         | ER  | 58            |   |   | * | *   | (  | C |   | 4       | 3      |

|                 |                                                                                         | ER         | IM  | 59            | _ |   |   |     |    |   |   | 4       | 3      |

| ATM             | Block all interrupt and<br>DMA requests during<br>execution of the next<br>instructions |            |     | 2F            |   |   |   |     |    |   |   | 1       | 2      |

| BCLR bit, dst   | dst[b <del>it]</del> 0                                                                  | r          |     | E2            |   | * |   | *   | C  | ) |   | 2       | 2      |

| BIT p, bit, dst | dst[b <del>it</del> ]p                                                                  | r          |     | E2            |   | * |   | *   | 0  |   |   | 2       | 2      |

| BRK             | Debugger Break                                                                          |            |     | 00            |   |   |   |     |    |   |   | 1       | 1      |

| BSET bit, dst   | dst[bi <del>t]</del> 1                                                                  | r          |     | E2            |   | * | 1 | *   | 0  |   |   | 2       | 2      |

| BSWAP dst       | dst[7:0] dst[0:7]                                                                       | R          |     | D5            | Х | * |   | *   | 0  | ) |   | 2       | 2      |

|                 | , if src[bit] = p                                                                       |            | r   | F6            |   |   |   |     |    |   |   | 3       | 3      |

| dst             | PC← PC + X                                                                              |            | lr  | F7            | _ |   |   |     |    |   |   | 3       | 4      |

|                 | , if src[bit] = 1                                                                       |            | r   | F6            |   |   |   |     |    |   |   | 3       | 3      |

| dst             | PC← PC + X                                                                              |            | lr  | F7            | _ |   |   |     |    |   |   | 3       | 4      |

|                 | if src[bit] = 0                                                                         |            | r   | F6            |   |   |   |     |    |   |   | 3       | 3      |

| dst             | PC← PC + X                                                                              |            | lr  | F7            | _ |   |   |     |    |   |   | 3       | 4      |

| CALL dst        | SP← SP 2                                                                                | IRR        |     | D4            |   |   |   |     |    |   |   | 2       | 6      |

|                 | @SP ← PC<br>PC ← dst                                                                    | DA         |     | D6            |   |   |   |     |    |   |   | 3       | 3      |

| CCF             | $C \leftarrow \sim C$                                                                   |            |     | EF            | * |   |   |     |    |   | - | 1       | 2      |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

= Unaffected.

X = Undefined.

O = Reset to O.

1 = Set to 1.

172

Z8 Encore!<sup>fi</sup> F0830 Series Product Specification

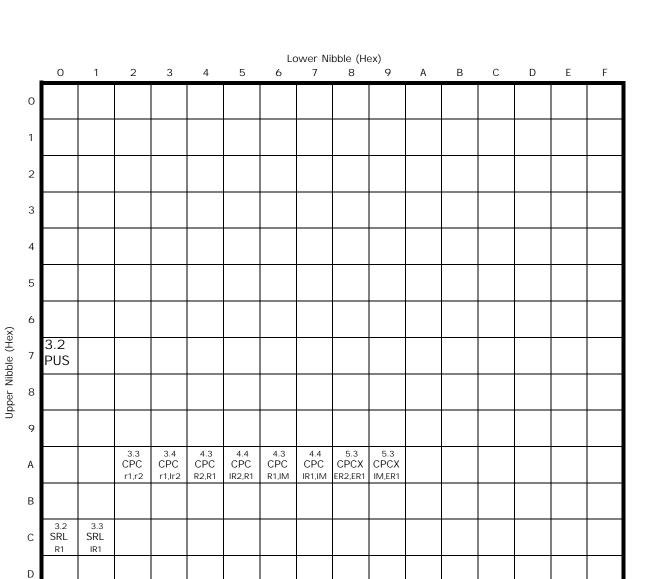

Figure 30. Second Op Code Map after 1FH

5, 4 LDWX

ER2,ER1

Е

F

# Hex Address: F09

### Table 139. Timer 1 Low Byte Register (T1L)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | Т   | L   |     |     |     |

| RESET   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | FO  | 9H  |     |     |     |

## Hex Address: FOA

### Table 140. Timer 1 Reload High Byte Register (T1RH)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | TRH  |     |     |     |     |     |     |  |  |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     | FOAH |     |     |     |     |     |     |  |  |  |

# Hex Address: FOB

## Table 141. Timer 1 Reload Low Byte Register (T1RL)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | TRL  |     |     |     |     |     |     |  |  |  |

| RESET   | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     | FOBH |     |     |     |     |     |     |  |  |  |

## Hex Address: FOC

## Table 142. Timer 1 PWM High Byte Register (T1PWMH)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | PW  | ΜH  |     |     |     |

| RESET   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | FO  | СН  |     |     |     |