Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0430pj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2012 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES or TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES or TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

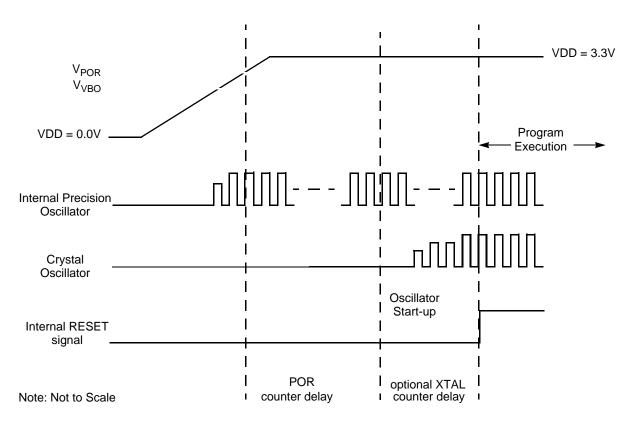

Figure 6. Power-On Reset Operation

## **Voltage Brown-Out Reset**

The devices in the Z8 Encore! F0830 Series provide low Voltage Brown-Out (VBO) protection. The VBO circuit forces the device to the Reset state, when the supply voltage drops below the VBO threshold voltage (unsafe level). While the supply voltage remains below the Power-On Reset threshold voltage ( $V_{POR}$ ), the VBO circuit holds the device in reset.

After the supply voltage exceeds the Power-On Reset threshold voltage, the device progresses through a full system reset sequence, as described in the POR section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 7 displays the Voltage Brown-Out operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

The eZ8 CPU fetches the reset vector at program memory addresses 0002H and 0003H and loads that value into the program counter. Program execution begins at the reset vector address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 11 lists the Stop Mode Recovery sources and resulting actions. The following sections provide more details about each of the Stop Mode Recovery sources.

| Operating<br>Mode | Stop Mode Recovery Source                                                   | Action                                                              |  |

|-------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------|--|

| STOP Mode         | Watchdog Timer time-out when configured for Reset                           | Stop Mode Recovery                                                  |  |

|                   | Watchdog Timer time-out when configured for interrupt                       | Stop Mode Recovery followed by interrup (if interrupts are enabled) |  |

|                   | Data transition on any GPIO port pin enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                  |  |

|                   | Assertion of external RESET Pin                                             | System reset                                                        |  |

|                   | Debug pin driven Low                                                        | System reset                                                        |  |

#### Table 11. Stop Mode Recovery Sources and Resulting Action

## Stop Mode Recovery using WDT Time-Out

If the Watchdog Timer times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) Register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! F0830 Series device is configured to respond to interrupts, the eZ8 CPU services the WDT interrupt request following the normal Stop Mode Recovery sequence.

## **Stop Mode Recovery using GPIO Port Pin Transition**

Each of the GPIO port pins may be configured as a Stop Mode Recovery input source. If any GPIO pin is enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery. In the Reset Status (RSTSTAT) Register, the STOP bit is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. These Port Input Data registers record the port transition only if the signal stays on the port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin).

# Architecture

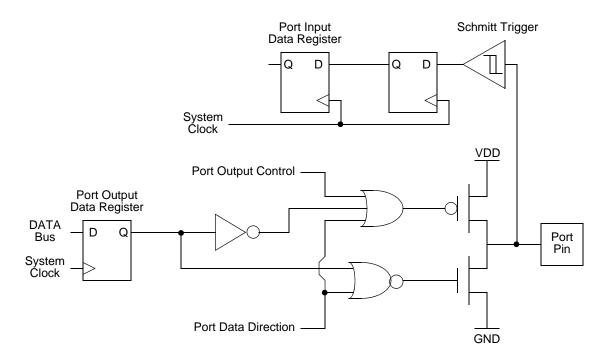

Figure 8 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

# **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general purpose input/output and access to onchip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function subregisters configure these pins for either GPIO or Alternate function operation. When a pin is configured for Alternate function, control of the port pin direction (input/output) is passed from the Port A–D data direction registers to the Alternate function assigned to this pin. <u>Table 16</u> on page 36 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, pins PA0 and PA1 functions as input and output for the crystal oscillator.

### 39

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the input pin signal. Other port pin interrupt sources, generate an interrupt when any edge occurs (both rising and falling). See the <u>Interrupt Controller</u> chapter on page 53 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data and output data; Table 17 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| P <i>x</i> ADDR           | Port A–D Address Register (selects subregisters)            |

| PxCTL                     | Port A–D Control Register (provides access to subregisters) |

| PxIN                      | Port A–D Input Data Register                                |

| P <i>x</i> OUT            | Port A–D Output Data Register                               |

| Port Subregister Mnemonic | Port Register Name                                          |

| PxDD                      | Data Direction                                              |

| P <i>x</i> AF             | Alternate Function                                          |

| PxOC                      | Output Control (open-drain)                                 |

| PxHDE                     | High Drive Enable                                           |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable                            |

| PxPUE                     | Pull-Up Enable                                              |

| PxAFS1                    | Alternate Function Set 1                                    |

| PxAFS2                    | Alternate Function Set 2                                    |

#### Table 17. GPIO Port Registers and Subregisters

# Port A–D Control Registers

The Port A–D Control registers, shown in Table 20, set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction.

| Bit     | 7                           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----------------------------|---|---|---|---|---|---|---|

| Field   | PCTL                        |   |   |   |   |   |   |   |

| RESET   | 00H                         |   |   |   |   |   |   |   |

| R/W     | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |   |

| Address | FD1H, FD5H, FD9H, FDDH      |   |   |   |   |   |   |   |

| Table 20 | . Port A-D | Control | Registers | (PxCTL) |

|----------|------------|---------|-----------|---------|

|----------|------------|---------|-----------|---------|

| Bit   | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Port Control</b>                                                                                   |

| PCTL  | The Port Control Register provides access to all subregisters that configure the GPIO port operation. |

## Port A–D Data Direction Subregisters

The Port A–D Data Direction Subregister, shown in Table 21, is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register.

| Bit     | 7         | 6                           | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|-----------------------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | DD7       | DD6                         | DD5         | DD4           | DD3          | DD2          | DD1          | DD0      |

| RESET   | 1         | 1                           | 1           | 1             | 1            | 1            | 1            | 1        |

| R/W     | R/W       | R/W R/W R/W R/W R/W R/W R/W |             |               |              |              |              |          |

| Address | If 01H ir | n Port A–D A                | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Direction                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction Register setting.</li> <li>0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register The output driver is tristated.</li> </ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                       |

Note: x indicates the specific GPIO port pin number (7–0).

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The compare time can be calculated by the following equation:

Compare Mode Time (s) =  $\frac{(Compare Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **GATED Mode**

In GATED Mode, the timer counts only when the timer input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the timer input signal is asserted, counting begins. A timer interrupt is generated when the timer input signal is deasserted or a timer reload occurs. To determine whether the timer input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the timer input signal remains asserted). Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps for configuring a timer for GATED Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deasser-

tion and reload events. The user can configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the timer input signal to initiate the counting.

### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE Mode, the timer begins counting on the first external timer input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the timer input signal, captures the current count value. The capture value is written to the timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE/COMPARE Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode.

- Set the prescale value.

- Set the capture edge (rising or falling) for the timer input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and Reload events. The user can configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

| Bit   | Description (Continued)                                                                   |

|-------|-------------------------------------------------------------------------------------------|

| [2:0] | Timer Mode                                                                                |

| TMODE | This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of |

|       | the timer. TMODEHI is the most significant bit of the timer mode selection value.         |

|       | 0000 = ONE-SHOT Mode.                                                                     |

|       | 0001 = CONTINUOUS Mode.                                                                   |

|       | 0010 = COUNTER Mode.                                                                      |

|       | 0011 = PWM SINGLE OUTPUT Mode.                                                            |

|       | 0100 = CAPTURE Mode.                                                                      |

|       | 0101 = COMPARE Mode.                                                                      |

|       | 0110 = GATED Mode.                                                                        |

|       | 0111 = CAPTURE/COMPARE Mode.                                                              |

|       | 1000 = PWM DUAL OUTPUT Mode.                                                              |

|       | 1001 = CAPTURE RESTART Mode.                                                              |

|       | 1010 = COMPARATOR COUNTER Mode.                                                           |

91

# **ADC Control Register 0**

The ADC Control 0 Register, shown in Table 63, initiates an A/D conversion and provides ADC status information.

| Bit            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                               | 5           | 4          | 3    | 2   | 1   | 0   |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|------|-----|-----|-----|--|

| Field          | START Reserved REFEN ADCEN Reserved ANAIN[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                 |             |            |      |     |     |     |  |

| RESET          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                               | 0           | 0          | 0    | 0   | 0   | 0   |  |

| R/W            | R/W1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                                                                                                                                                                                                                                                             | R/W         | R/W        | R/W  | R/W | R/W | R/W |  |

| Address        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                 |             | F7         | '0h  |     |     |     |  |

| Bit            | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | n                                                                                                                                                                                                                                                               |             |            |      |     |     |     |  |

| [7]<br>START   | 0 = Writing sion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>ADC Start/Busy</li> <li>0 = Writing to 0 has no effect; reading a 0 indicates that the ADC is available to begin a conversion.</li> <li>1 = Writing to 1 starts a conversion; reading a 1 indicates that a conversion is currently in prog-</li> </ul> |             |            |      |     |     |     |  |

| [6]            | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | eserved and                                                                                                                                                                                                                                                     | must be pre | ogrammed t | o 0. |     |     |     |  |

| [5]<br>REFEN   | <ul> <li>Reference Enable</li> <li>0 = Internal reference voltage is disabled allowing an external reference voltage to be used by the ADC.</li> <li>1 = Internal reference voltage for the ADC is enabled. The internal reference voltage can be measured on the V<sub>RFF</sub> pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                 |             |            |      |     |     |     |  |

| [4]<br>ADCEN   | ADC Enable<br>0 = ADC is disabled for low power operation.<br>1 = ADC is enabled for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                 |             |            |      |     |     |     |  |

| [3]            | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | eserved and                                                                                                                                                                                                                                                     | must be pro | ogrammed t | o 0. |     |     |     |  |

| [2:0]<br>ANAIN | This bit is reserved and must be programmed to 0.<br><b>Analog Input Select</b><br>000 = ANA0 input is selected for analog to digital conversion.<br>001 = ANA1 input is selected for analog to digital conversion.<br>010 = ANA2 input is selected for analog to digital conversion.<br>011 = ANA3 input is selected for analog to digital conversion.<br>100 = ANA4 input is selected for analog to digital conversion.<br>101 = ANA5 input is selected for analog to digital conversion.<br>101 = ANA6 input is selected for analog to digital conversion.<br>110 = ANA6 input is selected for analog to digital conversion.<br>111 = ANA7 input is selected for analog to digital conversion. |                                                                                                                                                                                                                                                                 |             |            |      |     |     |     |  |

### Table 63. ADC Control Register 0 (ADCCTL0)

# Flash Memory

The products in the Z8 Encore! F0830 Series features either 1KB (1024 bytes with NVDS), 2KB (2048 bytes with NVDS), 4KB (4096 bytes with NVDS), 8KB (8192 bytes with NVDS) or 12KB (12288 bytes with no NVDS) of nonvolatile Flash memory with read/write/erase capability. Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F0830 Series, each sector maps to one page (for 1KB, 2KB and 4KB devices), two pages (8KB device) or three pages (12KB device).

The first two bytes of Flash program memory is used as Flash option bits. For more information, see *the* <u>Flash Option Bits</u> chapter on page 124.

Table 69 lists the Flash memory configuration for each device in the Z8 Encore! F0830 Series. Figures 14 through 18 display the memory arrangements for each Flash memory size.

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F123x     | 12 (12,288)              | 24          | 0000H–2FFFH                    | 1536                         |

| Z8F083x     | 8 (8196)                 | 16          | 0000H-1FFFH                    | 1024                         |

| Z8F043x     | 4 (4096)                 | 8           | 0000H–0FFFH                    | 512                          |

| Z8F023x     | 2 (2048)                 | 4           | 0000H–07FFH                    | 512                          |

| Z8F013x     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

Figure 14. 1K Flash with NVDS

<sup>03</sup>FFH

03FFH

03FFH

0200H

Sector 1

Page 1

0200H

01FFH

Sector 0

Page 0

01FFh

0000H

0000H

0000H

0000H

| FHSWP  | FWP | Flash Code Protection Description                                                                                                                                                                  |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0   | Programming and erasing disabled for all Flash program memory. In user code pro-<br>gramming, page erase and mass erase are all disabled. Mass erase is available<br>through the On-Chip Debugger. |

| 0 or 1 | 1   | Programming, page erase and mass erase are enabled for all of the Flash program memory.                                                                                                            |

#### Table 71. Flash Code Protection using the Flash Option Bits

At reset, the Flash Controller is locked to prevent accidental program or erasure of Flash memory. To program or erase Flash memory, first write the target page to the page select register. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The page select register must be rewritten with the same page previously stored there. If the two page select writes do not match, the controller reverts to a Locked state. If the two writes match, the selected page becomes active. See Figure 19 for details.

After unlocking a specific page, you can enable either page program or erase. Writing the value 95H causes a page erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass erase is not allowed in the user code, but is allowed through the debug port.

After unlocking a specific page, the user can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register causes the active page to revert to a Locked state.

#### **Sector Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! devices are divided into maximum number of eight sectors. A sector is oneeighth of the total size of Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal. On Z8 Encore! F0830 Series devices, the sector size is varied according to the Z8 Encore! F0830 Series Flash Memory Configuration shown in Table 69 on page 108 and in Figures 14 through 18, which follow the table

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset and any previously written protection values is lost. User code must write this register in their initialization routine if they want to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When user code writes the Flash Sector Protect Register,

# **Runtime Counter**

The OCD contains a 16-bit runtime counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash read protect option bit (FRP). The FRP prevents the code in memory from being read out of the Z8 Encore! F0830 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 95 summarizes the On-Chip Debugger commands. This table indicates the commands that operate when the device is not in DEBUG Mode (normal operation) and the commands that are disabled by programming the FRP.

| Debug Command              | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                                     |

|----------------------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                | -                                                                                                                                                                                |

| Reserved                   | 01H             | _                                  | _                                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                                | _                                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                                  | -                                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                                | Cannot clear DBGMODE bit                                                                                                                                                         |

| Read OCD Control Register  | 05H             | Yes                                | _                                                                                                                                                                                |

| Write Program Counter      | 06H             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Counter       | 07H             | _                                  | Disabled                                                                                                                                                                         |

| Write Register             | 08H             | _                                  | Only writes of the Flash Memory Con-<br>trol registers are allowed. Additionally,<br>only the Mass Erase command is<br>allowed to be written to the Flash Con-<br>trol register. |

| Read Register              | 09H             | _                                  | Disabled                                                                                                                                                                         |

| Write Program Memory       | 0AH             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Memory        | 0BH             | _                                  | Disabled                                                                                                                                                                         |

| Write Data Memory          | 0CH             | _                                  | Yes                                                                                                                                                                              |

| Read Data Memory           | 0DH             | _                                  | _                                                                                                                                                                                |

#### Table 95. On-Chip Debugger Command Summary

# **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

| Table 97. OCD Status Register (OCDSTAT) | Table 97. | OCD | Status | Register | (OCDSTAT) |

|-----------------------------------------|-----------|-----|--------|----------|-----------|

|-----------------------------------------|-----------|-----|--------|----------|-----------|

| Bit             | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |

|-----------------|-----|------|--------|----------|---|---|---|---|--|

| Field           | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |

| RESET           | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |

| R/W             | R   | R    | R      | R        | R | R | R | R |  |

| Bit Description |     |      |        |          |   |   |   |   |  |

| Description                                                      |

|------------------------------------------------------------------|

| Debug Status<br>0 = NORMAL Mode.                                 |

| 1 = DEBUG Mode.                                                  |

| HALT Mode                                                        |

| 0 = Not in HALT Mode.                                            |

| 1 = In HALT Mode.                                                |

| Flash Read Protect Option Bit Enable                             |

| 0 = FRP bit enabled, that allows disabling of many OCD commands. |

| 1 = FRP bit has no effect.                                       |

| Reserved                                                         |

| These bits are reserved and must be programmed to 00000.         |

|                                                                  |

### Table 105. Arithmetic Instructions (Continued)

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

### Table 106. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                             |

|----------|-------------|---------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                               |

| BIT      | p, bit, dst | Bit Set or Clear                                        |

| BSET     | bit, dst    | Bit Set                                                 |

| BSWAP    | dst         | Bit Swap                                                |

| CCF      | —           | Complement Carry Flag                                   |

| RCF      | —           | Reset Carry Flag                                        |

| SCF      | —           | Set Carry Flag                                          |

| ТСМ      | dst, src    | Test Complement Under Mask                              |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended<br>Addressing |

| ТМ       | dst, src    | Test Under Mask                                         |

| TMX      | dst, src    | Test Under Mask using Extended Addressing               |

#### Table 107. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

### 170

### Table 112. Rotate and Shift Instructions (Continued)

| RRdstRotate RightRRCdstRotate Right through CarrySRAdstShift Right ArithmeticSRLdstShift Right LogicalSWAPdstSwap Nibbles | Mnemonic | Operands | Instruction                |

|---------------------------------------------------------------------------------------------------------------------------|----------|----------|----------------------------|

| SRAdstShift Right ArithmeticSRLdstShift Right Logical                                                                     | RR       | dst      | Rotate Right               |

| SRL dst Shift Right Logical                                                                                               | RRC      | dst      | Rotate Right through Carry |

|                                                                                                                           | SRA      | dst      | Shift Right Arithmetic     |

| SWAP dst Swap Nibbles                                                                                                     | SRL      | dst      | Shift Right Logical        |

|                                                                                                                           | SWAP     | dst      | Swap Nibbles               |

|                   |                                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = -40°C to<br>+105°C |                  |     |       |                                                             |  |

|-------------------|-------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|-----|-------|-------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                 | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max | Units | Conditions                                                  |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>disabled                              |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>enabled                               |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                                            |                               |     |     | _                                   | 10               | _   | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to gen<br>erate a Reset. |  |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to<br>transition from $V_{SS}$<br>to $V_{POR}$ to ensure<br>valid Reset |                               |     |     | 0.10                                | _                | 100 | ms    |                                                             |  |

### Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

ance only and are not tested in production.

### Hex Address: F0D

#### Table 143. Timer 1 PWM Low Byte Register (T1PWML)

| Bit     | 7    | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|------|------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   | PWML |      |     |     |     |     |     |     |  |  |  |

| RESET   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W  | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |      | F0DH |     |     |     |     |     |     |  |  |  |

### Hex Address: F0E

#### Table 144. Timer 1 Control Register 0 (T1CTL0)

| Bit     | 7       | 6        | 5   | 4        | 3    | 2   | 1   | 0      |  |  |  |

|---------|---------|----------|-----|----------|------|-----|-----|--------|--|--|--|

| Field   | TMODEHI | TICONFIG |     | Reserved | PWMD |     |     | INPCAP |  |  |  |

| RESET   | 0       | 0        | 0   | 0        | 0    | 0   | 0   | 0      |  |  |  |

| R/W     | R/W     | R/W      | R/W | R/W      | R/W  | R/W | R/W | R/W    |  |  |  |

| Address |         | FOEH     |     |          |      |     |     |        |  |  |  |

### Hex Address: F0F

### Table 145. Timer 1 Control Register 1 (T1CTL1)

| Bit     | 7    | 6    | 5          | 4   | 3   | 2   | 1   | 0   |

|---------|------|------|------------|-----|-----|-----|-----|-----|

| Field   | TEN  | TPOL | PRES TMODE |     |     |     |     |     |

| RESET   | 0    | 0    | 0          | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W  | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W |

| Address | FOFH |      |            |     |     |     |     |     |

### Hex Addresses: F10–F6F

This address range is reserved.

# **Analog-to-Digital Converter**

For more information about these ADC registers, see the <u>ADC Control Register Defini-</u> tions section on page 101.

### Hex Address: F70

| Bit     | 7     | 6        | 5     | 4     | 3        | 2          | 1   | 0   |

|---------|-------|----------|-------|-------|----------|------------|-----|-----|

| Field   | START | Reserved | REFEN | ADCEN | Reserved | ANAIN[2:0] |     |     |

| RESET   | 0     | 0        | 0     | 0     | 0        | 0          | 0   | 0   |

| R/W     | R/W1  | R/W      | R/W   | R/W   | R/W      | R/W        | R/W | R/W |

| Address | F70h  |          |       |       |          |            |     |     |

### Table 146. ADC Control Register 0 (ADCCTL0)

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>START   | <ul> <li>ADC Start/Busy</li> <li>0 = Writing to 0 has no effect; reading a 0 indicates that the ADC is available to begin a conversion.</li> <li>1 = Writing to 1 starts a conversion; reading a 1 indicates that a conversion is currently in progress.</li> </ul>                                                                                                                                                                                                                                                                                                                               |

| [6]            | This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [5]<br>REFEN   | <ul> <li>Reference Enable</li> <li>0 = Internal reference voltage is disabled allowing an external reference voltage to be used by the ADC.</li> <li>1 = Internal reference voltage for the ADC is enabled. The internal reference voltage can be measured on the V<sub>REF</sub> pin.</li> </ul>                                                                                                                                                                                                                                                                                                 |

| [4]<br>ADCEN   | ADC Enable<br>0 = ADC is disabled for low power operation.<br>1 = ADC is enabled for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [3]            | This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [2:0]<br>ANAIN | Analog Input Select000 = ANA0 input is selected for analog to digital conversion.001 = ANA1 input is selected for analog to digital conversion.010 = ANA2 input is selected for analog to digital conversion.011 = ANA3 input is selected for analog to digital conversion.100 = ANA4 input is selected for analog to digital conversion.101 = ANA5 input is selected for analog to digital conversion.101 = ANA5 input is selected for analog to digital conversion.111 = ANA6 input is selected for analog to digital conversion.111 = ANA7 input is selected for analog to digital conversion. |

### Hex Address: FDF

| Table 183. | Port D | Output | Data | Register | (PDOUT) |

|------------|--------|--------|------|----------|---------|

|            | IOIUD  | Output | Data | Register |         |

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address | FDFH  |       |       |       |       |       |       |       |  |  |

### Hex Addresses: FE0–FEF

This address range is reserved.

# Watchdog Timer

For more information about the Watchdog Timer registers, see the <u>Watchdog Timer Con-</u> trol Register Definitions section on page 95.

### Hex Address: FF0

The Watchdog Timer Control Register address is shared with the read-only Reset Status Register.

| Bit     | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------|---|---|---|---|---|---|---|--|--|

| Field   | WDTUNLK |   |   |   |   |   |   |   |  |  |

| RESET   | Х       | Х | Х | Х | Х | Х | Х | Х |  |  |

| R/W     | W       | W | W | W | W | W | W | W |  |  |

| Address | FF0H    |   |   |   |   |   |   |   |  |  |

| Bit     | 7                              | 6    | 5   | 4   | 3        | 2 | 1 | 0 |  |

|---------|--------------------------------|------|-----|-----|----------|---|---|---|--|

| Field   | POR                            | STOP | WDT | EXT | Reserved |   |   |   |  |

| RESET   | See <u>Table 12</u> on page 29 |      |     | 0   | 0        | 0 | 0 | 0 |  |

| R/W     | R                              | R    | R   | R   | R        | R | R | R |  |

| Address | FF0H                           |      |     |     |          |   |   |   |  |

Table 185. Reset Status Register (RSTSTAT)