# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0430sh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| Table 149. | ADC Sample Settling Time (ADCSST) 215        |

|------------|----------------------------------------------|

| Table 150. | ADC Sample Time (ADCST) 215                  |

| Table 151. | Power Control Register 0 (PWRCTL0) 216       |

| Table 152. | LED Drive Enable (LEDEN)                     |

| Table 153. | LED Drive Level High Register (LEDLVLH)      |

| Table 154. | LED Drive Level Low Register (LEDLVLL)       |

| Table 155. | Oscillator Control Register (OSCCTL) 217     |

| Table 156. | Comparator Control Register (CMP0) 218       |

| Table 157. | Interrupt Request 0 Register (IRQ0) 218      |

| Table 158. | IRQ0 Enable High Bit Register (IRQ0ENH)      |

| Table 159. | IRQ0 Enable Low Bit Register (IRQ0ENL)       |

| Table 160. | Interrupt Request 1 Register (IRQ1) 219      |

| Table 161. | IRQ1 Enable High Bit Register (IRQ1ENH)      |

| Table 162. | IRQ1 Enable Low Bit Register (IRQ1ENL)       |

| Table 163. | Interrupt Request 2 Register (IRQ2) 220      |

| Table 164. | IRQ2 Enable High Bit Register (IRQ2ENH)      |

| Table 165. | IRQ2 Enable Low Bit Register (IRQ2ENL)       |

| Table 166. | Interrupt Edge Select Register (IRQES) 221   |

| Table 167. | Shared Interrupt Select Register (IRQSS) 221 |

| Table 168. | Interrupt Control Register (IRQCTL) 221      |

| Table 169. | Port A GPIO Address Register (PAADDR) 222    |

| Table 170. | Port A Control Registers (PACTL) 222         |

| Table 171. | Port A Input Data Registers (PAIN) 222       |

| Table 172. | Port A Output Data Register (PAOUT) 223      |

| Table 173. | Port B GPIO Address Register (PBADDR) 223    |

| Table 174. | Port B Control Registers (PBCTL) 223         |

| Table 175. | Port B Input Data Registers (PBIN) 223       |

| Table 176. | Port B Output Data Register (PBOUT) 224      |

| Table 177. | Port C GPIO Address Register (PCADDR) 224    |

| Table 178. | Port C Control Registers (PCCTL)             |

|            |                                              |

# **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit CPU, meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 CPU code

- Expanded internal register file allows access up to 4KB

- New instructions improve execution efficiency for code developed using high-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the register file

- Up to 10 MIPS operation

- C Compiler-friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

# **General Purpose Input/Output**

The Z8 Encore! F0830 Series features up to 25 port pins (Ports A–D) for general-purpose input/output (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable.

# **Flash Controller**

The Flash Controller programs and erases the Flash memory. It also supports protection against accidental programming and erasure.

#### 28

# Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! F0830 Series device is in STOP Mode and the external RESET pin is driven low, a system reset occurs. Because of a glitch filter operating on the RESET pin, the low pulse must be greater than the minimum width specified about 12 ns or it is ignored. The EXT bit in the Reset Status (RSTSTAT) Register is set.

# **Debug Pin Driven Low**

Debug reset is initiated when the On-Chip Debugger detects any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received STOP bit is Low)

- Transmit collision (simultaneous OCD and host transmission detected by the OCD)

When the Z8F0830 Series device is operating in STOP Mode, the debug reset will cause a system reset. The On-Chip Debugger block is not reset, but the remainder of the chip's operations go through a normal system reset. The POR bit in the Reset Status (RSTSTAT) Register is set to 1.

# **Reset Register Definitions**

The following sections define the Reset registers.

#### **Reset Status Register**

The Reset Status (RSTSTAT) Register, shown in Table 12, is a read-only register that indicates the source of the most recent Reset event, Stop Mode Recovery event or Watchdog Timer time-out event. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer Control Register, which is writeonly.

# General Purpose Input/Output

The Z8 Encore! F0830 Series products support a maximum of 25 port pins (Ports A–D) for General Purpose Input/Output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

# **GPIO Port Availability by Device**

Table 15 lists the port pins available with each device and package type.

|                                                   |         | 10-Bit |        |        |        |        |           |

|---------------------------------------------------|---------|--------|--------|--------|--------|--------|-----------|

| Devices                                           | Package | ADC    | Port A | Port B | Port C | Port D | Total I/O |

| Z8F1232, Z8F0830,<br>Z8F0430, Z8F0230,<br>Z8F0130 | 20-pin  | Yes    | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F1233, Z8F0831<br>Z8F0431, Z8F0231<br>Z8F0131   | 20-pin  | No     | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F1232, Z8F0830,<br>Z8F0430, Z8F0230,<br>Z8F0130 | 28-pin  | Yes    | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F1233, Z8F0831<br>Z8F0431, Z8F0231<br>Z8F0131   | 28-pin  | No     | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

#### Table 15. Port Availability by Device and Package Type

# Port A–D Output Data Register

The Port A–D Output Data Register, shown in Table 30, controls the output data to the pins.

| Bit     | 7     | 6                           | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-----------------------------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6                       | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0                           | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W R/W R/W R/W R/W R/W R/W |       |       |       |       |       |       |  |  |

| Address |       | FD3H, FD7H, FDBH, FDFH      |       |       |       |       |       |       |  |  |

### Table 30. Port A–D Output Data Register (PxOUT)

#### Bit Description

#### [7:0] Port Output Data

PxOUT These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for Alternate function operation.

0 = Drive a logical 0 (Low).

1= Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding port output Control Register bit to 1.

Note: x indicates the specific GPIO port pin number (7–0).

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# Architecture

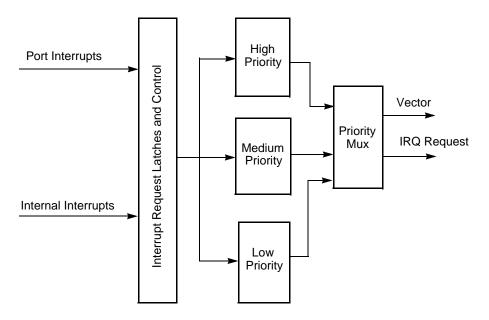

Figure 9 displays the Interrupt Controller block diagram.

Figure 9. Interrupt Controller Block Diagram

# Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 55

Interrupt Vectors and Priority: see page 56

Interrupt Assertion: see page 56

Software Interrupt Assertion: see page 57

# **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables the interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (enable interrupt) instruction

- Execution of an IRET (return from interrupt) instruction

# **Timers**

The Z8 Encore! F0830 Series products contain up to two 16-bit reloadable timers that can be used for timing, event counting or generation of pulse width modulated (PWM) signals. The timers feature include:

- 16-bit reload counter

- Programmable prescaler with prescale values ranging from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

# Architecture

Figure 10 displays the architecture of the timers.

tion and reload events. The user can configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the timer input signal to initiate the counting.

## **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE Mode, the timer begins counting on the first external timer input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the timer input signal, captures the current count value. The capture value is written to the timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt is caused by an input capture event.

If no capture event occurs, the timer counts up to the 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE/COMPARE Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode.

- Set the prescale value.

- Set the capture edge (rising or falling) for the timer input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

- 4. Enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and Reload events. The user can configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL1 Register.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

# **ADC Interrupt**

The ADC can generate an interrupt request when a conversion has been completed. An interrupt request that is pending when the ADC is disabled is not cleared automatically.

# **Reference Buffer**

The reference buffer, RBUF, supplies the reference voltage for the ADC. When enabled, the internal voltage reference generator supplies the ADC. When RBUF is disabled, the ADC must have the reference voltage supplied externally through the  $V_{REF}$  pin in 28-pin package. RBUF is controlled by the REFEN bit in the ADC Control Register.

# **Internal Voltage Reference Generator**

The internal voltage reference generator provides the voltage VR2, for the RBUF. VR2 is 2V.

# **Calibration and Compensation**

A user can perform calibration and store the values into Flash or the user code can perform a manual offset calibration. There is no provision for manual gain calibration.

# **ADC Control Register Definitions**

The ADC Control registers are defined in this section.

Flash information area is mapped into program memory and overlays the 128 bytes in the address range FE00H to FE7FH. When the information area access is enabled, all reads from these program memory addresses return the information area data rather than the program memory data. Access to the Flash information area is read-only.

The trim bits are handled differently than the other Zilog Flash option bits. The trim bits are the hybrid of the user option bits and the standard Zilog option bits. These trim bits must be user-accessible for reading at all times using external registers regardless of the state of bit 7 in the Flash Page Select Register. Writes to the trim space change the value of the Option Bit Holding Register but do not affect the Flash bits, which remain as read-only.

| Program Memory |                                                                                          |

|----------------|------------------------------------------------------------------------------------------|

| Address (Hex)  | Function                                                                                 |

| FE00–FE3F      | Zilog option bits                                                                        |

| FE40–FE53      | Part number<br>20-character ASCII alphanumeric code<br>Left justified and filled with FH |

| FE54–FE5F      | Reserved                                                                                 |

| FE60–FE7F      | Reserved                                                                                 |

Table 70. Z8F083 Flash Memory Area Map

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for byte programming, page erase and mass erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The flowchart in Figure 19 display basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase and Mass Erase) displayed in Figure 19.

# Operation

The following section describes the operation of the On-Chip Debugging function.

# **OCD** Interface

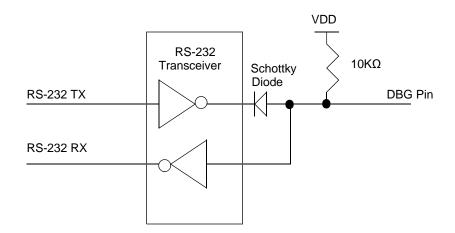

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, which means that transmission and data retrieval cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface between the Z8 Encore! F0830 Series products and the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figures 21 and 22. The recommended method is the buffered implementation depicted in Figure 22. The DBG pin must always be connected to  $V_{DD}$  through an external pull-up resistor.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

#### Figure 21. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

|                   |                              | T <sub>A</sub> = 0 | )°C to - | ⊦70°C | $T_A = -4$ | 10°C to          | +105°C |       |                                   |  |

|-------------------|------------------------------|--------------------|----------|-------|------------|------------------|--------|-------|-----------------------------------|--|

| Symbol            | Parameter                    | Min                | Тур      | Мах   | Min        | Тур              | Max    | Units | Conditions                        |  |

| I <sub>LED</sub>  | Controlled                   |                    |          |       | 1.5        | 3                | 4.5    | mA    | See GPIO section on               |  |

|                   | Current Drive                |                    |          |       | 2.8        | 7                | 10.5   | mA    | LED description                   |  |

|                   |                              |                    |          |       | 7.8        | 13               | 19.5   | mA    | -                                 |  |

|                   |                              |                    |          |       | 12         | 20               | 30     | mA    | -                                 |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance |                    |          |       | _          | 8.0 <sup>2</sup> | _      | pF    | TBD                               |  |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance       |                    |          |       | -          | 8.0 <sup>2</sup> | -      | pF    | TBD                               |  |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance      |                    |          |       | -          | 9.5 <sup>2</sup> | -      | pF    | TBD                               |  |

| I <sub>PU</sub>   | Weak Pull-up<br>Current      |                    |          |       | 50         | 120              | 220    | μA    | V <sub>DD</sub> = 2.7 - 3.6V      |  |

| ICCH <sup>3</sup> | Supply Current in HALT Mode  |                    |          |       |            | TBD              |        | mA    | TBD                               |  |

| ICCS              | Supply Current in STOP Mode  |                    |          | 2     |            |                  | 8      | μA    | Without Watchdog Timer<br>running |  |

#### Table 116. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

3. See Figure 31 for HALT Mode current.

186

# Packaging

Zilog's F0830 Series of MCUs includes the Z8F0130, Z8F0131, Z8F0230, Z8F0231, Z8F1232 and Z8F1233 devices, which are available in the following packages:

- 20-Pin Quad Flat No-Lead Package (QFN)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Plastic Dual-Inline Package (PDIP)

- 20-pin Small Shrink Outline Package (SSOP)

- 28-Pin Quad Flat No-Lead Package (QFN)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Shrink Outline Package (SSOP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

207

Table 129 lists the pin count by package.

|         | Pin Count    |    |  |  |  |  |

|---------|--------------|----|--|--|--|--|

| Package | 20           | 28 |  |  |  |  |

| PDIP    | $\checkmark$ |    |  |  |  |  |

| QFN     | $\checkmark$ |    |  |  |  |  |

| SOIC    | $\checkmark$ |    |  |  |  |  |

| SSOP    | $\checkmark$ |    |  |  |  |  |

### Table 129. Package and Pin Count Description

## Hex Address: F01

### Table 131. Timer 0 Low Byte Register (T0L)

| Bit     | 7                           | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----------------------------|------|---|---|---|---|---|---|--|--|

| Field   |                             | TL   |   |   |   |   |   |   |  |  |

| RESET   | 0                           | 0    | 0 | 0 | 0 | 0 | 0 | 1 |  |  |

| R/W     | R/W R/W R/W R/W R/W R/W R/W |      |   |   |   |   |   |   |  |  |

| Address |                             | F01H |   |   |   |   |   |   |  |  |

## Hex Address: F02

#### Table 132. Timer 0 Reload High Byte Register (T0RH)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | TRH                         |   |   |   |   |   |   |  |  |

| RESET   | 1   | 1                           | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | F02H                        |   |   |   |   |   |   |  |  |

# Hex Address: F03

### Table 133. Timer 0 Reload Low Byte Register (T0RL)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | TRL                         |   |   |   |   |   |   |  |  |

| RESET   | 1   | 1                           | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | F03H                        |   |   |   |   |   |   |  |  |

## Hex Address: F04

#### Table 134. Timer 0 PWM High Byte Register (T0PWMH)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | PWMH                        |   |   |   |   |   |   |  |  |

| RESET   | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | F04H                        |   |   |   |   |   |   |  |  |

# Low Power Control

For more information about the Power Control Register, see the <u>Power Control Register</u> <u>Definitions</u> section on page 31.

# Hex Address: F80

| Bit     | 7    | 6        | 5   | 4   | 3        | 2        | 1    | 0        |

|---------|------|----------|-----|-----|----------|----------|------|----------|

| Field   |      | Reserved |     | VBO | Reserved | Reserved | COMP | Reserved |

| RESET   | 1    | 0        | 0   | 0   | 1        | 0        | 0    | 0        |

| R/W     | R/W  | R/W      | R/W | R/W | R/W      | R/W      | R/W  | R/W      |

| Address | F80H |          |     |     |          |          |      |          |

#### Table 151. Power Control Register 0 (PWRCTL0)

## Hex Address: F81

This address range is reserved.

# **LED Controller**

For more information about the LED Drive registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

## Hex Address: F82

| Bit     | 7   | 6               | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | LEDEN[7:0]      |     |     |     |     |     |     |  |

| RESET   | 0   | 0 0 0 0 0 0 0 0 |     |     |     |     |     |     |  |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     |                 |     | F8  | 2H  |     |     |     |  |

### Table 152. LED Drive Enable (LEDEN)

## Hex Address: F83

#### Table 153. LED Drive Level High Register (LEDLVLH)

| Bit     | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | LEDLVLH[7:0] |     |     |     |     |     |     |  |

| RESET   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F83H         |     |     |     |     |     |     |  |

## Hex Address: F84

#### Table 154. LED Drive Level Low Register (LEDLVLL)

| Bit     | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | LEDLVLL[7:0] |     |     |     |     |     |     |  |

| RESET   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     |              |     | F8  | 4H  |     |     |     |  |

## Hex Address: F85

This address range is reserved.

# **Oscillator Control**

For more information about the Oscillator Control registers, see the <u>Oscillator Control</u> <u>Register Definitions</u> section on page 154.

### Hex Address: F86

| Table 155. | Oscillator | Control | Register | (OSCCTL) |

|------------|------------|---------|----------|----------|

|------------|------------|---------|----------|----------|

| Bit     | 7     | 6     | 5     | 4     | 3     | 2      | 1   | 0   |  |

|---------|-------|-------|-------|-------|-------|--------|-----|-----|--|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN | SCKSEL |     |     |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0      | 0   | 0   |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W    | R/W | R/W |  |

| Address |       | F86H  |       |       |       |        |     |     |  |

## Hex Address: FD3

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |       | FD3H  |       |       |       |       |       |       |  |  |

#### Table 172. Port A Output Data Register (PAOUT)

## Hex Address: FD4

#### Table 173. Port B GPIO Address Register (PBADDR)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | PADDR[7:0]                  |   |   |   |   |   |   |  |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | FD4H                        |   |   |   |   |   |   |  |  |

# Hex Address: FD5

## Table 174. Port B Control Registers (PBCTL)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | PCTL                        |   |   |   |   |   |   |  |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | FD5H                        |   |   |   |   |   |   |  |  |

## Hex Address: FD6

#### Table 175. Port B Input Data Registers (PBIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|------|------|------|------|------|------|------|------|--|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |  |

| Address |      | FD6H |      |      |      |      |      |      |  |

# Hex Address: FDB

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address |       | FDBH  |       |       |       |       |       |       |  |

## Hex Address: FDC

#### Table 181. Port D GPIO Address Register (PDADDR)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | PADDR[7:0]                  |   |   |   |   |   |   |  |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | FDCH                        |   |   |   |   |   |   |  |  |

# Hex Address: FDD

### Table 182. Port D Control Registers (PDCTL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PCTL |     |     |     |     |     |     |     |

| RESET   | 00H  |     |     |     |     |     |     |     |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FDDH |     |     |     |     |     |     |     |

## Hex Address: FDE

This address range is reserved.

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

JP 169 LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167 LDX 168 LEA 168 load 168 logical 169 **MULT 167 NOP 168** OR 169 ORX 169 POP 168 **POPX 168** program control 169 **PUSH 168** PUSHX 168 RCF 167, 168 **RET 169** RL 169 **RLC 169** rotate and shift 169 RR 170 **RRC** 170 **SBC 167** SCF 167. 168 **SRA 170 SRL 170 SRP 168 STOP 168 SUB 167 SUBX 167 SWAP 170** TCM 167 **TCMX 167** TM 167 TMX 167 **TRAP 169** watch-dog timer refresh 168 XOR 169 **XORX 169** instructions, eZ8 classes of 166

interrupt control register 67 interrupt controller 53 architecture 53 interrupt assertion types 56 interrupt vectors and priority 56 operation 55 register definitions 57 software interrupt assertion 57 interrupt edge select register 65 interrupt request 0 register 58 interrupt request 1 register 59 interrupt request 2 register 60 interrupt return 169 interrupt vector listing 53 IR 164 Ir 164 **IRET 169** IRQ0 enable high and low bit registers 60 IRQ1 enable high and low bit registers 62 IRQ2 enable high and low bit registers 63 **IRR 164** Irr 164

# J

JP 169 jump, conditional, relative, and relative conditional 169

# L

LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167, 168 LDX 168 LEA 168 load constant 167 load constant to/from program memory 168 load constant with auto-increment addresses 168 load effective address 168 load external data 168