# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0430sh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                                  | Description                                                                                                                                                                                 | Page<br>No.                                                                  |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Dec<br>2012 | 13                | GPIO                                                                                                                             | Modified GPIO Port D0 language in Shared<br>Reset Pin section and Port Alternate Func-<br>tion Mapping table.                                                                               | <u>35, 36</u>                                                                |

| Sep<br>2011 | 12                | LED Drive Enable Register                                                                                                        | Clarified statement surrounding the Alternate<br>Function Register as it relates to the LED<br>function; revised Sector Based Flash Protec-<br>tion description; revised Packaging chapter. | <u>51,</u><br><u>115,</u><br><u>199</u>                                      |

| Dec<br>2007 | 11                | n/a                                                                                                                              | Updated all instances of <i>Z8 Encore! XP</i><br><i>F0830</i> to <i>Z8 Encore! F0830</i> .                                                                                                  | All                                                                          |

| Nov<br>2007 | 10                | DC Characteristics, On-Chip<br>Peripheral AC and DC Electri-<br>cal Characteristics                                              | Updated Tables 116 and and 122.                                                                                                                                                             | <u>185,</u><br><u>193</u>                                                    |

| Sep<br>2007 | 09                | Timers, PWM SINGLE OUT-<br>PUT Mode, PWM DUAL OUT-<br>PUT Mode, Analog-to-Digital<br>Converter, Reference Buffer.                | Updated Figures 2 and 4, Table 4.                                                                                                                                                           | <u>8, 9,</u><br><u>11, 68,</u><br><u>74, 75,</u><br><u>98,</u><br><u>101</u> |

| Apr<br>2007 | 08                | Optimizing NVDS Memory<br>Usage for Execution Speed,<br>On-Chip Peripheral AC and DC<br>Electrical Characteristics               | Added a note under Table 93 in Nonvolatile<br>Data Storage chapter. Updated Table 121<br>and Table 122 in Electrical Characteristics<br>chapter. Other style updates.                       | <u>137,</u><br><u>193,</u><br><u>193</u>                                     |

| Dec         | 07                | General Purpose Input/Output                                                                                                     | Added PD0 in Table 16.                                                                                                                                                                      | <u>38</u>                                                                    |

| 2006        |                   | Overview, Interrupt Controller                                                                                                   | Changed the number of interrupts to 17.                                                                                                                                                     | <u>1,5, 53</u>                                                               |

|             |                   | Nonvolatile Data Storage                                                                                                         | Updated chapter.                                                                                                                                                                            | <u>136</u>                                                                   |

|             |                   | Oscillator Control Register Defi-<br>nitions, AC Characteristics, On-<br>Chip Peripheral AC and DC<br>Electrical Characteristics | Updated Tables 117 and 122. Added Figure 24.                                                                                                                                                | <u>156,</u><br><u>189,</u><br><u>193</u>                                     |

|             |                   | Ordering Information                                                                                                             | Updated Part Number Suffix Designations.                                                                                                                                                    | 205                                                                          |

|             |                   | n/a                                                                                                                              | Removed Preliminary stamp from footer.                                                                                                                                                      | All                                                                          |

iii

# **Table of Contents**

| Revision History                   | ii |

|------------------------------------|----|

| List of Figures                    | х  |

| List of Tables x                   | ii |

| Overview                           | 1  |

| Features                           | 1  |

| Part Selection Guide               | 2  |

| Block Diagram                      | 3  |

| CPU and Peripheral Overview        | 4  |

| General Purpose Input/Output       | 4  |

| Flash Controller                   | 4  |

| Nonvolatile Data Storage           | 5  |

| Internal Precision Oscillator      | 5  |

| External Crystal Oscillator        | 5  |

| 10-Bit Analog-to-Digital Converter | 5  |

| Analog Comparator                  | 5  |

| Timers                             | 5  |

| Interrupt Controller               | 5  |

| Reset Controller                   | 6  |

| On-Chip Debugger                   | 6  |

| Acronyms and Expansions            | 6  |

| Pin Description                    | 7  |

| Available Packages                 |    |

| Pin Configurations                 | 7  |

| Signal Descriptions                | 1  |

| Pin Characteristics                |    |

| Address Space                      | 4  |

| Register File                      |    |

| Program Memory                     | 5  |

| Data Memory                        |    |

| Flash Information Area 1           |    |

| Register Map 1                     | 7  |

| Reset and Stop Mode Recovery       | 21 |

| Reset Types                        |    |

| Reset Sources                      |    |

| Power-On Reset                     |    |

## **Data Memory**

The Z8 Encore! F0830 Series does not use the eZ8 CPU's 64KB data memory address space.

## **Flash Information Area**

Table 7 maps the Z8 Encore! F0830 Series Flash information area. The 128-byte information area is accessed, by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash information area is mapped into program memory and overlays these 128 bytes at addresses FE00H to FE7FH. When information area access is enabled, all reads from these program memory addresses return information area data rather than program memory data. Access to the Flash information area is read-only.

| Program<br>Memory<br>Address (Hex) | Function                                                                                 |

|------------------------------------|------------------------------------------------------------------------------------------|

| FE00–FE3F                          | Zilog option bits                                                                        |

| FE40-FE53                          | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH |

| FE54–FE5F                          | Reserved                                                                                 |

| FE60–FE7F                          | Reserved                                                                                 |

| FE80–FFFF                          | Reserved                                                                                 |

#### Table 7. Z8 Encore! F0830 Series Flash Memory Information Area Map

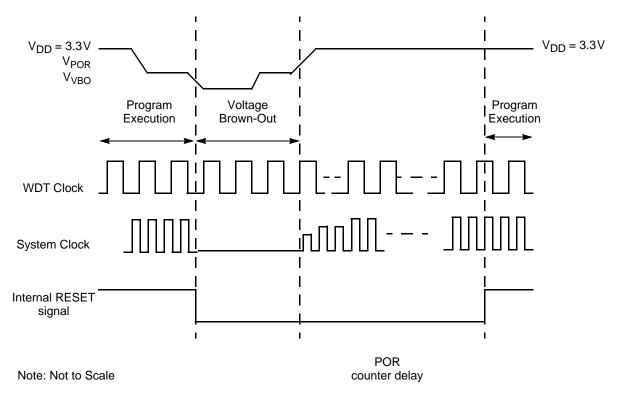

The Voltage Brown-Out circuit can be either enabled or disabled during STOP Mode. Operations during STOP Mode is set by the VBO\_AO Flash option bit. See the <u>Flash</u> <u>Option Bits</u> chapter on page 124 for information about configuring VBO\_AO.

Figure 7. Voltage Brown-Out Reset Operation

## Watchdog Timer Reset

If the device is operating in NORMAL or STOP Mode, the Watchdog Timer can initiate a system reset at time-out if the WDT\_RES Flash option bit is programmed to 1; this state is the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt – not a system reset – at time-out. The WDT status bit in the Reset Status (RSTSTAT) Register is set to 1 to signify that the reset was initiated by the Watchdog Timer.

## **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-triggered input and an internal pull-up resistor. After the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the system reset sequence. Because of the possible asynchronicity of the system

### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit                  | 7                       | 6                                                                        | 5                           | 4            | 3    | 2        | 1    | 0    |

|----------------------|-------------------------|--------------------------------------------------------------------------|-----------------------------|--------------|------|----------|------|------|

| Field                |                         | Rese                                                                     | erved                       |              | PC3I | PC2I     | PC1I | PC0I |

| RESET                | 0                       | 0                                                                        | 0                           | 0            | 0    | 0        | 0    | 0    |

| R/W                  | R/W                     | R/W R/W R/W R/W R/W R/W R/W                                              |                             |              |      |          |      |      |

| Address              |                         | FC6H                                                                     |                             |              |      |          |      |      |

| Bit                  | Description             | n                                                                        |                             |              |      |          |      |      |

| [7:4]                | Reserved<br>These regis | Reserved<br>These registers are reserved and must be programmed to 0000. |                             |              |      |          |      |      |

| [3]<br>PC <i>x</i> l | 1 = An inter            | rrupt reques                                                             | t is pending<br>t from GPIO | Port C pin 2 |      | service. |      |      |

| Note: x in           | dicates the sp          | ecific GPIO p                                                            | ort pin numbe               | ər (3–0).    |      |          |      |      |

#### Table 37. Interrupt Request 2 Register (IRQ2)

## **IRQ0 Enable High and Low Bit Registers**

Table 38 lists the priority control values for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling service for interrupts in the Interrupt Request 0 Register. Priority is generated by setting the bits in each register.

| IRQ0EN                                                       | IH[x] | IRQ0ENL[x] | Priority | Description |  |

|--------------------------------------------------------------|-------|------------|----------|-------------|--|

| C                                                            | )     | 0          | Disabled | Disabled    |  |

| C                                                            | )     | 1          | Level 1  | Low         |  |

| 1                                                            |       | 0          | Level 2  | Nominal     |  |

| 1                                                            |       | 1          | Level 3  | High        |  |

| Note: <i>x</i> indicates the register bits in the range 7–0. |       |            |          |             |  |

Table 38. IRQ0 Enable and Priority Encoding

## Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 54 and 55, control PWM operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   |     | PWMH       |     |     |     |     |     |     |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F04H, F0CH |     |     |     |     |     |     |

#### Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

#### Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|------|-----|-----|-----|-----|-----|-----|

| Field   |            | PWML |     |     |     |     |     |     |

| RESET   | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F05H, F0DH |      |     |     |     |     |     |     |

#### Bit Description

| [7:0] | Pulse Width Modulator High and Low Bytes                                                     |

|-------|----------------------------------------------------------------------------------------------|

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1).                         |

|       | The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operat-      |

|       | ing in capture or CAPTURE/COMPARE modes.                                                     |

| Bit   | Description (Continued)                                                                   |

|-------|-------------------------------------------------------------------------------------------|

| [2:0] | Timer Mode                                                                                |

| TMODE | This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of |

|       | the timer. TMODEHI is the most significant bit of the timer mode selection value.         |

|       | 0000 = ONE-SHOT Mode.                                                                     |

|       | 0001 = CONTINUOUS Mode.                                                                   |

|       | 0010 = COUNTER Mode.                                                                      |

|       | 0011 = PWM SINGLE OUTPUT Mode.                                                            |

|       | 0100 = CAPTURE Mode.                                                                      |

|       | 0101 = COMPARE Mode.                                                                      |

|       | 0110 = GATED Mode.                                                                        |

|       | 0111 = CAPTURE/COMPARE Mode.                                                              |

|       | 1000 = PWM DUAL OUTPUT Mode.                                                              |

|       | 1001 = CAPTURE RESTART Mode.                                                              |

|       | 1010 = COMPARATOR COUNTER Mode.                                                           |

91

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

113

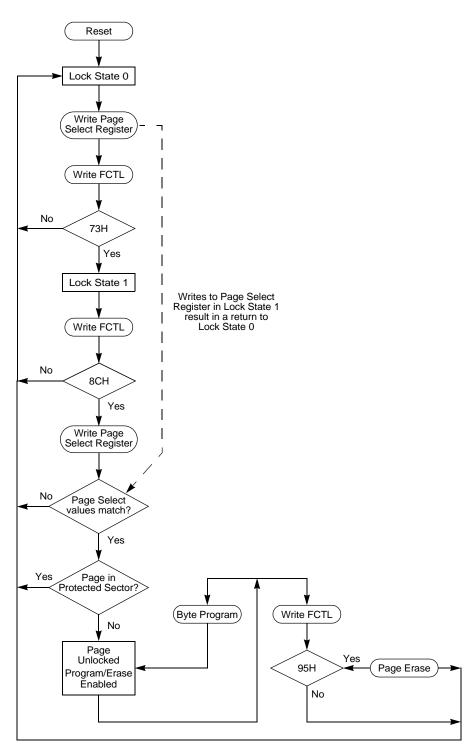

Figure 19. Flash Controller Operation Flow Chart

**Note:** The bit values used in Table 85 are set at the factory; no calibration is required.

#### Table 86. Trim Option Bits at 0002H (TIPO)

| Bit       | 7                                               | 6                             | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|-------------------------------------------------|-------------------------------|---|---|---|---|---|---|

| Field     |                                                 | IPO_TRIM                      |   |   |   |   |   |   |

| RESET     |                                                 | U                             |   |   |   |   |   |   |

| R/W       |                                                 | R/W                           |   |   |   |   |   |   |

| Address   |                                                 | Information Page Memory 0022H |   |   |   |   |   |   |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                               |   |   |   |   |   |   |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

**Note:** The bit values used in Table 86 are set at the factory; no calibration is required.

#### Table 87. Trim Option Bits at 0003H (TVBO)

| Bit       | 7           | 6                             | 5             | 4  | 3        | 2 | 1        | 0 |

|-----------|-------------|-------------------------------|---------------|----|----------|---|----------|---|

| Field     |             | Rese                          | erved         |    | Reserved |   | VBO_TRIM |   |

| RESET     |             | ι                             | J             |    | U        | 1 | 0        | 0 |

| R/W       |             | R/                            | W             |    | R/W      |   | R/W      |   |

| Address   |             | Information Page Memory 0023H |               |    |          |   |          |   |

| Note: U = | Unchanged b | by Reset. R/W                 | / = Read/Writ | e. |          |   |          |   |

| Bit      | Description                                                                 |

|----------|-----------------------------------------------------------------------------|

| [7:3]    | <b>Reserved</b><br>These bits are reserved and must be programmed to 11111. |

|          |                                                                             |

| [2]      | VBO Trim Values                                                             |

| VBO_TRIM | Contains factory-trimmed values for the oscillator and the VBO.             |

>

## Nonvolatile Data Storage

Z8 Encore! F0830 Series devices contain a Nonvolatile Data Storage (NVDS) element of up to 64 bytes (except when in Flash 12KB mode). This type of memory can perform over 100,000 write cycles.

## Operation

NVDS is implemented by special-purpose Zilog software stored in areas of program memory that are not user-accessible. These special-purpose routines use Flash memory to store the data, and incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

**Note:** The products in the Z8 Encore! F0830 Series feature multiple NVDS array sizes. See the <u>Z8 Encore! F0830 Series Family Part Selection Guide</u> section on page 2 for details.

## **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a predefined address outside of program memory that is accessible to the user. Both the NVDS address and data are singlebyte values. In order to not disturb the user code, these routines save the working register set before using it so that 16 bytes of stack space are required to preserve the site. After finishing the call to these routines, the working register set of the user code is recovered.

During both read and write accesses to the NVDS, interrupt service is not disabled. Any interrupts that occur during NVDS execution must not disturb the working register and existing stack contents; otherwise, the array can become corrupted. Zilog recommends the user disable interrupts before executing NVDS operations.

Use of the NVDS requires 16 bytes of available stack space. The contents of the working register set are saved before calling NVDS read or write routines.

For correct NVDS operation, the Flash Frequency registers must be programmed based on the system clock frequency. See *the* <u>Flash Operation Timing Using the Flash Frequency</u><u>Registers</u> *section on page 114*.

149

#### Table 96. OCD Control Register (OCDCTL)

| Bit           | 7                                                                  | 6                                                                                             | 5                                                                                         | 4                                                              | 3                                                          | 2                                                     | 1                                           | 0                        |

|---------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|--------------------------|

| Field         | DBGMODE                                                            | BRKEN                                                                                         | DBGACK                                                                                    |                                                                | Res                                                        | erved                                                 |                                             | RST                      |

| RESET         | 0                                                                  | 0                                                                                             | 0                                                                                         | 0                                                              | 0                                                          | 0                                                     | 0                                           | 0                        |

| R/W           | R/W                                                                | R/W                                                                                           | R/W                                                                                       | R                                                              | R                                                          | R                                                     | R                                           | R/W                      |

| Bit           | Descriptio                                                         | on                                                                                            |                                                                                           |                                                                |                                                            |                                                       |                                             |                          |

| [7]<br>DBGMOD | stops fetch<br>automatica<br>Flash read<br>cannot be<br>0 = The Z8 | e enters DE<br>ning new ins<br>ally set whe<br>protect option<br>written to 0<br>B Encore! F( | BUG Mode<br>structions. C<br>n a BRK inst<br>on bit is enal<br>0830 Series<br>0830 Series | learing this<br>ruction is de<br>bled, this bit<br>device is o | bit causes t<br>ecoded and<br>can only be<br>perating in N | he eZ8 CPU<br>breakpoints<br>e cleared by<br>NORMAL M | J to restart.<br>are enable<br>resetting th | This bit is<br>d. If the |

| [6]<br>BRKEN  | are disable<br>when a BR<br>cally set to<br>0 = Breakp             | ntrols the be<br>ed and the E<br>K instructio                                                 |                                                                                           | on behaves                                                     | similar to a                                               | n NOP insti                                           | uction. If thi                              | s bit is 1               |

| [5]<br>DBGACK | This bit en<br>Debug ack<br>0 = Debug                              | nowledge o<br>acknowled                                                                       | ebug acknow<br>character (F<br>ge is disable<br>ge is enable                              | FH) to the h<br>ed.                                            |                                                            |                                                       |                                             | ends a                   |

| [4:1]         | Reserved<br>These bits                                             | are reserve                                                                                   | ed and must                                                                               | be progran                                                     | nmed to 000                                                | 00.                                                   |                                             |                          |

| [0]<br>RST    | Power-On<br>bit is autor<br>0 = No effe                            | Reset seques<br>natically cle<br>ect.                                                         | sets the Z8F<br>ience with th<br>ared to 0 at<br>ad protect o                             | the end of t                                                   | h that the Or<br>the reset se                              | n-Chip Debi                                           |                                             |                          |

| Assembly      |                              |     |     | Address Op<br>Mode Code(s) |   |   | Fla | ags | Fetch | Instr. |   |   |

|---------------|------------------------------|-----|-----|----------------------------|---|---|-----|-----|-------|--------|---|---|

| Mnemonic      | Symbolic Operation           | dst | src | (Hex)                      | С | Ζ | S   | ۷   | D     | Н      |   |   |

| CLR dst       | dst ← 00H                    | R   |     | B0                         | _ | _ | _   | -   | _     | _      | 2 | 2 |

|               |                              | IR  |     | B1                         | _ |   |     |     |       |        | 2 | 3 |

| COM dst       | dst ← ~dst                   | R   |     | 60                         | - | * | *   | 0   | -     | _      | 2 | 2 |

|               |                              | IR  |     | 61                         | _ |   |     |     |       |        | 2 | 3 |

| CP dst, src   | dst - src                    | r   | r   | A2                         | * | * | *   | *   | -     | -      | 2 | 3 |

|               |                              | r   | lr  | A3                         | _ |   |     |     |       |        | 2 | 4 |

|               |                              | R   | R   | A4                         | _ |   |     |     |       |        | 3 | 3 |

|               |                              | R   | IR  | A5                         | _ |   |     |     |       |        | 3 | 4 |

|               |                              | R   | IM  | A6                         | _ |   |     |     |       |        | 3 | 3 |

|               |                              | IR  | IM  | A7                         | _ |   |     |     |       |        | 3 | 4 |

| CPC dst, src  | dst - src - C                | r   | r   | 1F A2                      | * | * | *   | *   | -     | -      | 3 | 3 |

|               |                              | r   | lr  | 1F A3                      | _ |   |     |     |       |        | 3 | 4 |

|               |                              | R   | R   | 1F A4                      | _ |   |     |     |       |        | 4 | 3 |

|               |                              | R   | IR  | 1F A5                      | _ |   |     |     |       |        | 4 | 4 |

|               |                              | R   | IM  | 1F A6                      | _ |   |     |     |       |        | 4 | 3 |

|               |                              | IR  | IM  | 1F A7                      | _ |   |     |     |       |        | 4 | 4 |

| CPCX dst, src | dst - src - C                | ER  | ER  | 1F A8                      | * | * | *   | *   | _     | _      | 5 | 3 |

|               |                              | ER  | IM  | 1F A9                      | _ |   |     |     |       |        | 5 | 3 |

| CPX dst, src  | dst - src                    | ER  | ER  | A8                         | * | * | *   | *   | -     | -      | 4 | 3 |

|               |                              | ER  | IM  | A9                         | _ |   |     |     |       |        | 4 | 3 |

| DA dst        | dst ← DA(dst)                | R   |     | 40                         | * | * | *   | Х   | -     | _      | 2 | 2 |

|               |                              | IR  |     | 41                         | _ |   |     |     |       |        | 2 | 3 |

| DEC dst       | $dst \gets dst \text{ - } 1$ | R   |     | 30                         | _ | * | *   | *   | _     | _      | 2 | 2 |

|               |                              | IR  |     | 31                         | _ |   |     |     |       |        | 2 | 3 |

| DECW dst      | dst ← dst - 1                | RR  |     | 80                         | _ | * | *   | *   | _     | -      | 2 | 5 |

|               |                              | IRR |     | 81                         | _ |   |     |     |       |        | 2 | 6 |

| DI            | IRQCTL[7] ← 0                |     |     | 8F                         | _ | _ | _   | _   | _     | _      | 1 | 2 |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| Abbreviation | Description                             | Abbreviation                                      | Description            |

|--------------|-----------------------------------------|---------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                               | Indirect Register Pair |

| CC           | Condition code                          | р                                                 | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displace-<br>ment | r                                                 | 4-bit Working Register |

| DA           | Destination address                     | R                                                 | 8-bit register         |

| ER           | Extended Addressing Register            | r1, R1, Ir1, Irr1,<br>IR1, rr1, RR1,<br>IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address         |

| lr           | Indirect Working Register               | RA                                                | Relative               |

| IR           | Indirect Register                       | rr                                                | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                                | Register Pair          |

#### Table 114. Op Code Map Abbreviations

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F0830 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 115 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | 0       | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     |       |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 125     | mA    |       |

#### **Table 115. Absolute Maximum Ratings**

188

Figure 32 displays the typical current consumption versus the system clock frequency in NORMAL Mode.

Figure 32.  $I_{CC}$  Versus System Clock Frequency (NORMAL Mode)

|                             |     | = 2.7 to<br>0°C to + |     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to +105°C |     |     |        |                                                 |  |

|-----------------------------|-----|----------------------|-----|-------------------------------------------------------------------|-----|-----|--------|-------------------------------------------------|--|

| Parameter                   | Min | Тур                  | Max | Min                                                               | Тур | Max | Units  | Notes                                           |  |

| NVDS Byte Read<br>Time      |     |                      |     | 71                                                                | -   | 258 | μs     | Withsystemclockat<br>20MHz                      |  |

| NVDS Byte Pro-<br>gram Time |     |                      |     | 126                                                               | -   | 136 | μs     | Withsystemclockat<br>20MHz                      |  |

| Data Retention              |     |                      |     | 10                                                                | _   | _   | years  | 25°C                                            |  |

| Endurance                   |     |                      |     | 100,000                                                           | -   | -   | cycles | Cumulative write<br>cycles for entire<br>memory |  |

#### Table 121. Nonvolatile Data Storage

**Note:** For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write can take up to 58 ms to complete.

#### Table 122. Analog-to-Digital Converter Electrical Characteristics and Timing

|                  |                                                 |     | = 2.7 to<br>0°C to + |     |     | = 2.7 to<br>40°C to |     |       |                |

|------------------|-------------------------------------------------|-----|----------------------|-----|-----|---------------------|-----|-------|----------------|

| Symbol           | Parameter                                       | Min | Тур                  | Max | Min | Тур                 | Мах | Units | Conditions     |

|                  | Resolution                                      |     |                      |     | _   | 10                  | _   | bits  |                |

|                  | Differential<br>Nonlinearity (DNL) <sup>1</sup> |     |                      |     | -1  | -                   | +4  | LSB   |                |

|                  | Integral<br>Nonlinearity (INL) <sup>1</sup>     |     |                      |     | -5  | _                   | +5  | LSB   |                |

|                  | Gain Error                                      |     |                      |     |     | 15                  |     | LSB   |                |

|                  | Offset Error                                    |     |                      |     | -15 | _                   | 15  | LSB   | PDIP package   |

|                  | -                                               |     |                      |     | -9  | -                   | 9   | LSB   | Other packages |

| V <sub>REF</sub> | On chip reference                               |     |                      |     | 1.9 | 2.0                 | 2.1 | V     |                |

|                  | Active Power<br>Consumption                     |     |                      |     |     | 4                   |     | mA    |                |

|                  | Power Down<br>Current                           |     |                      |     |     |                     | 1   | μA    |                |

Note: <sup>1</sup>When the input voltage is lower than 20mV, the conversion error is out of spec.

193

>

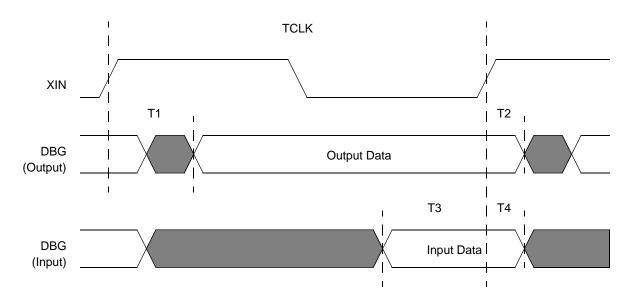

## **On-Chip Debugger Timing**

Figure 35 and Table 126 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

| Figure 35. On-Chip Debugger Timing | Figure 35. | <b>On-Chip</b> | Debugger | Timing |

|------------------------------------|------------|----------------|----------|--------|

|------------------------------------|------------|----------------|----------|--------|

|                |                                  | Delay (ns) |         |  |  |  |

|----------------|----------------------------------|------------|---------|--|--|--|

| Parameter      | Abbreviation                     | Minimum    | Maximum |  |  |  |

| DBG            |                                  |            |         |  |  |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | _          | 15      |  |  |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | _       |  |  |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5          | _       |  |  |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _       |  |  |  |

|              |                                          | Power Consumption |         |  |  |  |

|--------------|------------------------------------------|-------------------|---------|--|--|--|

| Category     | Block                                    | Typical           | Maximum |  |  |  |

| Logic        | CPU/Peripherals @ 20MHz                  | 5mA               |         |  |  |  |

| Flash        | Flash @20MHz                             |                   | 12mA    |  |  |  |

|              | ADC @20MHz                               | 4mA               | 4.5mA   |  |  |  |

|              | IPO                                      | 350µA             | 400µA   |  |  |  |

|              | Comparator @10MHz                        | 330µA             | 450µA   |  |  |  |

| Analog       | POR & VBO                                | 120µA             | 150µA   |  |  |  |

|              | WDT Oscillator                           | 2µA               | ЗµА     |  |  |  |

|              | OSC @ 20MHz                              | 600µA             | 900µA   |  |  |  |

|              | Clock Filter                             | 120µA             | 150µA   |  |  |  |

| Note: The va | lues in this table are subject to change | · · ·             |         |  |  |  |

#### Table 127. Power Consumption Reference Table

Figure 36. Flash Current Diagram

#### Hex Address: FDB

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |       | FDBH  |       |       |       |       |       |       |  |  |

#### Hex Address: FDC

#### Table 181. Port D GPIO Address Register (PDADDR)

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|

| Field   |      | PADDR[7:0]                  |   |   |   |   |   |   |  |

| RESET   | 00H  |                             |   |   |   |   |   |   |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FDCH |                             |   |   |   |   |   |   |  |

#### Hex Address: FDD

#### Table 182. Port D Control Registers (PDCTL)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | PCTL                        |   |   |   |   |   |   |  |  |

| RESET   | 00H |                             |   |   |   |   |   |   |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | FDDH                        |   |   |   |   |   |   |  |  |

#### Hex Address: FDE

This address range is reserved.

#### Hex Address: FDF

| Table 183. | Port D | Output | Data | Register | (PDOUT) |

|------------|--------|--------|------|----------|---------|

|            | IOIUD  | Output | Data | Register |         |

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address | FDFH  |       |       |       |       |       |       |       |  |  |

#### Hex Addresses: FE0–FEF

This address range is reserved.

## Watchdog Timer

For more information about the Watchdog Timer registers, see the <u>Watchdog Timer Con-</u> trol Register Definitions section on page 95.

#### Hex Address: FF0

The Watchdog Timer Control Register address is shared with the read-only Reset Status Register.

| Bit     | 7       | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------|------|---|---|---|---|---|---|--|--|

| Field   | WDTUNLK |      |   |   |   |   |   |   |  |  |

| RESET   | Х       | Х    | Х | Х | Х | Х | Х | Х |  |  |

| R/W     | W       | W    | W | W | W | W | W | W |  |  |

| Address |         | FF0H |   |   |   |   |   |   |  |  |

| Bit     | 7                              | 6    | 5   | 4   | 3        | 2 | 1 | 0 |  |

|---------|--------------------------------|------|-----|-----|----------|---|---|---|--|

| Field   | POR                            | STOP | WDT | EXT | Reserved |   |   |   |  |

| RESET   | See <u>Table 12</u> on page 29 |      |     | 0   | 0        | 0 | 0 | 0 |  |

| R/W     | R                              | R    | R   | R   | R        | R | R | R |  |

| Address | FFOH                           |      |     |     |          |   |   |   |  |

Table 185. Reset Status Register (RSTSTAT)