Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0430sj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| Voltage Brown-Out Reset                           |    |

|---------------------------------------------------|----|

| Watchdog Timer Reset                              |    |

| External Reset Input                              |    |

| External Reset Indicator                          |    |

| On-Chip Debugger Initiated Reset                  |    |

| Stop Mode Recovery                                |    |

| Stop Mode Recovery using WDT Time-Out             |    |

| Stop Mode Recovery using GPIO Port Pin Transition |    |

| Stop Mode Recovery Using the External RESET Pin   |    |

| Debug Pin Driven Low                              |    |

| Reset Register Definitions                        | 28 |

| Low-Power Modes                                   | 30 |

| STOP Mode                                         | 30 |

| HALT Mode                                         | 31 |

| Peripheral Level Power Control                    | 31 |

| Power Control Register Definitions                | 31 |

| General Purpose Input/Output                      | 33 |

| GPIO Port Availability by Device                  |    |

| Architecture                                      |    |

| GPIO Alternate Functions                          |    |

| Direct LED Drive                                  |    |

| Shared Reset Pin                                  | 35 |

| Crystal Oscillator Override                       |    |

| 5V Tolerance                                      |    |

| External Clock Setup                              | 36 |

| GPIO Interrupts                                   | 39 |

| GPIO Control Register Definitions                 | 39 |

| Port A–D Address Registers                        | 40 |

| Port A–D Control Registers                        | 41 |

| Port A–D Data Direction Subregisters              | 41 |

| Port A–D Alternate Function Subregisters          | 42 |

| Port A–C Input Data Registers                     | 49 |

| Port A–D Output Data Register                     | 50 |

| LED Drive Enable Register                         | 51 |

| LED Drive Level High Register                     | 51 |

| LED Drive Level Low Register                      | 52 |

| Interrupt Controller                              | 53 |

| Interrupt Vector Listing                          |    |

| Architecture                                      |    |

| Operation                                         |    |

|                                                   |    |

# **Register Map**

Table 8 provides an address map of the Z8 Encore! F0830 Series register file. Not all devices and package styles in the Z8 Encore! F0830 Series support the ADC or all of the GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)    | Register Description              | Mnemonic      | Reset (Hex) | Page No. |

|------------------|-----------------------------------|---------------|-------------|----------|

| General Purpos   | e RAM                             |               |             |          |

| 000–0FF          | General purpose register file RAM |               | XX          |          |

| 100–EFF          | Reserved                          | _             | XX          |          |

| Timer 0          |                                   |               |             |          |

| F00              | Timer 0 high byte                 | T0H           | 00          | 83       |

| F01              | Timer 0 low byte                  | TOL           | 01          | 83       |

| F02              | Timer 0 reload high byte          | TORH          | FF          | 85       |

| F03              | Timer 0 reload low byte           | TORL          | FF          | 85       |

| F04              | Timer 0 PWM high byte             | <b>T0PWMH</b> | 00          | 86       |

| F05              | Timer 0 PWM low byte              | TOPWML        | 00          | 86       |

| F06              | Timer 0 control 0                 | T0CTL0        | 00          | 87       |

| F07              | Timer 0 control 1                 |               | 00          | 88       |

| Timer 1          |                                   |               |             |          |

| F08              | Timer 1 high byte                 | T1H           | 00          | 83       |

| F09              | Timer 1 low byte                  | T1L           | 01          | 83       |

| F0A              | Timer 1 reload high byte          | T1RH          | FF          | 85       |

| F0B              | Timer 1 reload low byte           | T1RL          | FF          | 85       |

| F0C              | Timer 1 PWM high byte             | T1PWMH        | 00          | 86       |

| F0D              | Timer 1 PWM low byte              | T1PWML        | 00          | 86       |

| F0E              | Timer 1 control 0                 | T1CTL0        | 00          | 87       |

| F0F              | Timer 1 control 1                 | T1CTL1        | 00          | 83       |

| F10–F6F          | Reserved                          | _             | XX          |          |

| Analog-to-Digita | al Converter (ADC)                |               |             |          |

| F70              | ADC control 0                     | ADCCTL0       | 00          | 102      |

| F71              | Reserved                          |               | XX          |          |

| F72              | ADC data high byte                | ADCD_H        | XX          | 103      |

### Table 8. Register File Address Map

Note: XX = Undefined.

|                                                    | Re                                                     | eset Charact | eristics and Latency                               |

|----------------------------------------------------|--------------------------------------------------------|--------------|----------------------------------------------------|

| Reset Type                                         | Control Registers                                      | eZ8 CPU      | Reset Latency (Delay)                              |

| System Reset                                       | Reset (as applicable)                                  | Reset        | About 66 Internal Precision Oscillator<br>Cycles   |

| System Reset with Crystal<br>Oscillator Enabled    | Reset (as applicable)                                  | Reset        | About 5000 Internal Precision Oscillator<br>Cycles |

| Stop Mode Recovery                                 | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset        | About 66 Internal Precision Oscillator cycles      |

| Stop Mode Recovery with crystal oscillator enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset        | About 5000 Internal Precision Oscillator cycles    |

#### Table 9. Reset and Stop Mode Recovery Characteristics and Latency

During a system RESET or Stop Mode Recovery, the Z8 Encore! F0830 Series device is held in reset for about 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, the reset period is increased to about 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, the reset delay is measured from the time that the supply voltage first exceeds the POR level (discussed later in this chapter). If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 which is shared with the reset pin. On reset, the Port D0 pin is configured as a bidirectional open-drain reset. This pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer Oscillator continues to run.

On reset, control registers within the register file that have a defined reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general purpose RAM are undefined following the reset. The eZ8 CPU fetches the reset vector at program memory addresses 0002H and 0003H and loads that value into the program counter. Program execution begins at the reset vector address.

Because the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. User software must reconfigure the oscillator control block, to enable and select the correct system clock source.

```

LDX r0, IRQ0

AND r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

### Software Interrupt Assertion

Program code can generate interrupts directly. Writing 1 to the correct bit in the interrupt request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the interrupt request register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

### **Interrupt Control Register Definitions**

The Interrupt Control registers enable individual interrupts, set interrupt priorities and indicate interrupt requests for all of the interrupts other than the Watchdog Timer interrupt, the primary oscillator fail trap and the Watchdog Oscillator fail trap interrupts.

### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit                  | 7                       | 6             | 5                           | 4            | 3         | 2        | 1    | 0    |

|----------------------|-------------------------|---------------|-----------------------------|--------------|-----------|----------|------|------|

| Field                |                         | Reserved      |                             |              |           | PC2I     | PC1I | PC0I |

| RESET                | 0                       | 0             | 0                           | 0            | 0         | 0        | 0    | 0    |

| R/W                  | R/W                     | R/W           | R/W                         | R/W          | R/W       | R/W      | R/W  | R/W  |

| Address              |                         |               |                             | FC           | 6H        |          |      |      |

| Bit                  | Description             | n             |                             |              |           |          |      |      |

| [7:4]                | Reserved<br>These regis | sters are res | erved and n                 | nust be prog | rammed to | 0000.    |      |      |

| [3]<br>PC <i>x</i> l | 1 = An inter            | rrupt reques  | t is pending<br>t from GPIO | Port C pin 2 |           | service. |      |      |

| Note: x in           | dicates the sp          | ecific GPIO p | ort pin numbe               | ər (3–0).    |           |          |      |      |

#### Table 37. Interrupt Request 2 Register (IRQ2)

### **IRQ0 Enable High and Low Bit Registers**

Table 38 lists the priority control values for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling service for interrupts in the Interrupt Request 0 Register. Priority is generated by setting the bits in each register.

| IRQ0EN  | IH[x]    | IRQ0ENL[x]            | Priority         | Description |

|---------|----------|-----------------------|------------------|-------------|

| C       | )        | 0                     | Disabled         | Disabled    |

| C       | )        | 1                     | Level 1          | Low         |

| 1       |          | 0                     | Level 2          | Nominal     |

| 1       |          | 1                     | Level 3          | High        |

| Note: x | indicate | s the register bits i | n the range 7–0. |             |

Table 38. IRQ0 Enable and Priority Encoding

### Interrupt Edge Select Register

The interrupt edge select (IRQES) register determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin. See Table 47.

|         |          |      | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|----------|------|------|------|------|------|------|------|

| Field   | ES7      | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W F   | R/W      | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | <b>I</b> |      |      | FC   | DH   |      |      |      |

### Table 47. Interrupt Edge Select Register (IRQES)

# Bit Description [7] Interrupt Edge Select x IESx 0 = An interrupt request is generated on the falling edge of the PAx input or PDx. 1 = An interrupt request is generated on the rising edge of the PAx input or PDx. Note: x indicates register bits in the address range 7–0.

Observe the following steps for configuring a timer for PWM DUAL OUTPUT Mode and for initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM deadband delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM High and Low Byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the timer output and timer output complement alternate functions. The timer output complement function is shared with the timer input function for both timers. Setting the timer mode to DUAL PWM will automatically switch the function from timer-in to timer-out complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output high time to the total period is represented by:

# Watchdog Timer

The Watchdog Timer (WDT) protects from corrupted or unreliable software, power faults and other system-level problems which can place the Z8 Encore! F0830 Series devices into unsuitable operating states. The features of the Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The Watchdog Timer is a retriggerable one-shot timer that resets or interrupts the Z8 Encore! F0830 Series devices when the WDT reaches its terminal count. The WDT uses a dedicated on-chip RC oscillator as its clock source. The WDT operates only in two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the WDT to operate immediately on reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is calculated using the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the 24-bit decimal value provided by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10KHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value |            | ate Time-Out Delay<br>I WDT Oscillator Frequency) |

|------------------|------------------|------------|---------------------------------------------------|

| (Hex)            | (Decimal)        | Typical    | Description                                       |

| 000004           | 4                | 400µs      | Minimum time-out delay                            |

| 000400           | 1024             | 102ms      | Default time-out delay                            |

| FFFFF            | 16,777,215       | 28 minutes | Maximum time-out delay                            |

### Table 58. Watchdog Timer Approximate Time-Out Delays

# Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers. Watchdog Timer Control Register (WDTCTL): see page 95

Watchdog Timer Reload Low Byte Register (WDTL): see page 97

Watchdog Timer Reload Upper Byte Register (WDTU): see page 96

Watchdog Timer Reload High Byte Register (WDTH): see page 96

## Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) Register is a write-only control register. Writing the unlock sequence: 55H, AAH to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address have no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the reload registers.

This register address is shared with the read-only Reset Status Register.

| Bit     | 7        | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

|---------|----------|---|---|-----|------|---|---|---|

| Field   |          |   | · | WDT | UNLK | · |   |   |

| RESET   | Х        | Х | Х | Х   | Х    | Х | Х | Х |

| R/W     | W        | W | W | W   | W    | W | W | W |

| Address |          |   |   | FF  | ОH   |   |   |   |

| D:4     | Decering |   |   |     |      |   |   |   |

| Table 59. Watchdog Timer Control Register (WDTCTL) | Table 59 | . Watchdog | <b>Timer Control</b> | Register | (WDTCTL) |

|----------------------------------------------------|----------|------------|----------------------|----------|----------|

|----------------------------------------------------|----------|------------|----------------------|----------|----------|

| Bit     | Description                                                                               |

|---------|-------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Unlock                                                                     |

| WDTUNLK | The user software must write the correct unlocking sequence to this register before it is |

|         | allowed to modify the contents of the Watchdog Timer Reload registers.                    |

# **On-Chip Debugger**

The Z8 Encore! devices contain an integrated On-Chip Debugger (OCD) that provides the following advanced debugging features:

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

# Architecture

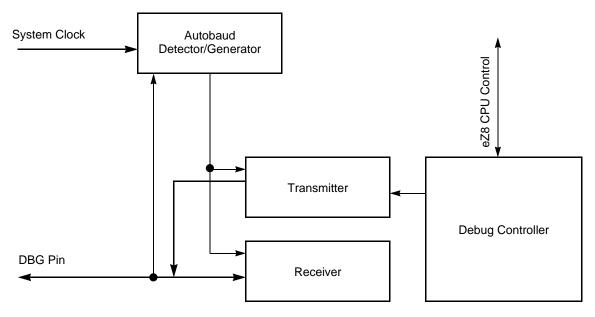

The On-Chip Debugger consists of four primary functional blocks: transmitter, receiver, autobaud detector/generator and debug controller. Figure 20 displays the architecture of the On-Chip Debugger.

Figure 20. On-Chip Debugger Block Diagram

# Operation

The following section describes the operation of the On-Chip Debugging function.

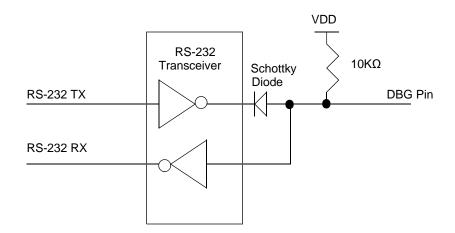

### **OCD** Interface

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, which means that transmission and data retrieval cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface between the Z8 Encore! F0830 Series products and the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figures 21 and 22. The recommended method is the buffered implementation depicted in Figure 22. The DBG pin must always be connected to  $V_{DD}$  through an external pull-up resistor.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

#### Figure 21. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

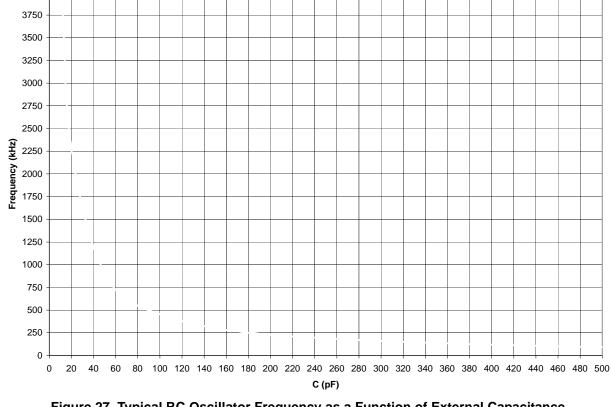

Figure 27. Typical RC Oscillator Frequency as a Function of External Capacitance with a 45 k $\Omega$  Resistor

**Caution:** When using the external RC OSCILLATOR Mode, the oscillator can stop oscillating if the power supply drops below 2.7V but before it drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7V.

160

4000

# eZ8 CPU Instruction Set

This chapter describes the following features of the eZ8 CPU instruction set: <u>Assembly Language Programming Introduction</u>: see page 162 <u>Assembly Language Syntax</u>: see page 163 <u>eZ8 CPU Instruction Notation</u>: see page 164 <u>eZ8 CPU Instruction Classes</u>: see page 166 <u>eZ8 CPU Instruction Summary</u>: see page 171

# **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (op codes and operands) to represent the instructions themselves. The op codes identify the instruction while the operands represent memory locations, registers or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement contains labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, these pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is provided in the following example.

### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called "START". The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working register R4, is the destination. The second operand,<br>; Working register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, extended mode register Address 234H,<br>; identifies the destination. The second operand, immediate data<br>; value 01H, is the source. The value 01H is written into the<br>; register at address 234H. |

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as *destination*, *source*. After assembly, the object code usually reflects the operands in the order *source*, *destination*, but ordering is op code-dependent.

The following examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

### Example 1

If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

| Table 101. Assembly | Language Syntax Example 1 |

|---------------------|---------------------------|

|---------------------|---------------------------|

| Assembly Language Code | ADD | 43H, | 08H | (ADD c | dst, | src) |

|------------------------|-----|------|-----|--------|------|------|

| Object Code            | 04  | 08   | 43  | (OPC s | src, | dst) |

| Assembly      |                                                                          |     | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | Fetch | Instr. |

|---------------|--------------------------------------------------------------------------|-----|-------------|---------------|---|---|-----|-----|---|---|-------|--------|

| Mnemonic      | Symbolic Operation                                                       | dst | src         | (Hex)         | С | Ζ | S   | ۷   | D | Н |       |        |

| POPX dst      | dst $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 1                           | ER  |             | D8            | - | _ | _   | -   | _ | - | 3     | 2      |

| PUSH src      | $SP \leftarrow SP - 1$                                                   | R   |             | 70            | - | - | _   | -   | _ | - | 2     | 2      |

|               | $@SP \leftarrow src$                                                     | IR  |             | 71            | - |   |     |     |   |   | 2     | 3      |

|               | -                                                                        | IM  |             | IF70          | - |   |     |     |   |   | 3     | 2      |

| PUSHX src     | $SP \leftarrow SP - 1$<br>@SP ← src                                      | ER  |             | C8            | _ | - | -   | _   | _ | - | 3     | 2      |

| RCF           | C ← 0                                                                    |     |             | CF            | 0 | - | -   | -   | _ | - | 1     | 2      |

| RET           | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |     |             | AF            | - | - | -   | -   | _ | - | 1     | 4      |

| RL dst        |                                                                          | R   |             | 90            | * | * | *   | *   | _ | _ | 2     | 2      |

|               | C                                                                        | IR  |             | 91            |   |   |     |     |   |   | 2     | 3      |

| RLC dst       |                                                                          | R   |             | 10            | * | * | *   | *   | - | _ | 2     | 2      |

|               | C D7 D6 D5 D4 D3 D2 D1 D0 dst                                            | IR  |             | 11            |   |   |     |     |   |   | 2     | 3      |

| RR dst        |                                                                          | R   |             | E0            | * | * | *   | *   | _ | - | 2     | 2      |

|               | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C                                            | IR  |             | E1            |   |   |     |     |   |   | 2     | 3      |

| RRC dst       |                                                                          | R   |             | C0            | * | * | *   | *   | _ | - | 2     | 2      |

|               | ► D7D6D5D4D3D2D1D0 ► C                                                   | IR  |             | C1            |   |   |     |     |   |   | 2     | 3      |

| SBC dst, src  | $dst \gets dst - src - C$                                                | r   | r           | 32            | * | * | *   | *   | 1 | * | 2     | 3      |

|               |                                                                          | r   | lr          | 33            | _ |   |     |     |   |   | 2     | 4      |

|               |                                                                          | R   | R           | 34            |   |   |     |     |   |   | 3     | 3      |

|               | -                                                                        | R   | IR          | 35            |   |   |     |     |   |   | 3     | 4      |

|               | -                                                                        | R   | IM          | 36            | _ |   |     |     |   |   | 3     | 3      |

|               |                                                                          | IR  | IM          | 37            |   |   |     |     |   |   | 3     | 4      |

| SBCX dst, src | $dst \gets dst - src - C$                                                | ER  | ER          | 38            | * | * | *   | *   | 1 | * | 4     | 3      |

|               | -                                                                        | ER  | IM          | 39            | _ |   |     |     |   |   | 4     | 3      |

| SCF           | C ← 1                                                                    |     |             | DF            | 1 | _ | _   | _   | _ | _ | 1     | 2      |

### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

177

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50pF on all outputs.

|                     |                                            |         | 7 to 3.6V<br>to +70°C | V <sub>DD</sub> = 2.7<br>T <sub>A</sub> = -4<br>+10 | 0°C to |       |                                                                                                              |

|---------------------|--------------------------------------------|---------|-----------------------|-----------------------------------------------------|--------|-------|--------------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                                  | Min Max |                       | Min                                                 | Max    | Units | Conditions                                                                                                   |

| F <sub>SYSCLK</sub> | System Clock Fre-<br>quency                |         |                       | -                                                   | 20.0   | MHz   | Read-only from Flash memory                                                                                  |

|                     |                                            |         |                       | 0.03276<br>8                                        | 20.0   | MHz   | Program or erasure of the Flash memory                                                                       |

| F <sub>XTAL</sub>   | Crystal Oscillator<br>Frequency            |         |                       | 1.0                                                 | 20.0   | MHz   | System clock frequen-<br>cies below the crystal<br>oscillator minimum<br>require an external                 |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |         |                       | 0.03276<br>8                                        | 5.5296 | MHz   | Oscillator is <b>not</b> adjust-<br>able over the entire<br>range. User may select<br>Min or Max value only. |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |         |                       | 5.31                                                | 5.75   | MHz   | High speed with trim-<br>ming                                                                                |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |         |                       | 4.15                                                | 6.91   | MHz   | High speed without trimming                                                                                  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |         |                       | 30.7                                                | 33.3   | KHz   | Low speed with trim-<br>ming                                                                                 |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |         |                       | 24                                                  | 40     | KHz   | Low speed without trimming                                                                                   |

| T <sub>XIN</sub>    | System Clock<br>Period                     |         |                       | 50                                                  | -      | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                     |

| T <sub>XINH</sub>   | System Clock High<br>Time                  |         |                       | 20                                                  | 30     | ns    | T <sub>CLK</sub> = 50 ns                                                                                     |

| T <sub>XINL</sub>   | System Clock Low<br>Time                   |         |                       | 20                                                  | 30     | ns    | T <sub>CLK</sub> = 50 ns                                                                                     |

### **Table 117. AC Characteristics**

# Packaging

Zilog's F0830 Series of MCUs includes the Z8F0130, Z8F0131, Z8F0230, Z8F0231, Z8F1232 and Z8F1233 devices, which are available in the following packages:

- 20-Pin Quad Flat No-Lead Package (QFN)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Plastic Dual-Inline Package (PDIP)

- 20-pin Small Shrink Outline Package (SSOP)

- 28-Pin Quad Flat No-Lead Package (QFN)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Shrink Outline Package (SSOP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

### Hex Address: FC1

| Bit     | 7        | 6     | 5     | 4        | 3        | 2        | 1        | 0      |  |  |

|---------|----------|-------|-------|----------|----------|----------|----------|--------|--|--|

| Field   | Reserved | T1ENH | T0ENH | Reserved | Reserved | Reserved | Reserved | ADCENH |  |  |

| RESET   | 0        | 0     | 0     | 0        | 0        | 0        | 0        | 0      |  |  |

| R/W     | R/W      | R/W   | R/W   | R/W      | R/W      | R/W      | R/W      | R/W    |  |  |

| Address |          | FC1H  |       |          |          |          |          |        |  |  |

### Hex Address: FC2

### Table 159. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5            | 4        | 3        | 2        | 1        | 0      |  |  |  |

|---------|----------|-------|--------------|----------|----------|----------|----------|--------|--|--|--|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | Reserved | Reserved | Reserved | Reserved | ADCENL |  |  |  |

| RESET   | 0        | 0     | 0            | 0        | 0        | 0        | 0        | 0      |  |  |  |

| R/W     | R        | R/W   | R/W          | R/W      | R/W      | R        | R        | R/W    |  |  |  |

| Address |          | FC2H  |              |          |          |          |          |        |  |  |  |

### Hex Address: FC3

### Table 160. Interrupt Request 1 Register (IRQ1)

| Bit     | 7    | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|---------|------|-------|------|------|------|------|------|------|--|--|--|

| Field   | PA7I | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |  |  |

| RESET   | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |

| R/W     | R/W  | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |  |

| Address |      | FC3H  |      |      |      |      |      |      |  |  |  |

### Hex Address: FC4

### Table 161. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |  |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|--|--|--|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |  |  |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |  |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |  |

| Address |        | FC4H    |        |        |               |        |        |        |  |  |  |

# **GPIO Port A**

For more information about the GPIO registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

### Hex Address: FD0

### Table 169. Port A GPIO Address Register (PAADDR)

| Bit     | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|----|----|---|---|---|--|--|

| Field   |     | PADDR[7:0]                  |   |    |    |   |   |   |  |  |

| RESET   |     | 00H                         |   |    |    |   |   |   |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |  |

| Address |     |                             |   | FD | 0H |   |   |   |  |  |

### Hex Address: FD1

### Table 170. Port A Control Registers (PACTL)

| Bit     | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|-----|-----------------------------|---|----|----|---|---|---|--|--|--|

| Field   |     | PCTL                        |   |    |    |   |   |   |  |  |  |

| RESET   |     | 00H                         |   |    |    |   |   |   |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |  |  |

| Address |     |                             |   | FD | 1H |   |   |   |  |  |  |

### Hex Address: FD2

### Table 171. Port A Input Data Registers (PAIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|--|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |  |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |  |  |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |  |  |  |

| Address |      | FD2H |      |      |      |      |      |      |  |  |  |