# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0431hh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

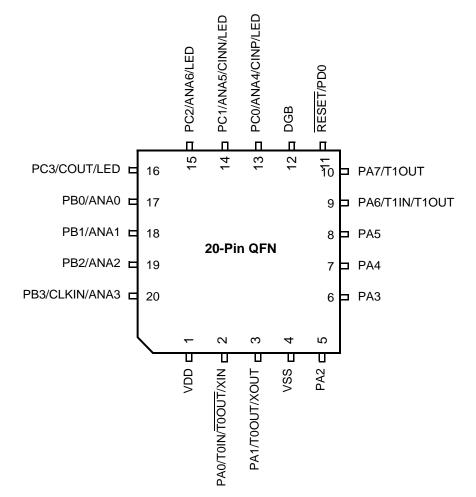

Figure 4. Z8F0830 Series in 20-Pin QFN Package

9

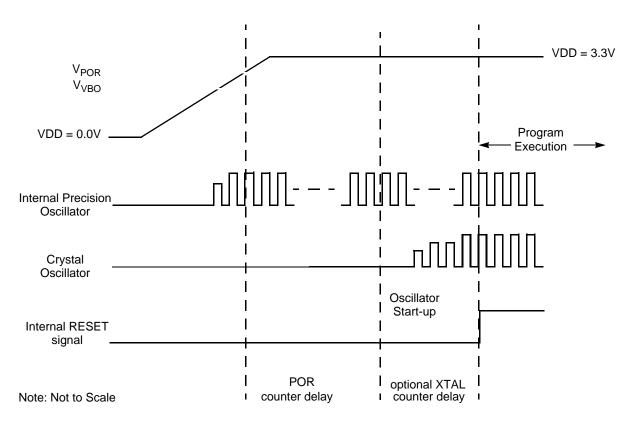

Figure 6. Power-On Reset Operation

## **Voltage Brown-Out Reset**

The devices in the Z8 Encore! F0830 Series provide low Voltage Brown-Out (VBO) protection. The VBO circuit forces the device to the Reset state, when the supply voltage drops below the VBO threshold voltage (unsafe level). While the supply voltage remains below the Power-On Reset threshold voltage ( $V_{POR}$ ), the VBO circuit holds the device in reset.

After the supply voltage exceeds the Power-On Reset threshold voltage, the device progresses through a full system reset sequence, as described in the POR section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 7 displays the Voltage Brown-Out operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

#### 31

# HALT Mode

Executing the eZ8 CPU HALT instruction places the device into HALT Mode. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any one of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as digital inputs must be driven to  $V_{DD}$  when pull-up register bit is enabled or to one of power rail ( $V_{DD}$  or GND) when pull-up register bit is disabled.

# **Peripheral Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! F0830 Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

#### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

# Architecture

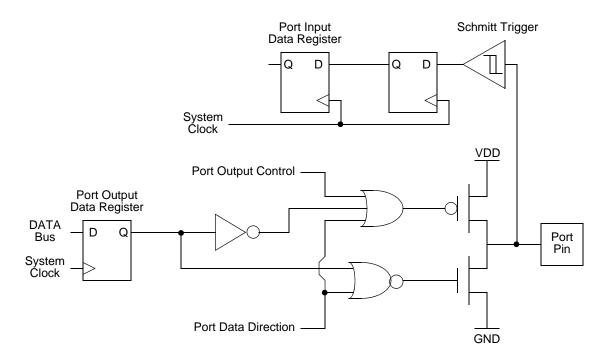

Figure 8 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

# **GPIO Alternate Functions**

Many of the GPIO port pins can be used for general purpose input/output and access to onchip peripheral functions such as the timers and serial communication devices. The Port A–D Alternate Function subregisters configure these pins for either GPIO or Alternate function operation. When a pin is configured for Alternate function, control of the port pin direction (input/output) is passed from the Port A–D data direction registers to the Alternate function assigned to this pin. <u>Table 16</u> on page 36 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function subregisters AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, pins PA0 and PA1 functions as input and output for the crystal oscillator.

| Port                | Pin | Mnemonic  | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-----------|--------------------------------|-----------------------------------------|

| Port C <sup>3</sup> | PC0 | Reserved  |                                | AFS1[0]: 0                              |

|                     |     | ANA4/CINP | ADC or comparator input        | AFS1[0]: 1                              |

|                     | PC1 | Reserved  |                                | AFS1[1]: 0                              |

|                     |     | ANA5/CINN | ADC or comparator input        | AFS1[1]: 1                              |

|                     | PC2 | Reserved  |                                | AFS1[2]: 0                              |

|                     |     | ANA6      | ADC analog input               | AFS1[2]: 1                              |

|                     | PC3 | COUT      | Comparator output              | AFS1[3]: 0                              |

|                     |     | Reserved  |                                | AFS1[3]: 1                              |

|                     | PC4 | Reserved  |                                | AFS1[4]: 0                              |

|                     |     |           |                                | AFS1[4]: 1                              |

|                     | PC5 | Reserved  |                                | AFS1[5]: 0                              |

|                     |     |           |                                | AFS1[5]: 1                              |

|                     | PC6 | Reserved  |                                | AFS1[6]: 0                              |

|                     |     |           |                                | AFS1[6]: 1                              |

|                     | PC7 | Reserved  |                                | AFS1[7]: 0                              |

|                     |     |           |                                | AFS1[7]: 1                              |

| Port D <sup>1</sup> | PD0 | RESET     | Default to be Reset function   | N/A                                     |

#### Table 16. Port Alternate Function Mapping (Continued)

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

## Port A–D Alternate Function Subregisters

The Port A–D Alternate Function Subregister is accessed through the Port A–D Control Register by writing 02H to the Port A–D Address Register. See Table 22 on page 42. The Port A–D Alternate Function subregisters enable the alternate function selection on pins. If disabled, the pins function as GPIOs. If enabled, select one of four alternate functions using Alternate Function Set subregisters 1 and 2, as described in the the <u>Port A–D Alternate Function</u> <u>Set 1 Subregisters</u> section on page 47 and the <u>Port A–D Alternate Function</u> <u>Set 2 Subregisters</u> section on page 48. See the <u>GPIO Alternate Functions</u> section on page 34 to determine the alternate functions associated with each port pin.

**Caution:** Do not enable alternate functions for GPIO port pins for which there is no associated Alternate function. Failure to follow this guideline can result in unpredictable operation.

| Bit     | 7           | 6                                                                                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-------------|---------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|--|

| Field   | AF7         | AF7 AF6 AF5 AF4 AF3 AF2 AF1 AF0                                                             |   |   |   |   |   |   |  |  |  |

| RESET   |             | 00H (Ports A–C); 01H (Port D)                                                               |   |   |   |   |   |   |  |  |  |

| R/W     |             | R/W                                                                                         |   |   |   |   |   |   |  |  |  |

| Address | If 02H in F | If 02H in Port A–D Address Register, then accessible through the Port A–D Control Register  |   |   |   |   |   |   |  |  |  |

| Bit     | Description |                                                                                             |   |   |   |   |   |   |  |  |  |

| [7:0]   | Port Altern | Port Alternate Function Enable                                                              |   |   |   |   |   |   |  |  |  |

| AFx     | •           | ) = The port pin is in NORMAL Mode and the DDx bit in the Port A–D Data Direction Subregis- |   |   |   |   |   |   |  |  |  |

Table 22. Port A–D Alternate Function Subregisters (PxAF)

ter determines the direction of the pin. 1 = The alternate function selected through Alternate function set subregisters is enabled. Port

= The alternate function selected through Alternate function set subregisters is enabled. Port pin operation is controlled by the Alternate function.

Note: x indicates the specific GPIO port pin number (7-0).

# **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 42 and 43, form a priority-encoded enabling service for interrupts in the Interrupt Request 1 Register. Priority is generated by setting the bits in each register.

| ty Description |

|----------------|

| ed Disabled    |

| 1 Low          |

| 2 Nominal      |

| 3 High         |

| 2              |

Table 41. IRQ1 Enable and Priority Encoding

#### Table 42. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address |        | FC4H    |        |        |               |        |        |        |

| Bit             | Description                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------------|

| [7]<br>PA7ENH   | Port A Bit[7] Interrupt Request Enable High Bit                                                          |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit                                            |

| [5:0]           | Port A Bit[x] Interrupt Request Enable High Bit                                                          |

| PA <i>x</i> ENH | See the interrupt port select register for selection of either Port A or Port D as the interrupt source. |

#### 73

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer reload in COMPARATOR COUNTER Mode, counting always begins at the reset value 0001H. Generally, in COMPARATOR COUNTER Mode, the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions is calculated with the following equation:

Comparator Output Transitions = Current Count Value – Start Value

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

## Watchdog Timer Refresh

Upon first enable, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the Reload operation.

When the Z8 Encore! F0830 Series devices are operating in DEBUG Mode (using the On-Chip Debugger), the Watchdog Timer must be continuously refreshed to prevent any WDT time-outs.

## Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash option bit determines the time-out response of the Watchdog Timer. See *the* <u>Flash Option</u> <u>Bits</u> chapter on page 124 for information about programming the WDT\_RES Flash option bit.

#### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the Interrupt Controller and sets the WDT status bit in the Reset Status Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter resets to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter will not automatically return to its reload value.

The Reset Status Register (see <u>Table 12</u> on page 29) must be read before clearing the WDT interrupt. This read clears the WDT time-out flag and prevents further WDT interrupts occurring immediately.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! F0830 Series devices are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. See *the* <u>Reset and Stop Mode Recovery</u> *chapter on page 21* for more information about Stop Mode Recovery operations.

If interrupts are enabled, following completion of the Stop Mode Recovery, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executes the code from the vector address.

## Sample Time Register

The Sample Time Register, shown in Table 67, is used to program the length of active time for a sample after a conversion has begun by setting the START bit in the ADC Control Register. The number of system clock cycles required for the sample time varies from system to system, depending on the clock period used. The system designer should program this register to contain the number of system clocks required to meet a  $1 \mu s$  minimum sample time.

| Bit     | 7    | 6     | 5 4 3 2 1 0 |             |  |  |  |  |

|---------|------|-------|-------------|-------------|--|--|--|--|

| Field   | Rese | erved | ST          |             |  |  |  |  |

| RESET   | (    | )     | 1           | 1 1 1 1 1 1 |  |  |  |  |

| R/W     | R/   | W     | R/W         |             |  |  |  |  |

| Address |      |       | F75H        |             |  |  |  |  |

| Table 67 | Sample Time | e (ADCST) |

|----------|-------------|-----------|

|----------|-------------|-----------|

| Bit         | Description                                                                           |

|-------------|---------------------------------------------------------------------------------------|

| [7:6]       | Reserved<br>These bits are reserved and must be programmed to 00.                     |

| [5:0]<br>ST | 0h–Fh = Sample-hold time in number of system clock periods to meet 1 $\mu$ s minimum. |

# **Flash Status Register**

The Flash Status Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its register file address with the write-only Flash Control Register.

| Bit     | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|---------|------|-------|-------|---|---|---|---|---|

| Field   | Rese | erved | FSTAT |   |   |   |   |   |

| RESET   | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W     | R    | R     | R     | R | R | R | R | R |

| Address |      | FF8H  |       |   |   |   |   |   |

|         |      |       |       |   |   |   |   |   |

#### Table 73. Flash Status Register (FSTAT)

| Bit   | Description                                            |

|-------|--------------------------------------------------------|

| [7:6] | Reserved                                               |

|       | These bits are reserved and must be programmed to 00.  |

| [5:0] | Flash Controller Status                                |

| FSTAT | 000000 = Flash Controller locked.                      |

|       | 000001 = First unlock command received (73H written).  |

|       | 000010 = Second unlock command received (8CH written). |

|       | 000011 = Flash Controller unlocked.                    |

|       | 000100 = Sector protect register selected.             |

|       | 001xxx = Program operation in progress.                |

|       | 010xxx = Page Erase operation in progress.             |

|       | 100xxx = Mass Erase operation in progress.             |

# **Power Failure Protection**

NVDS routines employ error-checking mechanisms to ensure that any power failure will only endanger the most recently written byte. Bytes previously written to the array are not perturbed. For this protection to function, the VBO must be enabled (see the <u>Low-Power</u> <u>Modes</u> chapter on page 30) and configured for a threshold voltage of 2.4V or greater (see *the* <u>Trim Bit Address Space</u> *section on page 129*).

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

# **Optimizing NVDS Memory Usage for Execution Speed**

As indicated in Table 93, the NVDS read time varies drastically; this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N as well as the number of writes since the most recent page erase. Neglecting the effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb to consider is that every write since the most recent page erase causes read times of unwritten addresses to increase by  $0.8\mu s$  up to a maximum of  $258\mu s$ .

| Operation     | Minimum<br>Latency (μs) | Maximum<br>Latency (µs) |

|---------------|-------------------------|-------------------------|

| Read          | 71                      | 258                     |

| Write         | 126                     | 136                     |

| Illegal Read  | 6                       | 6                       |

| Illegal Write | 7                       | 7                       |

| Table | 93. | NVDS | Read | Time |

|-------|-----|------|------|------|

|       |     |      |      |      |

• **Note:** For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write takes up to 58 ms to complete.

If NVDS read performance is critical to your software architecture, you can optimize your code for speed by using either of the two methods listed below.

1. Periodically refresh all addresses that are used; this is the more useful method. The optimal use of NVDS, in terms of speed, is to rotate the writes evenly among all addresses planned for use, thereby bringing all reads closer to the minimum read time.

# Operation

The following section describes the operation of the On-Chip Debugging function.

# **OCD** Interface

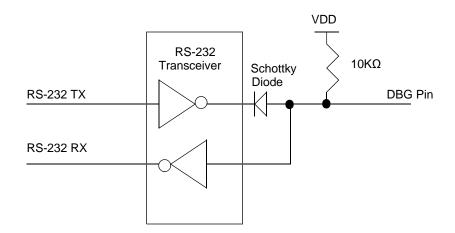

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, which means that transmission and data retrieval cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface between the Z8 Encore! F0830 Series products and the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figures 21 and 22. The recommended method is the buffered implementation depicted in Figure 22. The DBG pin must always be connected to  $V_{DD}$  through an external pull-up resistor.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

#### Figure 21. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

# **Runtime Counter**

The OCD contains a 16-bit runtime counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash read protect option bit (FRP). The FRP prevents the code in memory from being read out of the Z8 Encore! F0830 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 95 summarizes the On-Chip Debugger commands. This table indicates the commands that operate when the device is not in DEBUG Mode (normal operation) and the commands that are disabled by programming the FRP.

| Debug Command              | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                                     |

|----------------------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                | -                                                                                                                                                                                |

| Reserved                   | 01H             | _                                  | _                                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                                | _                                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                                  | -                                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                                | Cannot clear DBGMODE bit                                                                                                                                                         |

| Read OCD Control Register  | 05H             | Yes                                | _                                                                                                                                                                                |

| Write Program Counter      | 06H             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Counter       | 07H             | _                                  | Disabled                                                                                                                                                                         |

| Write Register             | 08H             | _                                  | Only writes of the Flash Memory Con-<br>trol registers are allowed. Additionally,<br>only the Mass Erase command is<br>allowed to be written to the Flash Con-<br>trol register. |

| Read Register              | 09H             | _                                  | Disabled                                                                                                                                                                         |

| Write Program Memory       | 0AH             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Memory        | 0BH             | _                                  | Disabled                                                                                                                                                                         |

| Write Data Memory          | 0CH             | _                                  | Yes                                                                                                                                                                              |

| Read Data Memory           | 0DH             | _                                  | _                                                                                                                                                                                |

#### Table 95. On-Chip Debugger Command Summary

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer Oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The Internal Precision Oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## **Clock Failure Detection and Recovery**

#### **Primary Oscillator Failure**

The Z8F04xA family devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer Oscillator to drive the system clock. The Watchdog Timer Oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer reset function outlined in the Watchdog Timer chapter of this document.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 KHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL Register).

#### Watchdog Timer Failure

In the event of failure of a Watchdog Timer Oscillator, a similar nonmaskable interruptlike event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer Oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer Oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure is detected. A very slow system clock results in very slow detection times.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# **Internal Precision Oscillator**

The Internal Precision Oscillator (IPO) is designed for use without external components. The user can either manually trim the oscillator for a nonstandard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency with  $\pm 4\%$  accuracy and 45%~55% duty cycle over the operating temperature and supply voltage of the device. The maximum start-up time of the IPO is 25µs. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8kHz (contains both a FAST and a SLOW mode)

- Trimming possible through Flash option bits, with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

# Operation

The internal oscillator is an RC relaxation oscillator with a minimized sensitivity to power supply variations. By using ratio-tracking thresholds, the effect of power supply voltage is cancelled out. The dominant source of oscillator error is the absolute variance of chip-level fabricated components, such as capacitors. An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed, the oscillator frequency is stable and does not require subsequent calibration. Trimming was performed during manufacturing and is not necessary for the user to repeat unless a frequency other than 5.53 MHz (FAST mode) or 32.8 kHz (SLOW mode) is required.

**Note:** The user can power down the IPO block for minimum system power.

By default, the oscillator is configured through the Flash option bits. However, the user code can override these trim values, as described in *the* <u>Trim Bit Address Space</u> section on page 129.

Select one of two frequencies for the oscillator: 5.53 MHz or 32.8 kHz, using the OSCSEL bits described in the <u>Oscillator Control</u> chapter on page 151.

#### Hex Address: F74

#### Table 149. ADC Sample Settling Time (ADCSST)

| Bit     | 7 | 6    | 5     | 4 | 3   | 2  | 1 | 0 |  |

|---------|---|------|-------|---|-----|----|---|---|--|

| Field   |   | Rese | erved |   | SST |    |   |   |  |

| RESET   | 0 |      |       |   | 1   | 1  | 1 | 1 |  |

| R/W     |   | F    | २     |   |     | R/ | W |   |  |

| Address |   | F74H |       |   |     |    |   |   |  |

| Bit          | Description                                                                            |

|--------------|----------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.             |

| [3:0]<br>SST | Sample Settling Time<br>0h–Fh = Number of system clock periods to meet 0.5 μs minimum. |

### Hex Address: F75

### Table 150. ADC Sample Time (ADCST)

| Bit     | 7    | 6     | 5    | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-------|------|---|---|---|---|---|--|

| Field   | Rese | erved | ST   |   |   |   |   |   |  |

| RESET   | 0    |       | 1    | 1 | 1 | 1 | 1 | 1 |  |

| R/W     | R/   | W     | R/W  |   |   |   |   |   |  |

| Address |      |       | F75H |   |   |   |   |   |  |

| Bit         | Description                                                                      |

|-------------|----------------------------------------------------------------------------------|

| [7:6]       | <b>Reserved</b><br>This register is reserved and must be programmed to 0.        |

| [5:0]<br>ST | Sample/Hold Time<br>0h–Fh = Number of system clock periods to meet 1 µs minimum. |

### Hex Addresses: F77–F7F

This address range is reserved.

#### Hex Addresses: F87–F8F

This address range is reserved.

# Comparator 0

For more information about the Comparator Register, see the <u>Comparator Control Register Definitions</u> section on page 107.

#### Hex Address: F90

| Bit     | 7        | 6      | 5   | 4        | 3   | 2   | 1   | 0   |

|---------|----------|--------|-----|----------|-----|-----|-----|-----|

| Field   | Reserved | INNSEL |     | REFLVL F |     |     |     |     |

| RESET   | 0        | 0      | 0   | 1        | 0   | 1   | 0   | 0   |

| R/W     | R/W      | R/W    | R/W | R/W      | R/W | R/W | R/W | R/W |

| Address | F90H     |        |     |          |     |     |     |     |

#### Table 156. Comparator Control Register (CMP0)

#### Hex Addresses: F91–FBF

This address range is reserved.

# **Interrupt Controller**

For more information about the Interrupt Control registers, see the <u>Interrupt Control Reg-</u> <u>ister Definitions</u> section on page 57.

#### Hex Address: FC0

| Bit     | 7        | 6   | 5   | 4        | 3        | 2        | 1        | 0    |

|---------|----------|-----|-----|----------|----------|----------|----------|------|

| Field   | Reserved | T1I | TOI | Reserved | Reserved | Reserved | Reserved | ADCI |

| RESET   | 0        | 0   | 0   | 0        | 0        | 0        | 0        | 0    |

| R/W     | R/W      | R/W | R/W | R/W      | R/W      | R/W      | R/W      | R/W  |

| Address | FCOH     |     |     |          |          |          |          |      |

#### Table 157. Interrupt Request 0 Register (IRQ0)

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

load external data to/from data memory and autoincrement addresses 167 load external to/from data memory and auto-increment addresses 168 load instructions 168 load using extended addressing 168 logical AND 169 logical AND/extended addressing 169 logical exclusive OR 169 logical exclusive OR/extended addressing 169 logical OR 169 logical OR 169 logical OR/extended addressing 169

## Μ

master interrupt enable 55 memory data 16 program 15 mode capture 89, 90 capture/compare 89 continuous 89 counter 89 gated 89 one-shot 89 PWM 89.90 modes 89 motor control measurements ADC Control register definitions 101 calibration and compensation 101 interrupts 101 overview 98 **MULT 167** multiply 167

# Ν

noise, electrical 98 NOP (no operation) 168 notation b 164

DA 164 ER 164 IM 164 IR 164 Ir 164 IRR 164 Irr 164 p 164 R 165 r 164 RA 165 RR 165 rr 165 vector 165 X 165 notational shorthand 164

cc 164

# 0

OCD architecture 139 auto-baud detector/generator 142 baud rate limits 142 block diagram 139 breakpoints 143 commands 144 control register 148 data format 142 DBG pin to RS-232 Interface 140 debug mode 141 debugger break 169 interface 140 serial errors 143 status register 150 timing 197 OCD commands execute instruction (12H) 148 read data memory (0DH) 147 read OCD control register (05H) 146 read OCD revision (00H) 145 read OCD status register (02H) 145 read program counter (07H) 146 read program memory (0BH) 147