Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | -                                                         |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 25                                                        |  |

| Program Memory Size        | 4KB (4K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                            |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0431hj020eg |  |

| Voltage Brown-Out Reset                           | . 24 |

|---------------------------------------------------|------|

| Watchdog Timer Reset                              | 25   |

| External Reset Input                              | . 25 |

| External Reset Indicator                          | . 26 |

| On-Chip Debugger Initiated Reset                  | . 26 |

| Stop Mode Recovery                                | . 26 |

| Stop Mode Recovery using WDT Time-Out             | . 27 |

| Stop Mode Recovery using GPIO Port Pin Transition | . 27 |

| Stop Mode Recovery Using the External RESET Pin   | . 28 |

| Debug Pin Driven Low                              | . 28 |

| Reset Register Definitions                        | . 28 |

| Low-Power Modes                                   | 30   |

| STOP Mode                                         |      |

| HALT Mode                                         |      |

| Peripheral Level Power Control                    |      |

|                                                   |      |

| Power Control Register Definitions                |      |

| General Purpose Input/Output                      | . 33 |

| GPIO Port Availability by Device                  | . 33 |

| Architecture                                      | . 34 |

| GPIO Alternate Functions                          | . 34 |

| Direct LED Drive                                  | . 35 |

| Shared Reset Pin                                  | . 35 |

| Crystal Oscillator Override                       | . 35 |

| 5 V Tolerance                                     | . 35 |

| External Clock Setup                              | . 36 |

| GPIO Interrupts                                   | . 39 |

| GPIO Control Register Definitions                 | . 39 |

| Port A–D Address Registers                        | 40   |

| Port A–D Control Registers                        | . 41 |

| Port A–D Data Direction Subregisters              | 41   |

| Port A–D Alternate Function Subregisters          | . 42 |

| Port A–C Input Data Registers                     | . 49 |

| Port A–D Output Data Register                     |      |

| LED Drive Enable Register                         |      |

| LED Drive Level High Register                     |      |

| LED Drive Level Low Register                      |      |

|                                                   |      |

| Interrupt Controller                              |      |

| Interrupt Vector Listing                          |      |

| Architecture                                      |      |

| Operation                                         | . 55 |

PS025113-1212 Table of Contents

# List of Figures

| Figure 1.  | Z8 Encore! F0830 Series Block Diagram                                        | 3    |

|------------|------------------------------------------------------------------------------|------|

| Figure 2.  | Z8F0830 Series in 20-Pin SOIC, SSOP, PDIP Package                            | 8    |

| Figure 3.  | Z8F0830 Series in 28-Pin SOIC, SSOP, PDIP Package                            | 8    |

| Figure 4.  | Z8F0830 Series in 20-Pin QFN Package                                         | 9    |

| Figure 5.  | Z8F0830 Series in 28-Pin QFN Package                                         | . 10 |

| Figure 6.  | Power-On Reset Operation                                                     | . 24 |

| Figure 7.  | Voltage Brown-Out Reset Operation                                            | . 25 |

| Figure 8.  | GPIO Port Pin Block Diagram                                                  | . 34 |

| Figure 9.  | Interrupt Controller Block Diagram                                           | . 55 |

| Figure 10. | Timer Block Diagram                                                          | . 69 |

| Figure 11. | Analog-to-Digital Converter Block Diagram                                    | . 99 |

| Figure 12. | ADC Timing Diagram                                                           | 100  |

| Figure 13. | ADC Convert Timing                                                           | 100  |

| Figure 14. | 1K Flash with NVDS                                                           | 108  |

| Figure 15. | 2K Flash with NVDS                                                           | 109  |

| Figure 16. | 4K Flash with NVDS                                                           | 109  |

| Figure 17. | 8K Flash with NVDS                                                           | 110  |

| Figure 18. | 12K Flash without NVDS                                                       | 111  |

| Figure 19. | Flash Controller Operation Flow Chart                                        | 113  |

| Figure 20. | On-Chip Debugger Block Diagram                                               | 139  |

| Figure 21. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2 | 140  |

| Figure 22. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2 | 141  |

| Figure 23. | OCD Data Format                                                              | 142  |

| Figure 24. | Oscillator Control Clock Switching Flow Chart                                | 156  |

| Figure 25. | Recommended 20MHz Crystal Oscillator Configuration                           | 158  |

| Figure 26  | Connecting the On-Chin Oscillator to an External RC Network                  | 150  |

PS025113-1212 List of Figures

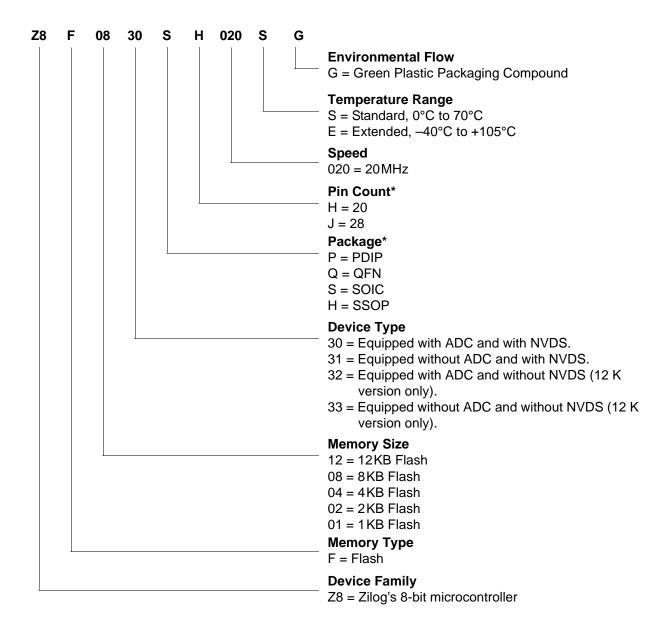

#### Z8 Encore!® F0830 Series Product Specification

xviii

| Table 179. | Port C Input Data Registers (PCIN)               | 224 |

|------------|--------------------------------------------------|-----|

| Table 180. | Port C Output Data Register (PCOUT)              | 225 |

| Table 181. | Port D GPIO Address Register (PDADDR)            | 225 |

| Table 182. | Port D Control Registers (PDCTL)                 | 225 |

| Table 183. | Port D Output Data Register (PDOUT)              | 226 |

| Table 184. | Watchdog Timer Control Register (WDTCTL)         | 226 |

| Table 185. | Reset Status Register (RSTSTAT)                  | 226 |

| Table 186. | Watchdog Timer Reload Upper Byte Register (WDTU) | 227 |

| Table 187. | Watchdog Timer Reload High Byte Register (WDTH)  | 227 |

| Table 188. | Watchdog Timer Reload Low Byte Register (WDTL)   | 227 |

| Table 189. | Trim Bit Address Register (TRMADR)               | 228 |

| Table 190. | Trim Bit Data Register (TRMDR)                   | 228 |

| Table 191. | Flash Control Register (FCTL)                    | 228 |

| Table 192. | Flash Status Register (FSTAT)                    | 229 |

| Table 193. | Flash Page Select Register (FPS)                 | 229 |

| Table 194. | Flash Sector Protect Register (FPROT)            | 229 |

| Table 195. | Flash Frequency High Byte Register (FFREQH)      | 229 |

| Table 196  | Flash Frequency Low Ryte Register (FFRFOL)       | 230 |

PS025113-1212 List of Tables

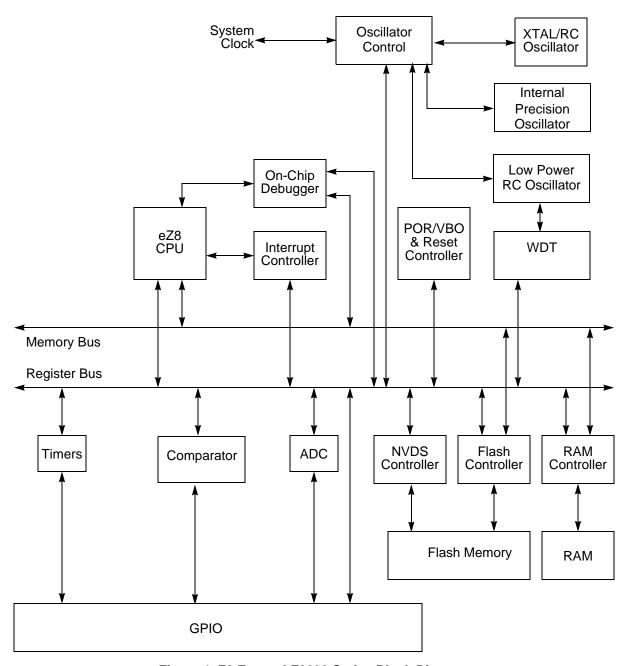

### **Block Diagram**

Figure 1 displays a block diagram of the Z8 Encore! F0830 Series architecture.

Figure 1. Z8 Encore! F0830 Series Block Diagram

PS025113-1212 Block Diagram

Table 9. Reset and Stop Mode Recovery Characteristics and Latency

|                                                    | Reset Characteristics and Latency                      |         |                                                 |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------|---------|-------------------------------------------------|--|--|--|--|

| Reset Type                                         | Control Registers                                      | eZ8 CPU | Reset Latency (Delay)                           |  |  |  |  |

| System Reset                                       | Reset (as applicable)                                  | Reset   | About 66 Internal Precision Oscillator Cycles   |  |  |  |  |

| System Reset with Crystal Oscillator Enabled       | Reset (as applicable)                                  | Reset   | About 5000 Internal Precision Oscillator Cycles |  |  |  |  |

| Stop Mode Recovery                                 | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset   | About 66 Internal Precision Oscillator cycles   |  |  |  |  |

| Stop Mode Recovery with crystal oscillator enabled | Unaffected, except WDT_CTL and OSC_CTL registers       | Reset   | About 5000 Internal Precision Oscillator cycles |  |  |  |  |

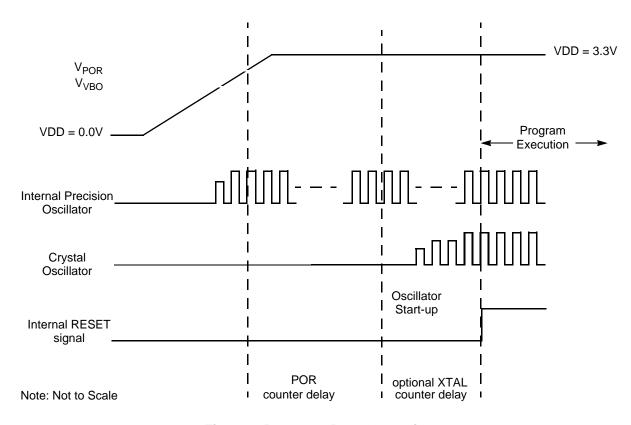

During a system RESET or Stop Mode Recovery, the Z8 Encore! F0830 Series device is held in reset for about 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, the reset period is increased to about 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, the reset delay is measured from the time that the supply voltage first exceeds the POR level (discussed later in this chapter). If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 which is shared with the reset pin. On reset, the Port D0 pin is configured as a bidirectional open-drain reset. This pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer Oscillator continues to run.

On reset, control registers within the register file that have a defined reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general purpose RAM are undefined following the reset. The eZ8 CPU fetches the reset vector at program memory addresses 0002H and 0003H and loads that value into the program counter. Program execution begins at the reset vector address.

Because the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. User software must reconfigure the oscillator control block, to enable and select the correct system clock source.

PS025113-1212 Reset Types

Figure 6. Power-On Reset Operation

#### **Voltage Brown-Out Reset**

The devices in the Z8 Encore! F0830 Series provide low Voltage Brown-Out (VBO) protection. The VBO circuit forces the device to the Reset state, when the supply voltage drops below the VBO threshold voltage (unsafe level). While the supply voltage remains below the Power-On Reset threshold voltage ( $V_{POR}$ ), the VBO circuit holds the device in reset.

After the supply voltage exceeds the Power-On Reset threshold voltage, the device progresses through a full system reset sequence, as described in the POR section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 7 displays the Voltage Brown-Out operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

PS025113-1212 Reset Sources

## Interrupt Controller

The Interrupt Controller on the Z8 Encore!<sup>®</sup> F0830 Series products prioritize the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the Interrupt Controller include:

- Seventeen interrupt sources using sixteen unique interrupt vectors:

- Twelve GPIO port pin interrupt sources

- Five on-chip peripheral interrupt sources (Comparator Output interrupt shares one interrupt vector with PA6)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt m

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the Interrupt Controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the eZ8 CPU User Manual (UM0128), which is available for download at <a href="https://www.zilog.com">www.zilog.com</a>.

#### Interrupt Vector Listing

Table 34 lists the interrupts available in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even program memory address and the least significant byte (LSB) at the odd program memory address.

Note:

Some port interrupts are not available on the 20-pin and 28-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

PS025113-1212 Interrupt Controller

#### **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 42 and 43, form a priority-encoded enabling service for interrupts in the Interrupt Request 1 Register. Priority is generated by setting the bits in each register.

Table 41. IRQ1 Enable and Priority Encoding

| IRQ1ENH[x]                                                       | IRQ1ENL[x] | Priority | Description |  |  |  |  |  |

|------------------------------------------------------------------|------------|----------|-------------|--|--|--|--|--|

| 0                                                                | 0          | Disabled | Disabled    |  |  |  |  |  |

| 0                                                                | 1          | Level 1  | Low         |  |  |  |  |  |

| 1 0 Level 2 Nominal                                              |            |          |             |  |  |  |  |  |

| 1 1 Level 3 High                                                 |            |          |             |  |  |  |  |  |

| Note: <i>x</i> indicates register bits in the address range 7–0. |            |          |             |  |  |  |  |  |

Table 42. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| Field   | PA7ENH | PA6CENH | PA5ENH | PA4ENH | PA3ENH | PA2ENH | PA1ENH | PA0ENH |

| RESET   | 0      | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | FC4H   |         |        |        |        |        |        |        |

| Bit                      | Description                                                                                                                                              |  |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| [7]<br>PA7ENH            | Port A Bit[7] Interrupt Request Enable High Bit                                                                                                          |  |  |  |  |

| [6]<br>PA6CENH           | Port A Bit[7] or Comparator Interrupt Request Enable High Bit                                                                                            |  |  |  |  |

| [5:0]<br>PA <i>x</i> ENH | Port A Bit[x] Interrupt Request Enable High Bit See the interrupt port select register for selection of either Port A or Port D as the interrupt source. |  |  |  |  |

Table 43. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| Field   | PA7ENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0      | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | FC5H   |         |        |        |        |        |        |        |

| Bit                      | Description                                                                                                                                             |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7ENL            | Port A Bit[7] Interrupt Request Enable Low Bit                                                                                                          |

| [6]<br>PA6CENL           | Port A Bit[7] or Comparator Interrupt Request Enable Low Bit                                                                                            |

| [5:0]<br>PA <i>x</i> ENL | Port A Bit[x] Interrupt Request Enable Low Bit See the interrupt port select register for selection of either Port A or Port D as the interrupt source. |

| Note: x indi             | cates register bits in the address range 5–0.                                                                                                           |

x indicates register bits in the address range 5–0.

#### **IRQ2 Enable High and Low Bit Registers**

Table 44 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 45 and 46, form a priority-encoded enabling service for interrupts in the Interrupt Request 2 Register. Priority is generated by setting the bits in each register.

Table 44. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x]                                                | Q2ENH[x] IRQ2ENL[x] |          | Description |  |  |  |  |

|-----------------------------------------------------------|---------------------|----------|-------------|--|--|--|--|

| 0                                                         | 0                   | Disabled | Disabled    |  |  |  |  |

| 0                                                         | 1                   | Level 1  | Low         |  |  |  |  |

| 1                                                         | 0                   | Level 2  | Nominal     |  |  |  |  |

| 1                                                         | 1                   | Level 3  | High        |  |  |  |  |

| Note: x indicates register bits in the address range 7–0. |                     |          |             |  |  |  |  |

Observe the following steps for configuring a timer for PWM DUAL OUTPUT Mode and for initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This write only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM deadband delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM High and Low Byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the timer output and timer output complement alternate functions. The timer output complement function is shared with the timer input function for both timers. Setting the timer mode to DUAL PWM will automatically switch the function from timer-in to timer-out complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$$PWM \ Period \ (s) \ = \ \frac{Reload \ Value \times Prescale}{System \ Clock \ Frequency \ (Hz)}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output high time to the total period is represented by:

PS025113-1212 Operation

#### Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 54 and 55, control PWM operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | PWMH       |     |     |     |     |     |     |     |  |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F04H, F0CH |     |     |     |     |     |     |     |  |

Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7   | 6    | 5   | 4     | 3    | 2   | 1   | 0   |  |  |

|---------|-----|------|-----|-------|------|-----|-----|-----|--|--|

| Field   |     | PWML |     |       |      |     |     |     |  |  |

| RESET   | 0   | 0    | 0   | 0     | 0    | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W  | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |

| Address |     |      |     | F05H, | F0DH |     |     |     |  |  |

| Bit   | Description                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Pulse Width Modulator High and Low Bytes                                                                                                                   |

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current                                                               |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1). |

|       | The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in capture or CAPTURE/COMPARE modes.                             |

#### Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 60 through 62, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. This 24-bit value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate reload value; reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

Table 60. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit         | 7              | 6            | 5             | 4               | 3            | 2              | 1    | 0    |  |  |

|-------------|----------------|--------------|---------------|-----------------|--------------|----------------|------|------|--|--|

| Field       | WDTU           |              |               |                 |              |                |      |      |  |  |

| RESET       | 0              | 0            | 0             | 0               | 0            | 0              | 0    | 0    |  |  |

| R/W         | R/W*           | R/W*         | R/W*          | R/W*            | R/W*         | R/W*           | R/W* | R/W* |  |  |

| Address     | FF1H           |              |               |                 |              |                |      |      |  |  |

| Note: *A re | ead returns th | e current WD | T count value | e; a write sets | the appropri | ate reload val | lue. |      |  |  |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

Table 61. Watchdog Timer Reload High Byte Register (WDTH)

| Bit         | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-------------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Field       | WDTH                                                                                          |      |      |      |      |      |      |      |  |  |

| RESET       | 0                                                                                             | 0    | 0    | 0    | 0    | 1    | 0    | 0    |  |  |

| R/W         | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| Address     | FF2H                                                                                          |      |      |      |      |      |      |      |  |  |

| Note: *A re | Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |  |  |

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte, bits[15:8] of the 24-bit WDT reload value. |

## Comparator

The Z8 Encore! F0830 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or from an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The comparator includes the following features:

- Positive input is connected to a GPIO pin

- Negative input can be connected to either a GPIO pin or a programmable internal reference

- Output can be either an interrupt source or an output to an external pin

### **Operation**

One of the comparator inputs can be connected to an internal reference that is a user-selectable reference and is user-programmable with 200 mV resolution.

The comparator can be powered down to save supply current. For details, see the <u>Power Control Register 0</u> section on page 31.

**Caution:** As a result of the propagation delay of the comparator, Zilog does not recommend enabling the comparator without first disabling interrupts and waiting for the comparator output to settle. This delay prevents spurious interrupts after comparator enabling.

The following example shows how to safely enable the comparator:

```

di

ld cmp0,r0; load some new configuration

nop

nop ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

PS025113-1212 Comparator

#### Flash Page Select Register

The Flash Page Select Register shares address space with the Flash Sector Protect Register. Unless the Flash Controller is locked and written with 5EH, any writes to this address will target the Flash Page Select Register.

The register selects one of the eight available Flash memory pages to be programmed or erased. Each Flash page contains 512-bytes of Flash memory. During a page erase operation, all Flash memory containing addresses with the most significant 7-bits within FPS[6:0] are chosen for program/erase operations.

Table 74. Flash Page Select Register (FPS)

| Bit     | 7       | 6   | 5    | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|---------|-----|------|-----|-----|-----|-----|-----|--|--|

| Field   | INFO_EN |     | PAGE |     |     |     |     |     |  |  |

| RESET   | 0       | 0   | 0    | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |         |     |      | FF  | 9H  |     |     |     |  |  |

| Bit     | Description                                                                                                                                                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]     | Information Area Enable                                                                                                                                                                                                                                          |

| INFO_EN | N 0 = Information area is not selected.                                                                                                                                                                                                                          |

|         | 1 = Information area is selected. The information area is mapped into the program memory address space at addresses FE00H through FFFFH.                                                                                                                         |

| [6:0]   | Page Select                                                                                                                                                                                                                                                      |

| PAGE    | This 7-bit field identifies the Flash memory page for page erase and page unlocking. Program memory address[15:9] = PAGE[6:0]. For Z8F04xx and Z8F02xx devices, the upper four bits must always be 0. For Z8F01xx devices, the upper five bits must always be 0. |

Table 80. Trim Bit Data Register (TRMDR)

| Bit     | 7   | 6                    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|----------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | TRMDR: Trim Bit Data |     |     |     |     |     |     |  |  |  |

| RESET   | 0   | 0                    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W                  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     |                      |     | FF  | 7H  |     |     |     |  |  |  |

### Flash Option Bit Address Space

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits. See Tables 81 and 82.

Table 81. Flash Option Bits at Program Memory Address 0000H

| Bit                                             | 7       | 6                    | 5     | 4       | 3      | 2   | 1        | 0   |  |  |  |

|-------------------------------------------------|---------|----------------------|-------|---------|--------|-----|----------|-----|--|--|--|

| Field                                           | WDT_RES | WDT_AO               | OSC_S | EL[1:0] | VBO_AO | FRP | Reserved | FWP |  |  |  |

| RESET                                           | U       | U                    | U     | U       | U      | U   | U        | U   |  |  |  |

| R/W                                             | R/W     | R/W                  | R/W   | R/W     | R/W    | R/W | R/W      | R/W |  |  |  |

| Address                                         |         | Program Memory 0000H |       |         |        |     |          |     |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |         |                      |       |         |        |     |          |     |  |  |  |

| Bit              | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>WDT_RES   | Watchdog Timer Reset  0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.  1 = Watchdog Timer time-out causes a system reset. This is the default setting for unprogrammed (erased) Flash.                                                                                                                                             |

| [6]<br>WDT_AO    | <ul> <li>Watchdog Timer Always On</li> <li>0 = On application of system power, Watchdog Timer is automatically enabled. Watchdog Timer cannot be disabled.</li> <li>1 = Watchdog Timer is enabled on execution of the WDT instruction. Once enabled, the Watchdog Timer can only be disabled by a reset. This is the default setting for unprogrammed (erased) Flash.</li> </ul>                                                         |

| [5:4]<br>OSC_SEL | OSCILLATOR Mode Selection  00 = On-chip oscillator configured for use with external RC networks (<4MHz).  01 = Minimum power for use with very low frequency crystals (32 kHz to 1.0MHz).  10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 5.0MHz).  11 = Maximum power for use with high frequency crystals (5.0MHz to 20.0MHz). This is the default setting for unprogrammed (erased) Flash. |

#### **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the Byte Write routine (0x20B3). At the return from the subroutine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 91. Additionally, user code should pop the address and data bytes off the stack.

The write routine uses 16 bytes of stack space in addition to the two bytes of address and data pushed by the user code. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $136\mu s$  (assuming a 20MHz system clock). For every 200 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to  $58\,ms$  to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $7\mu s$  execution time.

Table 91. Write Status Byte

| Bit              | 7 | 6        | 5 | 4 | 3 | 2 | 1      | 0  |

|------------------|---|----------|---|---|---|---|--------|----|

| Field            |   | Reserved |   |   |   |   | IGADDR | WE |

| Default<br>Value | 0 | 0        | 0 | 0 | 0 | 0 | 0      | 0  |

| Bit           | Description                                                                                                                                                                                                                |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3]         | Reserved These bits are reserved and must be programmed to 00000.                                                                                                                                                          |

| [2]<br>FE     | Flash Error If a Flash error is detected, this bit is set to 1.                                                                                                                                                            |

| [1]<br>IGADDR | Illegal Address When an NVDS byte writes to invalid addresses occur (those exceeding the NVDS array size), this bit is set to 1.                                                                                           |

| [0]<br>WE     | Write Error A failure occurs during data writes to Flash. When writing data into a certain address, a read-back operation is performed. If the read-back value is not the same as the value written, this bit is set to 1. |

PS025113-1212 NVDS Code Interface

Table 98. Oscillator Configuration and Selection

| Clock Source                          | Characteristics                                                                                                                                | Required Setup                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Internal precision<br>RC oscillator   | <ul> <li>32.8 kHz or 5.53MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>                           | Unlock and write to the Oscillator Control Register (OSCCTL) to enable and select oscillator at either 5.53MHz or 32.8 kHz                                                                                                                                                      |  |  |  |  |  |

| External crystal/resonator            | <ul> <li>32 kHz to 20MHz</li> <li>Very high accuracy (dependent on crystal or resonator used)</li> <li>Requires external components</li> </ul> | <ul> <li>Configure Flash option bits for correct external OSCILLATOR Mode</li> <li>Unlock and write OSCCTL to enable crystal oscillator, wait for it to stabilize and select as system clock (if the XTLDIS option bit has been de-asserted, no waiting is required)</li> </ul> |  |  |  |  |  |

| External RC oscillator                | <ul> <li>32 kHz to 4MHz</li> <li>Accuracy dependent on external components</li> </ul>                                                          | <ul> <li>Configure Flash option bits for correct external OSCILLATOR Mode</li> <li>Unlock and write OSCCTL to enable crystal oscillator and select as system clock</li> </ul>                                                                                                   |  |  |  |  |  |

| External clock drive                  | 0 to 20MHz     Accuracy dependent on external clock source                                                                                     | <ul> <li>Write GPIO registers to configure PB3</li> <li>r- pin for external clock function</li> <li>Unlock and write OSCCTL to select external system clock</li> <li>Apply external clock signal to GPIO</li> </ul>                                                             |  |  |  |  |  |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Low power consumption</li> </ul>                     | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT oscillator is operating.</li> <li>Unlock and write to the Oscillator Control Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>                                                                         |  |  |  |  |  |

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a nonfunctioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

#### **OSC Control Register Unlocking/Locking**

To write the Oscillator Control Register, unlock it by making two writes to the OSCCTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a Locked state. Any other sequence of Oscillator Control Register writes have no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

PS025113-1212 Operation

Table 113. eZ8 CPU Instruction Summary (Continued)

| Assembly                      |                                     | Address<br>Mode |       | Op<br>Code(s) | Flags |   |       |   |   |   | Fetch | Instr. |

|-------------------------------|-------------------------------------|-----------------|-------|---------------|-------|---|-------|---|---|---|-------|--------|

| Mnemonic                      | Symbolic Operation                  | dst             | src   |               |       | Z | S V I |   |   | Н |       |        |

| LDX dst, src                  | dst ← src                           | r               | ER    | 84            | _     | _ | _     | _ | _ | _ | 3     | 2      |

|                               |                                     | lr              | ER    | 85            | _     |   |       |   |   |   | 3     | 3      |

|                               |                                     | R               | IRR   | 86            | _     |   |       |   |   |   | 3     | 4      |

|                               |                                     | IR              | IRR   | 87            |       |   |       |   |   |   | 3     | 5      |

|                               |                                     | r               | X(rr) | 88            |       |   |       |   |   |   | 3     | 4      |

|                               |                                     | X(rr)           | r     | 89            |       |   |       |   |   |   | 3     | 4      |

|                               |                                     | ER              | r     | 94            | _     |   |       |   |   |   | 3     | 2      |

|                               |                                     | ER              | lr    | 95            |       |   |       |   |   |   | 3     | 3      |

|                               |                                     | IRR             | R     | 96            |       |   |       |   |   |   | 3     | 4      |

|                               |                                     | IRR             | IR    | 97            | _     |   |       |   |   |   | 3     | 5      |

|                               |                                     | ER              | ER    | E8            | _     |   |       |   |   |   | 4     | 2      |

|                               |                                     | ER              | IM    | E9            |       |   |       |   |   |   | 4     | 2      |

| LEA dst, X(src) dst ← src + X |                                     | r               | X(r)  | 98            | _     | _ | _     | _ | _ | _ | 3     | 3      |

|                               |                                     | rr              | X(rr) | 99            | _     |   |       |   |   |   | 3     | 5      |

| MULT dst                      | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR              |       | F4            | -     | - | -     | - | - | - | 2     | 8      |

| NOP                           | No operation                        |                 |       | 0F            | _     | _ | _     | _ | _ | _ | 1     | 2      |

| OR dst, src                   | dst ← dst OR src                    | r               | r     | 42            | _     | * | *     | 0 | _ | _ | 2     | 3      |

|                               |                                     | r               | lr    | 43            | _     |   |       |   |   |   | 2     | 4      |

|                               |                                     | R               | R     | 44            | _     |   |       |   |   |   | 3     | 3      |

|                               |                                     | R               | IR    | 45            | _     |   |       |   |   |   | 3     | 4      |

|                               |                                     | R               | IM    | 46            | _     |   |       |   |   |   | 3     | 3      |

|                               |                                     | IR              | IM    | 47            | _     |   |       |   |   |   | 3     | 4      |

| ORX dst, src                  | dst ← dst OR src                    | ER              | ER    | 48            | _     | * | *     | 0 | _ | - | 4     | 3      |

|                               |                                     | ER              | IM    | 49            | _     |   |       |   |   |   | 4     | 3      |

| POP dst                       | dst ← @SP                           | R               |       | 50            | -     | _ | _     | _ | _ | _ | 2     | 2      |

|                               | SP ← SP + 1                         | IR              |       | 51            | _     |   |       |   |   |   | 2     | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 121. Nonvolatile Data Storage

|                             | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     |     |         | = 2.7 to 3<br>0°C to + |     |            |                                           |  |

|-----------------------------|----------------------------------------------------------------|-----|-----|---------|------------------------|-----|------------|-------------------------------------------|--|

| Parameter                   | Min                                                            | Тур | Max | Min     | Тур                    | Max | _<br>Units | Notes                                     |  |

| NVDS Byte Read<br>Time      |                                                                |     |     | 71      | -                      | 258 | μs         | Withsystemclockat<br>20MHz                |  |

| NVDS Byte Pro-<br>gram Time |                                                                |     |     | 126     | -                      | 136 | μs         | Withsystemclockat<br>20MHz                |  |

| Data Retention              |                                                                |     |     | 10      | _                      | _   | years      | 25°C                                      |  |

| Endurance                   |                                                                |     |     | 100,000 | -                      | -   | cycles     | Cumulative write cycles for entire memory |  |

Note:

For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write can take up to 58ms to complete.

Table 122. Analog-to-Digital Converter Electrical Characteristics and Timing

|                  | -<br>Parameter                                  | $V_{DD} = 2.7 \text{ to } 3.6 \text{V}$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ |     |     |            | = 2.7 to<br>40°C to |     |       |                |

|------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|------------|---------------------|-----|-------|----------------|

| Symbol           |                                                 | Min                                                                                          | Тур | Max | Min        | Тур                 | Max | Units | Conditions     |

|                  | Resolution                                      |                                                                                              |     |     | _          | 10                  | _   | bits  |                |

|                  | Differential<br>Nonlinearity (DNL) <sup>1</sup> |                                                                                              |     |     | <b>–1</b>  | -                   | +4  | LSB   |                |

|                  | Integral<br>Nonlinearity (INL) <sup>1</sup>     |                                                                                              |     |     | <b>-</b> 5 | -                   | +5  | LSB   |                |

|                  | Gain Error                                      |                                                                                              |     |     |            | 15                  |     | LSB   |                |

|                  | Offset Error                                    |                                                                                              |     |     | -15        | _                   | 15  | LSB   | PDIP package   |

|                  | _                                               |                                                                                              |     |     | -9         | _                   | 9   | LSB   | Other packages |

| V <sub>REF</sub> | On chip reference                               |                                                                                              |     |     | 1.9        | 2.0                 | 2.1 | V     |                |

|                  | Active Power<br>Consumption                     |                                                                                              |     |     |            | 4                   |     | mA    |                |

|                  | Power Down<br>Current                           |                                                                                              |     |     |            |                     | 1   | μΑ    |                |

Note: <sup>1</sup>When the input voltage is lower than 20 mV, the conversion error is out of spec.