Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0431ph020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| Electrical Characteristics 1                              | 184 |

|-----------------------------------------------------------|-----|

| Absolute Maximum Ratings 1                                | 184 |

| DC Characteristics 1                                      | 185 |

| AC Characteristics 1                                      | 189 |

| On-Chip Peripheral AC and DC Electrical Characteristics 1 | 190 |

| General Purpose I/O Port Input Data Sample Timing 1       | 195 |

| General Purpose I/O Port Output Timing 1                  | 196 |

| On-Chip Debugger Timing 1                                 | 197 |

| Packaging 1                                               | 199 |

| Ordering Information                                      | 200 |

| Part Number Suffix Designations 2                         | 205 |

| Appendix A. Register Tables                               | 208 |

| General Purpose RAM                                       | 208 |

| Timer 0                                                   | 208 |

| Analog-to-Digital Converter                               | 213 |

| Low Power Control                                         | 216 |

| LED Controller                                            | 216 |

| Oscillator Control                                        | 217 |

| Comparator 0                                              | 218 |

| Interrupt Controller                                      | 218 |

| GPIO Port A 2                                             | 222 |

| Watchdog Timer                                            | 226 |

| Trim Bit Control                                          | 228 |

| Flash Memory Controller    2                              | 228 |

| Index                                                     | 231 |

| Customer Support                                          | 239 |

|                                                           |     |

### ix

### Nonvolatile Data Storage

The Nonvolatile Data Storage (NVDS) function uses a hybrid hardware/software scheme to implement a byte-programmable data memory and is capable of storing about 100,000 write cycles.

### **Internal Precision Oscillator**

The Internal Precision Oscillator (IPO) function, with an accuracy of  $\pm 4\%$  full voltage/ temperature range, is a trimmable clock source that requires no external components.

### **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies using an external crystal, ceramic resonator or RC network.

### **10-Bit Analog-to-Digital Converter**

The optional Analog-to-Digital Converter (ADC) converts an analog input signal to a 10bit binary number. The ADC accepts inputs from eight different analog input pins.

### Analog Comparator

The analog comparator compares the signal at an input pin with either an internal programmable reference voltage or with a signal at the second input pin. The comparator output is used either to drive a logic output pin or to generate an interrupt.

### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT Modes.

### **Interrupt Controller**

The Z8 Encore! F0830 Series products support seventeen interrupt sources with sixteen interrupt vectors: up to five internal peripheral interrupts and up to twelve GPIO interrupts. These interrupts have three levels of programmable interrupt priority.

### 17

# **Register Map**

Table 8 provides an address map of the Z8 Encore! F0830 Series register file. Not all devices and package styles in the Z8 Encore! F0830 Series support the ADC or all of the GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)    | Register Description              | Mnemonic      | Reset (Hex) | Page No. |

|------------------|-----------------------------------|---------------|-------------|----------|

| General Purpos   | e RAM                             |               |             |          |

| 000–0FF          | General purpose register file RAM |               | XX          |          |

| 100–EFF          | Reserved                          | _             | XX          |          |

| Timer 0          |                                   |               |             |          |

| F00              | Timer 0 high byte                 | T0H           | 00          | 83       |

| F01              | Timer 0 low byte                  | TOL           | 01          | 83       |

| F02              | Timer 0 reload high byte          | TORH          | FF          | 85       |

| F03              | Timer 0 reload low byte           | TORL          | FF          | 85       |

| F04              | Timer 0 PWM high byte             | <b>T0PWMH</b> | 00          | 86       |

| F05              | Timer 0 PWM low byte              | TOPWML        | 00          | 86       |

| F06              | Timer 0 control 0                 | T0CTL0        | 00          | 87       |

| F07              | Timer 0 control 1                 | T0CTL1        | 00          | 88       |

| Timer 1          |                                   |               |             |          |

| F08              | Timer 1 high byte                 | T1H           | 00          | 83       |

| F09              | Timer 1 low byte                  | T1L           | 01          | 83       |

| F0A              | Timer 1 reload high byte          | T1RH          | FF          | 85       |

| F0B              | Timer 1 reload low byte           | T1RL          | FF          | 85       |

| F0C              | Timer 1 PWM high byte             | T1PWMH        | 00          | 86       |

| F0D              | Timer 1 PWM low byte              | T1PWML        | 00          | 86       |

| F0E              | Timer 1 control 0                 | T1CTL0        | 00          | 87       |

| F0F              | Timer 1 control 1                 | T1CTL1        | 00          | 83       |

| F10–F6F          | Reserved                          | _             | XX          |          |

| Analog-to-Digita | al Converter (ADC)                |               |             |          |

| F70              | ADC control 0                     | ADCCTL0       | 00          | 102      |

| F71              | Reserved                          |               | XX          |          |

| F72              | ADC data high byte                | ADCD_H        | XX          | 103      |

#### Table 8. Register File Address Map

Note: XX = Undefined.

• Writing 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (disable interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the Interrupt Controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction Trap

- Primary oscillator fail trap

- Watchdog Oscillator fail trap

### **Interrupt Vectors and Priority**

The Interrupt Controller supports three levels of interrupt priority. Level 3 is the highest priority, level 2 is the second highest priority and level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 54. Level 3 interrupts are always assigned higher priority than level 2 interrupts and level 2 interrupts are assigned higher priority than level 1 interrupts. Within each interrupt priority level (level 1, level 2 or level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), primary oscillator fail trap, Watchdog Oscillator fail trap and illegal instruction trap always have highest (level 3) priority.

### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the interrupt request register is cleared. Writing 0 to the corresponding bit in the interrupt request register clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

### **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit                  | 7                                                                                                                                                            | 6                                                                        | 5             | 4         | 3    | 2    | 1    | 0    |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------|-----------|------|------|------|------|

| Field                |                                                                                                                                                              | Rese                                                                     | erved         |           | PC3I | PC2I | PC1I | PC0I |

| RESET                | 0                                                                                                                                                            | 0                                                                        | 0             | 0         | 0    | 0    | 0    | 0    |

| R/W                  | R/W                                                                                                                                                          | R/W                                                                      | R/W           | R/W       | R/W  | R/W  | R/W  | R/W  |

| Address              |                                                                                                                                                              |                                                                          |               | FC        | 6H   |      |      |      |

| Bit                  | Description                                                                                                                                                  | Description                                                              |               |           |      |      |      |      |

| [7:4]                | Reserved<br>These regis                                                                                                                                      | Reserved<br>These registers are reserved and must be programmed to 0000. |               |           |      |      |      |      |

| [3]<br>PC <i>x</i> l | <ul> <li>0 = No interrupt request is pending for GPIO Port C pin x.</li> <li>1 = An interrupt request from GPIO Port C pin x is awaiting service.</li> </ul> |                                                                          |               |           |      |      |      |      |

| Note: x in           | dicates the sp                                                                                                                                               | ecific GPIO p                                                            | ort pin numbe | ər (3–0). |      |      |      |      |

#### Table 37. Interrupt Request 2 Register (IRQ2)

### **IRQ0 Enable High and Low Bit Registers**

Table 38 lists the priority control values for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling service for interrupts in the Interrupt Request 0 Register. Priority is generated by setting the bits in each register.

| IRQ0EN  | IH[x]    | IRQ0ENL[x]            | Priority         | Description |

|---------|----------|-----------------------|------------------|-------------|

| C       | )        | 0                     | Disabled         | Disabled    |

| C       | )        | 1                     | Level 1          | Low         |

| 1       |          | 0                     | Level 2          | Nominal     |

| 1       |          | 1                     | Level 3          | High        |

| Note: x | indicate | s the register bits i | n the range 7–0. |             |

Table 38. IRQ0 Enable and Priority Encoding

### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a pulse width modulated (PWM) output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to 16-bit PWM match value stored in the timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the timer output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the timer output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The timer output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the timer output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The timer output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps for configuring a timer for PWM SINGLE OUTPUT Mode and for initiating PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This value only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the timer output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

### Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 54 and 55, control PWM operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   |            |     |     | PW  | MH  |     |     |     |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F04H, F0CH |     |     |     |     |     |     |     |

#### Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

#### Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   |     |            |     | PW  | ML  |     |     |     |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F05H, F0DH |     |     |     |     |     |     |

#### Bit Description

| [7:0] | Pulse Width Modulator High and Low Bytes                                                     |

|-------|----------------------------------------------------------------------------------------------|

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1).                         |

|       | The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operat-      |

|       | ing in capture or CAPTURE/COMPARE modes.                                                     |

| Bit    | Description (Continued)                                                                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0]    | Input Capture Event                                                                                                                                                        |

| INPCAP | This bit indicates whether the most recent timer interrupt is caused by a timer input capture event.                                                                       |

|        | <ul> <li>0 = Previous timer interrupt is not caused by timer input capture event.</li> <li>1 = Previous timer interrupt is caused by timer input capture event.</li> </ul> |

### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

| Bit     | 7          | 6    | 5   | 4    | 3   | 2   | 1     | 0   |

|---------|------------|------|-----|------|-----|-----|-------|-----|

| Field   | TEN        | TPOL |     | PRES |     |     | TMODE |     |

| RESET   | 0          | 0    | 0   | 0    | 0   | 0   | 0     | 0   |

| R/W     | R/W        | R/W  | R/W | R/W  | R/W | R/W | R/W   | R/W |

| Address | F07H, F0FH |      |     |      |     |     |       |     |

| Bit | Description                                           |

|-----|-------------------------------------------------------|

| [7] | Timer Enable                                          |

| TEN | 0 = Timer is disabled.<br>1 = Timer enabled to count. |

#### Bit Description (Continued)

#### [6] Timer Input/Output Polarity

TPOL Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### **COUNTER Mode**

If the timer is disabled, the timer output signal is set to the value of this bit. If the timer is enabled the timer output signal is complemented after timer reload.

- 0 = Count occurs on the rising edge of the timer input signal.

- 1 = Count occurs on the falling edge of the timer input signal.

#### PWM SINGLE OUTPUT Mode

- 0 = Timer output is forced Low (0), when the timer is disabled. The timer output is forced High (1) when the timer is enabled and the PWM count matches and the timer output is forced Low (0) when the timer is enabled and reloaded.

- 1 = Timer output is forced High (1), when the timer is disabled. The timer output is forced low(0), when the timer is enabled and the PWM count matches and forced High (1) when the timer is enabled and reloaded.

#### CAPTURE Mode

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### COMPARE Mode

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### GATED Mode

- 0 = Timer counts when the timer input signal is High (1) and interrupts are generated on the falling edge of the timer input.

- 1 = Timer counts when the timer input signal is Low (0) and interrupts are generated on the rising edge of the timer input.

#### CAPTURE/COMPARE Mode

- 0 = Counting is started on the first rising edge of the timer input signal. The current count is captured on subsequent rising edges of the timer input signal.

- 1 = Counting is started on the first falling edge of the timer input signal. The current count is captured on subsequent falling edges of the timer input signal.

### **ADC Interrupt**

The ADC can generate an interrupt request when a conversion has been completed. An interrupt request that is pending when the ADC is disabled is not cleared automatically.

### **Reference Buffer**

The reference buffer, RBUF, supplies the reference voltage for the ADC. When enabled, the internal voltage reference generator supplies the ADC. When RBUF is disabled, the ADC must have the reference voltage supplied externally through the  $V_{REF}$  pin in 28-pin package. RBUF is controlled by the REFEN bit in the ADC Control Register.

### **Internal Voltage Reference Generator**

The internal voltage reference generator provides the voltage VR2, for the RBUF. VR2 is 2V.

### **Calibration and Compensation**

A user can perform calibration and store the values into Flash or the user code can perform a manual offset calibration. There is no provision for manual gain calibration.

# **ADC Control Register Definitions**

The ADC Control registers are defined in this section.

## **ADC Control Register 0**

The ADC Control 0 Register, shown in Table 63, initiates an A/D conversion and provides ADC status information.

| Bit            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                   | 5           | 4          | 3    | 2   | 1   | 0   |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------|------------|------|-----|-----|-----|--|

| Field          | START Reserved REFEN ADCEN Reserved ANAIN[2:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |             |            |      |     |     |     |  |

| RESET          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                   | 0           | 0          | 0    | 0   | 0   | 0   |  |

| R/W            | R/W1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W                                                                                                 | R/W         | R/W        | R/W  | R/W | R/W | R/W |  |

| Address        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                     |             | F7         | '0h  |     |     |     |  |

| Bit            | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | n                                                                                                   |             |            |      |     |     |     |  |

| [7]<br>START   | 0 = Writing sion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 = Writing to 1 starts a conversion; reading a 1 indicates that a conversion is currently in prog- |             |            |      |     |     |     |  |

| [6]            | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reserved<br>This bit is reserved and must be programmed to 0.                                       |             |            |      |     |     |     |  |

| [5]<br>REFEN   | <ul> <li>Reference Enable</li> <li>0 = Internal reference voltage is disabled allowing an external reference voltage to be used by the ADC.</li> <li>1 = Internal reference voltage for the ADC is enabled. The internal reference voltage can be measured on the V<sub>RFF</sub> pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                     |             |            |      |     |     |     |  |

| [4]<br>ADCEN   | 0 = ADC is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADC Enable<br>0 = ADC is disabled for low power operation.<br>1 = ADC is enabled for normal use.    |             |            |      |     |     |     |  |

| [3]            | Reserved<br>This bit is re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | eserved and                                                                                         | must be pro | ogrammed t | o 0. |     |     |     |  |

| [2:0]<br>ANAIN | This bit is reserved and must be programmed to 0.<br>Analog Input Select<br>000 = ANA0 input is selected for analog to digital conversion.<br>001 = ANA1 input is selected for analog to digital conversion.<br>010 = ANA2 input is selected for analog to digital conversion.<br>011 = ANA3 input is selected for analog to digital conversion.<br>100 = ANA4 input is selected for analog to digital conversion.<br>101 = ANA5 input is selected for analog to digital conversion.<br>101 = ANA6 input is selected for analog to digital conversion.<br>110 = ANA6 input is selected for analog to digital conversion.<br>111 = ANA7 input is selected for analog to digital conversion. |                                                                                                     |             |            |      |     |     |     |  |

### Table 63. ADC Control Register 0 (ADCCTL0)

bits can only be set to 1. Thus, sectors can be protected, but not unprotected, via register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register. Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased. After setting a bit in the Sector Protect Register, the bit cannot be cleared by the user.

### **Byte Programming**

Flash memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either mass erase or page erase. When the Flash Controller is unlocked and mass erase is successfully enabled, all of the program memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and page erase is successfully enabled, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the page erase or mass erase commands.

Byte programming can be accomplished using the On-Chip Debugger's write memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the <u>eZ8 CPU</u> <u>Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>, for the description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles, but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control Register, except the mass erase or page erase commands.

**Caution:** The byte at each address within Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs.

130

#### Table 83. Trim Bit Address Space

| Address | Function                      |

|---------|-------------------------------|

| 00h     | ADC reference voltage         |

| 01h     | ADC and comparator            |

| 02h     | Internal Precision Oscillator |

| 03h     | Oscillator and VBO            |

| 06h     | ClkFltr                       |

#### Table 84. Trim Option Bits at 0000H (ADCREF)

| Bit                                             | 7                             | 6  | 5         | 4        | 3 | 2 | 1 | 0 |

|-------------------------------------------------|-------------------------------|----|-----------|----------|---|---|---|---|

| Field                                           |                               | Al | DCREF_TRI | Reserved |   |   |   |   |

| RESET                                           |                               |    | U         | U        |   |   |   |   |

| R/W                                             |                               |    | R/W       | R/W      |   |   |   |   |

| Address                                         | Information Page Memory 0020H |    |           |          |   |   |   |   |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |    |           |          |   |   |   |   |

| Bit                  | Description                                                                          |

|----------------------|--------------------------------------------------------------------------------------|

| [7:3]<br>ADCREF_TRIM | ADC Reference Voltage Trim Byte<br>Contains trimming bits for ADC reference voltage. |

| [2:0]                | <b>Reserved</b><br>These bits are reserved and must be programmed to 111.            |

**Note:** The bit values used in Table 84 are set at the factory; no calibration is required.

| Bit                                             | 7                             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                           | Reserved                      |     |     |     |     |     |     |     |

| RESET                                           | U                             | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 0021H |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |     |     |     |     |     |     |

| Bit Description                                 |                               |     |     |     |     |     |     |     |

#### Table 85. Trim Option Bits at 0001H (TADC\_COMP)

| Bit   | Description                                                      |

|-------|------------------------------------------------------------------|

| [7:0] | Reserved                                                         |

|       | Altering this register may result in incorrect device operation. |

| Debug Command           | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit |

|-------------------------|-----------------|------------------------------------|----------------------------------------------|

| Read Program Memory CRC | 0EH             | -                                  | -                                            |

| Reserved                | 0FH             | -                                  | -                                            |

| Step Instruction        | 10H             | -                                  | Disabled                                     |

| Stuff Instruction       | 11H             | -                                  | Disabled                                     |

| Execute Instruction     | 12H             | -                                  | Disabled                                     |

| Reserved                | 13H–FFH         | _                                  | _                                            |

#### Table 95. On-Chip Debugger Command Summary (Continued)

In the following bulleted list of OCD commands, data and commands sent from the host to the OCD are identified by DBG  $\leftarrow$  Command/Data. Data sent from the OCD back to the host is identified by DBG Data.

**Read OCD Revision (00H).** The read OCD revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed or changed this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

**Read Runtime Counter (03H).** The runtime counter counts system clock cycles in between breakpoints. The 16-bit runtime counter counts from 0000H and stops at the maximum count of FFFFH. The runtime counter is overwritten during the write memory, read memory, write register, read register, read memory CRC, step instruction, stuff instruction and execute instruction commands.

```

DBG \leftarrow 03H

DBG \rightarrow RuntimeCounter[15:8]

DBG \rightarrow RuntimeCounter[7:0]

```

Write OCD Control Register (04H). The write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash read protect option bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0. To return the device to normal operating mode, the device must be reset.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

149

### Table 96. OCD Control Register (OCDCTL)

| Bit           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                                                                                                                                                                                                                          | 5           | 4          | 3           | 2     | 1 | 0   |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-------|---|-----|--|--|--|

| Field         | DBGMODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BRKEN                                                                                                                                                                                                                                                                                                                                                                                      | DBGACK      |            | Res         | erved |   | RST |  |  |  |

| RESET         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                          | 0           | 0          | 0           | 0     | 0 | 0   |  |  |  |

| R/W           | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                        | R/W         | R          | R           | R     | R | R/W |  |  |  |

| Bit           | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                |             |            |             |       |   |     |  |  |  |

| [7]<br>DBGMOD | DEBUG Mode<br>MODE The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU<br>stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is<br>automatically set when a BRK instruction is decoded and breakpoints are enabled. If the<br>Flash read protect option bit is enabled, this bit can only be cleared by resetting the device. It<br>cannot be written to 0.<br>0 = The Z8 Encore! F0830 Series device is operating in NORMAL Mode.<br>1 = The Z8 Encore! F0830 Series device is in DEBUG Mode. |                                                                                                                                                                                                                                                                                                                                                                                            |             |            |             |       |   |     |  |  |  |

| [6]<br>BRKEN  | This bit co<br>are disable<br>when a BR<br>cally set to<br>0 = Breakp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Breakpoint Enable</b><br>This bit controls the behavior of the BRK instruction (opcode 00H). By default, breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1 when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.<br>0 = Breakpoints are disabled.<br>1 = Breakpoints are enabled. |             |            |             |       |   |     |  |  |  |

| [5]<br>DBGACK | This bit en<br>Debug ack<br>0 = Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>Debug Acknowledge</li> <li>This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug acknowledge character (FFH) to the host when a breakpoint occurs.</li> <li>0 = Debug acknowledge is disabled.</li> <li>1 = Debug acknowledge is enabled.</li> </ul>                                                                                     |             |            |             |       |   |     |  |  |  |

| [4:1]         | Reserved<br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | are reserve                                                                                                                                                                                                                                                                                                                                                                                | ed and must | be progran | nmed to 000 | 00.   |   |     |  |  |  |

| [0]<br>RST    | <ul> <li>Reset</li> <li>Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal Power-On Reset sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 at the end of the reset sequence.</li> <li>0 = No effect.</li> <li>1 = Reset the Flash read protect option bit device.</li> </ul>                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                            |             |            |             |       |   |     |  |  |  |

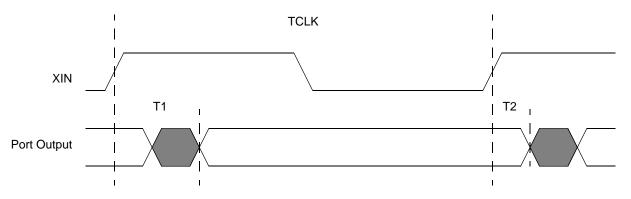

### **General Purpose I/O Port Output Timing**

Figure 34 and Table 125 provide timing information for the GPIO port pins.

|                |                                     | Dela    | Delay (ns) |  |  |

|----------------|-------------------------------------|---------|------------|--|--|

| Parameter      | Abbreviation                        | Minimum | Maximum    |  |  |

| GPIO Port F    | Pins                                |         |            |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _       | 15         |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2       | _          |  |  |

#### Table 125. GPIO Port Output Timing

### 200

# **Ordering Information**

Order your F0830 Series products from Zilog using the part numbers shown in Table 128. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

|                     |                 |           |      | ADC |             |

|---------------------|-----------------|-----------|------|-----|-------------|

| Part Number         | Flash           | RAM       | NVDS | -   | Description |

| Z8 Encore! F0830 Se | ries MCUs wi    | th 12KB F | lash |     |             |

| Standard Temperatu  | re: 0°C to 70°  | С         |      |     |             |

| Z8F1232SH020SG      | 12KB            | 256       | No   | 7   | SOIC 20-pin |

| Z8F1232HH020SG      | 12KB            | 256       | No   | 7   | SSOP 20-pin |

| Z8F1232PH020SG      | 12KB            | 256       | No   | 7   | PDIP 20-pin |

| Z8F1232QH020SG      | 12KB            | 256       | No   | 7   | QFN 20-pin  |

| Z8F1233SH020SG      | 12KB            | 256       | No   | 0   | SOIC 20-pin |

| Z8F1233HH020SG      | 12KB            | 256       | No   | 0   | SSOP 20-pin |

| Z8F1233PH020SG      | 12KB            | 256       | No   | 0   | PDIP 20-pin |

| Z8F1233QH020SG      | 12KB            | 256       | No   | 0   | QFN 20-pin  |

| Z8F1232SJ020SG      | 12KB            | 256       | No   | 8   | SOIC 28-pin |

| Z8F1232HJ020SG      | 12KB            | 256       | No   | 8   | SSOP 28-pin |

| Z8F1232PJ020SG      | 12KB            | 256       | No   | 8   | PDIP 28-pin |

| Z8F1232QJ020SG      | 12KB            | 256       | No   | 8   | QFN 28-pin  |

| Z8F1233SJ020SG      | 12KB            | 256       | No   | 0   | SOIC 28-pin |

| Z8F1233HJ020SG      | 12KB            | 256       | No   | 0   | SSOP 28-pin |

| Z8F1233PJ020SG      | 12KB            | 256       | No   | 0   | PDIP 28-pin |

| Z8F1233QJ020SG      | 12KB            | 256       | No   | 0   | QFN 28-pin  |

| Extended Temperatu  | ire: -40°C to 1 | 105°C     |      |     |             |

| Z8F1232SH020EG      | 12KB            | 256       | No   | 7   | SOIC 20-pin |

| Z8F1232HH020EG      | 12KB            | 256       | No   | 7   | SSOP 20-pin |

| Z8F1232PH020EG      | 12KB            | 256       | No   | 7   | PDIP 20-pin |

| Z8F1232QH020EG      | 12KB            | 256       | No   | 7   | QFN 20-pin  |

| Z8F1233SH020EG      | 12KB            | 256       | No   | 0   | SOIC 20-pin |

| Z8F1233HH020EG      | 12KB            | 256       | No   | 0   | SSOP 20-pin |

| Z8F1233PH020EG      | 12KB            | 256       | No   | 0   | PDIP 20-pin |

#### Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

# Low Power Control

For more information about the Power Control Register, see the <u>Power Control Register</u> <u>Definitions</u> section on page 31.

### Hex Address: F80

| Bit     | 7        | 6   | 5   | 4   | 3        | 2        | 1    | 0        |

|---------|----------|-----|-----|-----|----------|----------|------|----------|

| Field   | Reserved |     |     | VBO | Reserved | Reserved | COMP | Reserved |

| RESET   | 1        | 0   | 0   | 0   | 1        | 0        | 0    | 0        |

| R/W     | R/W      | R/W | R/W | R/W | R/W      | R/W      | R/W  | R/W      |

| Address | F80H     |     |     |     |          |          |      |          |

#### Table 151. Power Control Register 0 (PWRCTL0)

### Hex Address: F81

This address range is reserved.

# **LED Controller**

For more information about the LED Drive registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

### Hex Address: F82

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | LEDEN[7:0] |     |     |     |     |     |     |     |  |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F82H       |     |     |     |     |     |     |     |  |

#### Table 152. LED Drive Enable (LEDEN)

### Hex Address: FDF

| Table 183. | Port D | Output | Data | Register | (PDOUT) |

|------------|--------|--------|------|----------|---------|

|            | IOIUD  | Output | Data | Register |         |

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | FDFH  |       |       |       |       |       |       |       |  |

#### Hex Addresses: FE0–FEF

This address range is reserved.

# Watchdog Timer

For more information about the Watchdog Timer registers, see the <u>Watchdog Timer Con-</u> trol Register Definitions section on page 95.

### Hex Address: FF0

The Watchdog Timer Control Register address is shared with the read-only Reset Status Register.

| Bit     | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---------|---|---|---|---|---|---|---|--|

| Field   | WDTUNLK |   |   |   |   |   |   |   |  |

| RESET   | Х       | Х | Х | Х | Х | Х | Х | Х |  |

| R/W     | W       | W | W | W | W | W | W | W |  |

| Address | FF0H    |   |   |   |   |   |   |   |  |

| Bit     | 7                              | 6    | 5   | 4   | 3        | 2 | 1 | 0 |

|---------|--------------------------------|------|-----|-----|----------|---|---|---|

| Field   | POR                            | STOP | WDT | EXT | Reserved |   |   |   |

| RESET   | See <u>Table 12</u> on page 29 |      |     | 0   | 0        | 0 | 0 | 0 |

| R/W     | R                              | R    | R   | R   | R        | R | R | R |

| Address | FFOH                           |      |     |     |          |   |   |   |

Table 185. Reset Status Register (RSTSTAT)

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

read program memory CRC (0EH) 147 read register (09H) 146 read runtime counter (03H) 145 step instruction (10H) 148 stuff instruction (11H) 148 write data memory (0CH) 147 write OCD control register (04H) 145 write program counter (06H) 146 write program memory (0AH) 146 write register (08H) 146 on-chip debugger (OCD) 139 on-chip debugger signals 12 on-chip oscillator 157 one-shot mode 89 opcode map abbreviations 181 cell description 180 first 182 second after 1FH 183 operation 100 current measurement 99 voltage measurement timing diagram 100 Operational Description 21, 30, 33, 53, 68, 92, 98, 106, 108, 124, 134, 139, 151, 157, 161 OR 169 ordering information 200 ORX 169 oscillator signals 12

### Ρ

p 164

Packaging 199

part selection guide 2

PC 165

peripheral AC and DC electrical characteristics 190

pin characteristics 13

Pin Descriptions 7

polarity 164

POP 168

pop using extended addressing 168

POPX 168

port availability, device 33

port input timing (GPIO) 195

port output timing, GPIO 196 power supply signals 12 power-on reset (POR) 23 program control instructions 169 program memory 15 PUSH 168 push using extended addressing 168 PUSHX 168 PWM mode 89, 90 PxADDR register 40, 222, 223, 224, 225 PxCTL register 41, 222, 223, 224, 225

## R

R 165 r 164 RA register address 165 RCF 167, 168 register 165 flash control (FCTL) 119, 126, 127, 228 flash high and low byte (FFREQH and FRE-EQL) 123 flash page select (FPS) 121, 122 flash status (FSTAT) 120 GPIO port A-H address (PxADDR) 40, 222, 223, 224, 225 GPIO port A-H alternate function sub-registers 42 GPIO port A-H control address (PxCTL) 41, 222, 223, 224, 225 GPIO port A-H data direction sub-registers 41 OCD control 148 OCD status 150 watch-dog timer control (WDTCTL) 95, 107, 154, 217, 218, 226 watchdog timer control (WDTCTL) 29 watch-dog timer reload high byte (WDTH) 227 watchdog timer reload high byte (WDTH) 96 watch-dog timer reload low byte (WDTL) 227 watchdog timer reload low byte (WDTL) 97 watch-dog timer reload upper byte (WDTU) 227

236