Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0431ph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2012 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES or TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES or TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| ADC Control Register Definitions10ADC Control Register 010ADC Data High Byte Register10ADC Data Low Bits Register10Sample Settling Time Register10Sample Time Register10                                                                                                                                                                                                                                                                                                                                                                                                 | )2<br>)3<br>)3<br>)4                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Comparator10Operation10Comparator Control Register Definitions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )6                                              |

| Flash Memory       10         Data Memory Address Space       11         Flash Information Area       11         Operation       11         Flash Operation Timing Using the Flash Frequency Registers       11                                                                                                                                                                                                                                                                                                                                                          | 1<br>1<br>2                                     |

| Flash Code Protection Against External Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                                               |

| Flash Code Protection Against Accidental Program and Erasure11Byte Programming11Page Erase11Mass Erase11Flash Controller Bypass11Flash Controller Behavior in Debug Mode11NVDS Operational Requirements11Flash Control Register Definitions11Flash Control Register Definitions11Flash Status Register12Flash Status Register12Flash Page Select Register12Flash Sector Protect Register12Flash Frequency High and Low Byte Registers12                                                                                                                                  | 6<br>7<br>7<br>7<br>7<br>8<br>8<br>9<br>0<br>21 |

| Flash Option Bits       12.         Operation       12.         Option Bit Configuration by Reset       12.         Option Bit Types       12.         Flash Option Bit Control Register Definitions       12.         Flash Option Bit Control Register Definitions       12.         Flash Option Bit Control Register Definitions       12.         Trim Bit Address Register       12.         Trim Bit Data Register       12.         Flash Option Bit Address Space       12.         Trim Bit Address Space       12.         Nonvolatile Data Storage       13. | 24<br>24<br>25<br>26<br>26<br>26<br>27<br>29    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                               |

Calibration and Compensation ..... 101

### vii

# **Signal Descriptions**

Table 4 describes the Z8 Encore! F0830 Series signals. See the <u>Pin Configurations</u> section on page 7 to determine the signals available for each specific package style.

| Signal<br>Mnemonic                             | I/O | Description                                                                                                                     |  |  |  |  |  |  |

|------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| General-Purpose I/O Ports A–D                  |     |                                                                                                                                 |  |  |  |  |  |  |

| PA[7:0]                                        | I/O | Port A. These pins are used for general purpose I/O.                                                                            |  |  |  |  |  |  |

| PB[7:0]                                        | I/O | Port B. These pins are used for general purpose I/O. PB6 and PB7 are available only in those devices without an ADC.            |  |  |  |  |  |  |

| PC[7:0]                                        | I/O | Port C. These pins are used for general purpose I/O.                                                                            |  |  |  |  |  |  |

| PD[0]                                          | I/O | Port D. This pin is used for general purpose output only.                                                                       |  |  |  |  |  |  |

| Note: PB6 and PB7<br>placed by AV <sub>I</sub> |     | available in 28-pin packages without ADC. In 28-pin packages with ADC, they are re- $^{\prime}_{\rm SS}$                        |  |  |  |  |  |  |

| Timers                                         |     |                                                                                                                                 |  |  |  |  |  |  |

| T0OUT/T1OUT                                    | 0   | Timer output 0–1. These signals are the output from the timers.                                                                 |  |  |  |  |  |  |

| T0OUT/T1OUT                                    | 0   | Timer complement output 0–1. These signals are output from the timers in PWM DUAL OUTPUT Mode.                                  |  |  |  |  |  |  |

| T0IN/T1IN                                      | I   | Timer Input 0–1. These signals are used as the capture, gating and counte inputs. The T0IN signal is multiplexed T0OUT signals. |  |  |  |  |  |  |

| Comparator                                     |     |                                                                                                                                 |  |  |  |  |  |  |

| CINP/CINN                                      | I   | Comparator inputs. These signals are the positive and negative inputs to the comparator.                                        |  |  |  |  |  |  |

| COUT                                           | 0   | Comparator output. This is the output of the comparator.                                                                        |  |  |  |  |  |  |

| Analog                                         |     |                                                                                                                                 |  |  |  |  |  |  |

| ANA[7:0]                                       | I   | Analog port. These signals are used as inputs to the analog-to-digital converter (ADC).                                         |  |  |  |  |  |  |

| V <sub>REF</sub>                               | I/O | Analog-to-digital converter reference voltage input.                                                                            |  |  |  |  |  |  |

|                                                |     | <b>Note:</b> When configuring ADC using external $V_{REF}$ , PB5 is used as $V_{REF}$ in 28-pin package.                        |  |  |  |  |  |  |

|                                                |     | nals are available only in the 28-pin packages with ADC. They are replaced by PB6 ages without ADC.                             |  |  |  |  |  |  |

### **Table 4. Signal Descriptions**

# Operation

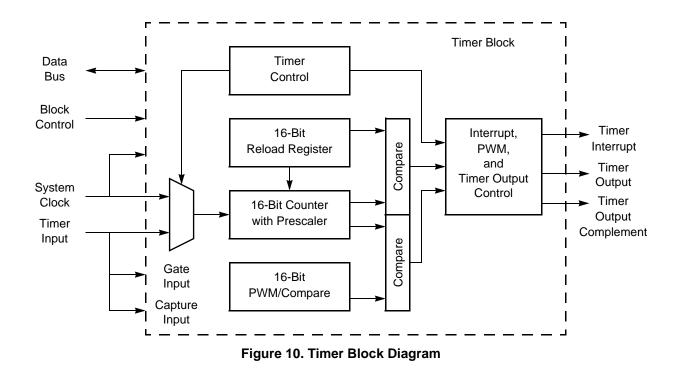

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer resets back to 0000H and continues counting.

### **Timer Operating Modes**

The timers can be configured to operate in the following modes:

### **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

Additionally, if the timer output alternate function is enabled, the timer output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer

reload. For the timer output to make a state change at a ONE-SHOT time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode

- Set the prescale value

- Set the initial output level (High or Low) if using the timer output Alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

One-Shot Mode Time-Out Period (s) =  $\frac{(\text{Reload Value} - \text{Start Value}) \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and for initiating the count:

1. Write to the Timer Control Register to:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period.

If TPOL bit is set to 0, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL bit is set to 1, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{PWM Value}}{\text{Reload Value}} \times 100$

### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to 16-bit PWM match value stored in the timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the timer output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the timer output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The timer output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the timer output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The timer output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal: the timer output complement. The timer output complement is the complement of the timer output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a Low to a High (inactive to active) to ensure a time gap between the deassertion of one PWM output to the assertion of its complement.

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers. <u>Timer 0–1 High and Low Byte Registers</u>: see page 83

Timer Reload High and Low Byte Registers: see page 85

Timer 0-1 PWM High and Low Byte Registers: see page 86

Timer 0-1 Control Registers: see page 87

# Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers, shown in Tables 50 and 51, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register content when the timer is enabled; however, when the timer is disabled, a read from the TxL reads the TxL Register content directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations; therefore, simultaneous 16-bit writes are not possible. If either the timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low byte) at the next clock edge. The counter continues counting from the new value.

| Bit     | 7          | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------|-----------------------------|---|---|---|---|---|---|--|

| Field   | TH         |                             |   |   |   |   |   |   |  |

| RESET   | 0          | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |  |

| R/W     | R/W        | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | F00H, F08H |                             |   |   |   |   |   |   |  |

Table 50. Timer 0–1 High Byte Register (TxH)

| Table 51 | . Timer 0–1 | Low Byte | Register | (TxL) |

|----------|-------------|----------|----------|-------|

|          |             |          |          |       |

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|

| Field   | TL  |                             |   |   |   |   |   |   |  |

| RESET   | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 1 |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address |     | F01H, F09H                  |   |   |   |   |   |   |  |

# **Timer 0–1 Control Registers**

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

### Time 0–1 Control Register 0

The Timer Control 0 (TxCTL0) and Timer Control 1 (TxCTL1) registers determine the timer operating mode. These registers also include a programmable PWM deadband delay, two bits to configure the timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

|         |         |                       |      |          |               | - |   |        |

|---------|---------|-----------------------|------|----------|---------------|---|---|--------|

| Bit     | 7       | 6                     | 5    | 4        | 3             | 2 | 1 | 0      |

| Field   | TMODEHI | TICO                  | NFIG | Reserved | Reserved PWMD |   |   | INPCAP |

| RESET   | 0       | 0                     | 0    | 0        | 0             | 0 | 0 | 0      |

| R/W     | R/W     | R/W R/W R/W R/W R/W I |      |          |               |   |   | R/W    |

| Address |         | F06H, F0EH            |      |          |               |   |   |        |

| Table 56. Ti | mer 0–1 Cor | ntrol Register | 0 (TxCTL0) |

|--------------|-------------|----------------|------------|

|--------------|-------------|----------------|------------|

| Bit               | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TMODEHI    | <b>Timer Mode High Bit</b><br>This bit along with the TMODE field in the TxCTL1 Register determines the operating mode<br>of the timer. This is the most significant bit of the timer mode selection value. See the<br>TxCTL1 Register description on the next page for additional details.                                                                                                                         |

| [6:5]<br>TICONFIG | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer interrupt occurs on all of the defined reload, compare and input events.</li> <li>10 = Timer interrupt occurs only on defined input capture/deassertion events.</li> <li>11 = Timer interrupt occurs only on defined reload/compare events.</li> </ul>                                        |

| [4]               | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                |

| [3:1]<br>PWMD     | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the timer output and the timer output complement are forced to their Active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>110 = 64 cycles delay.<br>111 = 128 cycles delay. |

# Watchdog Timer

The Watchdog Timer (WDT) protects from corrupted or unreliable software, power faults and other system-level problems which can place the Z8 Encore! F0830 Series devices into unsuitable operating states. The features of the Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The Watchdog Timer is a retriggerable one-shot timer that resets or interrupts the Z8 Encore! F0830 Series devices when the WDT reaches its terminal count. The WDT uses a dedicated on-chip RC oscillator as its clock source. The WDT operates only in two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the WDT to operate immediately on reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is calculated using the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the 24-bit decimal value provided by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10KHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10KHz Typical WDT Oscillator Frequency) |                        |  |  |  |

|------------------|------------------|-----------------------------------------------------------------------------|------------------------|--|--|--|

| (Hex)            | (Decimal)        | Typical                                                                     | Description            |  |  |  |

| 000004           | 4                | 400µs                                                                       | Minimum time-out delay |  |  |  |

| 000400           | 1024             | 102ms                                                                       | Default time-out delay |  |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                                  | Maximum time-out delay |  |  |  |

#### Table 58. Watchdog Timer Approximate Time-Out Delays

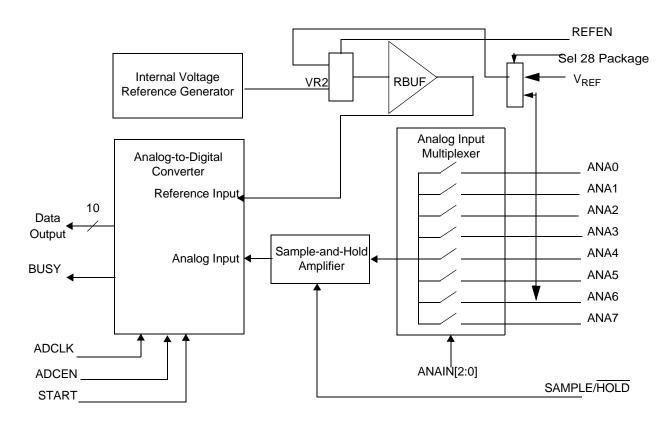

Figure 11. Analog-to-Digital Converter Block Diagram

# Operation

The ADC converts the analog input,  $ANA_X$ , to a 10-bit digital representation. The equation for calculating the digital value is represented by:

ADCOutput =  $1024 \times (ANA_x \div V_{REF})$

Assuming zero gain and offset errors, any voltage outside the ADC input limits of  $AV_{SS}$  and  $V_{REF}$  returns all 0s or 1s, respectively. A new conversion can be initiated by a software to the ADC Control Register's start bit.

Initiating a new conversion, stops any conversion currently in progress and begins a new conversion. To avoid disrupting a conversion already in progress, the START bit can be read to determine ADC operation status (busy or available).

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

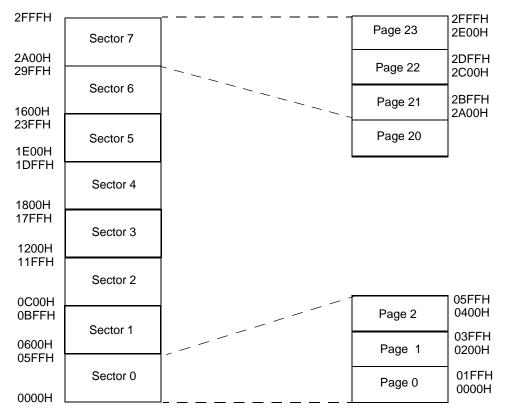

Figure 18. 12K Flash without NVDS

### **Data Memory Address Space**

The Flash information area, including Zilog Flash option bits, are located in the data memory address space. The Z8 Encore! MCU is configured by these proprietary Flash option bits to prevent the user from writing to the eZ8 CPU data memory address space.

## **Flash Information Area**

The Flash information area is physically separate from program memory and is mapped to the address range FE00H to FE7FH. Not all of these addresses are user-accessible. Factory trim values for the VBO, Internal Precision Oscillator and factory calibration data for the ADC are stored here.

Table 70 describes the Flash information area. This 128-byte information area is accessed by setting the bit 7 of the Flash Page Select Register to 1. When access is enabled, the

### Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

### Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

### Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

# **Option Bit Types**

This section describes the two types of Flash option bits offered in the F0830 Series.

### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. User access to these bits is provided because these locations contain application specific device configurations. The information contained here is lost when page 0 of program memory is erased.

## **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered by the user. Program memory can be erased without endangering these values. It is possible to alter working values of these bits by accessing the trim bit address and data registers, but these working values are lost after a power loss.

There are 32 bytes of trim data. To modify one of these values, the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20–3F only. The remaining information page is not accessible via the Trim Bit Address and Data registers.

During reset, the first 43 system clock cycles perform 43 Flash accesses. The six bits of the counter provide the lower six bits of the Flash memory address. All other address bits are set to 0. The option bit registers use the 6-bit address from the counter as an address and latch the data from the Flash on the positive edge of the IPO clock, allowing for a maximum of 344-bits (43 bytes) of option information to be read from Flash.

Because option information is stored in both the first two bytes of program memory and in the information area of Flash memory, the data must be placed in specific locations to be read correctly. In this case, the first two bytes at addresses 0 and 1 in program memory are read out and the remainder of the bytes are read out of the Flash information area.

Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

2. Use as few unique addresses as possible to optimize the impact of refreshing.

### **Runtime Counter**

The OCD contains a 16-bit runtime counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash read protect option bit (FRP). The FRP prevents the code in memory from being read out of the Z8 Encore! F0830 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 95 summarizes the On-Chip Debugger commands. This table indicates the commands that operate when the device is not in DEBUG Mode (normal operation) and the commands that are disabled by programming the FRP.

| Debug Command              | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                                     |

|----------------------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                | -                                                                                                                                                                                |

| Reserved                   | 01H             | _                                  | _                                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                                | _                                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                                  | -                                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                                | Cannot clear DBGMODE bit                                                                                                                                                         |

| Read OCD Control Register  | 05H             | Yes                                | _                                                                                                                                                                                |

| Write Program Counter      | 06H             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Counter       | 07H             | _                                  | Disabled                                                                                                                                                                         |

| Write Register             | 08H             | _                                  | Only writes of the Flash Memory Con-<br>trol registers are allowed. Additionally,<br>only the Mass Erase command is<br>allowed to be written to the Flash Con-<br>trol register. |

| Read Register              | 09H             | _                                  | Disabled                                                                                                                                                                         |

| Write Program Memory       | 0AH             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Memory        | 0BH             | _                                  | Disabled                                                                                                                                                                         |

| Write Data Memory          | 0CH             | _                                  | Yes                                                                                                                                                                              |

| Read Data Memory           | 0DH             | _                                  | _                                                                                                                                                                                |

#### Table 95. On-Chip Debugger Command Summary

# **Oscillator Control**

The Z8 Encore! F0830 Series device uses five possible clocking schemes. Each one of these is user-selectable.

- On-chip precision trimmed RC oscillator

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low precision Watchdog Timer Oscillator

In addition, Z8 Encore! F0830 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

## Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined further in this document.

### **System Clock Selection**

The oscillator control block selects from the available clocks. *Table 98* describes each clock source and its usage.

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50pF on all outputs.

|                     |                                            |     | 7 to 3.6V<br>to +70°C |              |        |       |                                                                                                              |

|---------------------|--------------------------------------------|-----|-----------------------|--------------|--------|-------|--------------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                                  | Min | Max                   | Min          | Max    | Units | Conditions                                                                                                   |

| F <sub>SYSCLK</sub> | System Clock Fre-<br>quency                |     |                       | -            | 20.0   | MHz   | Read-only from Flash<br>memory                                                                               |

|                     |                                            |     |                       | 0.03276<br>8 | 20.0   | MHz   | Program or erasure of the Flash memory                                                                       |

| F <sub>XTAL</sub>   | Crystal Oscillator<br>Frequency            |     |                       | 1.0          | 20.0   | MHz   | System clock frequen-<br>cies below the crystal<br>oscillator minimum<br>require an external                 |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |     |                       | 0.03276<br>8 | 5.5296 | MHz   | Oscillator is <b>not</b> adjust-<br>able over the entire<br>range. User may select<br>Min or Max value only. |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |     |                       | 5.31         | 5.75   | MHz   | High speed with trim-<br>ming                                                                                |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |     |                       | 4.15         | 6.91   | MHz   | High speed without trimming                                                                                  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |     |                       | 30.7         | 33.3   | KHz   | Low speed with trim-<br>ming                                                                                 |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |     |                       | 24           | 40     | KHz   | Low speed without trimming                                                                                   |

| T <sub>XIN</sub>    | System Clock<br>Period                     |     |                       | 50           | -      | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                     |

| T <sub>XINH</sub>   | System Clock High<br>Time                  |     |                       | 20           | 30     | ns    | T <sub>CLK</sub> = 50 ns                                                                                     |

| T <sub>XINL</sub>   | System Clock Low<br>Time                   |     |                       | 20           | 30     | ns    | T <sub>CLK</sub> = 50 ns                                                                                     |

### **Table 117. AC Characteristics**

### 200

# **Ordering Information**

Order your F0830 Series products from Zilog using the part numbers shown in Table 128. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

|                      |               |            |      | ADC | -           |

|----------------------|---------------|------------|------|-----|-------------|

| Part Number          | Flash         | RAM        | NVDS | -   | Description |

| Z8 Encore! F0830 Ser | ries MCUs wi  | ith 12KB F | lash |     |             |

| Standard Temperatur  | e: 0°C to 70° | °C         |      |     |             |

| Z8F1232SH020SG       | 12KB          | 256        | No   | 7   | SOIC 20-pin |

| Z8F1232HH020SG       | 12KB          | 256        | No   | 7   | SSOP 20-pin |

| Z8F1232PH020SG       | 12KB          | 256        | No   | 7   | PDIP 20-pin |

| Z8F1232QH020SG       | 12KB          | 256        | No   | 7   | QFN 20-pin  |

| Z8F1233SH020SG       | 12KB          | 256        | No   | 0   | SOIC 20-pin |

| Z8F1233HH020SG       | 12KB          | 256        | No   | 0   | SSOP 20-pin |

| Z8F1233PH020SG       | 12KB          | 256        | No   | 0   | PDIP 20-pin |

| Z8F1233QH020SG       | 12KB          | 256        | No   | 0   | QFN 20-pin  |

| Z8F1232SJ020SG       | 12KB          | 256        | No   | 8   | SOIC 28-pin |

| Z8F1232HJ020SG       | 12KB          | 256        | No   | 8   | SSOP 28-pin |

| Z8F1232PJ020SG       | 12KB          | 256        | No   | 8   | PDIP 28-pin |

| Z8F1232QJ020SG       | 12KB          | 256        | No   | 8   | QFN 28-pin  |

| Z8F1233SJ020SG       | 12KB          | 256        | No   | 0   | SOIC 28-pin |

| Z8F1233HJ020SG       | 12KB          | 256        | No   | 0   | SSOP 28-pin |

| Z8F1233PJ020SG       | 12KB          | 256        | No   | 0   | PDIP 28-pin |

| Z8F1233QJ020SG       | 12KB          | 256        | No   | 0   | QFN 28-pin  |

| Extended Temperatu   | re: –40°C to  | 105°C      |      |     |             |

| Z8F1232SH020EG       | 12KB          | 256        | No   | 7   | SOIC 20-pin |

| Z8F1232HH020EG       | 12KB          | 256        | No   | 7   | SSOP 20-pin |

| Z8F1232PH020EG       | 12KB          | 256        | No   | 7   | PDIP 20-pin |

| Z8F1232QH020EG       | 12KB          | 256        | No   | 7   | QFN 20-pin  |

| Z8F1233SH020EG       | 12KB          | 256        | No   | 0   | SOIC 20-pin |

| Z8F1233HH020EG       | 12KB          | 256        | No   | 0   | SSOP 20-pin |

| Z8F1233PH020EG       | 12KB          | 256        | No   | 0   | PDIP 20-pin |

|                      |               |            |      |     |             |

#### Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

### Hex Address: FD7

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | FD7H  |       |       |       |       |       |       |       |

### Table 176. Port B Output Data Register (PBOUT)

### Hex Address: FD8

#### Table 177. Port C GPIO Address Register (PCADDR)

| Bit     | 7                           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-----------------------------|---|---|---|---|---|---|---|--|

| Field   | PADDR[7:0]                  |   |   |   |   |   |   |   |  |

| RESET   | 00H                         |   |   |   |   |   |   |   |  |

| R/W     | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |   |  |

| Address | FD8H                        |   |   |   |   |   |   |   |  |

### Hex Address: FD9

#### Table 178. Port C Control Registers (PCCTL)

| Bit     | 7                       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------------------------|---|---|---|---|---|---|---|--|

| Field   | PCTL                    |   |   |   |   |   |   |   |  |

| RESET   | 00H                     |   |   |   |   |   |   |   |  |

| R/W     | R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |   |  |

| Address | FD9H                    |   |   |   |   |   |   |   |  |

### Hex Address: FDA

#### Table 179. Port C Input Data Registers (PCIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |

| Address | FDAH |      |      |      |      |      |      |      |

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

load external data to/from data memory and autoincrement addresses 167 load external to/from data memory and auto-increment addresses 168 load instructions 168 load using extended addressing 168 logical AND 169 logical AND/extended addressing 169 logical exclusive OR 169 logical exclusive OR/extended addressing 169 logical OR 169 logical OR 169 logical OR/extended addressing 169

### Μ

master interrupt enable 55 memory data 16 program 15 mode capture 89, 90 capture/compare 89 continuous 89 counter 89 gated 89 one-shot 89 PWM 89.90 modes 89 motor control measurements ADC Control register definitions 101 calibration and compensation 101 interrupts 101 overview 98 **MULT 167** multiply 167

## Ν

noise, electrical 98 NOP (no operation) 168 notation b 164

DA 164 ER 164 IM 164 IR 164 Ir 164 IRR 164 Irr 164 p 164 R 165 r 164 RA 165 RR 165 rr 165 vector 165 X 165 notational shorthand 164

cc 164

# 0

OCD architecture 139 auto-baud detector/generator 142 baud rate limits 142 block diagram 139 breakpoints 143 commands 144 control register 148 data format 142 DBG pin to RS-232 Interface 140 debug mode 141 debugger break 169 interface 140 serial errors 143 status register 150 timing 197 OCD commands execute instruction (12H) 148 read data memory (0DH) 147 read OCD control register (05H) 146 read OCD revision (00H) 145 read OCD status register (02H) 145 read program counter (07H) 146 read program memory (0BH) 147