Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-VQFN                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0431qj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Description**

The Z8 Encore! F0830 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and the pin configurations for each of the package styles. For information about the physical package specifications, see the <u>Packaging</u> chapter on page 199.

# **Available Packages**

Table 3 lists the package styles that are available for each device in the Z8 Encore! F0830 Series product line.

| Part<br>Number | ADC | 20-pin<br>QFN | 20-pin<br>SOIC | 20-pin<br>SSOP | 20-pin<br>PDIP | 28-pin<br>QFN | 28-pin<br>SOIC | 28-pin<br>SSOP | 28-pin<br>PDIP |

|----------------|-----|---------------|----------------|----------------|----------------|---------------|----------------|----------------|----------------|

| Z8F1232        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F1233        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0830        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0831        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0430        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0431        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0230        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0231        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0130        | Yes | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

| Z8F0131        | No  | Х             | Х              | Х              | Х              | Х             | Х              | Х              | Х              |

Table 3. Z8 Encore! F0830 Series Package Options

# **Pin Configurations**

Figures 2 and 3 display the pin configurations of all of the packages available in the Z8 Encore! F0830 Series. See <u>Table 4</u> on page 11 for a description of the signals. Analog input alternate functions (ANAx) are not available on the following devices:

- Z8F0831

- Z8F0431

- Z8F0131

- Z8F0231

- Z8F1233

| Address (Hex)    | Register Description             | Mnemonic | Reset (Hex) | Page No |

|------------------|----------------------------------|----------|-------------|---------|

| Interrupt Contro | oller (cont'd)                   |          |             |         |

| FCE              | Shared interrupt select          | IRQSS    | 00          | 66      |

| FCF              | Interrupt control                | IRQCTL   | 00          | 67      |

| GPIO Port A      |                                  |          |             |         |

| FD0              | Port A address                   | PAADDR   | 00          | 39      |

| FD1              | Port A control                   | PACTL    | 00          | 41      |

| FD2              | Port A input data                | PAIN     | XX          | 41      |

| FD3              | Port A output data               | PAOUT    | 00          | 41      |

| GPIO Port B      |                                  |          |             |         |

| FD4              | Port B address                   | PBADDR   | 00          | 39      |

| FD5              | Port B control                   | PBCTL    | 00          | 41      |

| FD6              | Port B input data                | PBIN     | XX          | 41      |

| FD7              | Port B output data               | PBOUT    | 00          | 41      |

| GPIO Port C      |                                  |          |             |         |

| FD8              | Port C address                   | PCADDR   | 00          | 39      |

| FD9              | Port C control                   | PCCTL    | 00          | 41      |

| FDA              | Port C input data                | PCIN     | XX          | 41      |

| FDB              | Port C output data               | PCOUT    | 00          | 41      |

| GPIO Port D      |                                  |          |             |         |

| FDC              | Port D address                   | PDADDR   | 00          | 39      |

| FDD              | Port D control                   | PDCTL    | 00          | 41      |

| FDE              | Reserved                         |          | XX          |         |

| FDF              | Port D output data               | PDOUT    | 00          | 41      |

| FE0–FEF          | Reserved                         | _        | XX          |         |

| Watchdog Time    | r (WDT)                          |          |             |         |

| FF0              | Reset status                     | RSTSTAT  | XX          | 95      |

|                  | Watchdog Timer control           | WDTCTL   | XX          | 95      |

| FF1              | Watchdog Timer reload upper byte | WDTU     | FF          | 96      |

| FF2              | Watchdog Timer reload high byte  | WDTH     | FF          | 96      |

| FF3              | Watchdog Timer reload low byte   | WDTL     | FF          | 97      |

| FF4–FF5          | Reserved                         |          | XX          |         |

#### Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

| Port                | Pin | Mnemonic         | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------|--------------------------------|-----------------------------------------|

| Port B <sup>2</sup> | PB0 | Reserved         |                                | AFS1[0]: 0                              |

|                     |     | ANA0             | ADC analog input               | AFS1[0]: 1                              |

|                     | PB1 | Reserved         |                                | AFS1[1]: 0                              |

|                     |     | ANA1             | ADC analog input               | AFS1[1]: 1                              |

|                     | PB2 | Reserved         |                                | AFS1[2]: 0                              |

|                     |     | ANA2             | ADC analog input               | AFS1[2]: 1                              |

|                     | PB3 | CLKIN            | External input clock           | AFS1[3]: 0                              |

|                     |     | ANA3             | ADC analog input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved         |                                | AFS1[4]: 0                              |

|                     |     | ANA7             | ADC analog input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved         |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> | ADC reference voltage          | AFS1[5]: 1                              |

|                     | PB6 | Reserved         |                                | AFS1[6]: 0                              |

|                     |     | Reserved         |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved         |                                | AFS1[7]: 0                              |

|                     |     | Reserved         |                                | AFS1[7]: 1                              |

#### Table 16. Port Alternate Function Mapping (Continued)

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

# Interrupt Controller

The Interrupt Controller on the Z8 Encore!<sup>®</sup> F0830 Series products prioritize the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the Interrupt Controller include:

- Seventeen interrupt sources using sixteen unique interrupt vectors:

- Twelve GPIO port pin interrupt sources

- Five on-chip peripheral interrupt sources (Comparator Output interrupt shares one interrupt vector with PA6)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt m

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the Interrupt Controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU User Manual (UM0128)</u>, which is available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 34 lists the interrupts available in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even program memory address and the least significant byte (LSB) at the odd program memory address.

**Note:** Some port interrupts are not available on the 20-pin and 28-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

| Bit                      | 7                                                            | 6                                              | 5            | 4      | 3             | 2      | 1      | 0           |

|--------------------------|--------------------------------------------------------------|------------------------------------------------|--------------|--------|---------------|--------|--------|-------------|

| Field                    | PA7ENL                                                       | PA6CENL                                        | PA5ENL       | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL      |

| RESET                    | 0                                                            | 0                                              | 0            | 0      | 0             | 0      | 0      | 0           |

| R/W                      | R/W                                                          | R/W                                            | R/W          | R/W    | R/W           | R/W    | R/W    | R/W         |

| Address                  |                                                              | •<br>•                                         |              | FC     | 5H            |        |        |             |

| Bit                      | Description                                                  |                                                |              |        |               |        |        |             |

| [7]<br>PA7ENL            | Port A E                                                     | Port A Bit[7] Interrupt Request Enable Low Bit |              |        |               |        |        |             |

| [6]<br>PA6CENL           | Port A Bit[7] or Comparator Interrupt Request Enable Low Bit |                                                |              |        |               |        |        |             |

| [5:0]<br>PA <i>x</i> ENL |                                                              |                                                |              |        |               |        |        | e interrupt |

| Note: x inc              | licates registe                                              | er bits in the a                               | ddress range | e 5–0. |               |        |        |             |

#### Table 43. IRQ1 Enable Low Bit Register (IRQ1ENL)

### **IRQ2 Enable High and Low Bit Registers**

Table 44 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 45 and 46, form a priority-encoded enabling service for interrupts in the Interrupt Request 2 Register. Priority is generated by setting the bits in each register.

| IRQ2ENH[x]                                                  | IRQ2ENL[x] | Priority | Description |  |  |

|-------------------------------------------------------------|------------|----------|-------------|--|--|

| 0                                                           | 0          | Disabled | Disabled    |  |  |

| 0                                                           | 1          | Level 1  | Low         |  |  |

| 1                                                           | 0          | Level 2  | Nominal     |  |  |

| 1                                                           | 1          | Level 3  | High        |  |  |

| Note: $x$ indicates register bits in the address range 7–0. |            |          |             |  |  |

Table 44. IRQ2 Enable and Priority Encoding

| Bit   | Description (Continued)                                                                   |

|-------|-------------------------------------------------------------------------------------------|

| [2:0] | Timer Mode                                                                                |

| TMODE | This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of |

|       | the timer. TMODEHI is the most significant bit of the timer mode selection value.         |

|       | 0000 = ONE-SHOT Mode.                                                                     |

|       | 0001 = CONTINUOUS Mode.                                                                   |

|       | 0010 = COUNTER Mode.                                                                      |

|       | 0011 = PWM SINGLE OUTPUT Mode.                                                            |

|       | 0100 = CAPTURE Mode.                                                                      |

|       | 0101 = COMPARE Mode.                                                                      |

|       | 0110 = GATED Mode.                                                                        |

|       | 0111 = CAPTURE/COMPARE Mode.                                                              |

|       | 1000 = PWM DUAL OUTPUT Mode.                                                              |

|       | 1001 = CAPTURE RESTART Mode.                                                              |

|       | 1010 = COMPARATOR COUNTER Mode.                                                           |

91

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| 1FFFH          |           | <br>Page 15 | 1FFFH<br>1E00H |

|----------------|-----------|-------------|----------------|

|                | Sector 7  | Page 14     | 1DFFH<br>1C00H |

| 1C00H<br>18FFH |           | <br>Page 13 | 1BFFH<br>1A00H |

|                | Sector 6  | <br>Page 12 | 19FFH<br>1800H |

| 1800H<br>17FFH |           | <br>Page 11 | 17FFH<br>1600H |

| 1400H          | Sector 5  | <br>Page 10 | 15FFH<br>1400H |

| 13FFH          |           | <br>Page 9  | 13FFH<br>1200H |

|                | Sector 4  | <br>Page 8  | 11FFH          |

| 1C00H<br>0FFFH | Sector 3  | <br>Page 7  | 1C00H<br>0FFFH |

| 0C00H          | Seciol 3  | Page 6      | 0E00H<br>0DFFH |

| 0BFFH          | On star 0 | <br>Page 5  | 0C00H<br>0BFFH |

| 0800H          | Sector 2  | <br>Page 4  | 0A00H<br>09FFH |

| 07FFH          | Sector 1  | Page 3      | 0800H<br>07FFH |

| 0400H          | Sector    | <br>Page 2  | 0600H<br>05FFH |

| 03FFH          | Sector 0  | Page 1      | 0400H<br>03FFH |

| 0000H          |           | <br>Page 0  | 0200H<br>0100H |

|                |           |             | 0000H          |

Figure 17. 8K Flash with NVDS

110

# **Oscillator Control**

The Z8 Encore! F0830 Series device uses five possible clocking schemes. Each one of these is user-selectable.

- On-chip precision trimmed RC oscillator

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low precision Watchdog Timer Oscillator

In addition, Z8 Encore! F0830 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

### Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined further in this document.

### **System Clock Selection**

The oscillator control block selects from the available clocks. *Table 98* describes each clock source and its usage.

| Bit             | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>POFEN    | <ul> <li>Primary Oscillator Failure Detection Enable</li> <li>1 = Failure detection and recovery of primary oscillator is enabled.</li> <li>0 = Failure detection and recovery of primary oscillator is disabled.</li> </ul>                                                                                                                                                                                                                                     |

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable<br>1 = Failure detection of Watchdog Timer Oscillator is enabled.<br>0 = Failure detection of Watchdog Timer Oscillator is disabled.                                                                                                                                                                                                                                                                          |

| [2:0]<br>SCKSEL | System Clock Oscillator Select<br>000 = Internal Precision Oscillator functions as system clock at 5.53MHz.<br>001 = Internal Precision Oscillator functions as system clock at 32 kHz.<br>010 = Crystal oscillator or external RC oscillator functions as system clock.<br>011 = Watchdog Timer Oscillator functions as system clock.<br>100 = External clock signal on PB3 functions as system clock.<br>101 = Reserved.<br>110 = Reserved.<br>111 = Reserved. |

ister, the user code must wait at least 5000 IPO cycles for the crystal to stabilize. After this period, the crystal oscillator may be selected as the system clock.

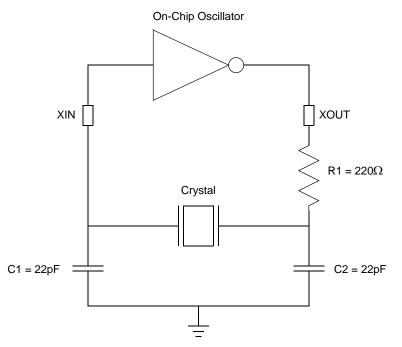

Figure 25 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20MHz. Recommended 20MHz crystal specifications are provided in Table 100. Resistor R<sub>1</sub> is optional and limits total power dissipation by the crystal. Printed circuit board layout must add no more than 4pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

Figure 25. Recommended 20MHz Crystal Oscillator Configuration

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | Ω     | Maximum  |

| Load Capacitance (CL)               | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

| Notation | Description           | Operand | Range                                                                                                                        |

|----------|-----------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| R        | Register              | Reg     | Reg. represents a number in the range of 00H to FFH                                                                          |

| RA       | Relative Address      | Х       | X represents an index in the range of $+127$ to $-128$ which is an offset relative to the address of the next instruction    |

| rr       | Working Register Pair | RRp     | p = 0, 2, 4, 6, 8, 10, 12 or 14                                                                                              |

| RR       | Register Pair         | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                    |

| Vector   | Vector Address        | Vector  | Vector represents a number in the range of 00H to FFH                                                                        |

| Х        | Indexed               | #Index  | The register or register pair to be indexed is off-<br>set by the signed Index value (#Index) in a +127<br>to<br>-128 range. |

#### Table 103. Notational Shorthand (Continued)

Table 104 contains additional symbols that are used throughout the instruction summary and instruction set description sections.

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

#### Table 104. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.  $dst \leftarrow dst + src$

#### 170

#### Table 112. Rotate and Shift Instructions (Continued)

| RRdstRotate RightRRCdstRotate Right through CarrySRAdstShift Right ArithmeticSRLdstShift Right LogicalSWAPdstSwap Nibbles | Mnemonic | Operands | Instruction                |

|---------------------------------------------------------------------------------------------------------------------------|----------|----------|----------------------------|

| SRA     dst     Shift Right Arithmetic       SRL     dst     Shift Right Logical                                          | RR       | dst      | Rotate Right               |

| SRL dst Shift Right Logical                                                                                               | RRC      | dst      | Rotate Right through Carry |

|                                                                                                                           | SRA      | dst      | Shift Right Arithmetic     |

| SWAP dst Swap Nibbles                                                                                                     | SRL      | dst      | Shift Right Logical        |

|                                                                                                                           | SWAP     | dst      | Swap Nibbles               |

| Assembly         |                                                                                           |     | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|------------------|-------------------------------------------------------------------------------------------|-----|-------------|---------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic         | Symbolic Operation                                                                        | dst | src         | (Hex)         | С | Ζ | S   | ۷   | D | Н |         |        |

| AND dst, src     | $dst \gets dst \; AND \; src$                                                             | r   | r           | 52            | _ | * | *   | 0   | _ | _ | 2       | 3      |

|                  |                                                                                           | r   | lr          | 53            | _ |   |     |     |   |   | 2       | 4      |

|                  |                                                                                           | R   | R           | 54            |   |   |     |     |   |   | 3       | 3      |

|                  |                                                                                           | R   | IR          | 55            | _ |   |     |     |   |   | 3       | 4      |

|                  |                                                                                           | R   | IM          | 56            | _ |   |     |     |   |   | 3       | 3      |

|                  |                                                                                           | IR  | IM          | 57            | _ |   |     |     |   |   | 3       | 4      |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER  | ER          | 58            | _ | * | *   | 0   | _ | _ | 4       | 3      |

|                  |                                                                                           | ER  | IM          | 59            | _ |   |     |     |   |   | 4       | 3      |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |     |             | 2F            | - | _ | _   | _   | _ | _ | 1       | 2      |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r   |             | E2            | _ | * | *   | 0   | _ | _ | 2       | 2      |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r   |             | E2            | _ | * | *   | 0   | _ | _ | 2       | 2      |

| BRK              | Debugger Break                                                                            |     |             | 00            | - | _ | -   | -   | _ | _ | 1       | 1      |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r   |             | E2            | - | * | *   | 0   | - | - | 2       | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R   |             | D5            | Х | * | *   | 0   | - | - | 2       | 2      |

| BTJ p, bit, src, | if src[bit] = p                                                                           |     | r           | F6            | - | _ | -   | -   | _ | _ | 3       | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr          | F7            | _ |   |     |     |   |   | 3       | 4      |

| BTJNZ bit, src,  |                                                                                           |     | r           | F6            | - | - | -   | -   | - | - | 3       | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr          | F7            | _ |   |     |     |   |   | 3       | 4      |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |     | r           | F6            | _ | - | _   | _   | - | - | 3       | 3      |

| dst              | $PC \gets PC + X$                                                                         |     | Ir          | F7            |   |   |     |     |   |   | 3       | 4      |

| CALL dst         | $SP \leftarrow SP -\!\!\!\!\!-\!\!\!\!\!2$                                                | IRR |             | D4            | _ | _ | -   | -   | _ | - | 2       | 6      |

|                  | @SP ← PC<br>PC ← dst                                                                      | DA  |             | D6            |   |   |     |     |   |   | 3       | 3      |

| CCF              | $C \leftarrow \sim C$                                                                     |     |             | EF            | * | _ | _   | _   | _ |   | 1       | 2      |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Assembly       |                                     |       | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | Fetch | Instr. |

|----------------|-------------------------------------|-------|-------------|---------------|---|---|-----|-----|---|---|-------|--------|

| Mnemonic       | Symbolic Operation                  | dst   | src         | (Hex)         | С | Ζ | S   | ۷   | D | Н |       |        |

| LDX dst, src   | $dst \gets src$                     | r     | ER          | 84            | _ | _ | _   | _   | - | - | 3     | 2      |

|                |                                     | lr    | ER          | 85            | _ |   |     |     |   |   | 3     | 3      |

|                |                                     | R     | IRR         | 86            | _ |   |     |     |   |   | 3     | 4      |

|                |                                     | IR    | IRR         | 87            | _ |   |     |     |   |   | 3     | 5      |

|                |                                     | r     | X(rr)       | 88            | _ |   |     |     |   |   | 3     | 4      |

|                |                                     | X(rr) | r           | 89            | _ |   |     |     |   |   | 3     | 4      |

|                |                                     | ER    | r           | 94            | _ |   |     |     |   |   | 3     | 2      |

|                |                                     | ER    | lr          | 95            | _ |   |     |     |   |   | 3     | 3      |

|                |                                     | IRR   | R           | 96            | _ |   |     |     |   |   | 3     | 4      |

|                |                                     | IRR   | IR          | 97            | _ |   |     |     |   |   | 3     | 5      |

|                |                                     | ER    | ER          | E8            | _ |   |     |     |   |   | 4     | 2      |

|                |                                     | ER    | IM          | E9            | _ |   |     |     |   |   | 4     | 2      |

| LEA dst, X(src | ) dst ← src + X                     | r     | X(r)        | 98            | _ | - | -   | _   | _ | _ | 3     | 3      |

|                |                                     | rr    | X(rr)       | 99            |   |   |     |     |   |   | 3     | 5      |

| MULT dst       | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR    |             | F4            | - | - | _   | -   | - | - | 2     | 8      |

| NOP            | No operation                        |       |             | 0F            | _ | - | -   | _   | _ | _ | 1     | 2      |

| OR dst, src    | $dst \gets dst \ OR \ src$          | r     | r           | 42            | _ | * | *   | 0   | _ | _ | 2     | 3      |

|                |                                     | r     | lr          | 43            | _ |   |     |     |   |   | 2     | 4      |

|                |                                     | R     | R           | 44            |   |   |     |     |   |   | 3     | 3      |

|                |                                     | R     | IR          | 45            | _ |   |     |     |   |   | 3     | 4      |

|                |                                     | R     | IM          | 46            | - |   |     |     |   |   | 3     | 3      |

|                |                                     | IR    | IM          | 47            | - |   |     |     |   |   | 3     | 4      |

| ORX dst, src   | dst ← dst OR src                    | ER    | ER          | 48            | _ | * | *   | 0   | _ | _ | 4     | 3      |

|                |                                     | ER    | IM          | 49            | - |   |     |     |   |   | 4     | 3      |

| POP dst        | dst ← @SP                           | R     |             | 50            | _ | - | -   | -   | - | - | 2     | 2      |

|                | $SP \leftarrow SP + 1$              | IR    |             | 51            |   |   |     |     |   |   | 2     | 3      |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| Abbreviation | Description                             | Abbreviation                                      | Description            |

|--------------|-----------------------------------------|---------------------------------------------------|------------------------|

| b            | Bit position                            | IRR                                               | Indirect Register Pair |

| CC           | Condition code                          | р                                                 | Polarity (0 or 1)      |

| Х            | 8-bit signed index or displace-<br>ment | r                                                 | 4-bit Working Register |

| DA           | Destination address                     | R                                                 | 8-bit register         |

| ER           | Extended Addressing Register            | r1, R1, Ir1, Irr1,<br>IR1, rr1, RR1,<br>IRR1, ER1 | Destination address    |

| IM           | Immediate data value                    | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address         |

| lr           | Indirect Working Register               | RA                                                | Relative               |

| IR           | Indirect Register                       | rr                                                | Working Register Pair  |

| Irr          | Indirect Working Register Pair          | RR                                                | Register Pair          |

#### Table 114. Op Code Map Abbreviations

|              |                                          | Power Co | onsumption |

|--------------|------------------------------------------|----------|------------|

| Category     | Block                                    | Typical  | Maximum    |

| Logic        | CPU/Peripherals @ 20MHz                  | 5mA      |            |

| Flash        | Flash @20MHz                             |          | 12mA       |

|              | ADC @20MHz                               | 4mA      | 4.5mA      |

|              | IPO                                      | 350µA    | 400µA      |

|              | Comparator @10MHz                        | 330µA    | 450µA      |

| Analog       | POR & VBO                                | 120µA    | 150µA      |

|              | WDT Oscillator                           | 2µA      | ЗµА        |

|              | OSC @ 20MHz                              | 600µA    | 900µA      |

|              | Clock Filter                             | 120µA    | 150µA      |

| Note: The va | lues in this table are subject to change | · · ·    |            |

#### Table 127. Power Consumption Reference Table

Figure 36. Flash Current Diagram

# Low Power Control

For more information about the Power Control Register, see the <u>Power Control Register</u> <u>Definitions</u> section on page 31.

#### Hex Address: F80

| Bit     | 7   | 6        | 5   | 4   | 3        | 2        | 1    | 0        |  |  |

|---------|-----|----------|-----|-----|----------|----------|------|----------|--|--|

| Field   |     | Reserved |     | VBO | Reserved | Reserved | COMP | Reserved |  |  |

| RESET   | 1   | 0        | 0   | 0   | 1        | 0        | 0    | 0        |  |  |

| R/W     | R/W | R/W      | R/W | R/W | R/W      | R/W      | R/W  | R/W      |  |  |

| Address |     | F80H     |     |     |          |          |      |          |  |  |

#### Table 151. Power Control Register 0 (PWRCTL0)

#### Hex Address: F81

This address range is reserved.

# **LED Controller**

For more information about the LED Drive registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

#### Hex Address: F82

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| Field   |     | LEDEN[7:0] |     |     |     |     |     |     |  |  |  |  |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address |     | F82H       |     |     |     |     |     |     |  |  |  |  |

#### Table 152. LED Drive Enable (LEDEN)

# **GPIO Port A**

For more information about the GPIO registers, see the <u>GPIO Control Register Definitions</u> section on page 39.

#### Hex Address: FD0

#### Table 169. Port A GPIO Address Register (PAADDR)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|--|

| Field   |     | PADDR[7:0]                  |   |   |   |   |   |   |  |  |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |  |

| Address |     | FD0H                        |   |   |   |   |   |   |  |  |  |

#### Hex Address: FD1

#### Table 170. Port A Control Registers (PACTL)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|--|

| Field   |     | PCTL                        |   |   |   |   |   |   |  |  |  |

| RESET   |     | 00H                         |   |   |   |   |   |   |  |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |  |

| Address |     | FD1H                        |   |   |   |   |   |   |  |  |  |

#### Hex Address: FD2

#### Table 171. Port A Input Data Registers (PAIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|--|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |  |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |  |  |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |  |  |  |

| Address |      | FD2H |      |      |      |      |      |      |  |  |  |

#### Hex Address: FDB

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | FDBH  |       |       |       |       |       |       |       |

#### Hex Address: FDC

#### Table 181. Port D GPIO Address Register (PDADDR)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PADDR[7:0] |     |     |     |     |     |     |     |

| RESET   | 00H        |     |     |     |     |     |     |     |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FDCH       |     |     |     |     |     |     |     |

#### Hex Address: FDD

#### Table 182. Port D Control Registers (PDCTL)

| Bit     | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|-----|-----|-----|-----|-----|-----|-----|

| Field   | PCTL |     |     |     |     |     |     |     |

| RESET   | 00H  |     |     |     |     |     |     |     |

| R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FDDH |     |     |     |     |     |     |     |

#### Hex Address: FDE

This address range is reserved.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# Index

### **Symbols**

@ 165# 165% 165

### **Numerics**

10-bit ADC 4

### Α

absolute maximum ratings 184 AC characteristics 189 ADC 166 block diagram 99 overview 98 ADC Channel Register 1 (ADCCTL) 102 ADC Data High Byte Register (ADCDH) 103 ADC Data Low Bit Register (ADCDL) 103, 104, 105 **ADCX 166** ADD 166 add - extended addressing 166 add with carry 166 add with carry - extended addressing 166 additional symbols 165 address space 14 **ADDX 166** analog block/PWM signal synchronization 100 analog block/PWM signal zynchronization 100 analog signals 11 analog-to-digital converter overview 98 AND 169 **ANDX 169** architecture voltage measurements 98 arithmetic instructions 166 assembly language programming 162 assembly language syntax 163

### В

B 165 b 164 **BCLR 167** binary number suffix 165 BIT 167 bit 164 clear 167 manipulation instructions 167 set 167 set or clear 167 swap 167 test and jump 169 test and jump if non-zero 169 test and jump if zero 169 bit jump and test if non-zero 166 bit swap 169 block diagram 3 block transfer instructions 167 **BRK 169 BSET 167** BSWAP 167. 169 **BTJ** 169 BTJNZ 166, 169 **BTJZ 169**

# С

calibration and compensation, motor control measurements 101 CALL procedure 169 capture mode 89, 90 capture/compare mode 89 cc 164 CCF 168 characteristics, electrical 184 clear 168 CLR 168 COM 169 compare 89