Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-VQFN                                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0830qj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Reset Controller**

The Z8 Encore! F0830 Series products are reset using any one of the following: the RESET pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP Mode exit or Voltage Brown-Out (VBO) warning signal. The RESET pin is bidirectional; i.e., it functions as a reset source as well as a reset indicator.

# **On-Chip Debugger**

The Z8 Encore! F0830 Series products feature an integrated On-Chip Debugger (OCD). The OCD provides a rich set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. The OCD uses one single-pin interface for communication with an external host.

# **Acronyms and Expansions**

This document references a number of acronyms; each is expanded in Table 2 for the reader's understanding.

| Acronyms | Expansions                       |

|----------|----------------------------------|

| ADC      | Analog-to-Digital Converter      |

| NVDS     | Nonvolatile Data Storage         |

| WDT      | Watchdog Timer                   |

| GPIO     | General-Purpose Input/Output     |

| OCD      | On-Chip Debugger                 |

| POR      | Power-On Reset                   |

| VBO      | Voltage Brown-Out                |

| IPO      | Internal Precision Oscillator    |

| PDIP     | Plastic Dual Inline Package      |

| SOIC     | Small Outline Integrated Circuit |

| SSOP     | Small Shrink Outline Package     |

| QFN      | Quad Flat No Lead                |

| IRQ      | Interrupt request                |

| ISR      | Interrupt service routine        |

| MSB      | Most significant byte            |

| LSB      | Least significant byte           |

| PWM      | Pulse Width Modulation           |

| SAR      | Successive Approximation Regis-  |

|          |                                  |

### Table 2. Acronyms and Expansions

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

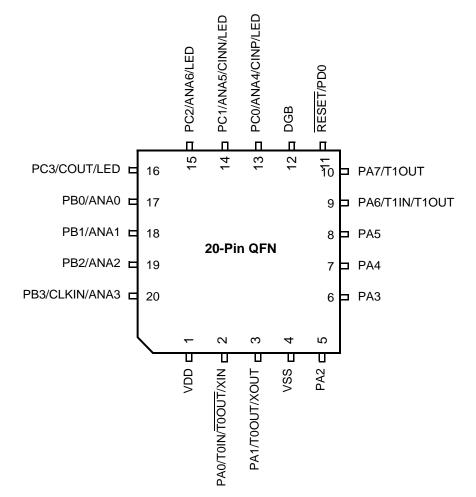

Figure 4. Z8F0830 Series in 20-Pin QFN Package

9

clock and reset signals, the required reset duration may be three or four clock periods. A reset pulse of three clock cycles in duration might trigger a reset and a reset pulse of four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted low, the Z8 Encore! F0830 Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held low beyond the system reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a system reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

## **External Reset Indicator**

During system reset or when enabled by the GPIO logic, the RESET pin functions as an open-drain (active low) RESET mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! F0830 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events. See the <u>Port A–D Control Registers</u> section on page 41.

After an internal Reset event occurs, the internal circuitry begins driving the RESET pin low. The  $\overrightarrow{\text{RESET}}$  pin is held low by the internal circuitry until the appropriate delay listed in <u>Table 9</u> (see page 22) has elapsed.

## **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset, but the remainder of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

# Stop Mode Recovery

The device enters the STOP Mode when the STOP instruction is executed by the eZ8 CPU. See the <u>Low-Power Modes</u> chapter on page 30 for detailed STOP Mode information. During Stop Mode Recovery, the CPU is held in reset for about 66 IPO cycles if the crystal oscillator is disabled or about 5000 cycles if it is enabled.

Stop Mode Recovery does not affect the on-chip registers other than the Reset Status (RSTSTAT) Register and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

### Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the Port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high-output current drive operation. The Port A–D High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit     | 7         | 6            | 5           | 4                         | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------------------|--------------|--------------|--------------|----------|

| Field   | PHDE7     | PHDE6        | PHDE5       | 5 PHDE4 PHDE3 PHDE2 PHDE1 |              |              |              | PHDE0    |

| RESET   | 0         | 0            | 0           | 0                         | 0            | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W                       | R/W          | R/W          | R/W          | R/W      |

| Address | lf 04H ir | n Port A–D A | Address Reg | gister, acces             | sible throug | h the Port A | –D Control F | Register |

### Bit Description

[7:0] Port High Drive Enable

PHDEx 0 = The port pin is configured for standard output current drive.

1 = The port pin is configured for high output current drive.

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–C Input Data Registers

Reading from the Port A–C Input Data registers, shown in Table 29, return the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those not included in the 8- and 28-pin packages, as well as those not included in the ADC-enabled 28-pin packages.

| Bit     | 7    | 6                | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|------------------|------|------|------|------|------|------|--|--|

| Field   | PIN7 | PIN6             | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |

| RESET   | Х    | Х                | Х    | Х    | Х    | Х    | Х    | Х    |  |  |

| R/W     | R    | R                | R    | R    | R    | R    | R    | R    |  |  |

| Address |      | FD2H, FD6H, FDAH |      |      |      |      |      |      |  |  |

|         |      |                  |      |      |      |      |      |      |  |  |

### Table 29. Port A–C Input Data Registers (PxIN)

Bit Description

[7:0] Port Input Data

PxIN Sampled data from the corresponding port pin input. 0 = Input data is logical 0 (Low).

1 =Input data is logical 1 (High).

Note: x indicates the specific GPIO port pin number (7–0).

is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for COUNTER Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COUNTER Mode

- Select either the rising edge or falling edge of the timer input signal for the count. This selection also sets the initial logic level (High or Low) for the timer output alternate function. However, the timer output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer reload in COUNTER Mode, counting always begins at the reset value 0001H. In COUNTER Mode, the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the timer input alternate function.

- 6. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of timer input transitions is calculated with the following equation:

Counter Mode Timer Input Transitions = Current Count Value – Start Value

### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER Mode, the timer counts the input transitions from the analog comparator output. The TPOL bit in the Timer Control Register determines whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPARATOR COUNTER Mode, the prescaler is disabled.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the timer input signal. No interrupt is generated by the first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on Timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the timer low byte register are placed in a holding register. A subsequent read from the timer low byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value when enabled. When the timers are not enabled, a read from the timer low byte register returns the actual value in the counter.

# **Timer Pin Signal Operation**

Timer output is a GPIO port pin alternate function. The timer output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO alternate function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT Mode. For this mode, no timer input is available.

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

# **ADC Interrupt**

The ADC can generate an interrupt request when a conversion has been completed. An interrupt request that is pending when the ADC is disabled is not cleared automatically.

# **Reference Buffer**

The reference buffer, RBUF, supplies the reference voltage for the ADC. When enabled, the internal voltage reference generator supplies the ADC. When RBUF is disabled, the ADC must have the reference voltage supplied externally through the  $V_{REF}$  pin in 28-pin package. RBUF is controlled by the REFEN bit in the ADC Control Register.

# **Internal Voltage Reference Generator**

The internal voltage reference generator provides the voltage VR2, for the RBUF. VR2 is 2V.

# **Calibration and Compensation**

A user can perform calibration and store the values into Flash or the user code can perform a manual offset calibration. There is no provision for manual gain calibration.

# **ADC Control Register Definitions**

The ADC Control registers are defined in this section.

- The Flash Sector Protect Register is ignored for programming and Erase operations.

- Programming operations are not limited to the page selected in the page select register.

- Bits in the Flash Sector Protect Register can be written to one or zero.

- The second write of the page select register to unlock the Flash Controller is not necessary.

- The page select register can be written when the Flash Controller is unlocked.

- The mass erase command is enabled through the Flash Control Register

**Caution:** For security reasons, Flash Controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the Flash Controller must go through the unlock sequence again to select another page.

# **NVDS Operational Requirements**

The device uses a 12KB Flash memory space, despite the maximum specified Flash size of 8KB (with the exception of 12KB mode with non-NVDS). User code accesses the lower 8KB of Flash, leaving the upper 4KB for proprietary (for Zilog-only) memory. The NVDS is implemented by using this proprietary memory space for special-purpose routines and for the data required by these routines, which are factory-programmed and cannot be altered by the user. The NVDS operation is described in detail in *the* <u>Nonvolatile</u> <u>Data Storage</u> *chapter on page 134*.

The NVDS routines are triggered by a user code: CALL into proprietary memory. Code executing from this proprietary memory must be able to read and write other locations within proprietary memory. User code must not be able to read or write proprietary memory.

# **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 119

Flash Status Register: see page 120

Flash Page Select Register: see page 121

Flash Sector Protect Register: see page 122

Flash Frequency High and Low Byte Registers: see page 123

130

### Table 83. Trim Bit Address Space

| Address | Function                      |

|---------|-------------------------------|

| 00h     | ADC reference voltage         |

| 01h     | ADC and comparator            |

| 02h     | Internal Precision Oscillator |

| 03h     | Oscillator and VBO            |

| 06h     | ClkFltr                       |

### Table 84. Trim Option Bits at 0000H (ADCREF)

| Bit       | 7                                               | 6  | 5         | 4        | 3 | 2   | 0 |  |  |  |

|-----------|-------------------------------------------------|----|-----------|----------|---|-----|---|--|--|--|

| Field     |                                                 | Al | DCREF_TRI | Reserved |   |     |   |  |  |  |

| RESET     |                                                 |    | U         |          |   | U   |   |  |  |  |

| R/W       |                                                 |    | R/W       |          |   | R/W |   |  |  |  |

| Address   | Information Page Memory 0020H                   |    |           |          |   |     |   |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |    |           |          |   |     |   |  |  |  |

| Bit                  | Description                                                                          |

|----------------------|--------------------------------------------------------------------------------------|

| [7:3]<br>ADCREF_TRIM | ADC Reference Voltage Trim Byte<br>Contains trimming bits for ADC reference voltage. |

| [2:0]                | <b>Reserved</b><br>These bits are reserved and must be programmed to 111.            |

**Note:** The bit values used in Table 84 are set at the factory; no calibration is required.

| Bit       | 7           | 6             | 5             | 4           | 3           | 2    | 1   | 0   |  |  |  |

|-----------|-------------|---------------|---------------|-------------|-------------|------|-----|-----|--|--|--|

| Field     | Reserved    |               |               |             |             |      |     |     |  |  |  |

| RESET     | U           | U             | U             | U           | U           | U    | U   | U   |  |  |  |

| R/W       | R/W         | R/W           | R/W           | R/W         | R/W         | R/W  | R/W | R/W |  |  |  |

| Address   |             |               | Infor         | mation Page | e Memory 00 | 021H |     |     |  |  |  |

| Note: U = | Unchanged b | by Reset. R/W | / = Read/Writ | te.         |             |      |     |     |  |  |  |

| Bit       | De          | scription     |               |             |             |      |     |     |  |  |  |

### Table 85. Trim Option Bits at 0001H (TADC\_COMP)

| Bit   | Description                                                      |

|-------|------------------------------------------------------------------|

| [7:0] | Reserved                                                         |

|       | Altering this register may result in incorrect device operation. |

# Operation

The following section describes the operation of the On-Chip Debugging function.

# **OCD** Interface

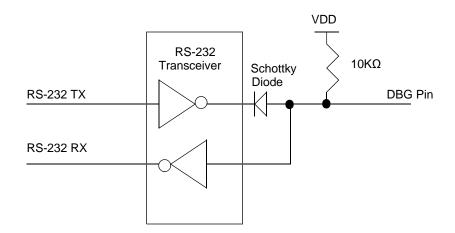

The On-Chip Debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, which means that transmission and data retrieval cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface between the Z8 Encore! F0830 Series products and the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figures 21 and 22. The recommended method is the buffered implementation depicted in Figure 22. The DBG pin must always be connected to  $V_{DD}$  through an external pull-up resistor.

**Caution:** For proper operation of the On-Chip Debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

### Figure 21. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

If the OCD receives a serial break (nine or more continuous bits low), the autobaud detector/generator resets. Reconfigure the autobaud detector/generator by sending 80H.

## **OCD Serial Errors**

The OCD can detect any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received Stop bit is Low)

- Transmit collision (simultaneous transmission by OCD and host detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long serial break back to the host and resets the autobaud detector/generator. A framing error or transmit collision may be caused by the host sending a serial break to the OCD. As a result of the open-drain nature of the interface, returning a serial break back to the host only extends the length of the serial break if the host releases the serial break early.

The host transmits a serial break on the DBG pin when first connecting to the Z8 Encore! F0830 Series devices or when recovering from an error. A serial break from the host resets the autobaud generator/detector, but does not reset the OCD Control Register. A serial break leaves the device in DEBUG Mode, if that is the current mode. The OCD is held in reset until the end of the serial break when the DBG pin returns high. Because of the opendrain nature of the DBG pin, the host can send a serial break to the OCD even if the OCD is transmitting a character.

## **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

| Assembly      |                          |      | ress<br>ode | Op<br>_ Code(s) |   |   | Fla | ags |   |   | Fetch | Instr. |

|---------------|--------------------------|------|-------------|-----------------|---|---|-----|-----|---|---|-------|--------|

| Mnemonic      | Symbolic Operation       | dst  | src         | (Hex)           | С | Ζ | S   | ۷   | D | Н |       |        |

| LD dst, rc    | dst ← src                | r    | IM          | 0C-FC           | _ | - | -   | _   | - | _ | 2     | 2      |

|               |                          | r    | X(r)        | C7              | _ |   |     |     |   |   | 3     | 3      |

|               |                          | X(r) | r           | D7              | _ |   |     |     |   |   | 3     | 4      |

|               |                          | r    | lr          | E3              | _ |   |     |     |   |   | 2     | 3      |

|               |                          | R    | R           | E4              | _ |   |     |     |   |   | 3     | 2      |

|               |                          | R    | IR          | E5              | _ |   |     |     |   |   | 3     | 4      |

|               |                          | R    | IM          | E6              | _ |   |     |     |   |   | 3     | 2      |

|               |                          | IR   | IM          | E7              | _ |   |     |     |   |   | 3     | 3      |

|               |                          | lr   | r           | F3              | _ |   |     |     |   |   | 2     | 3      |

|               |                          | IR   | R           | F5              | _ |   |     |     |   |   | 3     | 3      |

| LDC dst, src  | dst ← src                | r    | Irr         | C2              | _ | _ | _   | _   | _ | _ | 2     | 5      |

|               |                          | lr   | Irr         | C5              | _ |   |     |     |   |   | 2     | 9      |

|               |                          | Irr  | r           | D2              | _ |   |     |     |   |   | 2     | 5      |

| LDCI dst, src | dst ← src                | lr   | Irr         | C3              | - | - | -   | -   | - | - | 2     | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | D3              |   |   |     |     |   |   | 2     | 9      |

| LDE dst, src  | dst ← src                | r    | Irr         | 82              | _ | _ | _   | _   | _ | - | 2     | 5      |

|               |                          | Irr  | r           | 92              | _ |   |     |     |   |   | 2     | 5      |

| LDEI dst, src | dst ← src                | lr   | Irr         | 83              | _ | _ | _   | _   | _ | _ | 2     | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | 93              |   |   |     |     |   |   | 2     | 9      |

| LDWX dst, src | dst ← src                | ER   | ER          | 1FE8            | - | _ | _   | _   | _ | _ | 5     | 4      |

### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

Z8 Encore!<sup>®</sup> F0830 Series Product Specification

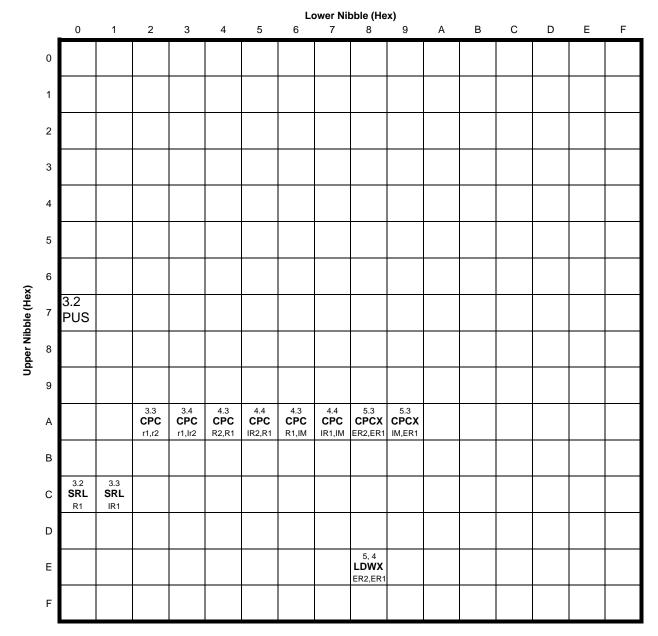

Figure 30. Second Op Code Map after 1FH

183

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F0830 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 115 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                      | Minimum | Maximum | Units | Notes |

|----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                 | 0       | +105    | °C    |       |

| Storage temperature                                            | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>             | -0.3    | +5.5    | V     |       |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$               | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin            | -5      | +5      | μA    |       |

| Maximum output current from active output pin                  | -25     | +25     | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$               |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                 |         |         |       |       |

| Total power dissipation                                        |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub> |         | 125     | mA    |       |

### **Table 115. Absolute Maximum Ratings**

### Hex Address: F01

### Table 131. Timer 0 Low Byte Register (T0L)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     |      |     | Т   | Ľ   |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 1   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F01H |     |     |     |     |     |     |  |

### Hex Address: F02

### Table 132. Timer 0 Reload High Byte Register (T0RH)

| Bit     | 7   | 6               | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     |                 |     | TF  | RH  |     |     |     |  |  |

| RESET   | 1   | 1 1 1 1 1 1 1 1 |     |     |     |     |     |     |  |  |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F02H            |     |     |     |     |     |     |  |  |

## Hex Address: F03

### Table 133. Timer 0 Reload Low Byte Register (T0RL)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | TRL                         |   |   |   |   |   |   |  |  |

| RESET   | 1   | 1 1 1 1 1 1 1 1             |   |   |   |   |   |   |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | F03H                        |   |   |   |   |   |   |  |  |

### Hex Address: F04

### Table 134. Timer 0 PWM High Byte Register (T0PWMH)

| Bit     | 7   | 6               | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | PWMH            |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0 0 0 0 0 0 0 0 |     |     |     |     |     |     |  |  |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F04H            |     |     |     |     |     |     |  |  |

### Hex Address: F09

### Table 139. Timer 1 Low Byte Register (T1L)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | TL   |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 1   |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F09H |     |     |     |     |     |     |  |  |

### Hex Address: F0A

### Table 140. Timer 1 Reload High Byte Register (T1RH)

| Bit     | 7   | 6               | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     |                 |     | TF  | RH  |     |     |     |  |  |

| RESET   | 1   | 1 1 1 1 1 1 1 1 |     |     |     |     |     |     |  |  |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | FOAH            |     |     |     |     |     |     |  |  |

## Hex Address: F0B

### Table 141. Timer 1 Reload Low Byte Register (T1RL)

| Bit     | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |     | TRL                         |   |   |   |   |   |   |  |  |

| RESET   | 1   | 1 1 1 1 1 1 1 1             |   |   |   |   |   |   |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address |     | FOBH                        |   |   |   |   |   |   |  |  |

### Hex Address: F0C

### Table 142. Timer 1 PWM High Byte Register (T1PWMH)

| Bit     | 7   | 6               | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|-----------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | PWMH            |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0 0 0 0 0 0 0 0 |     |     |     |     |     |     |  |  |

| R/W     | R/W | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | FOCH            |     |     |     |     |     |     |  |  |

### Hex Address: F83

### Table 153. LED Drive Level High Register (LEDLVLH)

| Bit     | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | LEDLVLH[7:0] |     |     |     |     |     |     |  |

| RESET   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F83H         |     |     |     |     |     |     |  |

### Hex Address: F84

### Table 154. LED Drive Level Low Register (LEDLVLL)

| Bit     | 7   | 6               | 5   | 4     | 3       | 2   | 1   | 0   |  |  |

|---------|-----|-----------------|-----|-------|---------|-----|-----|-----|--|--|

| Field   |     |                 |     | LEDLV | LL[7:0] |     |     |     |  |  |

| RESET   | 0   | 0 0 0 0 0 0 0 0 |     |       |         |     |     |     |  |  |

| R/W     | R/W | R/W             | R/W | R/W   | R/W     | R/W | R/W | R/W |  |  |

| Address |     | F84H            |     |       |         |     |     |     |  |  |

### Hex Address: F85

This address range is reserved.

# **Oscillator Control**

For more information about the Oscillator Control registers, see the <u>Oscillator Control</u> <u>Register Definitions</u> section on page 154.

### Hex Address: F86

| Table 155. | Oscillator | Control | Register | (OSCCTL) |

|------------|------------|---------|----------|----------|

|------------|------------|---------|----------|----------|

| Bit     | 7     | 6     | 5     | 4     | 3     | 2   | 1      | 0   |  |  |

|---------|-------|-------|-------|-------|-------|-----|--------|-----|--|--|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN |     | SCKSEL |     |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0   | 0      | 0   |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W | R/W    | R/W |  |  |

| Address |       | F86H  |       |       |       |     |        |     |  |  |

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

JP 169 LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167 LDX 168 LEA 168 load 168 logical 169 **MULT 167 NOP 168** OR 169 ORX 169 POP 168 **POPX 168** program control 169 **PUSH 168** PUSHX 168 RCF 167, 168 **RET 169** RL 169 **RLC 169** rotate and shift 169 RR 170 **RRC** 170 **SBC 167** SCF 167. 168 **SRA 170 SRL 170 SRP 168 STOP 168 SUB 167 SUBX 167 SWAP 170** TCM 167 **TCMX 167** TM 167 TMX 167 **TRAP 169** watch-dog timer refresh 168 XOR 169 **XORX 169** instructions, eZ8 classes of 166

interrupt control register 67 interrupt controller 53 architecture 53 interrupt assertion types 56 interrupt vectors and priority 56 operation 55 register definitions 57 software interrupt assertion 57 interrupt edge select register 65 interrupt request 0 register 58 interrupt request 1 register 59 interrupt request 2 register 60 interrupt return 169 interrupt vector listing 53 IR 164 Ir 164 **IRET 169** IRQ0 enable high and low bit registers 60 IRQ1 enable high and low bit registers 62 IRQ2 enable high and low bit registers 63 **IRR 164** Irr 164

## J

JP 169 jump, conditional, relative, and relative conditional 169

## L

LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167, 168 LDX 168 LEA 168 load constant 167 load constant to/from program memory 168 load constant with auto-increment addresses 168 load effective address 168 load external data 168