# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0830sh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

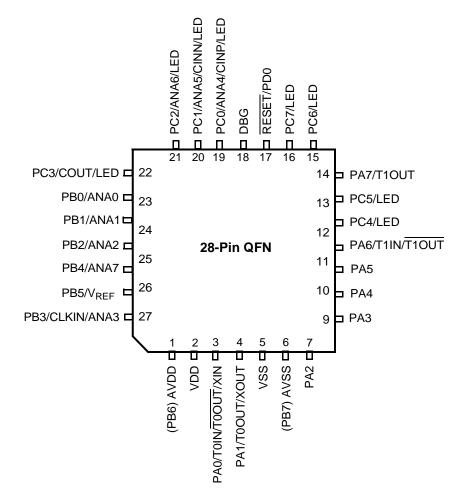

Figure 5. Z8F0830 Series in 28-Pin QFN Package

10

# **Data Memory**

The Z8 Encore! F0830 Series does not use the eZ8 CPU's 64KB data memory address space.

# **Flash Information Area**

Table 7 maps the Z8 Encore! F0830 Series Flash information area. The 128-byte information area is accessed, by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash information area is mapped into program memory and overlays these 128 bytes at addresses FE00H to FE7FH. When information area access is enabled, all reads from these program memory addresses return information area data rather than program memory data. Access to the Flash information area is read-only.

| Program<br>Memory<br>Address (Hex) | Function                                                                                 |

|------------------------------------|------------------------------------------------------------------------------------------|

| FE00–FE3F                          | Zilog option bits                                                                        |

| FE40-FE53                          | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH |

| FE54–FE5F                          | Reserved                                                                                 |

| FE60–FE7F                          | Reserved                                                                                 |

| FE80–FFFF                          | Reserved                                                                                 |

#### Table 7. Z8 Encore! F0830 Series Flash Memory Information Area Map

| Address (Hex)    | Register Description             | Mnemonic | Reset (Hex) | Page No |

|------------------|----------------------------------|----------|-------------|---------|

| Interrupt Contro | oller (cont'd)                   |          |             |         |

| FCE              | Shared interrupt select          | IRQSS    | 00          | 66      |

| FCF              | Interrupt control                | IRQCTL   | 00          | 67      |

| GPIO Port A      |                                  |          |             |         |

| FD0              | Port A address                   | PAADDR   | 00          | 39      |

| FD1              | Port A control                   | PACTL    | 00          | 41      |

| FD2              | Port A input data                | PAIN     | XX          | 41      |

| FD3              | Port A output data               | PAOUT    | 00          | 41      |

| GPIO Port B      |                                  |          |             |         |

| FD4              | Port B address                   | PBADDR   | 00          | 39      |

| FD5              | Port B control                   | PBCTL    | 00          | 41      |

| FD6              | Port B input data                | PBIN     | XX          | 41      |

| FD7              | Port B output data               | PBOUT    | 00          | 41      |

| GPIO Port C      |                                  |          |             |         |

| FD8              | Port C address                   | PCADDR   | 00          | 39      |

| FD9              | Port C control                   | PCCTL    | 00          | 41      |

| FDA              | Port C input data                | PCIN     | XX          | 41      |

| FDB              | Port C output data               | PCOUT    | 00          | 41      |

| GPIO Port D      |                                  |          |             |         |

| FDC              | Port D address                   | PDADDR   | 00          | 39      |

| FDD              | Port D control                   | PDCTL    | 00          | 41      |

| FDE              | Reserved                         |          | XX          |         |

| FDF              | Port D output data               | PDOUT    | 00          | 41      |

| FE0–FEF          | Reserved                         | _        | XX          |         |

| Watchdog Time    | r (WDT)                          |          |             |         |

| FF0              | Reset status                     | RSTSTAT  | XX          | 95      |

|                  | Watchdog Timer control           | WDTCTL   | XX          | 95      |

| FF1              | Watchdog Timer reload upper byte | WDTU     | FF          | 96      |

| FF2              | Watchdog Timer reload high byte  | WDTH     | FF          | 96      |

| FF3              | Watchdog Timer reload low byte   | WDTL     | FF          | 97      |

| FF4–FF5          | Reserved                         |          | XX          |         |

### Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

clock and reset signals, the required reset duration may be three or four clock periods. A reset pulse of three clock cycles in duration might trigger a reset and a reset pulse of four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted low, the Z8 Encore! F0830 Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held low beyond the system reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a system reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

### **External Reset Indicator**

During system reset or when enabled by the GPIO logic, the RESET pin functions as an open-drain (active low) RESET mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! F0830 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events. See the <u>Port A–D Control Registers</u> section on page 41.

After an internal Reset event occurs, the internal circuitry begins driving the RESET pin low. The  $\overrightarrow{\text{RESET}}$  pin is held low by the internal circuitry until the appropriate delay listed in <u>Table 9</u> (see page 22) has elapsed.

# **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset, but the remainder of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

# Stop Mode Recovery

The device enters the STOP Mode when the STOP instruction is executed by the eZ8 CPU. See the <u>Low-Power Modes</u> chapter on page 30 for detailed STOP Mode information. During Stop Mode Recovery, the CPU is held in reset for about 66 IPO cycles if the crystal oscillator is disabled or about 5000 cycles if it is enabled.

Stop Mode Recovery does not affect the on-chip registers other than the Reset Status (RSTSTAT) Register and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

# Port A–D Address Registers

The Port A–D Address registers select the GPIO port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO port controls; see Tables 18 and 19.

| <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W | Bit     | 7                      | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------------|---------|------------------------|------------|-----|-----|-----|-----|-----|-----|

| <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W | Field   |                        | PADDR[7:0] |     |     |     |     |     |     |

|                                        | RESET   |                        | 00H        |     |     |     |     |     |     |

| Address FD0H, FD4H, FD8H, FDCH         | R/W     | R/W                    | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

|                                        | Address | FD0H, FD4H, FD8H, FDCH |            |     |     |     |     |     |     |

### Table 18. Port A–D GPIO Address Registers (PxADDR)

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The port address selects one of the subregisters accessible through the Port Control Register. |

### Table 19. Port Control Subregister Access

| PADDR[7:0] | Port Control Subregister accessible using the Port A–D Control registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental port reconfiguration. |

| 01H        | Data Direction                                                                 |

| 02H        | Alternate Function                                                             |

| 03H        | Output Control (open-drain)                                                    |

| 04H        | High Drive Enable                                                              |

| 05H        | Stop Mode Recovery Source Enable                                               |

| 06H        | Pull-Up Enable                                                                 |

| 07H        | Alternate Function Set 1                                                       |

| 08H        | Alternate Function Set 2                                                       |

| 09H–FFH    | No function                                                                    |

# LED Drive Enable Register

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7    | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|---------|------|-----|-----|------|--------|-----|-----|-----|

| Field   |      |     |     | LEDE | N[7:0] |     |     |     |

| RESET   | 0    | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

| R/W     | R/W  | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Address | F82H |     |     |      |        |     |     |     |

| Bit   | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | LED Drive Enable                                                                                                                                                           |

| LEDEN | These bits determine which Port C pins are connected to an internal current sink.<br>0 = Tristate the Port C pin.<br>1= Connect controlled current sink to the Port C pin. |

# LED Drive Level High Register

The LED Drive Level High Register, shown in Table 32, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|--------------|-----|-----|-----|-----|-----|-----|

| Field   |     | LEDLVLH[7:0] |     |     |     |     |     |     |

| RESET   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F83H         |     |     |     |     |     |     |

#### Bit Description

[7:0] LED Level High Bits

LEDLVLH {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3mA.

01= 7 mA.

10= 13mA.

11= 20mA.

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the timer output Alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the timer output function) for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

Continuous Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

# **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin: timer input alternate function. The TPOL bit in the Timer Control Register determines whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Additionally, if the timer output alternate function

| Bit    | Description (Continued)                                                                                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0]    | Input Capture Event                                                                                                                                                        |

| INPCAP | This bit indicates whether the most recent timer interrupt is caused by a timer input capture event.                                                                       |

|        | <ul> <li>0 = Previous timer interrupt is not caused by timer input capture event.</li> <li>1 = Previous timer interrupt is caused by timer input capture event.</li> </ul> |

### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

| Bit     | 7          | 6    | 5    | 4   | 3   | 2     | 1   | 0   |

|---------|------------|------|------|-----|-----|-------|-----|-----|

| Field   | TEN        | TPOL | PRES |     |     | TMODE |     |     |

| RESET   | 0          | 0    | 0    | 0   | 0   | 0     | 0   | 0   |

| R/W     | R/W        | R/W  | R/W  | R/W | R/W | R/W   | R/W | R/W |

| Address | F07H, F0FH |      |      |     |     |       |     |     |

| Bit | Description                                           |

|-----|-------------------------------------------------------|

| [7] | Timer Enable                                          |

| TEN | 0 = Timer is disabled.<br>1 = Timer enabled to count. |

# Watchdog Timer Refresh

Upon first enable, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the Reload operation.

When the Z8 Encore! F0830 Series devices are operating in DEBUG Mode (using the On-Chip Debugger), the Watchdog Timer must be continuously refreshed to prevent any WDT time-outs.

# Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash option bit determines the time-out response of the Watchdog Timer. See *the* <u>Flash Option</u> <u>Bits</u> chapter on page 124 for information about programming the WDT\_RES Flash option bit.

### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the Interrupt Controller and sets the WDT status bit in the Reset Status Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter resets to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter will not automatically return to its reload value.

The Reset Status Register (see <u>Table 12</u> on page 29) must be read before clearing the WDT interrupt. This read clears the WDT time-out flag and prevents further WDT interrupts occurring immediately.

### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! F0830 Series devices are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control Register are set to 1 following a WDT time-out in STOP Mode. See *the* <u>Reset and Stop Mode Recovery</u> *chapter on page 21* for more information about Stop Mode Recovery operations.

If interrupts are enabled, following completion of the Stop Mode Recovery, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executes the code from the vector address.

#### 96

# Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 60 through 62, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. This 24-bit value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate reload value; reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Field                                                                                         | WDTU |      |      |      |      |      |      |      |

| RESET                                                                                         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W                                                                                           | R/W* |

| Address                                                                                       | FF1H |      |      |      |      |      |      |      |

| Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |      |

#### Table 60. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

| Bit                                                                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|--|

| Field                                                                                         |      | WDTH |      |      |      |      |      |      |  |

| RESET                                                                                         | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    |  |

| R/W                                                                                           | R/W* |  |

| Address                                                                                       | FF2H |      |      |      |      |      |      |      |  |

| Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |      |  |

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte, bits[15:8] of the 24-bit WDT reload value. |

# ADC Data High Byte Register

The ADC Data High Byte Register, listed in Table 64, contains the upper eight bits of the ADC output. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

#### Table 64. ADC Data High Byte Register (ADCD\_H)

| Bit     | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|-------|---|---|---|---|---|---|---|--|

| Field   | ADCDH |   |   |   |   |   |   |   |  |

| RESET   | Х     |   |   |   |   |   |   |   |  |

| R/W     | R     |   |   |   |   |   |   |   |  |

| Address | F72H  |   |   |   |   |   |   |   |  |

|         |       |   |   |   |   |   |   |   |  |

| Bit   | Description                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------|

| [7:0] | ADC High Byte                                                                                                       |

| ADCDH | 00h–FFh = The last conversion output is held in the data registers until the next ADC conver-<br>sion is completed. |

# ADC Data Low Bits Register

The ADC Data Low Bits Register, shown in Table 65, contains the lower bits of the ADC output. Access to the ADC Data Low Bits Register is read-only. Reading the ADC Data High Byte Register latches lower bits of the ADC in the ADC Data Low Bits Register.

| Bit     | 7    | 6   | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|-----|----------|---|---|---|---|---|--|--|

| Field   | ADO  | CDL | Reserved |   |   |   |   |   |  |  |

| RESET   | Х    |     | Х        |   |   |   |   |   |  |  |

| R/W     | F    | R R |          |   |   |   |   |   |  |  |

| Address | F73H |     |          |   |   |   |   |   |  |  |

| Table 65. | ADC Data L | ow Bits R | Register (A | ADCD_L) |

|-----------|------------|-----------|-------------|---------|

|-----------|------------|-----------|-------------|---------|

| Bit            | Description                                                                                                                                                                                                                                  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]<br>ADCDL | ADC Low Bits<br>00–11b = These bits are the two least-significant bits of the 10-bit ADC output. These bits are<br>undefined after a reset. The low bits are latched into this register whenever the ADC Data High<br>Byte Register is read. |

| [5:0]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                 |

### 170

### Table 112. Rotate and Shift Instructions (Continued)

| RRdstRotate RightRRCdstRotate Right through CarrySRAdstShift Right ArithmeticSRLdstShift Right LogicalSWAPdstSwap Nibbles | Mnemonic | Operands | Instruction                |

|---------------------------------------------------------------------------------------------------------------------------|----------|----------|----------------------------|

| SRA     dst     Shift Right Arithmetic       SRL     dst     Shift Right Logical                                          | RR       | dst      | Rotate Right               |

| SRL dst Shift Right Logical                                                                                               | RRC      | dst      | Rotate Right through Carry |

|                                                                                                                           | SRA      | dst      | Shift Right Arithmetic     |

| SWAP dst Swap Nibbles                                                                                                     | SRL      | dst      | Shift Right Logical        |

|                                                                                                                           | SWAP     | dst      | Swap Nibbles               |

| Assembly      |                              |     | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | Fetch<br>Cycles | Instr.<br>Cycles |

|---------------|------------------------------|-----|-------------|---------------|---|---|-----|-----|---|---|-----------------|------------------|

| Mnemonic      | Symbolic Operation           | dst | src         | (Hex)         | С | Ζ | S   | ۷   | D | Н |                 |                  |

| CLR dst       | dst ← 00H                    | R   |             | B0            | _ | _ | _   | -   | _ | - | 2               | 2                |

|               |                              | IR  |             | B1            | _ |   |     |     |   |   | 2               | 3                |

| COM dst       | dst ← ~dst                   | R   |             | 60            | - | * | *   | 0   | - | - | 2               | 2                |

|               |                              | IR  |             | 61            | _ |   |     |     |   |   | 2               | 3                |

| CP dst, src   | dst - src                    | r   | r           | A2            | * | * | *   | *   | - | - | 2               | 3                |

|               |                              | r   | lr          | A3            | _ |   |     |     |   |   | 2               | 4                |

|               |                              | R   | R           | A4            | _ |   |     |     |   |   | 3               | 3                |

|               |                              | R   | IR          | A5            | _ |   |     |     |   |   | 3               | 4                |

|               |                              | R   | IM          | A6            | _ |   |     |     |   |   | 3               | 3                |

|               |                              | IR  | IM          | A7            | _ |   |     |     |   |   | 3               | 4                |

| CPC dst, src  | dst - src - C                | r   | r           | 1F A2         | * | * | *   | *   | - | - | 3               | 3                |

|               |                              | r   | lr          | 1F A3         | _ |   |     |     |   |   | 3               | 4                |

|               |                              | R   | R           | 1F A4         | _ |   |     |     |   |   | 4               | 3                |

|               |                              | R   | IR          | 1F A5         | _ |   |     |     |   |   | 4               | 4                |

|               |                              | R   | IM          | 1F A6         | _ |   |     |     |   |   | 4               | 3                |

|               |                              | IR  | IM          | 1F A7         | _ |   |     |     |   |   | 4               | 4                |

| CPCX dst, src | dst - src - C                | ER  | ER          | 1F A8         | * | * | *   | *   | _ | _ | 5               | 3                |

|               |                              | ER  | IM          | 1F A9         | _ |   |     |     |   |   | 5               | 3                |

| CPX dst, src  | dst - src                    | ER  | ER          | A8            | * | * | *   | *   | - | - | 4               | 3                |

|               |                              | ER  | IM          | A9            | _ |   |     |     |   |   | 4               | 3                |

| DA dst        | dst ← DA(dst)                | R   |             | 40            | * | * | *   | Х   | - | - | 2               | 2                |

|               |                              | IR  |             | 41            | _ |   |     |     |   |   | 2               | 3                |

| DEC dst       | $dst \gets dst \text{ - } 1$ | R   |             | 30            | _ | * | *   | *   | _ | _ | 2               | 2                |

|               |                              | IR  |             | 31            | _ |   |     |     |   |   | 2               | 3                |

| DECW dst      | dst ← dst - 1                | RR  |             | 80            | _ | * | *   | *   | - | _ | 2               | 5                |

|               |                              | IRR |             | 81            | _ |   |     |     |   |   | 2               | 6                |

| DI            | IRQCTL[7] ← 0                |     |             | 8F            | _ | _ | _   | _   | _ | _ | 1               | 2                |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| Assembly      |                                                                          |         | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | Fetch  | Instr. |

|---------------|--------------------------------------------------------------------------|---------|-------------|---------------|---|---|-----|-----|---|---|--------|--------|

| Mnemonic      | Symbolic Operation                                                       | dst src |             | (Hex)         | С | Ζ | S   | ۷   | D | Н | Cycles |        |

| POPX dst      | dst $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 1                           | ER      |             | D8            | - | _ | _   | -   | - | _ | 3      | 2      |

| PUSH src      | $SP \leftarrow SP - 1$                                                   | R       |             | 70            | - | - | _   | -   | - | - | 2      | 2      |

|               | $@SP \leftarrow src$                                                     | IR      |             | 71            | - |   |     |     |   |   | 2      | 3      |

|               | -                                                                        | IM      |             | IF70          | - |   |     |     |   |   | 3      | 2      |

| PUSHX src     | $SP \leftarrow SP - 1$<br>@SP ← src                                      | ER      |             | C8            | _ | - | -   | _   | _ | - | 3      | 2      |

| RCF           | C ← 0                                                                    |         |             | CF            | 0 | - | -   | -   | _ | - | 1      | 2      |

| RET           | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |         |             | AF            | - | - | -   | -   | - | - | 1      | 4      |

| RL dst        |                                                                          | R       |             | 90            | * | * | *   | *   | _ | - | 2      | 2      |

|               | C                                                                        | IR      |             | 91            | - |   |     |     |   |   | 2      | 3      |

| RLC dst       |                                                                          | R       |             | 10            | * | * | *   | *   | - | _ | 2      | 2      |

|               | C D7 D6 D5 D4 D3 D2 D1 D0 dst                                            | IR      |             | 11            | _ |   |     |     |   |   | 2      | 3      |

| RR dst        |                                                                          | R       |             | E0            | * | * | *   | *   | - | _ | 2      | 2      |

|               | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                                     | IR      |             | E1            | _ |   |     |     |   |   | 2      | 3      |

| RRC dst       |                                                                          | R       |             | C0            | * | * | *   | *   | - | - | 2      | 2      |

|               | ► D7D6D5D4D3D2D1D0 ► C                                                   | IR      |             | C1            |   |   |     |     |   |   | 2      | 3      |

| SBC dst, src  | $dst \gets dst - src - C$                                                | r       | r           | 32            | * | * | *   | *   | 1 | * | 2      | 3      |

|               | -                                                                        | r       | lr          | 33            |   |   |     |     |   |   | 2      | 4      |

|               | -                                                                        | R       | R           | 34            |   |   |     |     |   |   | 3      | 3      |

|               | -                                                                        | R       | IR          | 35            | _ |   |     |     |   |   | 3      | 4      |

|               | -                                                                        | R       | IM          | 36            | _ |   |     |     |   |   | 3      | 3      |

|               | -                                                                        | IR      | IM          | 37            | _ |   |     |     |   |   | 3      | 4      |

| SBCX dst, src | $dst \gets dst - src - C$                                                | ER      | ER          | 38            | * | * | *   | *   | 1 | * | 4      | 3      |

|               | -                                                                        | ER      | IM          | 39            | _ |   |     |     |   |   | 4      | 3      |

| SCF           | C ← 1                                                                    |         |             | DF            | 1 | _ | _   | _   | _ | _ | 1      | 2      |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

177

# **General Purpose I/O Port Output Timing**

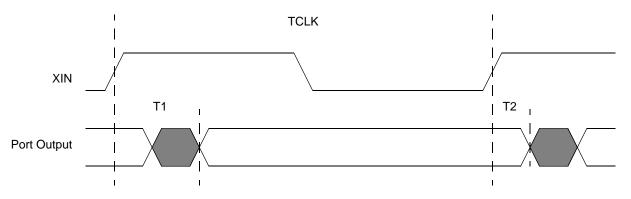

Figure 34 and Table 125 provide timing information for the GPIO port pins.

|                |                                     | Dela    | y (ns)  |

|----------------|-------------------------------------|---------|---------|

| Parameter      | Abbreviation                        | Minimum | Maximum |

| GPIO Port F    | Pins                                |         |         |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _       | 15      |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2       | _       |

#### Table 125. GPIO Port Output Timing

| Part Number          | Flash      | RAM   | NVDS | ADC<br>Channels | Description                                    |

|----------------------|------------|-------|------|-----------------|------------------------------------------------|

| Z8F0131PJ020SG       | 1KB        | 256   | Yes  | 0               | PDIP 28-pin                                    |

| Z8F0131QJ020SG       | 1KB        | 256   | Yes  | 0               | QFN 28-pin                                     |

| Extended Temperature | : −40°C to | 105°C |      |                 |                                                |

| Z8F0130SH020EG       | 1KB        | 256   | Yes  | 7               | SOIC 20-pin                                    |

| Z8F0130HH020EG       | 1KB        | 256   | Yes  | 7               | SSOP 20-pin                                    |

| Z8F0130PH020EG       | 1KB        | 256   | Yes  | 7               | PDIP 20-pin                                    |

| Z8F0130QH020EG       | 1KB        | 256   | Yes  | 7               | QFN 20-pin                                     |

| Z8F0131SH020EG       | 1KB        | 256   | Yes  | 0               | SOIC 20-pin                                    |

| Z8F0131HH020EG       | 1KB        | 256   | Yes  | 0               | SSOP 20-pin                                    |

| Z8F0131PH020EG       | 1KB        | 256   | Yes  | 0               | PDIP 20-pin                                    |

| Z8F0131QH020EG       | 1KB        | 256   | Yes  | 0               | QFN 20-pin                                     |

| Z8F0130SJ020EG       | 1KB        | 256   | Yes  | 8               | SOIC 28-pin                                    |

| Z8F0130HJ020EG       | 1KB        | 256   | Yes  | 8               | SSOP 28-pin                                    |

| Z8F0130PJ020EG       | 1KB        | 256   | Yes  | 8               | PDIP 28-pin                                    |

| Z8F0130QJ020EG       | 1KB        | 256   | Yes  | 8               | QFN 28-pin                                     |

| Z8F0131SJ020EG       | 1KB        | 256   | Yes  | 0               | SOIC 28-pin                                    |

| Z8F0131HJ020EG       | 1KB        | 256   | Yes  | 0               | SSOP 28-pin                                    |

| Z8F0131PJ020EG       | 1KB        | 256   | Yes  | 0               | PDIP 28-pin                                    |

| Z8F0131QJ020EG       | 1KB        | 256   | Yes  | 0               | QFN 28-pin                                     |

| ZUSBSC00100ZACG      |            |       |      |                 | USB Smart Cable Accessory Kit                  |

| ZUSBOPTSC01ZACG      |            |       |      |                 | Opto-Isolated USB Smart Cable<br>Accessory Kit |

#### Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

# **Part Number Suffix Designations**

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0830SH020SG is an 8-bit 20MHz Flash MCU with 8KB Program Memory and equipped with ADC and NVDS in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

### Hex Addresses: FC9–FCC

This address range is reserved.

#### Hex Address: FCD

#### Table 166. Interrupt Edge Select Register (IRQES)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|--|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |  |  |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |  |

| Address |      | FCDH |      |      |      |      |      |      |  |  |  |

#### Hex Address: FCE

#### Table 167. Shared Interrupt Select Register (IRQSS)

| Bit     | 7        | 6     | 5   | 4        | 3   | 2   | 1   | 0   |  |  |  |  |

|---------|----------|-------|-----|----------|-----|-----|-----|-----|--|--|--|--|

| Field   | Reserved | PA6CS |     | Reserved |     |     |     |     |  |  |  |  |

| RESET   | 0        | 0     | 0   | 0        | 0   | 0   | 0   | 0   |  |  |  |  |

| R/W     | R/W      | R/W   | R/W | R/W      | R/W | R/W | R/W | R/W |  |  |  |  |

| Address |          | FCEH  |     |          |     |     |     |     |  |  |  |  |

### Hex Address: FCF

#### Table 168. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6    | 5        | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|---------|------|------|----------|---|---|---|---|---|--|--|--|--|

| Field   | IRQE |      | Reserved |   |   |   |   |   |  |  |  |  |

| RESET   | 0    | 0    | 0        | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

| R/W     | R/W  | R    | R        | R | R | R | R | R |  |  |  |  |

| Address |      | FCFH |          |   |   |   |   |   |  |  |  |  |

### Hex Address: FFB

### Table 196. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|---------|---|--------|---|----|----|---|---|---|--|--|--|--|

| Field   |   | FFREQL |   |    |    |   |   |   |  |  |  |  |

| RESET   |   | 0      |   |    |    |   |   |   |  |  |  |  |

| R/W     |   | R/W    |   |    |    |   |   |   |  |  |  |  |

| Address |   |        |   | FF | BH |   |   |   |  |  |  |  |

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

JP 169 LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167 LDX 168 LEA 168 load 168 logical 169 **MULT 167 NOP 168** OR 169 ORX 169 POP 168 **POPX 168** program control 169 **PUSH 168** PUSHX 168 RCF 167, 168 **RET 169** RL 169 **RLC 169** rotate and shift 169 RR 170 **RRC** 170 **SBC 167** SCF 167. 168 **SRA 170 SRL 170 SRP** 168 **STOP 168 SUB 167 SUBX 167 SWAP 170** TCM 167 **TCMX 167** TM 167 TMX 167 **TRAP 169** watch-dog timer refresh 168 XOR 169 **XORX 169** instructions, eZ8 classes of 166

interrupt control register 67 interrupt controller 53 architecture 53 interrupt assertion types 56 interrupt vectors and priority 56 operation 55 register definitions 57 software interrupt assertion 57 interrupt edge select register 65 interrupt request 0 register 58 interrupt request 1 register 59 interrupt request 2 register 60 interrupt return 169 interrupt vector listing 53 IR 164 Ir 164 **IRET 169** IRQ0 enable high and low bit registers 60 IRQ1 enable high and low bit registers 62 IRQ2 enable high and low bit registers 63 **IRR 164** Irr 164

# J

JP 169 jump, conditional, relative, and relative conditional 169

### L

LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167, 168 LDX 168 LEA 168 load constant 167 load constant to/from program memory 168 load constant with auto-increment addresses 168 load effective address 168 load external data 168

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

load external data to/from data memory and autoincrement addresses 167 load external to/from data memory and auto-increment addresses 168 load instructions 168 load using extended addressing 168 logical AND 169 logical AND/extended addressing 169 logical exclusive OR 169 logical exclusive OR/extended addressing 169 logical instructions 169 logical OR 169 logical OR/extended addressing 169

# Μ

master interrupt enable 55 memory data 16 program 15 mode capture 89, 90 capture/compare 89 continuous 89 counter 89 gated 89 one-shot 89 PWM 89.90 modes 89 motor control measurements ADC Control register definitions 101 calibration and compensation 101 interrupts 101 overview 98 **MULT 167** multiply 167

# Ν

noise, electrical 98 NOP (no operation) 168 notation b 164

DA 164 ER 164 IM 164 IR 164 Ir 164 IRR 164 Irr 164 p 164 R 165 r 164 RA 165 RR 165 rr 165 vector 165 X 165 notational shorthand 164

cc 164

# 0

OCD architecture 139 auto-baud detector/generator 142 baud rate limits 142 block diagram 139 breakpoints 143 commands 144 control register 148 data format 142 DBG pin to RS-232 Interface 140 debug mode 141 debugger break 169 interface 140 serial errors 143 status register 150 timing 197 OCD commands execute instruction (12H) 148 read data memory (0DH) 147 read OCD control register (05H) 146 read OCD revision (00H) 145 read OCD status register (02H) 145 read program counter (07H) 146 read program memory (0BH) 147