Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 23                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | ·                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0830sj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| ADC Control Register Definitions10ADC Control Register 010ADC Data High Byte Register10ADC Data Low Bits Register10Sample Settling Time Register10Sample Time Register10                                                                                                                                                                                                                                                                                                                                                                                                    | )2<br>)3<br>)3<br>)4                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Comparator10Operation10Comparator Control Register Definitions10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )6                                              |

| Flash Memory       10         Data Memory Address Space       11         Flash Information Area       11         Operation       11         Flash Operation Timing Using the Flash Frequency Registers       11                                                                                                                                                                                                                                                                                                                                                             | 1<br>1<br>2                                     |

| Flash Code Protection Against External Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                               |

| Flash Code Protection Against Accidental Program and Erasure11Byte Programming11Page Erase11Mass Erase11Flash Controller Bypass11Flash Controller Behavior in Debug Mode11NVDS Operational Requirements11Flash Control Register Definitions11Flash Control Register Definitions11Flash Status Register12Flash Status Register12Flash Page Select Register12Flash Sector Protect Register12Flash Frequency High and Low Byte Registers12                                                                                                                                     | 6<br>7<br>7<br>7<br>7<br>8<br>8<br>9<br>0<br>21 |

| Flash Option Bits       12.         Operation       12.         Option Bit Configuration by Reset       12.         Option Bit Types       12.         Flash Option Bit Control Register Definitions       12.         Flash Option Bit Control Register Definitions       12.         Flash Option Bit Control Register Definitions       12.         Trim Bit Address Register       12.         Trim Bit Address Register       12.         Flash Option Bit Address Space       12.         Trim Bit Address Space       12.         Nonvolatile Data Storage       13. | 24<br>24<br>25<br>26<br>26<br>26<br>27<br>29    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                                               |

Calibration and Compensation ..... 101

### vii

# **Overview**

Zilog's Z8 Encore! MCU family of products are the first in a line of Zilog microcontroller products based on the 8-bit eZ8 CPU. The Z8 Encore! F0830 Series products expand on Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward-compatible with existing Z8 CPU instructions. The rich peripheral set of Z8 Encore! F0830 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices and sensors.

# **Features**

The key features of Z8 Encore! F0830 Series MCU include:

- 20MHz eZ8 CPU

- Up to 12KB Flash memory with in-circuit programming capability

- Up to 256B register RAM

- 64B Nonvolatile Data Storage (NVDS)

- Up to 25 I/O pins depending upon package

- Internal Precision Oscillator (IPO)

- External crystal oscillator

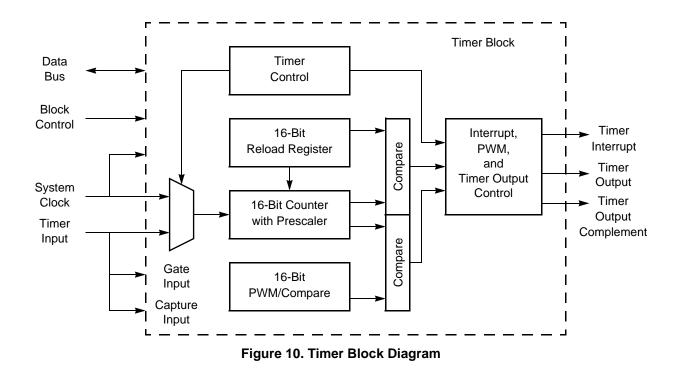

- Two enhanced 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Single-pin, On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-chip analog comparator

- Up to 17 interrupt sources

- Voltage Brown-Out (VBO) protection

- Power-On Reset (POR)

- 2.7V to 3.6V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 20- and 28-pin packages

- 0°C to +70°C standard temperature range and -40°C to +105°C extended temperature operating ranges

# **Register Map**

Table 8 provides an address map of the Z8 Encore! F0830 Series register file. Not all devices and package styles in the Z8 Encore! F0830 Series support the ADC or all of the GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)    | Register Description              | Mnemonic      | Reset (Hex) | Page No. |

|------------------|-----------------------------------|---------------|-------------|----------|

| General Purpos   | e RAM                             |               |             |          |

| 000–0FF          | General purpose register file RAM |               | XX          |          |

| 100–EFF          | Reserved                          | _             | XX          |          |

| Timer 0          |                                   |               |             |          |

| F00              | Timer 0 high byte                 | T0H           | 00          | 83       |

| F01              | Timer 0 low byte                  | TOL           | 01          | 83       |

| F02              | Timer 0 reload high byte          | TORH          | FF          | 85       |

| F03              | Timer 0 reload low byte           | TORL          | FF          | 85       |

| F04              | Timer 0 PWM high byte             | <b>T0PWMH</b> | 00          | 86       |

| F05              | Timer 0 PWM low byte              | TOPWML        | 00          | 86       |

| F06              | Timer 0 control 0                 | T0CTL0        | 00          | 87       |

| F07              | Timer 0 control 1                 | T0CTL1        | 00          | 88       |

| Timer 1          |                                   |               |             |          |

| F08              | Timer 1 high byte                 | T1H           | 00          | 83       |

| F09              | Timer 1 low byte                  | T1L           | 01          | 83       |

| F0A              | Timer 1 reload high byte          | T1RH          | FF          | 85       |

| F0B              | Timer 1 reload low byte           | T1RL          | FF          | 85       |

| F0C              | Timer 1 PWM high byte             | T1PWMH        | 00          | 86       |

| F0D              | Timer 1 PWM low byte              | T1PWML        | 00          | 86       |

| F0E              | Timer 1 control 0                 | T1CTL0        | 00          | 87       |

| F0F              | Timer 1 control 1                 | T1CTL1        | 00          | 83       |

| F10–F6F          | Reserved                          | _             | XX          |          |

| Analog-to-Digita | al Converter (ADC)                |               |             |          |

| F70              | ADC control 0                     | ADCCTL0       | 00          | 102      |

| F71              | Reserved                          |               | XX          |          |

| F72              | ADC data high byte                | ADCD_H        | XX          | 103      |

#### Table 8. Register File Address Map

Note: XX = Undefined.

|                  | _                          |          | -           |          |

|------------------|----------------------------|----------|-------------|----------|

| Address (Hex)    | Register Description       | Mnemonic | Reset (Hex) | Page No. |

| Analog-to-Digita | al Converter (ADC, cont'd) |          |             |          |

| F73              | ADC data low bits          | ADCD_L   | XX          | 103      |

| F74              | ADC sample settling time   | ADCSST   | 0F          | 104      |

| F75              | ADC sample time            | ADCST    | 3F          | 105      |

| F76              | Reserved                   | —        | XX          |          |

| F77–F7F          | Reserved                   | —        | XX          |          |

| Low Power Con    | trol                       |          |             |          |

| F80              | Power control 0            | PWRCTL0  | 88          | 32       |

| F81              | Reserved                   | _        | XX          |          |

| LED Controller   |                            |          |             |          |

| F82              | LED drive enable           | LEDEN    | 00          | 51       |

| F83              | LED drive level high       | LEDLVLH  | 00          | 51       |

| F84              | LED drive level low        | LEDLVLL  | 00          | 52       |

| F85              | Reserved                   | _        | XX          |          |

| Oscillator Contr | ol                         |          |             |          |

| F86              | Oscillator control         | OSCCTL   | A0          | 154      |

| F87–F8F          | Reserved                   | —        | XX          |          |

| Comparator 0     |                            |          |             |          |

| F90              | Comparator 0 control       | CMP0     | 14          | 107      |

| F91–FBF          | Reserved                   | _        | XX          |          |

| Interrupt Contro | bller                      |          |             |          |

| FC0              | Interrupt request 0        | IRQ0     | 00          | 58       |

| FC1              | IRQ0 enable high bit       | IRQ0ENH  | 00          | 61       |

| FC2              | IRQ0 enable low Bit        | IRQ0ENL  | 00          | 61       |

| FC3              | Interrupt request 1        | IRQ1     | 00          | 59       |

| FC4              | IRQ1 enable high bit       | IRQ1ENH  | 00          | 62       |

| FC5              | IRQ1 enable low bit        | IRQ1ENL  | 00          | 63       |

| FC6              | Interrupt request 2        | IRQ2     | 00          | 60       |

| FC7              | IRQ2 enable high bit       | IRQ2ENH  | 00          | 64       |

| FC8              | IRQ2 enable low bit        | IRQ2ENL  | 00          | 64       |

| FC9–FCC          | Reserved                   | —        | XX          |          |

| FCD              | Interrupt edge select      | IRQES    | 00          | 66       |

# Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

# Port A–D Control Registers

The Port A–D Control registers, shown in Table 20, set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction.

| Bit     | 7                      | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------------------|------|-----|-----|-----|-----|-----|-----|

| Field   |                        | PCTL |     |     |     |     |     |     |

| RESET   | 00H                    |      |     |     |     |     |     |     |

| R/W     | R/W                    | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FD1H, FD5H, FD9H, FDDH |      |     |     |     |     |     |     |

| Table 20 | . Port A-D | Control | Registers | (PxCTL) |

|----------|------------|---------|-----------|---------|

|----------|------------|---------|-----------|---------|

| Bit   | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Port Control</b>                                                                                   |

| PCTL  | The Port Control Register provides access to all subregisters that configure the GPIO port operation. |

# Port A–D Data Direction Subregisters

The Port A–D Data Direction Subregister, shown in Table 21, is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register.

| Bit     | 7         | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| Field   | DD7       | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET   | 1         | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W       | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | If 01H ir | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Direction                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction Register setting.</li> <li>0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register The output driver is tristated.</li> </ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                       |

Note: x indicates the specific GPIO port pin number (7–0).

## Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the Port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high-output current drive operation. The Port A–D High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit     | 7                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Field   | PHDE7                                                                                 | PHDE6 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |       |

#### Bit Description

[7:0] Port High Drive Enable

PHDEx 0 = The port pin is configured for standard output current drive.

1 = The port pin is configured for high output current drive.

Note: x indicates the specific GPIO port pin number (7–0).

# Table 45. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7    | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|------|------|-------|-----|-------|-------|-------|-------|

| Field   |      | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET   | 0    | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address | FC7H |      |       |     |       |       |       |       |

| Bit          | Description                                                                     |

|--------------|---------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit                                       |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit                                       |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit                                       |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit                                       |

### Table 46. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7    | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |  |

|---------|------|------|-------|-----|-------|-------|-------|-------|--|--|

| Field   |      | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |  |  |

| RESET   | 0    | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |

| Address | FC8H |      |       |     |       |       |       |       |  |  |

| Bit          | Description                                                                     |

|--------------|---------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000. |

| [3]<br>C3ENL | Port C3 Interrupt Request Enable Low Bit                                        |

| [2]<br>C2ENL | Port C2 Interrupt Request Enable Low Bit                                        |

| [1]<br>C1ENL | Port C1 Interrupt Request Enable Low Bit                                        |

| [0]<br>COENL | Port C0 Interrupt Request Enable Low Bit                                        |

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7    | 6    | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|------|----------|---|---|---|---|---|--|--|

| Field   | IRQE |      | Reserved |   |   |   |   |   |  |  |

| RESET   | 0    | 0    | 0        | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W     | R/W  | R    | R        | R | R | R | R | R |  |  |

| Address |      | FCFH |          |   |   |   |   |   |  |  |

|         |      |      |          |   |   |   |   |   |  |  |

# Table 49. Interrupt Control Register (IRQCTL)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by executing an Enable Interrupts (EI) or Interrupt Return (IRET) instruction or by a direct register write of 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset, or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                                                                                                            |

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer resets back to 0000H and continues counting.

# **Timer Operating Modes**

The timers can be configured to operate in the following modes:

## **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

Additionally, if the timer output alternate function is enabled, the timer output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

#### Bit Description (Continued)

#### [6] Timer Input/Output Polarity

TPOL Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### **COUNTER Mode**

If the timer is disabled, the timer output signal is set to the value of this bit. If the timer is enabled the timer output signal is complemented after timer reload.

- 0 = Count occurs on the rising edge of the timer input signal.

- 1 = Count occurs on the falling edge of the timer input signal.

#### PWM SINGLE OUTPUT Mode

- 0 = Timer output is forced Low (0), when the timer is disabled. The timer output is forced High (1) when the timer is enabled and the PWM count matches and the timer output is forced Low (0) when the timer is enabled and reloaded.

- 1 = Timer output is forced High (1), when the timer is disabled. The timer output is forced low(0), when the timer is enabled and the PWM count matches and forced High (1) when the timer is enabled and reloaded.

#### CAPTURE Mode

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### COMPARE Mode

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled and reloaded, the timer output signal is complemented.

#### GATED Mode

- 0 = Timer counts when the timer input signal is High (1) and interrupts are generated on the falling edge of the timer input.

- 1 = Timer counts when the timer input signal is Low (0) and interrupts are generated on the rising edge of the timer input.

#### CAPTURE/COMPARE Mode

- 0 = Counting is started on the first rising edge of the timer input signal. The current count is captured on subsequent rising edges of the timer input signal.

- 1 = Counting is started on the first falling edge of the timer input signal. The current count is captured on subsequent falling edges of the timer input signal.

| Bit                     | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6]<br>TPOL<br>(cont'd) | <ul> <li>PWM DUAL OUTPUT Mode</li> <li>0 = Timer output is forced Low (0) and timer output complement is forced High (1), when the timer is disabled. When enabled and the PWM count matches, the timer output is forced High (1) and forced Low (0) when enabled and reloaded. When enabled and the PWM count matches, the timer output complement is forced Low (0) and forced High (1) when enabled and reloaded.</li> <li>1 = Timer output is forced High (1) and timer output complement is forced Low (0) when the timer is disabled. When enabled and the PWM count matches, the timer output is forced Low (0) when the timer is disabled. When enabled and the PWM count matches, the timer output is forced Low (0) and forced High (1) when enabled and reloaded. Use (0) and forced High (1) when enabled and reloaded. The PWMD field in the TxCTL0 register determines an optional added delay on the assertion (Low to High) transition of both timer output and timer output complement for deadband generation.</li> <li>CAPTURE RESTART Mode</li> <li>0 = Count is captured on the rising edge of the timer input signal.</li> </ul> |

|                         | <ul> <li>1 = Count is captured on the falling edge of the timer input signal.</li> <li>COMPARATOR COUNTER Mode</li> <li>When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                         | <b>Caution:</b> When the timer output alternate function TxOUT on a GPIO port pin is enabled, TxOUT will change to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Additionally, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit when the timer is enabled and running does not immediately change the polarity TxOUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [5:3]<br>PRES           | Prescale Value<br>The timer input clock is divided by 2 <sup>PRES</sup> , where PRES can be set from 0 to 7. The prescaler is<br>reset each time the timer is disabled. This reset ensures proper clock division each time the<br>timer is restarted.<br>000 = Divide by 1.<br>001 = Divide by 2.<br>010 = Divide by 4.<br>011 = Divide by 8.<br>100 = Divide by 16.<br>101 = Divide by 32.<br>110 = Divide by 64.<br>111 = Divide by 128.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Bit   | Description (Continued)                                                                   |

|-------|-------------------------------------------------------------------------------------------|

| [2:0] | Timer Mode                                                                                |

| TMODE | This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of |

|       | the timer. TMODEHI is the most significant bit of the timer mode selection value.         |

|       | 0000 = ONE-SHOT Mode.                                                                     |

|       | 0001 = CONTINUOUS Mode.                                                                   |

|       | 0010 = COUNTER Mode.                                                                      |

|       | 0011 = PWM SINGLE OUTPUT Mode.                                                            |

|       | 0100 = CAPTURE Mode.                                                                      |

|       | 0101 = COMPARE Mode.                                                                      |

|       | 0110 = GATED Mode.                                                                        |

|       | 0111 = CAPTURE/COMPARE Mode.                                                              |

|       | 1000 = PWM DUAL OUTPUT Mode.                                                              |

|       | 1001 = CAPTURE RESTART Mode.                                                              |

|       | 1010 = COMPARATOR COUNTER Mode.                                                           |

# Flash Memory

The products in the Z8 Encore! F0830 Series features either 1KB (1024 bytes with NVDS), 2KB (2048 bytes with NVDS), 4KB (4096 bytes with NVDS), 8KB (8192 bytes with NVDS) or 12KB (12288 bytes with no NVDS) of nonvolatile Flash memory with read/write/erase capability. Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into eight rows of 64 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! F0830 Series, each sector maps to one page (for 1KB, 2KB and 4KB devices), two pages (8KB device) or three pages (12KB device).

The first two bytes of Flash program memory is used as Flash option bits. For more information, see *the* <u>Flash Option Bits</u> chapter on page 124.

Table 69 lists the Flash memory configuration for each device in the Z8 Encore! F0830 Series. Figures 14 through 18 display the memory arrangements for each Flash memory size.

| Part Number | Flash Size<br>KB (Bytes) | Flash Pages | Program<br>Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|-------------|--------------------------------|------------------------------|

| Z8F123x     | 12 (12,288)              | 24          | 0000H–2FFFH                    | 1536                         |

| Z8F083x     | 8 (8196)                 | 16          | 0000H-1FFFH                    | 1024                         |

| Z8F043x     | 4 (4096)                 | 8           | 0000H–0FFFH                    | 512                          |

| Z8F023x     | 2 (2048)                 | 4           | 0000H–07FFH                    | 512                          |

| Z8F013x     | 1 (1024)                 | 2           | 0000H-03FFH                    | 512                          |

Figure 14. 1K Flash with NVDS

<sup>03</sup>FFH

03FFH

03FFH

0200H

Sector 1

Page 1

0200H

01FFH

Sector 0

Page 0

01FFH

0000H

0000H

0000H

0000H

| Bit             | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>POFEN    | <ul> <li>Primary Oscillator Failure Detection Enable</li> <li>1 = Failure detection and recovery of primary oscillator is enabled.</li> <li>0 = Failure detection and recovery of primary oscillator is disabled.</li> </ul>                                                                                                                                                                                                                                     |

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable<br>1 = Failure detection of Watchdog Timer Oscillator is enabled.<br>0 = Failure detection of Watchdog Timer Oscillator is disabled.                                                                                                                                                                                                                                                                          |

| [2:0]<br>SCKSEL | System Clock Oscillator Select<br>000 = Internal Precision Oscillator functions as system clock at 5.53MHz.<br>001 = Internal Precision Oscillator functions as system clock at 32 kHz.<br>010 = Crystal oscillator or external RC oscillator functions as system clock.<br>011 = Watchdog Timer Oscillator functions as system clock.<br>100 = External clock signal on PB3 functions as system clock.<br>101 = Reserved.<br>110 = Reserved.<br>111 = Reserved. |

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50pF on all outputs.

|                     |                                            | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |                  | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to<br>+105°C |        |            |                                                                                                              |  |

|---------------------|--------------------------------------------|----------------------------------------------------------------|------------------|----------------------------------------------------------------------|--------|------------|--------------------------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                                  | Min                                                            | in Max Min Max U |                                                                      | Units  | Conditions |                                                                                                              |  |

| F <sub>SYSCLK</sub> | System Clock Fre-<br>quency                |                                                                |                  | -                                                                    | 20.0   | MHz        | Read-only from Flash memory                                                                                  |  |

|                     |                                            |                                                                |                  | 0.03276<br>8                                                         | 20.0   | MHz        | Program or erasure of the Flash memory                                                                       |  |

| F <sub>XTAL</sub>   | Crystal Oscillator<br>Frequency            |                                                                |                  | 1.0                                                                  | 20.0   | MHz        | System clock frequen-<br>cies below the crystal<br>oscillator minimum<br>require an external                 |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |                  | 0.03276<br>8                                                         | 5.5296 | MHz        | Oscillator is <b>not</b> adjust-<br>able over the entire<br>range. User may select<br>Min or Max value only. |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |                  | 5.31                                                                 | 5.75   | MHz        | High speed with trim-<br>ming                                                                                |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |                  | 4.15                                                                 | 6.91   | MHz        | High speed without trimming                                                                                  |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |                  | 30.7                                                                 | 33.3   | KHz        | Low speed with trim-<br>ming                                                                                 |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |                  | 24                                                                   | 40     | KHz        | Low speed without trimming                                                                                   |  |

| T <sub>XIN</sub>    | System Clock<br>Period                     |                                                                |                  | 50                                                                   | -      | ns         | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                     |  |

| T <sub>XINH</sub>   | System Clock High<br>Time                  |                                                                |                  | 20                                                                   | 30     | ns         | T <sub>CLK</sub> = 50 ns                                                                                     |  |

| T <sub>XINL</sub>   | System Clock Low<br>Time                   |                                                                |                  | 20                                                                   | 30     | ns         | T <sub>CLK</sub> = 50 ns                                                                                     |  |

### **Table 117. AC Characteristics**

|                   |                                                                                           | T <sub>A</sub> = 0°C to +70°C |     |     | T <sub>A</sub> = -40°C to<br>+105°C |                  |     |       |                                                             |  |

|-------------------|-------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------|------------------|-----|-------|-------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                 | Min                           | Тур | Max | Min                                 | Typ <sup>1</sup> | Max | Units | Conditions                                                  |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>POR</sub>  | Power-On Reset<br>Digital Delay                                                           |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>disabled                              |                               |     |     | TBD                                 | 13               | TBD | μs    | 66 Internal Preci-<br>sion Oscillator<br>cycles             |  |

| T <sub>SMR</sub>  | Stop Mode<br>Recovery with<br>crystal oscillator<br>enabled                               |                               |     |     | TBD                                 | 8                | TBD | ms    | 5000 Internal Pre-<br>cision Oscillator<br>cycles           |  |

| T <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                                            |                               |     |     | _                                   | 10               | _   | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to gen<br>erate a Reset. |  |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to<br>transition from $V_{SS}$<br>to $V_{POR}$ to ensure<br>valid Reset |                               |     |     | 0.10                                | _                | 100 | ms    |                                                             |  |

# Table 118. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

ance only and are not tested in production.

# **Ordering Information**

Order your F0830 Series products from Zilog using the part numbers shown in Table 128. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

|                      |               |            |      | ADC | -           |

|----------------------|---------------|------------|------|-----|-------------|

| Part Number          | Flash         | RAM        | NVDS | -   | Description |

| Z8 Encore! F0830 Ser | ries MCUs wi  | ith 12KB F | lash |     |             |

| Standard Temperatur  | e: 0°C to 70° | °C         |      |     |             |

| Z8F1232SH020SG       | 12KB          | 256        | No   | 7   | SOIC 20-pin |

| Z8F1232HH020SG       | 12KB          | 256        | No   | 7   | SSOP 20-pin |

| Z8F1232PH020SG       | 12KB          | 256        | No   | 7   | PDIP 20-pin |

| Z8F1232QH020SG       | 12KB          | 256        | No   | 7   | QFN 20-pin  |

| Z8F1233SH020SG       | 12KB          | 256        | No   | 0   | SOIC 20-pin |

| Z8F1233HH020SG       | 12KB          | 256        | No   | 0   | SSOP 20-pin |

| Z8F1233PH020SG       | 12KB          | 256        | No   | 0   | PDIP 20-pin |

| Z8F1233QH020SG       | 12KB          | 256        | No   | 0   | QFN 20-pin  |

| Z8F1232SJ020SG       | 12KB          | 256        | No   | 8   | SOIC 28-pin |

| Z8F1232HJ020SG       | 12KB          | 256        | No   | 8   | SSOP 28-pin |

| Z8F1232PJ020SG       | 12KB          | 256        | No   | 8   | PDIP 28-pin |

| Z8F1232QJ020SG       | 12KB          | 256        | No   | 8   | QFN 28-pin  |

| Z8F1233SJ020SG       | 12KB          | 256        | No   | 0   | SOIC 28-pin |

| Z8F1233HJ020SG       | 12KB          | 256        | No   | 0   | SSOP 28-pin |

| Z8F1233PJ020SG       | 12KB          | 256        | No   | 0   | PDIP 28-pin |

| Z8F1233QJ020SG       | 12KB          | 256        | No   | 0   | QFN 28-pin  |

| Extended Temperatu   | re: –40°C to  | 105°C      |      |     |             |

| Z8F1232SH020EG       | 12KB          | 256        | No   | 7   | SOIC 20-pin |

| Z8F1232HH020EG       | 12KB          | 256        | No   | 7   | SSOP 20-pin |

| Z8F1232PH020EG       | 12KB          | 256        | No   | 7   | PDIP 20-pin |

| Z8F1232QH020EG       | 12KB          | 256        | No   | 7   | QFN 20-pin  |

| Z8F1233SH020EG       | 12KB          | 256        | No   | 0   | SOIC 20-pin |

| Z8F1233HH020EG       | 12KB          | 256        | No   | 0   | SSOP 20-pin |

| Z8F1233PH020EG       | 12KB          | 256        | No   | 0   | PDIP 20-pin |

|                      |               |            |      |     |             |

#### Table 128. Z8 Encore! XP F0830 Series Ordering Matrix

# Hex Address: FD7

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |       | FD7H  |       |       |       |       |       |       |  |  |

### Table 176. Port B Output Data Register (PBOUT)

### Hex Address: FD8

#### Table 177. Port C GPIO Address Register (PCADDR)

| Bit     | 7          | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------|-----------------------------|---|---|---|---|---|---|--|

| Field   | PADDR[7:0] |                             |   |   |   |   |   |   |  |

| RESET   | 00H        |                             |   |   |   |   |   |   |  |

| R/W     | R/W        | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FD8H       |                             |   |   |   |   |   |   |  |

# Hex Address: FD9

#### Table 178. Port C Control Registers (PCCTL)

| Bit     | 7    | 6                       | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-------------------------|---|---|---|---|---|---|--|

| Field   | PCTL |                         |   |   |   |   |   |   |  |

| RESET   | 00H  |                         |   |   |   |   |   |   |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FD9H |                         |   |   |   |   |   |   |  |

### Hex Address: FDA

#### Table 179. Port C Input Data Registers (PCIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|------|------|------|------|------|------|------|------|--|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |  |

| Address | FDAH |      |      |      |      |      |      |      |  |

# Hex Address: FFB

# Table 196. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|--------|---|---|----|----|---|---|---|--|--|

| Field   | FFREQL |   |   |    |    |   |   |   |  |  |

| RESET   | 0      |   |   |    |    |   |   |   |  |  |

| R/W     | R/W    |   |   |    |    |   |   |   |  |  |

| Address |        |   |   | FF | BH |   |   |   |  |  |