# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0831hh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Warning:** DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2012 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES or TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES or TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore! and Z8 Encore! XP are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

## Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| Electrical Characteristics 1                              | 184 |

|-----------------------------------------------------------|-----|

| Absolute Maximum Ratings 1                                | 184 |

| DC Characteristics 1                                      | 185 |

| AC Characteristics 1                                      | 189 |

| On-Chip Peripheral AC and DC Electrical Characteristics 1 | 190 |

| General Purpose I/O Port Input Data Sample Timing 1       | 195 |

| General Purpose I/O Port Output Timing 1                  | 196 |

| On-Chip Debugger Timing 1                                 | 197 |

| Packaging 1                                               | 199 |

| Ordering Information                                      | 200 |

| Part Number Suffix Designations 2                         | 205 |

| Appendix A. Register Tables                               | 208 |

| General Purpose RAM                                       | 208 |

| Timer 0                                                   | 208 |

| Analog-to-Digital Converter                               | 213 |

| Low Power Control                                         | 216 |

| LED Controller                                            | 216 |

| Oscillator Control                                        | 217 |

| Comparator 0                                              | 218 |

| Interrupt Controller                                      | 218 |

| GPIO Port A 2                                             | 222 |

| Watchdog Timer                                            | 226 |

| Trim Bit Control                                          | 228 |

| Flash Memory Controller    2                              | 228 |

| Index                                                     | 231 |

| Customer Support                                          | 239 |

|                                                           |     |

#### ix

# **Block Diagram**

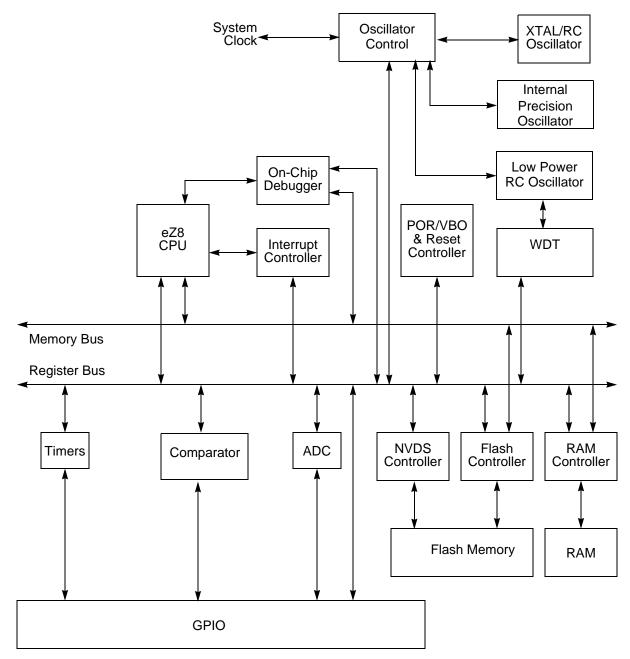

Figure 1 displays a block diagram of the Z8 Encore! F0830 Series architecture.

Figure 1. Z8 Encore! F0830 Series Block Diagram

## Nonvolatile Data Storage

The Nonvolatile Data Storage (NVDS) function uses a hybrid hardware/software scheme to implement a byte-programmable data memory and is capable of storing about 100,000 write cycles.

#### **Internal Precision Oscillator**

The Internal Precision Oscillator (IPO) function, with an accuracy of  $\pm 4\%$  full voltage/ temperature range, is a trimmable clock source that requires no external components.

## **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies using an external crystal, ceramic resonator or RC network.

#### **10-Bit Analog-to-Digital Converter**

The optional Analog-to-Digital Converter (ADC) converts an analog input signal to a 10bit binary number. The ADC accepts inputs from eight different analog input pins.

#### Analog Comparator

The analog comparator compares the signal at an input pin with either an internal programmable reference voltage or with a signal at the second input pin. The comparator output is used either to drive a logic output pin or to generate an interrupt.

#### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT Modes.

## **Interrupt Controller**

The Z8 Encore! F0830 Series products support seventeen interrupt sources with sixteen interrupt vectors: up to five internal peripheral interrupts and up to twelve GPIO interrupts. These interrupts have three levels of programmable interrupt priority.

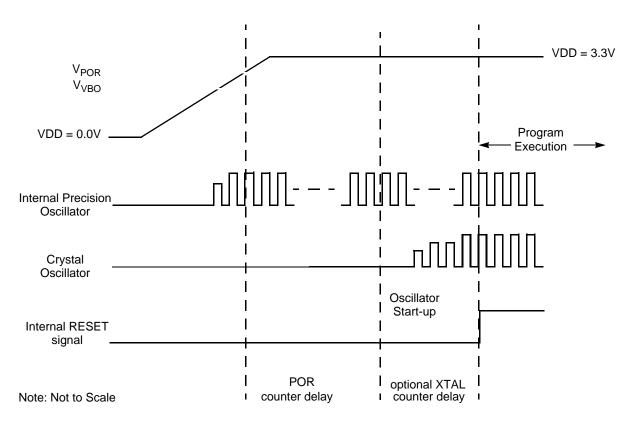

Figure 6. Power-On Reset Operation

## **Voltage Brown-Out Reset**

The devices in the Z8 Encore! F0830 Series provide low Voltage Brown-Out (VBO) protection. The VBO circuit forces the device to the Reset state, when the supply voltage drops below the VBO threshold voltage (unsafe level). While the supply voltage remains below the Power-On Reset threshold voltage ( $V_{POR}$ ), the VBO circuit holds the device in reset.

After the supply voltage exceeds the Power-On Reset threshold voltage, the device progresses through a full system reset sequence, as described in the POR section. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1. Figure 7 displays the Voltage Brown-Out operation. See the <u>Electrical Characteristics</u> chapter on page 184 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

## Port A–D Alternate Function Subregisters

The Port A–D Alternate Function Subregister is accessed through the Port A–D Control Register by writing 02H to the Port A–D Address Register. See Table 22 on page 42. The Port A–D Alternate Function subregisters enable the alternate function selection on pins. If disabled, the pins function as GPIOs. If enabled, select one of four alternate functions using Alternate Function Set subregisters 1 and 2, as described in the the <u>Port A–D Alternate Function</u> <u>Set 1 Subregisters</u> section on page 47 and the <u>Port A–D Alternate Function</u> <u>Set 2 Subregisters</u> section on page 48. See the <u>GPIO Alternate Functions</u> section on page 34 to determine the alternate functions associated with each port pin.

**Caution:** Do not enable alternate functions for GPIO port pins for which there is no associated Alternate function. Failure to follow this guideline can result in unpredictable operation.

| Bit     | 7           | 6                                                                                         | 5            | 4             | 3            | 2           | 1            | 0           |  |  |

|---------|-------------|-------------------------------------------------------------------------------------------|--------------|---------------|--------------|-------------|--------------|-------------|--|--|

| Field   | AF7         | AF7 AF6 AF5 AF4 AF3 AF2 AF1 AF0                                                           |              |               |              |             |              |             |  |  |

| RESET   |             | 00H (Ports A–C); 01H (Port D)                                                             |              |               |              |             |              |             |  |  |

| R/W     |             | R/W                                                                                       |              |               |              |             |              |             |  |  |

| Address | If 02H in F | Port A-D Ade                                                                              | dress Regist | ter, then acc | essible thro | ugh the Por | t A–D Contro | ol Register |  |  |

| Bit     | Description | Description                                                                               |              |               |              |             |              |             |  |  |

| [7:0]   | Port Altern | Port Alternate Function Enable                                                            |              |               |              |             |              |             |  |  |

| AFx     | •           | = The port pin is in NORMAL Mode and the DDx bit in the Port A–D Data Direction Subregis- |              |               |              |             |              |             |  |  |

Table 22. Port A–D Alternate Function Subregisters (PxAF)

ter determines the direction of the pin. 1 = The alternate function selected through Alternate function set subregisters is enabled. Port

= The alternate function selected through Alternate function set subregisters is enabled. Port pin operation is controlled by the Alternate function.

Note: x indicates the specific GPIO port pin number (7-0).

#### Port A–D Output Control Subregisters

The Port A–D Output Control Subregister, shown in Table 23, is accessed through the Port A–D Control Register by writing 03H to the Port A–D Address Register. Setting the bits in the Port A–D Output Control subregisters to 1 configures the specified port pins for opendrain operation. These subregisters affect the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7         | 6                                                                                     | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|-----------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|

| Field   | POC7      | POC6                                                                                  | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |

| RESET   | 0         | 0                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W       | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | lf 03H ir | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |      |      |      |      |      |      |

#### Table 23. Port A–D Output Control Subregisters (PxOC)

#### Bit Description

[7:0] Port Output Control

POCx These bits function independently of the Alternate function bit and always disable the drains, if set to 1.

0 = The drains are enabled for any OUTPUT Mode (unless overridden by the Alternate function).

1 = The drain of the associated pin is disabled (OPEN-DRAIN mode).

Note: x indicates the specific GPIO port pin number (7–0).

# LED Drive Level Low Register

The LED Drive Level Low Register, shown in Table 33, contains two control bits for each Port C pin. These two bits select one of four programmable current drive levels for each Port C pin. Each pin is individually programmable.

| Bit     | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|--------------|-----|-----|-----|-----|-----|-----|

| Field   |     | LEDLVLL[7:0] |     |     |     |     |     |     |

| RESET   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F84H         |     |     |     |     |     |     |

|         |     |              |     |     |     |     |     |     |

#### Table 33. LED Drive Level Low Register (LEDLVLL)

| Bit     | Description                                                                                  |

|---------|----------------------------------------------------------------------------------------------|

| [7:0]   | LED Level Low Bits                                                                           |

| LEDLVLL | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. |

|         | 00 = 3mA.                                                                                    |

|         | 01 = 7mA.                                                                                    |

|         | 10 = 13mA.                                                                                   |

|         | 11 = 20mA.                                                                                   |

• Writing 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (disable interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the Interrupt Controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction Trap

- Primary oscillator fail trap

- Watchdog Oscillator fail trap

#### **Interrupt Vectors and Priority**

The Interrupt Controller supports three levels of interrupt priority. Level 3 is the highest priority, level 2 is the second highest priority and level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 54. Level 3 interrupts are always assigned higher priority than level 2 interrupts and level 2 interrupts are assigned higher priority than level 1 interrupts. Within each interrupt priority level (level 1, level 2 or level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), primary oscillator fail trap, Watchdog Oscillator fail trap and illegal instruction trap always have highest (level 3) priority.

## **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the interrupt request register is cleared. Writing 0 to the corresponding bit in the interrupt request register clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

## **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) Register, shown in Table 36, stores interrupt requests for both vectored and polled interrupts. When a request is sent to the Interrupt Controller, the corresponding bit in the IRQ1 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the Interrupt Controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 Register to determine if any interrupt requests are pending.

| Bit     | 7          | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------------|-------|------|------|------|------|------|------|

| Field   | PA7I       | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET   | 0          | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W        | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |            | FC3H  |      |      |      |      |      |      |

| Bit     | Descriptio | n     |      |      |      |      |      |      |

#### Table 36. Interrupt Request 1 Register (IRQ1)

| Bit   | Description                                                            |  |

|-------|------------------------------------------------------------------------|--|

| [7]   | Port A7                                                                |  |

| PA7I  | 0 = No interrupt request is pending for GPIO Port A.                   |  |

|       | 1 = An interrupt request from GPIO Port A.                             |  |

| [6]   | Port A6 or Comparator Interrupt Request                                |  |

| PA6CI | 0 = No interrupt request is pending for GPIO Port A or comparator.     |  |

|       | 1 = An interrupt request from GPIO Port A or comparator.               |  |

| [5]   | Port A Pin <i>x</i> Interrupt Request                                  |  |

| PAxI  | 0 = No interrupt request is pending for GPIO Port A pin x.             |  |

|       | 1 = An interrupt request from GPIO Port A pin $x$ is awaiting service. |  |

#### Table 39. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit     | 7        | 6     | 5     | 4                  | 3   | 2   | 1   | 0      |

|---------|----------|-------|-------|--------------------|-----|-----|-----|--------|

| Field   | Reserved | T1ENH | T0ENH | ENH Reserved ADCEN |     |     |     | ADCENH |

| RESET   | 0        | 0     | 0     | 0                  | 0   | 0   | 0   | 0      |

| R/W     | R/W      | R/W   | R/W   | R/W                | R/W | R/W | R/W | R/W    |

| Address |          | FC1H  |       |                    |     |     |     |        |

| Bit           | Description                                                          |

|---------------|----------------------------------------------------------------------|

| [7]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 0. |

| [6]<br>T1ENH  | Timer 1 Interrupt Request Enable High Bit                            |

| [5]<br>T0ENH  | Timer 0 Interrupt Request Enable High Bit                            |

| [4:1]         | Reserved                                                             |

|               | These registers are reserved and must be programmed to 0000.         |

| [0]<br>ADCENH | ADC Interrupt Request Enable High Bit                                |

#### Table 40. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5     | 4   | 3          | 2 | 1 | 0   |

|---------|----------|-------|-------|-----|------------|---|---|-----|

| Field   | Reserved | T1ENL | T0ENL |     | Reserved A |   |   |     |

| RESET   | 0        | 0     | 0     | 0   | 0          | 0 | 0 | 0   |

| R/W     | R        | R/W   | R/W   | R/W | R/W        | R | R | R/W |

| Address |          | FC2H  |       |     |            |   |   |     |

| Bit           | Description                                                                     |

|---------------|---------------------------------------------------------------------------------|

| [7]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.            |

| [6]<br>T1ENL  | Timer 1 Interrupt Request Enable Low Bit                                        |

| [5]<br>T0ENL  | Timer 0 Interrupt Request Enable Low Bit                                        |

| [4:1]         | <b>Reserved</b><br>These registers are reserved and must be programmed to 0000. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                                            |

# **Timers**

The Z8 Encore! F0830 Series products contain up to two 16-bit reloadable timers that can be used for timing, event counting or generation of pulse width modulated (PWM) signals. The timers feature include:

- 16-bit reload counter

- Programmable prescaler with prescale values ranging from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

# Architecture

Figure 10 displays the architecture of the timers.

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines whether the capture occurs on a rising edge or a falling edge of the timer input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt has been caused by an input capture event.

If no capture event occurs, the timer counts up to 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

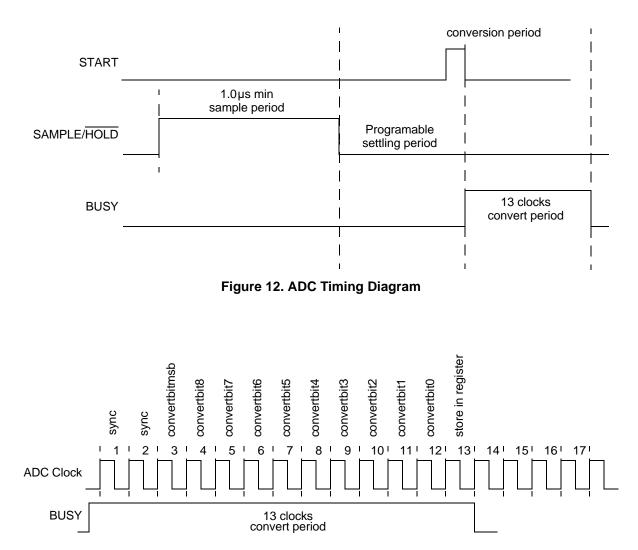

## **ADC** Timing

Each ADC measurement consists of three phases:

- 1. Input sampling (programmable, minimum of 1.0µs)

- 2. Sample-and-hold amplifier settling (programmable, minimum of 0.5µs)

- 3. Conversion is 13 ADCLK cycles

Figures 12 and 13 display the timing of an ADC conversion.

Figure 13. ADC Convert Timing

**Note:** The bit values used in Table 85 are set at the factory; no calibration is required.

#### Table 86. Trim Option Bits at 0002H (TIPO)

| Bit       | 7                                     | 6                             | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|---------------------------------------|-------------------------------|---|---|---|---|---|---|

| Field     |                                       | IPO_TRIM                      |   |   |   |   |   |   |

| RESET     |                                       | U                             |   |   |   |   |   |   |

| R/W       |                                       | R/W                           |   |   |   |   |   |   |

| Address   |                                       | Information Page Memory 0022H |   |   |   |   |   |   |

| Note: U = | Unchanged by Reset. R/W = Read/Write. |                               |   |   |   |   |   |   |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

**Note:** The bit values used in Table 86 are set at the factory; no calibration is required.

## Table 87. Trim Option Bits at 0003H (TVBO)

| Bit       | 7                                               | 6 | 5 | 4 | 3        | 2        | 1   | 0 |  |

|-----------|-------------------------------------------------|---|---|---|----------|----------|-----|---|--|

| Field     | Reserved                                        |   |   |   | Reserved | VBO_TRIM |     |   |  |

| RESET     | U                                               |   |   |   | U        | 1        | 0   | 0 |  |

| R/W       | R/W                                             |   |   |   | R/W      |          | R/W |   |  |

| Address   | Information Page Memory 0023H                   |   |   |   |          |          |     |   |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |   |   |   |          |          |     |   |  |

| Bit      | Description                                                                 |

|----------|-----------------------------------------------------------------------------|

| [7:3]    | <b>Reserved</b><br>These bits are reserved and must be programmed to 11111. |

|          |                                                                             |

| [2]      | VBO Trim Values                                                             |

| VBO_TRIM | Contains factory-trimmed values for the oscillator and the VBO.             |

>

| Description (Continued)                             |  |  |  |  |  |

|-----------------------------------------------------|--|--|--|--|--|

| Filter Select                                       |  |  |  |  |  |

| 2-bit selection for the clock filter mode.          |  |  |  |  |  |

| 00 = No filter.                                     |  |  |  |  |  |

| 01 = Filter low level noise on high level signal.   |  |  |  |  |  |

| 10 = Filter high level noise on low level signal.   |  |  |  |  |  |

| 11 = Filter both.                                   |  |  |  |  |  |

| dicates bit values 3–1; y indicates bit values 1–0. |  |  |  |  |  |

|                                                     |  |  |  |  |  |

**Note:** The bit values used in Table 89 are set at factory and no calibration is required.

| DlyCtl3, DlyCtl2,<br>DlyCtl1 | Low Noise Pulse<br>on High Signal (ns) | High Noise Pulse<br>on Low Signal (ns) |

|------------------------------|----------------------------------------|----------------------------------------|

| 000                          | 5                                      | 5                                      |

| 001                          | 7                                      | 7                                      |

| 010                          | 9                                      | 9                                      |

| 011                          | 11                                     | 11                                     |

| 100                          | 13                                     | 13                                     |

| 101                          | 17                                     | 17                                     |

| 110                          | 20                                     | 20                                     |

| 111                          | 25                                     | 25                                     |

| Note: The variation is       | about 30%.                             |                                        |

#### Table 90. ClkFlt Delay Control Definition

## **Runtime Counter**

The OCD contains a 16-bit runtime counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the On-Chip Debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash read protect option bit (FRP). The FRP prevents the code in memory from being read out of the Z8 Encore! F0830 Series products. When this option is enabled, several of the OCD commands are disabled.

Table 95 summarizes the On-Chip Debugger commands. This table indicates the commands that operate when the device is not in DEBUG Mode (normal operation) and the commands that are disabled by programming the FRP.

| Debug Command              | Command<br>Byte | Enabled when not<br>in DEBUG Mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                                     |

|----------------------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                | -                                                                                                                                                                                |

| Reserved                   | 01H             | _                                  | _                                                                                                                                                                                |

| Read OCD Status Register   | 02H             | Yes                                | _                                                                                                                                                                                |

| Read Runtime Counter       | 03H             | _                                  | -                                                                                                                                                                                |

| Write OCD Control Register | 04H             | Yes                                | Cannot clear DBGMODE bit                                                                                                                                                         |

| Read OCD Control Register  | 05H             | Yes                                | _                                                                                                                                                                                |

| Write Program Counter      | 06H             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Counter       | 07H             | _                                  | Disabled                                                                                                                                                                         |

| Write Register             | 08H             | _                                  | Only writes of the Flash Memory Con-<br>trol registers are allowed. Additionally,<br>only the Mass Erase command is<br>allowed to be written to the Flash Con-<br>trol register. |

| Read Register              | 09H             | _                                  | Disabled                                                                                                                                                                         |

| Write Program Memory       | 0AH             | _                                  | Disabled                                                                                                                                                                         |

| Read Program Memory        | 0BH             | _                                  | Disabled                                                                                                                                                                         |

| Write Data Memory          | 0CH             | _                                  | Yes                                                                                                                                                                              |

| Read Data Memory           | 0DH             | _                                  | _                                                                                                                                                                                |

#### Table 95. On-Chip Debugger Command Summary

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

# **Internal Precision Oscillator**

The Internal Precision Oscillator (IPO) is designed for use without external components. The user can either manually trim the oscillator for a nonstandard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency with  $\pm 4\%$  accuracy and 45%~55% duty cycle over the operating temperature and supply voltage of the device. The maximum start-up time of the IPO is 25µs. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8kHz (contains both a FAST and a SLOW mode)

- Trimming possible through Flash option bits, with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

# Operation

The internal oscillator is an RC relaxation oscillator with a minimized sensitivity to power supply variations. By using ratio-tracking thresholds, the effect of power supply voltage is cancelled out. The dominant source of oscillator error is the absolute variance of chip-level fabricated components, such as capacitors. An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed, the oscillator frequency is stable and does not require subsequent calibration. Trimming was performed during manufacturing and is not necessary for the user to repeat unless a frequency other than 5.53 MHz (FAST mode) or 32.8 kHz (SLOW mode) is required.

**Note:** The user can power down the IPO block for minimum system power.

By default, the oscillator is configured through the Flash option bits. However, the user code can override these trim values, as described in *the* <u>Trim Bit Address Space</u> section on page 129.

Select one of two frequencies for the oscillator: 5.53 MHz or 32.8 kHz, using the OSCSEL bits described in the <u>Oscillator Control</u> chapter on page 151.

#### Hex Address: F74

#### Table 149. ADC Sample Settling Time (ADCSST)

| Bit     | 7        | 6 | 5 | 4 | 3   | 2  | 1 | 0 |  |

|---------|----------|---|---|---|-----|----|---|---|--|

| Field   | Reserved |   |   |   | SST |    |   |   |  |

| RESET   | 0        |   |   |   | 1   | 1  | 1 | 1 |  |

| R/W     | R        |   |   |   |     | R/ | W |   |  |

| Address | F74H     |   |   |   |     |    |   |   |  |

| Bit          | Description                                                                            |

|--------------|----------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.             |

| [3:0]<br>SST | Sample Settling Time<br>0h–Fh = Number of system clock periods to meet 0.5 μs minimum. |

## Hex Address: F75

## Table 150. ADC Sample Time (ADCST)

| Bit     | 7        | 6 | 5  | 4 | 3  | 2 | 1 | 0 |  |

|---------|----------|---|----|---|----|---|---|---|--|

| Field   | Reserved |   | ST |   |    |   |   |   |  |

| RESET   | 0        |   | 1  | 1 | 1  | 1 | 1 | 1 |  |

| R/W     | R/W      |   |    |   | R/ | W |   |   |  |

| Address | F75H     |   |    |   |    |   |   |   |  |

| Bit         | Description                                                                      |

|-------------|----------------------------------------------------------------------------------|

| [7:6]       | <b>Reserved</b><br>This register is reserved and must be programmed to 0.        |

| [5:0]<br>ST | Sample/Hold Time<br>0h–Fh = Number of system clock periods to meet 1 µs minimum. |

## Hex Addresses: F77–F7F

This address range is reserved.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

238

reload high and low byte registers 85 timer control register definitions 83 timer output signal operation 82 timers 0-3 control registers 87, 88 high and low byte registers 83, 86 TM 167 TMX 167 TRAP 169

## V

vector 165 voltage brown-out reset (VBR) 24 voltage measurement timing diagram 100

## W

watch-dog timer approximate time-out delay 92 approximate time-out delays 92, 106, 134, 151, 161 CNTL 24 control register 95, 154 electrical characteristics and timing 194 interrupt in noromal operation 93 interrupt in stop mode 93 operation 92, 106, 134, 151, 161 refresh 93 reload unlock sequence 94 reload upper, high and low registers 96 reset 25 reset in normal operation 94 reset in Stop mode 94 time-out response 93 watchdog timer refresh 168 WDTCTL register 29, 95, 107, 154, 217, 218, 226 WDTH register 96, 227 WDTL register 97, 227 working register 164 working register pair 165 WTDU register 96, 227

# Χ

X 165 XOR 169 XORX 169

# Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2