Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | -                                                         |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 17                                                        |  |

| Program Memory Size        | 8KB (8K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0831hh020sg |  |

# **Table of Contents**

| List of Tables       xi         Overview       xi         Features       Part Selection Guide         Block Diagram       20         CPU and Peripheral Overview       30         General Purpose Input/Output       40         Flash Controller       41         Nonvolatile Data Storage       41         Internal Precision Oscillator       51         External Crystal Oscillator       51         External Crystal Oscillator       51         Internal Precision Oscillator       51         Interrupt Controller       51         Analog Comparator       52         Interrupt Controller       52         Reset Controller       60         On-Chip Debugger       60         Acronyms and Expansions       60         Pin Description       60         Available Packages       7         Pin Configurations       7         Signal Descriptions       11         Address Space       12         Register File       14         Program Memory       15         Data Memory       16         Flash Information Area       16         Register Map       17 <t< th=""><th>Revision Historyii</th></t<>                                                                                                                                                                                                                                                      | Revision Historyii            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Overview Features Part Selection Guide Block Diagram CPU and Peripheral Overview General Purpose Input/Output Flash Controller Nonvolatile Data Storage Internal Precision Oscillator External Crystal Oscillator 10-Bit Analog-to-Digital Converter Analog Comparator Timers Interrupt Controller Reset Controller On-Chip Debugger Acronyms and Expansions Pin Description Available Packages Pin Configurations Signal Descriptions 1 Pin Characteristics 1 Address Space Register File Program Memory 1 Data Memory Flash Information Area Register Map Reset Types Reset Types 2 Reset Types 2 Reset Types 2 Reset Types 2 Reset Sources 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | List of Figures               |

| Features Part Selection Guide Block Diagram CPU and Peripheral Overview General Purpose Input/Output Flash Controller Nonvolatile Data Storage Internal Precision Oscillator External Crystal Oscillator 10-Bit Analog-to-Digital Converter Analog Comparator Timers Interrupt Controller Reset Controller On-Chip Debugger Acronyms and Expansions Pin Description Available Packages Pin Configurations Signal Descriptions 1 Pin Characteristics 1 Address Space Register File Program Memory 1 Data Memory Flash Information Area Reset and Stop Mode Recovery Reset Types Reset Types Reset Types Reset Sources 2 Reset Types Reset Sources 2 Reset Sources 2 Reset Sources 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | List of Tables                |

| Part Selection Guide         Block Diagram           CPU and Peripheral Overview         General Purpose Input/Output           Flash Controller         4           Nonvolatile Data Storage         Internal Precision Oscillator           External Crystal Oscillator         5           10-Bit Analog-to-Digital Converter         4           Analog Comparator         7           Timers         1           Interrupt Controller         6           Reset Controller         6           On-Chip Debugger         6           Acronyms and Expansions         6           Pin Description         7           Available Packages         7           Pin Configurations         7           Signal Descriptions         1           Pin Characteristics         1           Address Space         1           Register File         14           Program Memory         15           Data Memory         16           Flash Information Area         16           Reset and Stop Mode Recovery         2           Reset Types         2           Reset Sources         2                                                                                                                                                                                                                                                                                | Overview                      |

| Block Diagram CPU and Peripheral Overview General Purpose Input/Output Flash Controller Nonvolatile Data Storage Internal Precision Oscillator External Crystal Oscillator 10-Bit Analog-to-Digital Converter Analog Comparator Timers Interrupt Controller Reset Controller On-Chip Debugger Acronyms and Expansions Pin Description Available Packages Pin Configurations Signal Descriptions 1 Pin Characteristics 1 Register File Program Memory 1 Data Memory 1 Flash Information Area 1 Register Map Reset Types 2 Reset Types 1 Reset Types 2 Reset Types 2 Reset Types 2 Reset Sources 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Features                      |

| CPU and Peripheral Overview General Purpose Input/Output Flash Controller Nonvolatile Data Storage Internal Precision Oscillator External Crystal Oscillator 10-Bit Analog-to-Digital Converter Analog Comparator Timers Interrupt Controller Reset Controller On-Chip Debugger Acronyms and Expansions  Pin Description Available Packages Pin Configurations Signal Descriptions Signal Descriptions 1 Pin Characteristics 1 Address Space 1 Register File Program Memory Data Memory Flash Information Area  Register Map 1 Reset and Stop Mode Recovery Reset Types Reset Types Reset Sources 2 Reset Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Part Selection Guide          |

| General Purpose Input/Output       4         Flash Controller       4         Nonvolatile Data Storage       5         Internal Precision Oscillator       5         External Crystal Oscillator       6         10-Bit Analog-to-Digital Converter       6         Analog Comparator       7         Timers       7         Interrupt Controller       6         On-Chip Debugger       6         Acronyms and Expansions       6         Pin Description       7         Available Packages       7         Pin Configurations       7         Signal Descriptions       1         Pin Characteristics       1         Address Space       1         Register File       1         Program Memory       1         Data Memory       1         Flash Information Area       1         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Block Diagram                 |

| Flash Controller       4         Nonvolatile Data Storage       1         Internal Precision Oscillator       2         External Crystal Oscillator       10-Bit Analog-to-Digital Converter         Analog Comparator       2         Timers       3         Interrupt Controller       4         Reset Controller       6         On-Chip Debugger       6         Acronyms and Expansions       6         Pin Description       7         Available Packages       7         Pin Configurations       1         Signal Descriptions       1         Pin Characteristics       1         Address Space       14         Register File       14         Program Memory       15         Data Memory       10         Flash Information Area       16         Register Map       17         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CPU and Peripheral Overview   |

| Nonvolatile Data Storage       Internal Precision Oscillator         External Crystal Oscillator       20-Bit Analog-to-Digital Converter         Analog Comparator       3-Bit Analog-to-Digital Converter         Analog Comparator       3-Bit Analog-to-Digital Converter         Analog Comparator       3-Bit Analog-to-Digital Converter         Timers       3-Bit Analog-to-Digital Converter         Interrupt Controller       3-Bit Analog-to-Digital Converter         On-Chip Debugger       3-Bit Acronyms and Expansions         Pin Description       3-Bit Analog-to-Digital Converter         Available Packages       3-Bit Analog-to-Digital Converter         Pin Description       3-Bit Analog-to-Digital Converter         Available Packages       3-Bit Analog-to-Digital Converter         Pin Description       3-Bit Analog-to-Digital Converter         Available Packages       3-Bit Analog-to-Digital Converter         Pin Description       3-Bit Analog-to-Digital Converter         Available Packages       3-Bit Analog-to-Digital Converter         Pin Description       3-Bit Analog-to-Digital Converter         Acronyms and Expansions       4-Bit Analog-to-Digital Converter         Acronyms and Expansions       4-Bit Analog-to-Digital Converter         Pin Description       4-Bit Analog-to-Digital Converter | General Purpose Input/Output  |

| Internal Precision Oscillator         External Crystal Oscillator           10-Bit Analog-to-Digital Converter         Analog Comparator           Timers         Interrupt Controller           Reset Controller         On-Chip Debugger           Acronyms and Expansions         On-Chip Debugger           Acronyms and Expansions         On-Chip Debugger           Available Packages         Pin Configurations           Signal Descriptions         1           Pin Characteristics         1           Address Space         1           Register File         14           Program Memory         15           Data Memory         16           Flash Information Area         16           Register Map         17           Reset and Stop Mode Recovery         2           Reset Types         2           Reset Sources         25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Flash Controller              |

| External Crystal Oscillator  10-Bit Analog-to-Digital Converter Analog Comparator Timers Interrupt Controller Reset Controller On-Chip Debugger Acronyms and Expansions Pin Description Available Packages Pin Configurations Signal Descriptions 11 Pin Characteristics 12 Address Space Register File Program Memory Data Memory Flash Information Area  Register Map Reset and Stop Mode Recovery Reset Types Reset Types Reset Sources 22 Reset Sources 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Nonvolatile Data Storage      |

| External Crystal Oscillator  10-Bit Analog-to-Digital Converter Analog Comparator Timers Interrupt Controller Reset Controller On-Chip Debugger Acronyms and Expansions Pin Description Available Packages Pin Configurations Signal Descriptions 11 Pin Characteristics 12 Address Space Register File Program Memory Data Memory Flash Information Area  Register Map Reset and Stop Mode Recovery Reset Types Reset Types Reset Sources 22 Reset Sources 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Internal Precision Oscillator |

| 10-Bit Analog-to-Digital Converter       Analog Comparator         Timers       State of Controller         Reset Controller       On-Chip Debugger         Acronyms and Expansions       On-Chip Debugger         Pin Description       Available Packages         Pin Configurations       1         Signal Descriptions       1         Pin Characteristics       1         Address Space       1         Register File       1         Program Memory       1         Data Memory       1         Flash Information Area       1         Register Map       1         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |

| Analog Comparator       1         Timers       2         Interrupt Controller       3         Reset Controller       4         On-Chip Debugger       5         Acronyms and Expansions       6         Pin Description       7         Available Packages       7         Pin Configurations       1         Signal Descriptions       1         Pin Characteristics       1         Address Space       1         Register File       1         Program Memory       1         Data Memory       1         Flash Information Area       1         Register Map       1         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |

| Timers       Interrupt Controller         Reset Controller       6         On-Chip Debugger       6         Acronyms and Expansions       6         Pin Description       7         Available Packages       7         Pin Configurations       1         Signal Descriptions       1         Pin Characteristics       1         Address Space       1         Register File       14         Program Memory       12         Data Memory       16         Flash Information Area       16         Register Map       1         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |

| Interrupt Controller       Reset Controller         On-Chip Debugger       On-Chip Debugger         Acronyms and Expansions       On-Chip Debugger         Acronyms and Expansions       On-Chip Debugger         Pin Description       Available Packages         Pin Configurations       1         Signal Descriptions       1         Pin Characteristics       1         Address Space       1         Register File       1         Program Memory       1         Data Memory       1         Flash Information Area       1         Register Map       1         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |

| Reset Controller On-Chip Debugger Acronyms and Expansions  Pin Description Available Packages Pin Configurations Signal Descriptions 1 Pin Characteristics 1 Address Space 1 Register File Program Memory Data Memory 1 Flash Information Area 1 Register Map 1 Reset and Stop Mode Recovery Reset Types Reset Sources 2 Reset Sources 2 2 Reset Sources 2 2 2 2 2 3 3 4 3 4 4 5 6 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |

| On-Chip Debugger Acronyms and Expansions  Pin Description Available Packages Pin Configurations Signal Descriptions 1 Pin Characteristics 1 Address Space 14 Register File 14 Program Memory 15 Data Memory 16 Flash Information Area 16 Register Map 17 Reset and Stop Mode Recovery Reset Types 2 Reset Sources 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |

| Acronyms and Expansions       6         Pin Description       7         Available Packages       7         Pin Configurations       1         Signal Descriptions       1         Pin Characteristics       1         Address Space       1         Register File       1         Program Memory       1         Data Memory       1         Flash Information Area       1         Register Map       1         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |

| Pin Description Available Packages Pin Configurations Signal Descriptions Pin Characteristics 12 Address Space Register File Program Memory Data Memory Flash Information Area 16 Register Map 17 Reset and Stop Mode Recovery Reset Types Reset Sources 22 Reset Sources 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |

| Available Packages Pin Configurations Signal Descriptions Pin Characteristics 1 Address Space Register File Program Memory Data Memory Flash Information Area 1 Register Map 1 Reset and Stop Mode Recovery Reset Types Reset Sources 2 2 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                             |

| Pin Configurations7Signal Descriptions1Pin Characteristics1Address Space14Register File12Program Memory15Data Memory16Flash Information Area16Register Map17Reset and Stop Mode Recovery2Reset Types2Reset Sources2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                               |

| Signal Descriptions1Pin Characteristics1Address Space14Register File14Program Memory15Data Memory16Flash Information Area16Register Map17Reset and Stop Mode Recovery2Reset Types2Reset Sources2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u> </u>                      |

| Pin Characteristics15Address Space14Register File14Program Memory15Data Memory16Flash Information Area16Register Map17Reset and Stop Mode Recovery2Reset Types2Reset Sources2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               |

| Address Space       12         Register File       12         Program Memory       15         Data Memory       16         Flash Information Area       16         Register Map       17         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                             |

| Register File       14         Program Memory       15         Data Memory       16         Flash Information Area       16         Register Map       17         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Characteristics           |

| Register File       14         Program Memory       15         Data Memory       16         Flash Information Area       16         Register Map       17         Reset and Stop Mode Recovery       2         Reset Types       2         Reset Sources       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Address Space                 |

| Data Memory 10 Flash Information Area 110 Register Map 117 Reset and Stop Mode Recovery 21 Reset Types 22 Reset Sources 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Register File                 |

| Flash Information Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Program Memory                |

| Flash Information Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Data Memory                   |

| Reset and Stop Mode Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |

| Reset Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Register Map                  |

| Reset Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reset and Stop Mode Recovery  |

| Reset Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • •                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                               |

PS025113-1212 Table of Contents

### Z8 Encore!® F0830 Series Product Specification

xiii

| Table 29. | Port A–C Input Data Registers (PxIN)            |

|-----------|-------------------------------------------------|

| Table 30. | Port A–D Output Data Register (PxOUT)           |

| Table 31. | LED Drive Enable (LEDEN)                        |

| Table 32. | LED Drive Level High Register (LEDLVLH)         |

| Table 33. | LED Drive Level Low Register (LEDLVLL)          |

| Table 34. | Trap and Interrupt Vectors in Order of Priority |

| Table 35. | Interrupt Request 0 Register (IRQ0)             |

| Table 36. | Interrupt Request 1 Register (IRQ1)             |

| Table 37. | Interrupt Request 2 Register (IRQ2) 60          |

| Table 38. | IRQ0 Enable and Priority Encoding 60            |

| Table 39. | IRQ0 Enable Low Bit Register (IRQ0ENL)          |

| Table 40. | IRQ0 Enable High Bit Register (IRQ0ENH)         |

| Table 41. | IRQ1 Enable and Priority Encoding               |

| Table 42. | IRQ1 Enable High Bit Register (IRQ1ENH)         |

| Table 43. | IRQ2 Enable and Priority Encoding               |

| Table 44. | IRQ1 Enable Low Bit Register (IRQ1ENL)          |

| Table 45. | IRQ2 Enable Low Bit Register (IRQ2ENL)          |

| Table 46. | IRQ2 Enable High Bit Register (IRQ2ENH)         |

| Table 47. | Interrupt Edge Select Register (IRQES)          |

| Table 48. | Shared Interrupt Select Register (IRQSS)        |

| Table 49. | Interrupt Control Register (IRQCTL)             |

| Table 50. | Timer 0–1 High Byte Register (TxH)              |

| Table 51. | Timer 0–1 Low Byte Register (TxL)               |

| Table 52. | Timer 0–1 Reload High Byte Register (TxRH)      |

| Table 53. | Timer 0–1 Reload Low Byte Register (TxRL)       |

| Table 54. | Timer 0–1 PWM High Byte Register (TxPWMH)       |

| Table 55. | Timer 0–1 PWM Low Byte Register (TxPWML)        |

| Table 56. | Timer 0–1 Control Register 0 (TxCTL0)           |

| Table 57. | Timer 0–1 Control Register 1 (TxCTL1)           |

| Table 58. | Watchdog Timer Approximate Time-Out Delays      |

PS025113-1212 List of Tables

### **Stop Mode Recovery Using the External RESET Pin**

When the Z8 Encore! F0830 Series device is in STOP Mode and the external RESET pin is driven low, a system reset occurs. Because of a glitch filter operating on the RESET pin, the low pulse must be greater than the minimum width specified about 12 ns or it is ignored. The EXT bit in the Reset Status (RSTSTAT) Register is set.

### **Debug Pin Driven Low**

Debug reset is initiated when the On-Chip Debugger detects any of the following error conditions on the DBG pin:

- Serial break (a minimum of nine continuous bits Low)

- Framing error (received STOP bit is Low)

- Transmit collision (simultaneous OCD and host transmission detected by the OCD)

When the Z8F0830 Series device is operating in STOP Mode, the debug reset will cause a system reset. The On-Chip Debugger block is not reset, but the remainder of the chip's operations go through a normal system reset. The POR bit in the Reset Status (RSTSTAT) Register is set to 1.

### **Reset Register Definitions**

The following sections define the Reset registers.

#### **Reset Status Register**

The Reset Status (RSTSTAT) Register, shown in Table 12, is a read-only register that indicates the source of the most recent Reset event, Stop Mode Recovery event or Watchdog Timer time-out event. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer Control Register, which is write-only.

## **Timers**

The Z8 Encore! F0830 Series products contain up to two 16-bit reloadable timers that can be used for timing, event counting or generation of pulse width modulated (PWM) signals. The timers feature include:

- 16-bit reload counter

- Programmable prescaler with prescale values ranging from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

#### **Architecture**

Figure 10 displays the architecture of the timers.

PS025113-1212 Timers

### **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

<u>Timer 0–1 High and Low Byte Registers</u>: see page 83

Timer Reload High and Low Byte Registers: see page 85

<u>Timer 0–1 PWM High and Low Byte Registers</u>: see page 86

Timer 0–1 Control Registers: see page 87

#### Timer 0-1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers, shown in Tables 50 and 51, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register content when the timer is enabled; however, when the timer is disabled, a read from the TxL reads the TxL Register content directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations; therefore, simultaneous 16-bit writes are not possible. If either the timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low byte) at the next clock edge. The counter continues counting from the new value.

Table 50. Timer 0–1 High Byte Register (TxH)

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   | TH  |            |     |     |     |     |     |     |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F00H, F08H |     |     |     |     |     |     |

Table 51. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TL         |     |     |     |     |     |     |     |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F01H, F09H |     |     |     |     |     |     |     |

#### Bit Description (Continued)

#### [6] PWM DUAL OUTPUT Mode

# TPOL (cont'd)

- 0 = Timer output is forced Low (0) and timer output complement is forced High (1), when the timer is disabled. When enabled and the PWM count matches, the timer output is forced High (1) and forced Low (0) when enabled and reloaded. When enabled and the PWM count matches, the timer output complement is forced Low (0) and forced High (1) when enabled and reloaded.

- 1 = Timer output is forced High (1) and timer output complement is forced Low (0) when the timer is disabled. When enabled and the PWM count matches, the timer output is forced Low (0) and forced High (1) when enabled and reloaded. When enabled and the PWM count matches, the timer output complement is forced High (1) and forced Low (0) when enabled and reloaded. The PWMD field in the TxCTL0 register determines an optional added delay on the assertion (Low to High) transition of both timer output and timer output complement for deadband generation.

#### **CAPTURE RESTART Mode**

- 0 = Count is captured on the rising edge of the timer input signal.

- 1 = Count is captured on the falling edge of the timer input signal.

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the timer output signal is set to the value of this bit. When the timer is enabled, the timer output signal is complemented on timer reload.

**Caution:** When the timer output alternate function TxOUT on a GPIO port pin is enabled, TxOUT will change to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Additionally, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit when the timer is enabled and running does not immediately change the polarity TxOUT.

#### [5:3] **Prescale Value**

#### **PRES**

The timer input clock is divided by 2<sup>PRES</sup>, where PRES can be set from 0 to 7. The prescaler is reset each time the timer is disabled. This reset ensures proper clock division each time the timer is restarted.

- 000 = Divide by 1.

- 001 = Divide by 2.

- 010 = Divide by 4.

- 011 = Divide by 8.

- 100 = Divide by 16.

- 101 = Divide by 32.

- 110 = Divide by 64.

- 111 = Divide by 128.

| Bit   | Description (Continued)                                                                |  |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| [2:0] | Timer Mode                                                                             |  |  |  |  |  |  |  |

| TMODE | This field along with the TMODEHI bit in TxCTL0 register determines the operating mode |  |  |  |  |  |  |  |

|       | the timer. TMODEHI is the most significant bit of the timer mode selection value.      |  |  |  |  |  |  |  |

|       | 0000 = ONE-SHOT Mode.                                                                  |  |  |  |  |  |  |  |

|       | 0001 = CONTINUOUS Mode.                                                                |  |  |  |  |  |  |  |

|       | 0010 = COUNTER Mode.                                                                   |  |  |  |  |  |  |  |

|       | 0011 = PWM SINGLE OUTPUT Mode.                                                         |  |  |  |  |  |  |  |

|       | 0100 = CAPTURE Mode.                                                                   |  |  |  |  |  |  |  |

|       | 0101 = COMPARE Mode.                                                                   |  |  |  |  |  |  |  |

|       | 0110 = GATED Mode.                                                                     |  |  |  |  |  |  |  |

|       | 0111 = CAPTURE/COMPARE Mode.                                                           |  |  |  |  |  |  |  |

|       | 1000 = PWM DUAL OUTPUT Mode.                                                           |  |  |  |  |  |  |  |

|       | 1001 = CAPTURE RESTART Mode.                                                           |  |  |  |  |  |  |  |

|       | 1010 = COMPARATOR COUNTER Mode.                                                        |  |  |  |  |  |  |  |

### Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 60 through 62, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. This 24-bit value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate reload value; reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

Table 60. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit          | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Field        | WDTU                                                                                          |      |      |      |      |      |      |      |

| RESET        | 0                                                                                             | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W          | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |

| Address FF1H |                                                                                               |      |      |      |      |      |      |      |

| Note: *A re  | Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

Table 61. Watchdog Timer Reload High Byte Register (WDTH)

| Bit          | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Field        | WDTH                                                                                          |      |      |      |      |      |      |      |

| RESET        | 0                                                                                             | 0    | 0    | 0    | 0    | 1    | 0    | 0    |

| R/W          | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |

| Address FF2H |                                                                                               |      |      |      |      |      |      |      |

| Note: *A re  | Note: *A read returns the current WDT count value; a write sets the appropriate reload value. |      |      |      |      |      |      |      |

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte, bits[15:8] of the 24-bit WDT reload value. |

# Flash Option Bits

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! F0830 Series operation. The feature configuration data is stored in the Flash program memory and read during reset. The features available for control through the Flash option bits are:

- Watchdog Timer time-out response selection–interrupt or system reset

- Watchdog Timer enabled at reset

- The ability to prevent unwanted read access to user code in program memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in program memory

- Voltage Brown-Out configuration always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- OSCILLATOR Mode selection for high, medium and low power crystal oscillators or external RC oscillator

- Factory trimming information for the Internal Precision Oscillator and VBO voltage

### **Operation**

This section describes the type and configuration of the programmable Flash option bits.

### **Option Bit Configuration by Reset**

Each time the Flash option bits are programmed or erased, the device must be reset for the change to be effective. During any Reset operation (system reset or Stop Mode Recovery), the Flash option bits are automatically read from Flash program memory and written to the Option Configuration registers, which control Z8 Encore! F0830 Series device operation. Option bit control is established before the device exits reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the register file and are not accessible for read or write access.

PS025113-1212 Flash Option Bits

#### **Power Failure Protection**

NVDS routines employ error-checking mechanisms to ensure that any power failure will only endanger the most recently written byte. Bytes previously written to the array are not perturbed. For this protection to function, the VBO must be enabled (see the <u>Low-Power Modes</u> chapter on page 30) and configured for a threshold voltage of 2.4V or greater (see *the* <u>Trim Bit Address Space</u> *section on page 129*).

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

### **Optimizing NVDS Memory Usage for Execution Speed**

As indicated in Table 93, the NVDS read time varies drastically; this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N as well as the number of writes since the most recent page erase. Neglecting the effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb to consider is that every write since the most recent page erase causes read times of unwritten addresses to increase by  $0.8\mu s$  up to a maximum of  $258\mu s$ .

Table 93. NVDS Read Time

| Operation     | Minimum<br>Latency (µs) | Maximum<br>Latency (µs) |

|---------------|-------------------------|-------------------------|

| Read          | 71                      | 258                     |

| Write         | 126                     | 136                     |

| Illegal Read  | 6                       | 6                       |

| Illegal Write | 7                       | 7                       |

Note:

For every 200 writes, a maintenance operation is necessary. In this rare occurrence, the write takes up to 58ms to complete.

If NVDS read performance is critical to your software architecture, you can optimize your code for speed by using either of the two methods listed below.

1. Periodically refresh all addresses that are used; this is the more useful method. The optimal use of NVDS, in terms of speed, is to rotate the writes evenly among all addresses planned for use, thereby bringing all reads closer to the minimum read time.

PS025113-1212 NVDS Code Interface

Table 98. Oscillator Configuration and Selection

| Clock Source                          | Characteristics                                                                                                                                | Required Setup                                                                                                                                                                                                                                                                  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal precision<br>RC oscillator   | <ul> <li>32.8 kHz or 5.53MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>                           | Unlock and write to the Oscillator Control Register (OSCCTL) to enable and select oscillator at either 5.53MHz or 32.8 kHz                                                                                                                                                      |

| External crystal/resonator            | <ul> <li>32 kHz to 20MHz</li> <li>Very high accuracy (dependent on crystal or resonator used)</li> <li>Requires external components</li> </ul> | <ul> <li>Configure Flash option bits for correct external OSCILLATOR Mode</li> <li>Unlock and write OSCCTL to enable crystal oscillator, wait for it to stabilize and select as system clock (if the XTLDIS option bit has been de-asserted, no waiting is required)</li> </ul> |

| External RC oscillator                | <ul> <li>32 kHz to 4MHz</li> <li>Accuracy dependent on external components</li> </ul>                                                          | <ul> <li>Configure Flash option bits for correct external OSCILLATOR Mode</li> <li>Unlock and write OSCCTL to enable crystal oscillator and select as system clock</li> </ul>                                                                                                   |

| External clock drive                  | 0 to 20MHz     Accuracy dependent on external clock source                                                                                     | <ul> <li>Write GPIO registers to configure PB3</li> <li>r- pin for external clock function</li> <li>Unlock and write OSCCTL to select external system clock</li> <li>Apply external clock signal to GPIO</li> </ul>                                                             |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Low power consumption</li> </ul>                     | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT oscillator is operating.</li> <li>Unlock and write to the Oscillator Control Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>                                                                         |

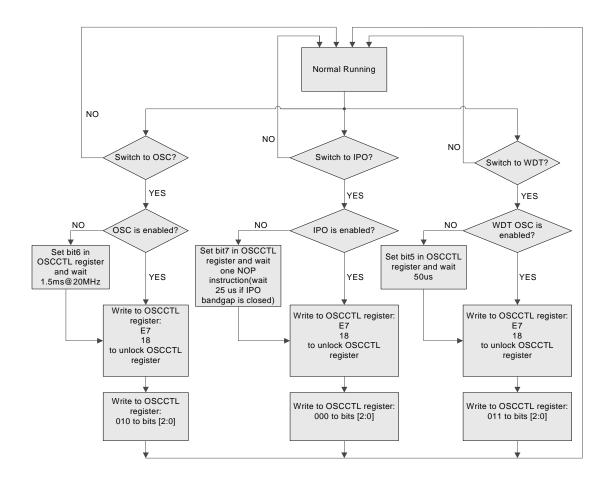

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a nonfunctioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

#### **OSC Control Register Unlocking/Locking**

To write the Oscillator Control Register, unlock it by making two writes to the OSCCTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a Locked state. Any other sequence of Oscillator Control Register writes have no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

PS025113-1212 Operation

Caution: It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! F0830 Series device ceases functioning and can only be recovered by power-on-reset.

### **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control Register.

#### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

Figure 24 displays the oscillator control clock switching flow. See <u>Table 117</u> on page 189 to review the waiting times of various oscillator circuits.

Table 99. Oscillator Control Register (OSCCTL)

| Bit     | 7     | 6     | 5     | 4     | 3     | 2      | 1   | 0   |  |  |  |

|---------|-------|-------|-------|-------|-------|--------|-----|-----|--|--|--|

| Field   | INTEN | XTLEN | WDTEN | POFEN | WDFEN | SCKSEL |     |     |  |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0      | 0   | 0   |  |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W    | R/W | R/W |  |  |  |

| Address |       | F86H  |       |       |       |        |     |     |  |  |  |

| Bit          | Description                                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INTEN | Internal Precision Oscillator Enable  1 = Internal Precision Oscillator is enabled.  0 = Internal Precision Oscillator is disabled.                                  |

| [6]<br>XTLEN | Crystal Oscillator Enable This setting overrides the GPIO register control for PA0 and PA1.  1 = Crystal oscillator is enabled.  0 = Crystal oscillator is disabled. |

| [5]<br>WDTEN | Watchdog Timer Oscillator Enable  1 = Watchdog Timer Oscillator is enabled.  0 = Watchdog Timer Oscillator is disabled.                                              |

Figure 24. Oscillator Control Clock Switching Flow Chart

#### **Assembly Language Source Program Example**

; Everything after the semicolon is a comment. JP START START: ; A label called "START". The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs. ; A Load (LD) instruction with two operands. The first operand, LD R4, R7 : Working register R4, is the destination. The second operand. ; Working register R7, is the source. The contents of R7 is ; written into R4. ; Another Load (LD) instruction with two operands. LD 234H, #%01 ; The first operand, extended mode register Address 234H, ; identifies the destination. The second operand, immediate data : value 01H, is the source. The value 01H is written into the ; register at address 234H.

### **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as *destination*, *source*. After assembly, the object code usually reflects the operands in the order *source*, *destination*, but ordering is op code-dependent.