Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0831hj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

29

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                        | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---|----|----|---|---|---|--|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                           | OR STOP WDT EXT Reserved |   |    |    |   |   |   |  |

| RESET       | :                                                                                                                                                                                                                                                                                                                                                                                                                                             | See Table 13             | 3 | 0  | 0  | 0 | 0 | 0 |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                        | R | R  | R  | R | R | R |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |   | FF | ОH |   |   |   |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                    | n                        |   |    |    |   |   |   |  |

| [7]<br>POR  | <b>Power-On Reset Indicator</b><br>This bit is set to 1 if a Power-On Reset event occurs and is reset to 0, if a WDT time-out or Stop<br>Mode Recovery occurs. Reading this register also reset this bit to 0.                                                                                                                                                                                                                                |                          |   |    |    |   |   |   |  |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>This bit is set to 1 if a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery is not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |                          |   |    |    |   |   |   |  |

| [5]<br>WDT  | Watchdog Timer Time-Out Indicator<br>This bit is set to 1 if a WDT time-out occurs. A Power-On Reset resets this pin. A Stop Mode<br>Recovery from a change in an input pin also resets this bit. Reading this register resets this bit.<br>This read must occur before clearing the WDT interrupt.                                                                                                                                           |                          |   |    |    |   |   |   |  |

| [4]<br>EXT  | <b>External Reset Indicator</b><br>If this bit is set to 1, a reset initiated by the external RESET pin occurred. A Power-On Reset or<br>a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                                                                                                                                                                        |                          |   |    |    |   |   |   |  |

| [3:0]       | Reserved<br>These registers are reserved and must be programmed to 0000.                                                                                                                                                                                                                                                                                                                                                                      |                          |   |    |    |   |   |   |  |

#### Table 13. POR Indicator Values

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out                 | 0   | 1    | 1   | 0   |

#### Port A–D Pull-up Enable Subregisters

The Port A–D Pull-Up Enable Subregister is accessed through the Port A–D Control Register by writing 06H to the Port A–D Address Register. See Table 26. Setting the bits in the Port A–D Pull-Up Enable subregisters enables a weak internal resistive pull-up on the specified port pins.

| Bit     | 1                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Field   | PPUE7                                                                                 | PPUE6 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |       |

#### Table 26. Port A–D Pull-Up Enable Subregisters (PxPUE)

| Bit       | Description                                       |

|-----------|---------------------------------------------------|

| [7:0]     | Port Pull-Up Enable                               |

| PxPUE     | 0 = The weak pull-up on the port pin is disabled. |

|           | 1 = The weak pull-up on the port pin is enabled.  |

| Note: x i | ndicates the specific GPIO port pin number (7–0). |

# **Timers**

The Z8 Encore! F0830 Series products contain up to two 16-bit reloadable timers that can be used for timing, event counting or generation of pulse width modulated (PWM) signals. The timers feature include:

- 16-bit reload counter

- Programmable prescaler with prescale values ranging from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

### Architecture

Figure 10 displays the architecture of the timers.

reload. For the timer output to make a state change at a ONE-SHOT time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode

- Set the prescale value

- Set the initial output level (High or Low) if using the timer output Alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the timer output function, configure the associated GPIO port pin for the timer output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is calculated with the following equation:

One-Shot Mode Time-Out Period (s) =  $\frac{(\text{Reload Value} - \text{Start Value}) \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and the counting resumes. Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) at timer reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and for initiating the count:

1. Write to the Timer Control Register to:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output high time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$$

#### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the capture occurs on a rising edge or a falling edge of the timer input signal.

When the capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in the TxCTL1 Register is set to indicate the timer interrupt because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in the TxCTL1 Register clears, indicating that the timer interrupt has not occurred because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the timer PWM High and Low Byte registers to 0000H. Clearing these registers allows user software to determine if interrupts were generated either by a capture event or by a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt were generated by a reload.

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external timer input transition occurs. The capture count value is written to the timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines whether the capture occurs on a rising edge or a falling edge of the timer input signal. When the capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is set to indicate that the timer interrupt has been caused by an input capture event.

If no capture event occurs, the timer counts up to 16-bit compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in the TxCTL1 Register is cleared to indicate that the timer interrupt has not been caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode; setting the mode also involves writing to TMODEHI bit in the TxCTL1 Register

- Set the prescale value

- Set the capture edge (rising or falling) for the timer input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

### Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 54 and 55, control PWM operations. These registers also store the capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | PWMH       |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | F04H, F0CH |     |     |     |     |     |     |  |  |

#### Table 54. Timer 0–1 PWM High Byte Register (TxPWMH)

#### Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | PWML       |     |     |     |     |     |     |     |  |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F05H, F0DH |     |     |     |     |     |     |     |  |

#### Bit Description

| [7:0] | Pulse Width Modulator High and Low Bytes                                                     |

|-------|----------------------------------------------------------------------------------------------|

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1).                         |

|       | The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operat-      |

|       | ing in capture or CAPTURE/COMPARE modes.                                                     |

### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

| 1FFFH          |           | <br>Page 15 | 1FFFH<br>1E00H |

|----------------|-----------|-------------|----------------|

|                | Sector 7  | Page 14     | 1DFFH<br>1C00H |

| 1C00H<br>18FFH |           | <br>Page 13 | 1BFFH<br>1A00H |

|                | Sector 6  | <br>Page 12 | 19FFH<br>1800H |

| 1800H<br>17FFH |           | <br>Page 11 | 17FFH<br>1600H |

| 1400H          | Sector 5  | <br>Page 10 | 15FFH<br>1400H |

| 13FFH          |           | <br>Page 9  | 13FFH<br>1200H |

|                | Sector 4  | <br>Page 8  | 11FFH          |

| 1C00H<br>0FFFH | Sector 3  | <br>Page 7  | 1C00H<br>0FFFH |

| 0C00H          | Seciol 3  | Page 6      | 0E00H<br>0DFFH |

| 0BFFH          | On star 0 | <br>Page 5  | 0C00H<br>0BFFH |

| 0800H          | Sector 2  | <br>Page 4  | 0A00H<br>09FFH |

| 07FFH          | Sector 1  | Page 3      | 0800H<br>07FFH |

| 0400H          | Sector    | <br>Page 2  | 0600H<br>05FFH |

| 03FFH          | Sector 0  | Page 1      | 0400H<br>03FFH |

| 0000H          |           | <br>Page 0  | 0200H<br>0100H |

|                |           |             | 0000H          |

Figure 17. 8K Flash with NVDS

110

### Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

### Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

### **Flash Sector Protect Register**

The Flash Sector Protect Register is shared with the Flash Page Select Register. When the Flash Control Register is locked and written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the eight available Flash memory sectors to be protected. The Reset state of each sector protect bit is the zero (unprotected) state. After a sector is protected by setting its corresponding register bit, the register bit cannot be cleared by the user.

To determine the appropriate Flash memory sector address range and sector number for your F0830 Series product, please refer to <u>Table 70</u> on page 112.

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |  |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address |        | FF9H   |        |        |        |        |        |        |  |  |

| Table 75. | Flash | Sector | Protect | Register | (FPROT) |

|-----------|-------|--------|---------|----------|---------|

|-----------|-------|--------|---------|----------|---------|

#### Bit Description

#### [7:0] Sector Protection

SPROT*x* For Z8F12xx, Z8F08xx and Z8F04xx devices, all bits are used. For Z8F02xx devices, the upper four bits remain unused. For Z8F01xx devices, the upper six bits remain unused. To determine the appropriate Flash memory sector address range and sector number for your F0830 Series product, please refer to Table 69 and to Figures 14 through 18.

Note: x indicates bits in the range 7–0.

ory size and is approximately equal to the system clock period multiplied by the number of bytes in program memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

**Step Instruction (10H).** The step instruction command, steps one assembly instruction at the current program counter (PC) location. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 10H

```

**Stuff Instruction (11H).** The stuff instruction command, steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0–4 bytes of the instruction are read from program memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a breakpoint. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The execute instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG Mode or the Flash read protect option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

### **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

### **OCD Control Register**

The OCD Control Register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It can also reset the Z8 Encore! F0830 Series device.

A reset and stop function can be achieved by writing 81H to this register. A *reset and go* function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

| Bit             | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>POFEN    | <ul> <li>Primary Oscillator Failure Detection Enable</li> <li>1 = Failure detection and recovery of primary oscillator is enabled.</li> <li>0 = Failure detection and recovery of primary oscillator is disabled.</li> </ul>                                                                                                                                                                                                                                     |

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable<br>1 = Failure detection of Watchdog Timer Oscillator is enabled.<br>0 = Failure detection of Watchdog Timer Oscillator is disabled.                                                                                                                                                                                                                                                                          |

| [2:0]<br>SCKSEL | System Clock Oscillator Select<br>000 = Internal Precision Oscillator functions as system clock at 5.53MHz.<br>001 = Internal Precision Oscillator functions as system clock at 32 kHz.<br>010 = Crystal oscillator or external RC oscillator functions as system clock.<br>011 = Watchdog Timer Oscillator functions as system clock.<br>100 = External clock signal on PB3 functions as system clock.<br>101 = Reserved.<br>110 = Reserved.<br>111 = Reserved. |

#### Example 2

In general, when an instruction format requires an 8-bit register address, the address can specify any register location in the range 0–255 or, using escaped mode addressing, a working register R0–R15. If the contents of register 43H and working register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 102. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device specific product specification to determine the exact register file range available. The register file size varies, depending on the device type.

### eZ8 CPU Instruction Notation

In the eZ8 CPU instruction summary and description sections, the operands, condition codes, status flags and address modes are represented by the notational shorthand listed in Table 103.

| Notation | Description                    | Operand | Range                                                     |

|----------|--------------------------------|---------|-----------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).          |

| CC       | Condition Code                 | —       | See condition codes overview in the eZ8 CPU User Manual.  |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH     |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                       |

| lr       | Indirect Working Register      | @Rn     | n = 0 –15                                                 |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH       |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12 or 14                           |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH    |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B. |

| r        | Working Register               | Rn      | n = 0 – 15                                                |

#### Table 103. Notational Shorthand

| Assembly         |                                                                                           | Address<br>Mode |     | On    |   |   | Fla | ags | Fetch | Instr. |   |   |

|------------------|-------------------------------------------------------------------------------------------|-----------------|-----|-------|---|---|-----|-----|-------|--------|---|---|

| Mnemonic         | Symbolic Operation                                                                        | dst             | src | (Hex) | С | Ζ | S   | ۷   | D     | Н      |   |   |

| AND dst, src     | $dst \gets dst \; AND \; src$                                                             | r               | r   | 52    | _ | * | *   | 0   | _     | _      | 2 | 3 |

|                  |                                                                                           | r               | lr  | 53    | _ |   |     |     |       |        | 2 | 4 |

|                  |                                                                                           | R               | R   | 54    |   |   |     |     |       |        | 3 | 3 |

|                  |                                                                                           | R               | IR  | 55    | _ |   |     |     |       |        | 3 | 4 |

|                  |                                                                                           | R               | IM  | 56    | _ |   |     |     |       |        | 3 | 3 |

|                  |                                                                                           | IR              | IM  | 57    | _ |   |     |     |       |        | 3 | 4 |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER              | ER  | 58    | _ | * | *   | 0   | _     | _      | 4 | 3 |

|                  |                                                                                           | ER              | IM  | 59    | _ |   |     |     |       |        | 4 | 3 |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions |                 |     | 2F    | - | _ | _   | _   | _     | _      | 1 | 2 |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r               |     | E2    | _ | * | *   | 0   | _     | _      | 2 | 2 |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r               |     | E2    | _ | * | *   | 0   | _     | _      | 2 | 2 |

| BRK              | Debugger Break                                                                            |                 |     | 00    | - | _ | -   | -   | _     | _      | 1 | 1 |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r               |     | E2    | - | * | *   | 0   | -     | -      | 2 | 2 |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R               |     | D5    | Х | * | *   | 0   | -     | -      | 2 | 2 |

| BTJ p, bit, src, | if src[bit] = p                                                                           |                 | r   | F6    | - | _ | -   | -   | _     | _      | 3 | 3 |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7    | _ |   |     |     |       |        | 3 | 4 |

| BTJNZ bit, src,  |                                                                                           |                 | r   | F6    | - | - | -   | -   | -     | -      | 3 | 3 |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7    | _ |   |     |     |       |        | 3 | 4 |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |                 | r   | F6    | _ | - | _   | _   | -     | -      | 3 | 3 |

| dst              | $PC \gets PC + X$                                                                         |                 | Ir  | F7    |   |   |     |     |       |        | 3 | 4 |

| CALL dst         | $SP \leftarrow SP -\!\!\!\!\!-\!\!\!\!\!2$                                                | IRR             |     | D4    | _ | _ | -   | -   | _     | -      | 2 | 6 |

|                  | @SP ← PC<br>PC ← dst                                                                      | DA              |     | D6    |   |   |     |     |       |        | 3 | 3 |

| CCF              | $C \leftarrow \sim C$                                                                     |                 |     | EF    | * | _ | _   | _   | _     |        | 1 | 2 |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Assembly      |                          |      | ress<br>ode | Op<br>Code(s) |   |   | Fla | ags |   |   | Fetch | Instr. |

|---------------|--------------------------|------|-------------|---------------|---|---|-----|-----|---|---|-------|--------|

| Mnemonic      | Symbolic Operation       | dst  | src         | (Hex)         | С | Ζ | S   | ۷   | D | Н |       |        |

| LD dst, rc    | dst ← src                | r    | IM          | 0C-FC         | _ | - | -   | _   | - | _ | 2     | 2      |

|               |                          | r    | X(r)        | C7            | _ |   |     |     |   |   | 3     | 3      |

|               |                          | X(r) | r           | D7            | _ |   |     |     |   |   | 3     | 4      |

|               |                          | r    | lr          | E3            | _ |   |     |     |   |   | 2     | 3      |

|               |                          | R    | R           | E4            | _ |   |     |     |   |   | 3     | 2      |

|               |                          | R    | IR          | E5            | _ |   |     |     |   |   | 3     | 4      |

|               |                          | R    | IM          | E6            | _ |   |     |     |   |   | 3     | 2      |

|               |                          | IR   | IM          | E7            | _ |   |     |     |   |   | 3     | 3      |

|               |                          | lr   | r           | F3            | _ |   |     |     |   |   | 2     | 3      |

|               |                          | IR   | R           | F5            | _ |   |     |     |   |   | 3     | 3      |

| LDC dst, src  | dst ← src                | r    | Irr         | C2            | _ | _ | _   | _   | _ | - | 2     | 5      |

|               |                          | lr   | Irr         | C5            | _ |   |     |     |   |   | 2     | 9      |

|               |                          | Irr  | r           | D2            | _ |   |     |     |   |   | 2     | 5      |

| LDCI dst, src | dst ← src                | lr   | Irr         | C3            | - | - | -   | -   | - | - | 2     | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | D3            |   |   |     |     |   |   | 2     | 9      |

| LDE dst, src  | dst ← src                | r    | Irr         | 82            | _ | _ | _   | _   | _ | - | 2     | 5      |

|               |                          | Irr  | r           | 92            | _ |   |     |     |   |   | 2     | 5      |

| LDEI dst, src | dst ← src                | lr   | Irr         | 83            | _ | _ | _   | _   | _ | _ | 2     | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | 93            |   |   |     |     |   |   | 2     | 9      |

| LDWX dst, src | dst ← src                | ER   | ER          | 1FE8          | - | _ | _   | _   | _ | _ | 5     | 4      |

#### Table 113. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

### **General Purpose I/O Port Output Timing**

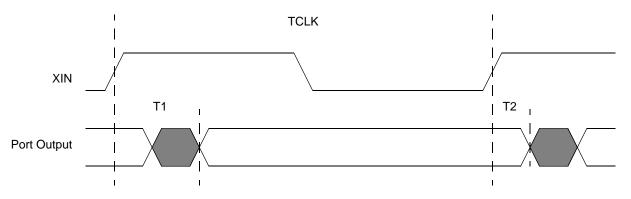

Figure 34 and Table 125 provide timing information for the GPIO port pins.

|                |                                     | Dela    | y (ns)  |

|----------------|-------------------------------------|---------|---------|

| Parameter      | Abbreviation                        | Minimum | Maximum |

| GPIO Port F    | Pins                                |         |         |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _       | 15      |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2       | _       |

#### Table 125. GPIO Port Output Timing

#### Hex Address: F74

#### Table 149. ADC Sample Settling Time (ADCSST)

| Bit     | 7 | 6     | 5     | 4 | 3   | 2 | 1 | 0 |  |

|---------|---|-------|-------|---|-----|---|---|---|--|

| Field   |   | Rese  | erved |   | SST |   |   |   |  |

| RESET   |   | (     | )     |   | 1   | 1 | 1 | 1 |  |

| R/W     |   | R R/W |       |   |     |   |   |   |  |

| Address |   | F74H  |       |   |     |   |   |   |  |

| Bit          | Description                                                                                   |

|--------------|-----------------------------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                    |

| [3:0]<br>SST | <b>Sample Settling Time</b><br>0h–Fh = Number of system clock periods to meet 0.5 μs minimum. |

#### Hex Address: F75

#### Table 150. ADC Sample Time (ADCST)

| Bit     | 7    | 6     | 5    | 4   | 3 | 2 | 1 | 0 |  |  |  |

|---------|------|-------|------|-----|---|---|---|---|--|--|--|

| Field   | Rese | erved | ST   |     |   |   |   |   |  |  |  |

| RESET   | (    | )     | 1    | 1   | 1 | 1 | 1 | 1 |  |  |  |

| R/W     | R/   | W     |      | R/W |   |   |   |   |  |  |  |

| Address |      |       | F75H |     |   |   |   |   |  |  |  |

| Bit         | Description                                                                      |

|-------------|----------------------------------------------------------------------------------|

| [7:6]       | <b>Reserved</b><br>This register is reserved and must be programmed to 0.        |

| [5:0]<br>ST | Sample/Hold Time<br>0h–Fh = Number of system clock periods to meet 1 µs minimum. |

#### Hex Addresses: F77–F7F

This address range is reserved.

#### Hex Address: FD7

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |  |  |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |  |  |

| Address |       | FD7H  |       |       |       |       |       |       |  |  |  |  |

#### Table 176. Port B Output Data Register (PBOUT)

#### Hex Address: FD8

#### Table 177. Port C GPIO Address Register (PCADDR)

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|

| Field   |      | PADDR[7:0]                  |   |   |   |   |   |   |  |

| RESET   |      | 00H                         |   |   |   |   |   |   |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FD8H |                             |   |   |   |   |   |   |  |

#### Hex Address: FD9

#### Table 178. Port C Control Registers (PCCTL)

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|

| Field   |      | PCTL                        |   |   |   |   |   |   |  |

| RESET   |      | 00H                         |   |   |   |   |   |   |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FD9H |                             |   |   |   |   |   |   |  |

#### Hex Address: FDA

#### Table 179. Port C Input Data Registers (PCIN)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |

| RESET   | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| R/W     | R    | R    | R    | R    | R    | R    | R    | R    |

| Address | FDAH |      |      |      |      |      |      |      |

#### Hex Address: FDB

| Bit     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Field   | POUT7 | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | FDBH  |       |       |       |       |       |       |       |

#### Hex Address: FDC

#### Table 181. Port D GPIO Address Register (PDADDR)

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|

| Field   |      | PADDR[7:0]                  |   |   |   |   |   |   |  |

| RESET   |      | 00H                         |   |   |   |   |   |   |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address | FDCH |                             |   |   |   |   |   |   |  |

#### Hex Address: FDD

#### Table 182. Port D Control Registers (PDCTL)

| Bit     | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|-----------------------------|---|---|---|---|---|---|--|--|

| Field   |      | PCTL                        |   |   |   |   |   |   |  |  |

| RESET   |      | 00H                         |   |   |   |   |   |   |  |  |

| R/W     | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |

| Address | FDDH |                             |   |   |   |   |   |   |  |  |

#### Hex Address: FDE

This address range is reserved.

#### Z8 Encore!<sup>®</sup> F0830 Series Product Specification

## Index

### **Symbols**

@ 165# 165% 165

### **Numerics**

10-bit ADC 4

### Α

absolute maximum ratings 184 AC characteristics 189 ADC 166 block diagram 99 overview 98 ADC Channel Register 1 (ADCCTL) 102 ADC Data High Byte Register (ADCDH) 103 ADC Data Low Bit Register (ADCDL) 103, 104, 105 **ADCX 166** ADD 166 add - extended addressing 166 add with carry 166 add with carry - extended addressing 166 additional symbols 165 address space 14 **ADDX 166** analog block/PWM signal synchronization 100 analog block/PWM signal zynchronization 100 analog signals 11 analog-to-digital converter overview 98 AND 169 **ANDX 169** architecture voltage measurements 98 arithmetic instructions 166 assembly language programming 162 assembly language syntax 163

### В

B 165 b 164 **BCLR 167** binary number suffix 165 BIT 167 bit 164 clear 167 manipulation instructions 167 set 167 set or clear 167 swap 167 test and jump 169 test and jump if non-zero 169 test and jump if zero 169 bit jump and test if non-zero 166 bit swap 169 block diagram 3 block transfer instructions 167 **BRK 169 BSET 167** BSWAP 167. 169 **BTJ** 169 BTJNZ 166, 169 **BTJZ 169**

### С

calibration and compensation, motor control measurements 101 CALL procedure 169 capture mode 89, 90 capture/compare mode 89 cc 164 CCF 168 characteristics, electrical 184 clear 168 CLR 168 COM 169 compare 89