# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-VQFN Exposed Pad                                       |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0831qh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                                  | Description                                                                                                                                                                                 | Page<br>No.                                                                  |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Dec<br>2012 | 13                | GPIO                                                                                                                             | Modified GPIO Port D0 language in Shared<br>Reset Pin section and Port Alternate Func-<br>tion Mapping table.                                                                               | <u>35, 36</u>                                                                |

| Sep<br>2011 | 12                | LED Drive Enable Register                                                                                                        | Clarified statement surrounding the Alternate<br>Function Register as it relates to the LED<br>function; revised Sector Based Flash Protec-<br>tion description; revised Packaging chapter. | <u>51,</u><br><u>115,</u><br><u>199</u>                                      |

| Dec<br>2007 | 11                | n/a                                                                                                                              | Updated all instances of <i>Z8 Encore! XP</i><br><i>F0830</i> to <i>Z8 Encore! F0830</i> .                                                                                                  | All                                                                          |

| Nov<br>2007 | 10                | DC Characteristics, On-Chip<br>Peripheral AC and DC Electri-<br>cal Characteristics                                              | Updated Tables 116 and and 122.                                                                                                                                                             | <u>185,</u><br><u>193</u>                                                    |

| Sep<br>2007 | 09                | Timers, PWM SINGLE OUT-<br>PUT Mode, PWM DUAL OUT-<br>PUT Mode, Analog-to-Digital<br>Converter, Reference Buffer.                | Updated Figures 2 and 4, Table 4.                                                                                                                                                           | <u>8, 9,</u><br><u>11, 68,</u><br><u>74, 75,</u><br><u>98,</u><br><u>101</u> |

| Apr<br>2007 | 08                | Optimizing NVDS Memory<br>Usage for Execution Speed,<br>On-Chip Peripheral AC and DC<br>Electrical Characteristics               | Added a note under Table 93 in Nonvolatile<br>Data Storage chapter. Updated Table 121<br>and Table 122 in Electrical Characteristics<br>chapter. Other style updates.                       | <u>137,</u><br><u>193,</u><br><u>193</u>                                     |

| Dec         | 07                | General Purpose Input/Output                                                                                                     | Added PD0 in Table 16.                                                                                                                                                                      | <u>38</u>                                                                    |

| 2006        |                   | Overview, Interrupt Controller                                                                                                   | Changed the number of interrupts to 17.                                                                                                                                                     | <u>1,5, 53</u>                                                               |

|             |                   | Nonvolatile Data Storage                                                                                                         | Updated chapter.                                                                                                                                                                            | <u>136</u>                                                                   |

|             |                   | Oscillator Control Register Defi-<br>nitions, AC Characteristics, On-<br>Chip Peripheral AC and DC<br>Electrical Characteristics | Updated Tables 117 and 122. Added Figure 24.                                                                                                                                                | <u>156,</u><br><u>189,</u><br><u>193</u>                                     |

|             |                   | Ordering Information                                                                                                             | Updated Part Number Suffix Designations.                                                                                                                                                    | 205                                                                          |

|             |                   | n/a                                                                                                                              | Removed Preliminary stamp from footer.                                                                                                                                                      | All                                                                          |

iii

| Master Interrupt Enable                                  | . 55 |

|----------------------------------------------------------|------|

| Interrupt Vectors and Priority                           | . 56 |

| Interrupt Assertion                                      | . 56 |

| Software Interrupt Assertion                             | . 57 |

| Interrupt Control Register Definitions                   | . 57 |

| Interrupt Request 0 Register                             | . 58 |

| Interrupt Request 1 Register                             | . 59 |

| Interrupt Request 2 Register                             | . 60 |

| IRQ0 Enable High and Low Bit Registers                   | . 60 |

| IRQ1 Enable High and Low Bit Registers                   | . 62 |

| IRQ2 Enable High and Low Bit Registers                   |      |

| Interrupt Edge Select Register                           |      |

| Shared Interrupt Select Register                         | . 66 |

| Interrupt Control Register                               | . 67 |

| Timers                                                   | . 68 |

| Architecture                                             | . 68 |

| Operation                                                | . 69 |

| Timer Operating Modes                                    | . 69 |

| Reading the Timer Count Values                           |      |

| Timer Pin Signal Operation                               | . 82 |

| Timer Control Register Definitions                       |      |

| Timer 0–1 High and Low Byte Registers                    |      |

| Timer Reload High and Low Byte Registers                 |      |

| Timer 0–1 PWM High and Low Byte Registers                |      |

| Timer 0–1 Control Registers                              | . 87 |

| Watchdog Timer                                           | . 92 |

| Operation                                                | . 92 |

| Watchdog Timer Refresh                                   | . 93 |

| Watchdog Timer Time-Out Response                         | . 93 |

| Watchdog Timer Reload Unlock Sequence                    | . 94 |

| Watchdog Timer Control Register Definitions              | . 95 |

| Watchdog Timer Control Register                          | . 95 |

| Watchdog Timer Reload Upper, High and Low Byte Registers | . 96 |

| Analog-to-Digital Converter                              | . 98 |

| Architecture                                             | . 98 |

| Operation                                                | . 99 |

| ADC Timing                                               | 100  |

| ADC Interrupt                                            | 101  |

| Reference Buffer                                         | 101  |

| Internal Voltage Reference Generator                     | 101  |

|                  | _                          |          | -           |          |

|------------------|----------------------------|----------|-------------|----------|

| Address (Hex)    | Register Description       | Mnemonic | Reset (Hex) | Page No. |

| Analog-to-Digita | al Converter (ADC, cont'd) |          |             |          |

| F73              | ADC data low bits          | ADCD_L   | XX          | 103      |

| F74              | ADC sample settling time   | ADCSST   | 0F          | 104      |

| F75              | ADC sample time            | ADCST    | 3F          | 105      |

| F76              | Reserved                   | —        | XX          |          |

| F77–F7F          | Reserved                   | —        | XX          |          |

| Low Power Con    | trol                       |          |             |          |

| F80              | Power control 0            | PWRCTL0  | 88          | 32       |

| F81              | Reserved                   | _        | XX          |          |

| LED Controller   |                            |          |             |          |

| F82              | LED drive enable           | LEDEN    | 00          | 51       |

| F83              | LED drive level high       | LEDLVLH  | 00          | 51       |

| F84              | LED drive level low        | LEDLVLL  | 00          | 52       |

| F85              | Reserved                   | _        | XX          |          |

| Oscillator Contr | ol                         |          |             |          |

| F86              | Oscillator control         | OSCCTL   | A0          | 154      |

| F87–F8F          | Reserved                   | —        | XX          |          |

| Comparator 0     |                            |          |             |          |

| F90              | Comparator 0 control       | CMP0     | 14          | 107      |

| F91–FBF          | Reserved                   | _        | XX          |          |

| Interrupt Contro | bller                      |          |             |          |

| FC0              | Interrupt request 0        | IRQ0     | 00          | 58       |

| FC1              | IRQ0 enable high bit       | IRQ0ENH  | 00          | 61       |

| FC2              | IRQ0 enable low Bit        | IRQ0ENL  | 00          | 61       |

| FC3              | Interrupt request 1        | IRQ1     | 00          | 59       |

| FC4              | IRQ1 enable high bit       | IRQ1ENH  | 00          | 62       |

| FC5              | IRQ1 enable low bit        | IRQ1ENL  | 00          | 63       |

| FC6              | Interrupt request 2        | IRQ2     | 00          | 60       |

| FC7              | IRQ2 enable high bit       | IRQ2ENH  | 00          | 64       |

| FC8              | IRQ2 enable low bit        | IRQ2ENL  | 00          | 64       |

| FC9–FCC          | Reserved                   | —        | XX          |          |

| FCD              | Interrupt edge select      | IRQES    | 00          | 66       |

#### Table 8. Register File Address Map (Continued)

Note: XX = Undefined.

## Low-Power Modes

The Z8 Encore! F0830 Series products contain power saving features. The highest level of power reduction is provided by the STOP Mode. The next level of power reduction is provided by the HALT Mode.

Further power savings can be implemented by disabling the individual peripheral blocks while in NORMAL Mode.

The user must not enable the pull-up register bits for unused GPIO pins, since these ports are default output to VSS. Unused GPIOs include those missing on 20-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

## **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP Mode. In STOP Mode, the operating characteristics are:

- Primary crystal oscillator and Internal Precision Oscillator are stopped; XIN and XOUT (if previously enabled) are disabled and PA0/PA1 revert to the states programmed by the GPIO registers

- System clock is stopped

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register

- If enabled, the Watchdog Timer logic continues to operate

- If enabled for operation in STOP Mode by the associated Flash option bit, the Voltage Brown-Out protection circuit continues to operate

- All other on-chip peripherals are idle

To minimize the current in STOP Mode, all GPIO pins that are configured as digital inputs must be driven to  $V_{DD}$  when the pull-up register bit is enabled or to one of power rail ( $V_{DD}$  or GND) when the pull-up register bit is disabled. The device can be brought out of STOP Mode using Stop Mode Recovery. For more information about Stop Mode Recovery, see *the* <u>Reset and Stop Mode Recovery</u> *chapter on page 21*.

| Port                | Pin | Mnemonic  | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-----------|--------------------------------|-----------------------------------------|

| Port C <sup>3</sup> | PC0 | Reserved  |                                | AFS1[0]: 0                              |

|                     |     | ANA4/CINP | ADC or comparator input        | AFS1[0]: 1                              |

|                     | PC1 | Reserved  |                                | AFS1[1]: 0                              |

|                     |     | ANA5/CINN | ADC or comparator input        | AFS1[1]: 1                              |

|                     | PC2 | Reserved  |                                | AFS1[2]: 0                              |

|                     |     | ANA6      | ADC analog input               | AFS1[2]: 1                              |

|                     | PC3 | COUT      | Comparator output              | AFS1[3]: 0                              |

|                     |     | Reserved  |                                | AFS1[3]: 1                              |

|                     | PC4 | Reserved  |                                | AFS1[4]: 0                              |

|                     |     |           |                                | AFS1[4]: 1                              |

|                     | PC5 | Reserved  |                                | AFS1[5]: 0                              |

|                     |     |           |                                | AFS1[5]: 1                              |

|                     | PC6 | Reserved  |                                | AFS1[6]: 0                              |

|                     |     |           |                                | AFS1[6]: 1                              |

|                     | PC7 | Reserved  |                                | AFS1[7]: 0                              |

|                     |     |           |                                | AFS1[7]: 1                              |

| Port D <sup>1</sup> | PD0 | RESET     | Default to be Reset function   | N/A                                     |

#### Table 16. Port Alternate Function Mapping (Continued)

Notes:

- Because there is only a single alternate function for each Port A and Port D (PD0) pin, the Alternate Function Set registers are not implemented for Port A and Port D (PD0). Enabling alternate function selections (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) automatically enables the associated alternate function.

- Because there are at most two choices of alternate functions for any Port B pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

- Because there are at most two choices of alternate functions for any Port C pin, the AFS2 Alternate Function Set Register is implemented but is not used to select the function. Additionally, alternate function selection (as described in the <u>Port A–D Alternate Function Subregisters</u> section on page 42) must also be enabled.

#### Port A–D Output Control Subregisters

The Port A–D Output Control Subregister, shown in Table 23, is accessed through the Port A–D Control Register by writing 03H to the Port A–D Address Register. Setting the bits in the Port A–D Output Control subregisters to 1 configures the specified port pins for opendrain operation. These subregisters affect the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7         | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | POC7      | POC6         | POC5        | POC4          | POC3         | POC2         | POC1         | POC0     |

| RESET   | 0         | 0            | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | lf 03H ir | n Port A–D A | Address Reg | gister, acces | sible throug | h the Port A | –D Control F | Register |

#### Table 23. Port A–D Output Control Subregisters (PxOC)

#### Bit Description

[7:0] Port Output Control

POCx These bits function independently of the Alternate function bit and always disable the drains, if set to 1.

0 = The drains are enabled for any OUTPUT Mode (unless overridden by the Alternate function).

1 = The drain of the associated pin is disabled (OPEN-DRAIN mode).

Note: x indicates the specific GPIO port pin number (7–0).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the timer PWM High and Low Byte registers to 0000H. This allows user software to determine if interrupts are generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt were generated by a reload.

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and Reload events. The user can configure the timer interrupt to be generated only at the input capture event or the reload event by setting the TICONFIG field of the TxCTL1 Register.

- 6. Configure the associated GPIO port pin for the timer input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time between the timer start and the capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **COMPARE Mode**

In COMPARE Mode, the timer counts up to 16-bit maximum compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Additionally, if the timer output alternate function is enabled, the timer output pin changes state (from Low to High or from High to Low) upon compare.

If the timer reaches FFFFH, the timer resets to 0000H and continues counting.

Observe the following steps for configuring a timer for COMPARE Mode and for initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the timer output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the compare value.

| 1FFFH          |           | <br>Page 15 | 1FFFH<br>1E00H |

|----------------|-----------|-------------|----------------|

|                | Sector 7  | Page 14     | 1DFFH<br>1C00H |

| 1C00H<br>18FFH |           | <br>Page 13 | 1BFFH<br>1A00H |

|                | Sector 6  | <br>Page 12 | 19FFH<br>1800H |

| 1800H<br>17FFH |           | <br>Page 11 | 17FFH<br>1600H |

| 1400H          | Sector 5  | <br>Page 10 | 15FFH<br>1400H |

| 13FFH          |           | <br>Page 9  | 13FFH<br>1200H |

|                | Sector 4  | <br>Page 8  | 11FFH          |

| 1C00H<br>0FFFH | Sector 3  | <br>Page 7  | 1C00H<br>0FFFH |

| 0C00H          | Seciol 3  | Page 6      | 0E00H<br>0DFFH |

| 0BFFH          | On star 0 | <br>Page 5  | 0C00H<br>0BFFH |

| 0800H          | Sector 2  | <br>Page 4  | 0A00H<br>09FFH |

| 07FFH          | Sector 1  | Page 3      | 0800H<br>07FFH |

| 0400H          | Sector    | <br>Page 2  | 0600H<br>05FFH |

| 03FFH          | Sector 0  | Page 1      | 0400H<br>03FFH |

| 0000H          |           | <br>Page 0  | 0200H<br>0100H |

|                |           |             | 0000H          |

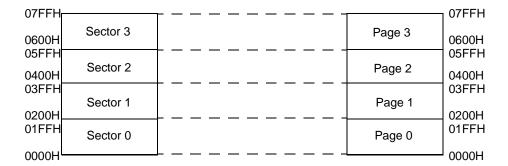

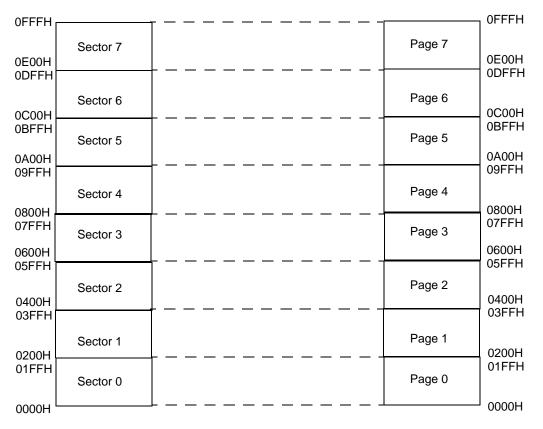

Figure 17. 8K Flash with NVDS

110

### Flash Operation Timing Using the Flash Frequency Registers

Before performing either a Program or Erase operation on Flash memory, the user must first configure the Flash Frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 10kHz to 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control the timing for Flash Program and Erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 10kHz or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! F0830 Series devices.

#### Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access by using the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code using the On-Chip Debugger. For more information, see the <u>Flash Option</u> <u>Bits</u> chapter on page 124 and the <u>On-Chip Debugger</u> chapter on page 139.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! F0830 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FHSWP and FWP Flash option bits combine to provide three levels of Flash program memory protection, as listed in Table 71. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

## Nonvolatile Data Storage

Z8 Encore! F0830 Series devices contain a Nonvolatile Data Storage (NVDS) element of up to 64 bytes (except when in Flash 12KB mode). This type of memory can perform over 100,000 write cycles.

### Operation

NVDS is implemented by special-purpose Zilog software stored in areas of program memory that are not user-accessible. These special-purpose routines use Flash memory to store the data, and incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

**Note:** The products in the Z8 Encore! F0830 Series feature multiple NVDS array sizes. See the <u>Z8 Encore! F0830 Series Family Part Selection Guide</u> section on page 2 for details.

### **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a predefined address outside of program memory that is accessible to the user. Both the NVDS address and data are singlebyte values. In order to not disturb the user code, these routines save the working register set before using it so that 16 bytes of stack space are required to preserve the site. After finishing the call to these routines, the working register set of the user code is recovered.

During both read and write accesses to the NVDS, interrupt service is not disabled. Any interrupts that occur during NVDS execution must not disturb the working register and existing stack contents; otherwise, the array can become corrupted. Zilog recommends the user disable interrupts before executing NVDS operations.

Use of the NVDS requires 16 bytes of available stack space. The contents of the working register set are saved before calling NVDS read or write routines.

For correct NVDS operation, the Flash Frequency registers must be programmed based on the system clock frequency. See *the* <u>Flash Operation Timing Using the Flash Frequency</u><u>Registers</u> *section on page 114*.

## **Crystal Oscillator**

The products in the Z8 Encore! F0830 Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of its on-chip peripherals. Alternatively, the X<sub>IN</sub> input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the X<sub>OUT</sub> pin must remain unconnected. The on-chip crystal oscillator also contains a clock filter function. To see the settings for this clock filter, see Table 90 on page 133. By default, however, this clock filter is disabled; therefore, no divide to the input clock (namely, the frequency of the signal on the X<sub>IN</sub> input pin) can determine the frequency of the system clock when using the default settings.

**Note:** Although the X<sub>IN</sub> pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use. See *the* System Clock Selection *section on page 151* for more information.

## **Operating Modes**

The Z8 Encore! F0830 Series products support the following four OSCILLATOR Modes:

- Minimum power for use with very low frequency crystals (32kHz to 1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The OSCILLATOR Mode is selected using user-programmable Flash option bits. See the <u>Flash Option Bits</u> chapter on page 124 for more information.

## **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Reg-

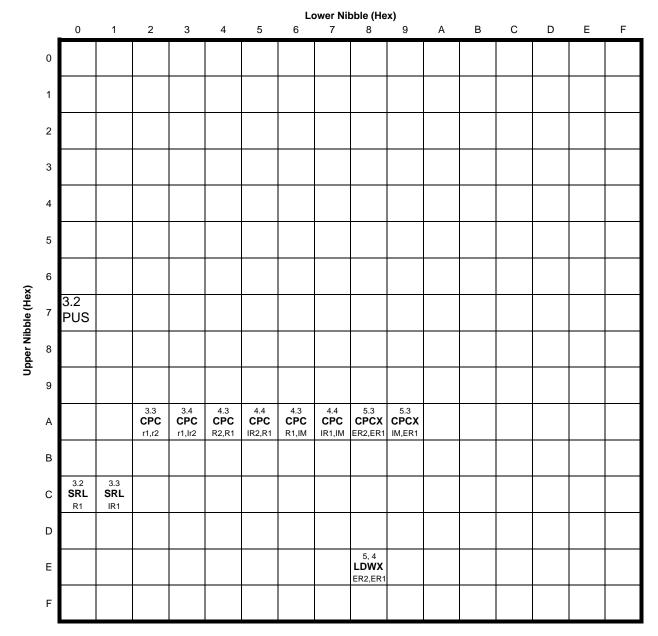

Figure 30. Second Op Code Map after 1FH

183

## **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50pF on all outputs.

|                     |                                            | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = 0°C to +70°C |     | V <sub>DD</sub> = 2.7 to 3.6V<br>T <sub>A</sub> = -40°C to<br>+105°C |        |       |                                                                                                              |  |

|---------------------|--------------------------------------------|----------------------------------------------------------------|-----|----------------------------------------------------------------------|--------|-------|--------------------------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                                  | Min                                                            | Max | Min                                                                  | Max    | Units | Conditions                                                                                                   |  |

| F <sub>SYSCLK</sub> | System Clock Fre-<br>quency                |                                                                |     | -                                                                    | 20.0   | MHz   | Read-only from Flash<br>memory                                                                               |  |

|                     |                                            |                                                                |     | 0.03276<br>8                                                         | 20.0   | MHz   | Program or erasure of the Flash memory                                                                       |  |

| F <sub>XTAL</sub>   | Crystal Oscillator<br>Frequency            |                                                                |     | 1.0                                                                  | 20.0   | MHz   | System clock frequen-<br>cies below the crystal<br>oscillator minimum<br>require an external                 |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |     | 0.03276<br>8                                                         | 5.5296 | MHz   | Oscillator is <b>not</b> adjust-<br>able over the entire<br>range. User may select<br>Min or Max value only. |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |     | 5.31                                                                 | 5.75   | MHz   | High speed with trim-<br>ming                                                                                |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |     | 4.15                                                                 | 6.91   | MHz   | High speed without trimming                                                                                  |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |     | 30.7                                                                 | 33.3   | KHz   | Low speed with trim-<br>ming                                                                                 |  |

| F <sub>IPO</sub>    | Internal Precision<br>Oscillator Frequency |                                                                |     | 24                                                                   | 40     | KHz   | Low speed without trimming                                                                                   |  |

| T <sub>XIN</sub>    | System Clock<br>Period                     |                                                                |     | 50                                                                   | -      | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                     |  |

| T <sub>XINH</sub>   | System Clock High<br>Time                  |                                                                |     | 20                                                                   | 30     | ns    | T <sub>CLK</sub> = 50 ns                                                                                     |  |

| T <sub>XINL</sub>   | System Clock Low<br>Time                   |                                                                |     | 20                                                                   | 30     | ns    | T <sub>CLK</sub> = 50 ns                                                                                     |  |

#### **Table 117. AC Characteristics**

## Appendix A. Register Tables

For the reader's convenience, this appendix lists all F0830 Series registers numerically by hexadecimal address.

## **General Purpose RAM**

In the F0830 Series, the 000–EFF hexadecimal address range is partitioned for general-purpose random access memory, as follows.

#### Hex Addresses: 000–0FF

This address range is reserved for general-purpose register file RAM. For more details, see the <u>Register File</u> section on page 14.

#### Hex Addresses: 100-EFF

This address range is reserved.

### Timer 0

For more information about these Timer Control registers, see the <u>Timer Control Register</u> <u>Definitions</u> section on page 83.

#### Hex Address: F00

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | Т   | Н   |     |     |     |

| RESET   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F0  | 0H  |     |     |     |

#### Table 130. Timer 0 High Byte Register (T0H)

#### Hex Address: F05

#### Table 135. Timer 0 PWM Low Byte Register (T0PWML)

| Bit     | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|-----|-----------------------------|---|----|----|---|---|---|--|--|

| Field   |     | PWML                        |   |    |    |   |   |   |  |  |

| RESET   | 0   | 0                           | 0 | 0  | 0  | 0 | 0 | 0 |  |  |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |  |  |

| Address |     |                             |   | F0 | 5H |   |   |   |  |  |

#### Hex Address: F06

#### Table 136. Timer 0 Control Register 0 (T0CTL0)

| Bit     | 7       | 6    | 5    | 4        | 3   | 2    | 1   | 0      |

|---------|---------|------|------|----------|-----|------|-----|--------|

| Field   | TMODEHI | TICO | NFIG | Reserved |     | PWMD |     | INPCAP |

| RESET   | 0       | 0    | 0    | 0        | 0   | 0    | 0   | 0      |

| R/W     | R/W     | R/W  | R/W  | R/W      | R/W | R/W  | R/W | R/W    |

| Address |         |      |      | F0       | 6H  |      |     |        |

#### Hex Address: F07

#### Table 137. Timer 0 Control Register 1 (T0CTL1)

| Bit     | 7   | 6    | 5          | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------|------------|-----|-----|-----|-----|-----|

| Field   | TEN | TPOL | PRES TMODE |     |     |     |     |     |

| RESET   | 0   | 0    | 0          | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W |

| Address |     |      |            | F0  | 7H  |     |     |     |

#### Hex Address: F08

#### Table 138. Timer 1 High Byte Register (T1H)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | TH   |     |     |     |     |     |     |  |

| RESET   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F08H |     |     |     |     |     |     |  |

#### Hex Addresses: F87–F8F

This address range is reserved.

## Comparator 0

For more information about the Comparator Register, see the <u>Comparator Control Register Definitions</u> section on page 107.

#### Hex Address: F90

| Bit     | 7        | 6      | 5   | 4   | 3        | 2   | 1   | 0   |

|---------|----------|--------|-----|-----|----------|-----|-----|-----|

| Field   | Reserved | INNSEL |     | REF | Reserved |     |     |     |

| RESET   | 0        | 0      | 0   | 1   | 0        | 1   | 0   | 0   |

| R/W     | R/W      | R/W    | R/W | R/W | R/W      | R/W | R/W | R/W |

| Address | F90H     |        |     |     |          |     |     |     |

#### Table 156. Comparator Control Register (CMP0)

#### Hex Addresses: F91–FBF

This address range is reserved.

### **Interrupt Controller**

For more information about the Interrupt Control registers, see the <u>Interrupt Control Reg-</u> <u>ister Definitions</u> section on page 57.

#### Hex Address: FC0

| Bit     | 7        | 6   | 5   | 4        | 3        | 2        | 1        | 0    |

|---------|----------|-----|-----|----------|----------|----------|----------|------|

| Field   | Reserved | T1I | TOI | Reserved | Reserved | Reserved | Reserved | ADCI |

| RESET   | 0        | 0   | 0   | 0        | 0        | 0        | 0        | 0    |

| R/W     | R/W      | R/W | R/W | R/W      | R/W      | R/W      | R/W      | R/W  |

| Address | FC0H     |     |     |          |          |          |          |      |

#### Table 157. Interrupt Request 0 Register (IRQ0)

#### Hex Address: FC5

| Bit     | 7      | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |

|---------|--------|---------|--------|--------|---------------|--------|--------|--------|--|

| Field   | PA7ENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |  |

| RESET   | 0      | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |

| R/W     | R/W    | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |

| Address |        | FC5H    |        |        |               |        |        |        |  |

#### Hex Address: FC6

#### Table 163. Interrupt Request 2 Register (IRQ2)

| Bit     | 7        | 6    | 5   | 4   | 3    | 2    | 1    | 0    |  |

|---------|----------|------|-----|-----|------|------|------|------|--|

| Field   | Reserved |      |     |     | PC3I | PC2I | PC1I | PC0I |  |

| RESET   | 0        | 0    | 0   | 0   | 0    | 0    | 0    | 0    |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W  | R/W  | R/W  | R/W  |  |

| Address |          | FC6H |     |     |      |      |      |      |  |

#### Hex Address: FC7

#### Table 164. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7        | 6    | 5   | 4   | 3     | 2     | 1     | 0     |  |

|---------|----------|------|-----|-----|-------|-------|-------|-------|--|

| Field   | Reserved |      |     |     | C3ENH | C2ENH | C1ENH | C0ENH |  |

| RESET   | 0        | 0    | 0   | 0   | 0     | 0     | 0     | 0     |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   |  |

| Address |          | FC7H |     |     |       |       |       |       |  |

#### Hex Address: FC8

#### Table 165. IRQ2 Enable Low Bit Register (IRQ2ENL)

| Bit     | 7        | 6    | 5   | 4   | 3     | 2     | 1     | 0     |  |

|---------|----------|------|-----|-----|-------|-------|-------|-------|--|

| Field   | Reserved |      |     |     | C3ENL | C2ENL | C1ENL | C0ENL |  |

| RESET   | 0        | 0    | 0   | 0   | 0     | 0     | 0     | 0     |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   |  |

| Address |          | FC8H |     |     |       |       |       |       |  |

JP 169 LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167 LDX 168 LEA 168 load 168 logical 169 **MULT 167 NOP 168** OR 169 ORX 169 POP 168 **POPX 168** program control 169 **PUSH 168** PUSHX 168 RCF 167, 168 **RET 169** RL 169 **RLC 169** rotate and shift 169 RR 170 **RRC** 170 **SBC 167** SCF 167. 168 **SRA 170** SRL 170 **SRP** 168 **STOP 168 SUB 167 SUBX 167 SWAP 170** TCM 167 **TCMX 167** TM 167 TMX 167 **TRAP 169** watch-dog timer refresh 168 XOR 169 **XORX 169** instructions, eZ8 classes of 166

interrupt control register 67 interrupt controller 53 architecture 53 interrupt assertion types 56 interrupt vectors and priority 56 operation 55 register definitions 57 software interrupt assertion 57 interrupt edge select register 65 interrupt request 0 register 58 interrupt request 1 register 59 interrupt request 2 register 60 interrupt return 169 interrupt vector listing 53 IR 164 Ir 164 **IRET 169** IRQ0 enable high and low bit registers 60 IRQ1 enable high and low bit registers 62 IRQ2 enable high and low bit registers 63 **IRR 164** Irr 164

#### J

JP 169 jump, conditional, relative, and relative conditional 169

#### L

LD 168 LDC 168 LDCI 167, 168 LDE 168 LDEI 167, 168 LDX 168 LEA 168 load constant 167 load constant to/from program memory 168 load constant with auto-increment addresses 168 load effective address 168 load external data 168

## **Customer Support**

To share comments, get your technical questions answered or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://zilog.com/</u><u>kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.